Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 19                                                        |

| Program Memory Size        | 4KB (4K × 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0412sj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### ilog° Embedded in Life An IXYS Company

17

# **Register File Address Map**

Table 7 provides the address map for the Register File of the Z8 Encore! XP<sup>®</sup> F0822 Series products. Not all devices and package styles in the F0822 Series support the ADC, the SPI, or all of the GPIO Ports. Consider registers for unimplemented peripherals to be reserved.

| Address (He | ex) Register Description          | Mnemonic | Reset (Hex) | Page No   |

|-------------|-----------------------------------|----------|-------------|-----------|

| General Pur | pose RAM                          |          |             |           |

| 000–3FF     | General-Purpose Register File RAM | —        | XX          |           |

| 400–EFF     | Reserved                          | _        | XX          |           |

| Timer 0     |                                   |          |             |           |

| F00         | Timer 0 High Byte                 | тон      | 00          | <u>64</u> |

| F01         | Timer 0 Low Byte                  | TOL      | 01          | <u>64</u> |

| F02         | Timer 0 Reload High Byte          | TORH     | FF          | <u>65</u> |

| F03         | Timer 0 Reload Low Byte           | TORL     | FF          | <u>65</u> |

| F04         | Timer 0 PWM High Byte             | TOPWMH   | 00          | <u>66</u> |

| F05         | Timer 0 PWM Low Byte              | TOPWML   | 00          | <u>66</u> |

| F06         | Timer 0 Control 0                 | T0CTL0   | 00          | <u>68</u> |

| F07         | Timer 0 Control 1                 | T0CTL1   | 00          | <u>68</u> |

| Timer 1     |                                   |          |             |           |

| F08         | Timer 1 High Byte                 | T1H      | 00          | <u>64</u> |

| F09         | Timer 1 Low Byte                  | T1L      | 01          | <u>64</u> |

| F0A         | Timer 1 Reload High Byte          | T1RH     | FF          | <u>65</u> |

| F0B         | Timer 1 Reload Low Byte           | T1RL     | FF          | <u>65</u> |

| F0C         | Timer 1 PWM High Byte             | T1PWMH   | 00          | <u>66</u> |

| F0D         | Timer 1 PWM Low Byte              | T1PWML   | 00          | <u>66</u> |

| F0E         | Timer 1 Control 0                 | T1CTL0   | 00          | <u>68</u> |

| F0F         | Timer 1 Control 1                 | T1CTL1   | 00          | <u>68</u> |

| F10–F3F     | Reserved                          | _        | XX          |           |

#### Table 7. Register File Address Map

Note: XX = undefined.

Embedded in Life

| Address (He         | ex) Register Description              | Mnemonic | Reset (Hex) | Page No                    |

|---------------------|---------------------------------------|----------|-------------|----------------------------|

| GPIO Port C         | ;                                     |          |             |                            |

| FD8                 | Port C Address                        | PCADDR   | 00          | <u>32</u>                  |

| FD9                 | Port C Control                        | PCCTL    | 00          | <u>33</u>                  |

| FDA                 | Port C Input Data                     | PCIN     | XX          | <u>38</u>                  |

| FDB                 | Port C Output Data                    | PCOUT    | 00          | <u>39</u>                  |

| FDC-FEF             | Reserved                              | _        | XX          |                            |

| Watchdog T          | ïmer (WDT)                            |          |             |                            |

| FF0                 | Watchdog Timer Control                | WDTCTL   | XXX00000b   | <u>73</u>                  |

| FF1                 | Watchdog Timer Reload Upper Byte      | WDTU     | FF          | <u>75</u>                  |

| FF2                 | Watchdog Timer Reload High Byte       | WDTH     | FF          | <u>75</u>                  |

| FF3                 | Watchdog Timer Reload Low Byte        | WDTL     | FF          | <u>75</u>                  |

| FF4-FF7             | Reserved                              |          | XX          |                            |

| Flash Memo          | ry Controller                         |          |             |                            |

| FF8                 | Flash Control                         | FCTL     | 00          | <u>150</u>                 |

| FF8                 | Flash Status                          | FSTAT    | 00          | <u>151</u>                 |

| FF9                 | Page Select                           | FPS      | 00          | <u>152</u>                 |

| FF9 (if<br>enabled) | Flash Sector Protect                  | FPROT    | 00          | <u>153</u>                 |

| FFA                 | Flash Programming Frequency High Byte | FFREQH   | 00          | <u>153</u>                 |

| FFB                 | Flash Programming Frequency Low Byte  | FFREQL   | 00          | <u>153</u>                 |

| Read-Only I         | Memory                                |          |             |                            |

| FF8                 | Reserved                              | _        | XX          |                            |

| FF9                 | Page Select                           | RPS      | 00          | <u>152</u>                 |

| FFA-FFB             | Reserved                              | —        | XX          |                            |

| eZ8 CPU             |                                       |          |             |                            |

| FFC                 | Flags                                 | _        | XX          | Refer to the               |

| FFD                 | Register Pointer                      | RP       | XX          | eZ8 CPU                    |

| FFE                 | Stack Pointer High Byte               | SPH      | XX          | <u>Core User</u><br>Manual |

| FFF                 | Stack Pointer Low Byte                | SPL      | XX          | <u>(UM0128)</u>            |

| Note: XX = u        | ndefined.                             |          |             |                            |

# Table 7. Register File Address Map (Continued)

20

# Embedded in Life An TIXYS Company 21

# Reset and Stop Mode Recovery

The Reset Controller within the Z8 Encore! XP<sup>®</sup> F0822 Series controls Reset and Stop Mode Recovery operation. In typical operation, the following events cause a Reset to occur:

- Power-On Reset (POR)

- Voltage Brown-Out

- WDT time-out (when configured through the WDT\_RES option bit to initiate a Reset)

- External **RESET** pin assertion

- On-Chip Debugger initiated Reset (OCDCTL[0] set to 1)

When the Z8 Encore! XP<sup>®</sup> F0822 Series device is in STOP Mode, a Stop Mode Recovery is initiated by any of the following events:

- WDT time-out

- GPIO Port input pin transition on an enabled Stop Mode Recovery source

- DBG pin driven Low

# **Reset Types**

Z8 Encore! XP<sup>®</sup> F0822 Series provides two types of reset operation (System Reset and Stop Mode Recovery). The type of reset is a function of both the current operating mode of the Z8 Encore! XP<sup>®</sup> F0822 Series device and the source of the Reset. Table 8 lists the types of Resets and their operating characteristics.

#### Table 8. Reset and Stop Mode Recovery Characteristics and Latency

|                       | Reset Characteristics and Latency           |         |                                                   |  |  |  |

|-----------------------|---------------------------------------------|---------|---------------------------------------------------|--|--|--|

| Reset Type            | <b>Control Registers</b>                    | eZ8 CPU | Reset Latency (Delay)                             |  |  |  |

| System Reset          | Reset (as applicable)                       | Reset   | 66 WDT Oscillator cycles + 16 System Clock cycles |  |  |  |

| Stop Mode<br>Recovery | Unaffected, except for the WDT_CTL Register | Reset   | 66 WDT Oscillator cycles + 16 System Clock cycles |  |  |  |

# System Reset

During a System Reset, a Z8 Encore! XP<sup>®</sup> F0822 Series device is held in Reset for 66 cycles of the WDT oscillator followed by 16 cycles of the system clock. At the beginning

# Embedded in Life

# Port A–C Output Control Subregisters

The Port A–C Output Control Subregister, shown in Table 18, is accessed through the Port A–C Control Register by writing 03H to the Port A–C Address Register. Setting the bits in the Port A–C Output Control subregisters to 1 configures the specified port pins for opendrain operation. These subregisters affect the pins directly and, as a result, alternate functions are also affected.

#### Table 18. Port A–C Output Control Subregisters

| Bit         | 7                                                                                                                  | 7 6 5 4 3 2 1 0                                                                                 |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Field       | POC7                                                                                                               | POC7         POC6         POC5         POC4         POC3         POC2         POC1         POC0 |  |  |  |  |  |  |

| RESET       |                                                                                                                    | 0                                                                                               |  |  |  |  |  |  |

| R/W         |                                                                                                                    | R/W                                                                                             |  |  |  |  |  |  |

| Address     | See footnote.                                                                                                      |                                                                                                 |  |  |  |  |  |  |

| Note: If 03 | Note: If 03H is written to the Port A–C Address Register, then it is accessible via the Port A–C Control Register. |                                                                                                 |  |  |  |  |  |  |

| <b>D</b> '' | <b>D</b>                                                                                                           |                                                                                                 |  |  |  |  |  |  |

| Bit   | Description                                                                                                                                                                                   |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Port Output Control                                                                                                                                                                           |

| POCx  | These bits function independently of the alternate function bit and always disable the drains if set to 1.                                                                                    |

|       | <ul> <li>0 = The drains are enabled for any output mode (unless overridden by the alternate function).</li> <li>1 = The drain of the associated pin is disabled (open-drain mode).</li> </ul> |

Note: x indicates register bits in the range [7:0].

#### ilog<sup>°</sup> Embedded in Life An IXYS Company 40

# Interrupt Controller

The interrupt controller on Z8 Encore! XP<sup>®</sup> F0822 Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of the interrupt controller include the following:

- 19 unique interrupt vectors:

- 12 GPIO port pin interrupt sources

- 7 On-chip peripheral interrupt sources

- Flexible GPIO interrupts:

- 8 selectable rising and falling edge GPIO interrupts

- 4 dual-edge interrupts

- Three levels of individually programmable interrupt priority

- WDT is configured to generate an interrupt

Interrupt Requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an Interrupt Service Routine (ISR). Usually this ISR is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt control has no effect on operation. For more information about interrupt servicing, refer to the <u>eZ8 CPU Core User Manual (UM0128)</u>, which is available for download at <u>www.zilog.com</u>.

# **Interrupt Vector Listing**

Table 24 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most significant byte (MSB) at the even program memory address and the least significant byte (LSB) at the following odd program memory address.

### ilog Embedded in Life An IXYS Company

45

# **Interrupt Control Register Definitions**

For all interrupts other than the WDT interrupt, the Interrupt Control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

# **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) Register, shown in Table 25, stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the IRQ0 Register to determine if any interrupt requests are pending.

| Bit          | 7                                                                                      | 6                                                                                                                                                                                    | 5            | 4                                          | 3          | 2 | 1 | 0 |

|--------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------|------------|---|---|---|

| Field        | Reserved         T1I         T0I         U0RXI         U0TXI         I2CI         SPII |                                                                                                                                                                                      |              |                                            |            |   |   |   |

| RESET        |                                                                                        |                                                                                                                                                                                      |              | (                                          | )          |   |   |   |

| R/W          |                                                                                        |                                                                                                                                                                                      |              | R/                                         | W          |   |   |   |

| Address      |                                                                                        |                                                                                                                                                                                      |              | FC                                         | ОH         |   |   |   |

| Bit          | Description                                                                            | n                                                                                                                                                                                    |              |                                            |            |   |   |   |

| [7]          | Reserved<br>This bit is re                                                             | Reserved<br>This bit is reserved and must be programmed to 0.                                                                                                                        |              |                                            |            |   |   |   |

| [6]<br>T1I   | 0 = No inter                                                                           | <b>Timer 1 Interrupt Request</b><br>0 = No interrupt request is pending for Timer 1.<br>1 = An interrupt request from Timer 1 is awaiting service.                                   |              |                                            |            |   |   |   |

| [5]<br>T0I   |                                                                                        | rupt reques                                                                                                                                                                          | t is pending | for Timer 0.<br>0 is awaitin               |            |   |   |   |

| [4]<br>U0RXI | 0 = No inter                                                                           | UART 0 Receiver Interrupt Request<br>0 = No interrupt request is pending for the UART 0 receiver.<br>1 = An interrupt request from the UART 0 receiver is awaiting service.          |              |                                            |            |   |   |   |

| [3]<br>UOTXI | 0 = No inter                                                                           | UART 0 Transmitter Interrupt Request<br>0 = No interrupt request is pending for the UART 0 transmitter.<br>1 = An interrupt request from the UART 0 transmitter is awaiting service. |              |                                            |            |   |   |   |

| [2]<br>I2CI  |                                                                                        | rupt reques                                                                                                                                                                          | t is pending | for the I <sup>2</sup> C.<br>C is awaiting | g service. |   |   |   |

#### Table 25. Interrupt Request 0 Register (IRQ0)

# Embedded in Life

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT Mode equation is used to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is calculated using the following equation:

$PWM \text{ Output High Time Ratio (\%)} = \frac{\text{Reload Value} - PWM \text{ Value}}{\text{Reload Value}} x100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is calculated using the following equation:

PWM Output High Time Ratio (%) =  $\frac{PWM \text{ Value}}{\text{Reload Value}} \times 100$

#### CAPTURE Mode

In CAPTURE Mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The capture count value is written to the Timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the capture event occurs, an interrupt is generated and the timer continues counting.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting.

Observe the following procedure for configuring a timer for CAPTURE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. This allows user software to determine if interrupts were generated by either a capture event or a reload. If

- ilog<sup>\*</sup> Embedded in Life n⊒IXYS Company 81

- Set or clear the CTSE bit to enable or disable control from the remote receiver through the CTS pin.

- 7. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. Because the UART Transmit Data Register is empty, an interrupt is generated immediately. When the UART transmit interrupt is detected, the associated ISR performs the following:

- 1. Write the UART Control 1 Register to select the outgoing address bit:

- Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte; clear it if sending a data byte.

- 2. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers data to the Transmit Shift Register and then transmits the data.

- 3. Clear the UART transmit interrupt bit in the applicable Interrupt Request Register.

- 4. Execute the IRET instruction to return from the ISR and waits for the Transmit Data Register to again become empty.

# **Receiving Data using the Polled Method**

Observe the following procedure to configure the UART for polled data reception:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register to enable Multiprocessor mode functions, if appropriate.

- 4. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if required, and if MULTIPROCESSOR Mode is not enabled, and select either even or odd parity.

- 5. Check the RDA bit in the UART Status 0 Register to determine if the Receive Data Register contains a valid data byte (indicated by 1). If RDA is set to 1 to indicate available data, continue to <u>Step 6</u>. If the Receive Data Register is empty (indicated by a 0), continue to monitor the RDA bit awaiting reception of the valid data.

ilog<sup>°</sup> <sup>nbedded in Life</sup> IXYS Company 96

For reliable communication, the UART baud rate error must never exceed 5 percent. Table 62 provides information about data rate errors for popular baud rates and commonly used crystal oscillator frequencies.

|                          | 10.0MHz Sy                  | stem Clock              | (                     |                          | 5.5296 MHz S                | System Clock         | (         |

|--------------------------|-----------------------------|-------------------------|-----------------------|--------------------------|-----------------------------|----------------------|-----------|

| Desired<br>Rate<br>(kHz) | BRG<br>Divisor<br>(Decimal) | Actual<br>Rate<br>(kHz) | Error (%)             | Desired<br>Rate<br>(kHz) | BRG<br>Divisor<br>(Decimal) | Actual<br>Rate (kHz) | Error (%) |

| 1250.0                   | N/A                         | N/A                     | N/A                   | 1250.0                   | N/A                         | N/A                  | N/A       |

| 625.0                    | 1                           | 625.0                   | 0.00                  | 625.0                    | N/A                         | N/A                  | N/A       |

| 250.0                    | 3                           | 208.33                  | -16.67                | 250.0                    | 1                           | 345.6                | 38.24     |

| 115.2                    | 5                           | 125.0                   | 8.51                  | 115.2                    | 3                           | 115.2                | 0.00      |

| 57.6                     | 11                          | 56.8                    | -1.36                 | 57.6                     | 6                           | 57.6                 | 0.00      |

| 38.4                     | 16                          | 39.1                    | 1.73                  | 38.4                     | 9                           | 38.4                 | 0.00      |

| 19.2                     | 33                          | 18.9                    | 0.16                  | 19.2                     | 18                          | 19.2                 | 0.00      |

| 9.60                     | 65                          | 9.62                    | 0.16                  | 9.60                     | 36                          | 9.60                 | 0.00      |

| 4.80                     | 130                         | 4.81                    | 0.16                  | 4.80                     | 72                          | 4.80                 | 0.00      |

| 2.40                     | 260                         | 2.40                    | -0.03                 | 2.40                     | 144                         | 2.40                 | 0.00      |

| 1.20                     | 521                         | 1.20                    | -0.03                 | 1.20                     | 288                         | 1.20                 | 0.00      |

| 0.60                     | 1042                        | 0.60                    | -0.03                 | 0.60                     | 576                         | 0.60                 | 0.00      |

| 0.30                     | 2083                        | 0.30                    | 0.2                   | 0.30                     | 1152                        | 0.30                 | 0.00      |

| 3                        | .579545 MHz                 | System Clo              | ock                   |                          | 1.8432MHz \$                | System Clock         | (         |

| Desired<br>Rate<br>(kHz) | BRG<br>Divisor<br>(Decimal) | Actual<br>Rate<br>(kHz) | Error (%)             | Desired<br>Rate<br>(kHz) | BRG<br>Divisor<br>(Decimal) | Actual<br>Rate (kHz) | Error (%) |

| 1250.0                   | N/A                         | N/A                     | N/A                   | 1250.0                   | N/A                         | N/A                  | N/A       |

| 625.0                    | N/A                         | N/A                     | N/A                   | 625.0                    | N/A                         | N/A                  | N/A       |

| 250.0                    | 1                           | 223.72                  | -10.51                | 250.0                    | N/A                         | N/A                  | N/A       |

| 115.2                    | 2                           | 111.9                   | -2.90                 | 115.2                    | 1                           | 115.2                | 0.00      |

| 57.6                     | 4                           | 55.9                    | -2.90                 | 57.6                     | 2                           | 57.6                 | 0.00      |

| 38.4                     | 6                           | 37.3                    | -2.90                 | 38.4                     | 3                           | 38.4                 | 0.00      |

|                          | 40                          | 18.6                    | -2.90                 | 19.2                     | 6                           | 19.2                 | 0.00      |

| 19.2                     | 12                          | 10.0                    | 2.00                  |                          |                             |                      |           |

| 19.2<br>9.60             | 23                          | 9.73                    | 1.32                  | 9.60                     | 12                          | 9.60                 | 0.00      |

|                          |                             |                         |                       | 9.60<br>4.80             | 12<br>24                    | 9.60<br>4.80         | 0.00      |

| 9.60                     | 23                          | 9.73                    | 1.32                  |                          |                             |                      |           |

| 9.60<br>4.80             | 23<br>47                    | 9.73<br>4.76            | 1.32<br>-0.83         | 4.80                     | 24                          | 4.80                 | 0.00      |

| 9.60<br>4.80<br>2.40     | 23<br>47<br>93              | 9.73<br>4.76<br>2.41    | 1.32<br>-0.83<br>0.23 | 4.80<br>2.40             | 24<br>48                    | 4.80<br>2.40         | 0.00      |

#### Table 62. UART Baud Rates

#### ILO Embedded in Life IXYS Company 119

# **Start and Stop Conditions**

The Master ( $I^2C$ ) drives all Start and Stop signals and initiates all transactions. To start a transaction, the  $I^2C$  Controller generates a start condition by pulling the SDA signal Low while SCL is High. To complete a transaction, the  $I^2C$  Controller generates a Stop condition by creating a Low-to-High transition of the SDA signal while the SCL signal is High. The start and stop bits in the  $I^2C$  Control Register control the sending of start and stop conditions. A Master is also allowed to end one transaction and begin a new one by issuing a restart. This restart issuance is accomplished by setting the start bit at the end of a transaction rather than setting the stop bit.

**Note:** The start condition is not sent until the start bit is set and data has been written to the I<sup>2</sup>C Data Register.

# Master Write and Read Transactions

The following sections provide Zilog's recommended procedure for performing  $I^2C$  write and read transactions from the  $I^2C$  Controller (Master) to slave  $I^2C$  devices. In general, software should rely on the TDRE, RDRF and NCKI bits of the status register (these bits generate interrupts) to initiate software actions. When using interrupts or DMA, the TXI bit is set to start each transaction and cleared at the end of each transaction to eliminate a *trailing* transmit interrupt.

**Caution:** Caution should be used in using the ACK status bit within a transaction because it is difficult for software to tell when it is updated by hardware.

When writing data to a slave, the  $I^2C$  pauses at the beginning of the Acknowledge cycle if the data register has not been written with the next value to be sent (TDRE bit in the  $I^2C$ Status Register equal to 1). In this scenario where software is not keeping up with the  $I^2C$ bus (TDRE asserted longer than one byte time), the Acknowledge clock cycle for byte *n* is delayed until the data register is written with byte n+1, and appears to be grouped with the data clock cycles for byte n+1. If either the start or stop bit is set, the  $I^2C$  does not pause prior to the Acknowledge cycle because no additional data is sent.

When a Not Acknowledge condition is received during a write (either during the address or data phases), the I<sup>2</sup>C Controller generates the Not Acknowledge interrupt (NCKI = 1) and pause until either the stop or start bit is set. Unless the Not Acknowledge was received on the last byte, the data register will already have been written with the next address or data byte to send. In this case the FLUSH bit of the control register should be set at the same time the stop or start bit is set to remove the stale transmit data and enable subsequent transmit interrupts.

#### ilog° Embedded in Life An∎IXYS Company

130

| Bit         | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [5]<br>ACK  | Acknowledge<br>This bit indicates the status of the Acknowledge for the last byte transmitted or received. When<br>set, this bit indicates that an Acknowledge occurred for the last byte transmitted or received.<br>This bit is cleared when IEN = 0 or when a Not Acknowledge occurred for the last byte trans-<br>mitted or received. It is not reset at the beginning of each transaction and is not reset when this<br>register is read.                                                                                                                                                                                                                                                         |

|             | <b>Caution:</b> When making decisions based on this bit within a transaction, software cannot determine when the bit is updated by hardware. In the case of write transactions, the $1^{2}$ C pauses at the beginning of the Acknowledge cycle if the next transmit data or address byte has not been written (TDRE = 1) and STOP and start = 0. In this case the ACK bit is not updated until the transmit interrupt is serviced and the Acknowledge cycle for the previous byte completes. For examples on usage of the ACK bit, see the <u>Address Only Transaction with a 7-Bit Address</u> section on page 120 and the <u>Address-Only Transaction with a 10-Bit Address</u> section on page 122. |

| [4]         | <b>10-Bit Address</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 10B         | This bit indicates whether a 10-bit or 7-bit address is being transmitted. After the start bit is set, if the five most-significant bits of the address are 11110B, this bit is set. When set, it is reset after the first byte of the address has been sent.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| [3]         | <b>Read</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RD          | This bit indicates the direction of transfer of the data. It is active High during a read. The status of this bit is determined by the least-significant bit of the I <sup>2</sup> C Shift Register after the start bit is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| [2]         | <b>Transmit Address State</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TAS         | This bit is active High while the address is being shifted out of the I <sup>2</sup> C Shift Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| [1]         | <b>Data Shift State</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DSS         | This bit is active High while data is being shifted to or from the I <sup>2</sup> C Shift Register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| [0]<br>NCKI | <b>NACK Interrupt</b><br>This bit is set High when a Not Acknowledge condition is received or sent and neither the start<br>nor the stop bit is active. When set, this bit generates an interrupt that can only be cleared by<br>setting the start or stop bit, allowing you to specify whether you want to perform a stop or a<br>repeated start.                                                                                                                                                                                                                                                                                                                                                     |

# Page Select Register

The Page Select (FPS) Register, shown in Table 86, selects the Flash memory page to be erased or programmed. Each Flash page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory locations with the 7 most significant bits of the address provided by the PAGE field are erased to FFH.

The Page Select Register shares its Register File address with the Flash Sector Protect Register. The Page Select Register cannot be accessed when the Flash Sector Protect Register is enabled.

| Bit     | 7       | 6    | 5   | 4  | 3  | 2 | 1 | 0 |

|---------|---------|------|-----|----|----|---|---|---|

| Field   | INFO_EN | PAGE |     |    |    |   |   |   |

| RESET   |         | 0    |     |    |    |   |   |   |

| R/W     |         |      | R/W |    |    |   |   |   |

| Address |         |      |     | FF | 9H |   |   |   |

| Bit     | Description                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------|

| [7]     | Information Area Enable                                                                                                                   |

| INFO_EN | 0 = Information Area is not selected.                                                                                                     |

|         | 1 = Information Area is selected. The Information area is mapped into the Flash memory<br>address space at addresses FE00H through FFFFH. |

| [6:0]   | Page Select                                                                                                                               |

| PAGE    | This 7-bit field selects the Flash memory page for Programming and Page Erase operations.<br>Flash memory address[15:9] = PAGE[6:0].      |

# **Flash Sector Protect Register**

The Flash Sector Protect Register, shown in Table 87, protects Flash memory sectors from being programmed or erased from user code. The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register can be accessed only after writing the Flash Control Register with 5EH.

User code can only write bits in this register to 1 (bits cannot be cleared to 0 by user code). To determine the appropriate Flash memory sector address range and sector number for your F0822 Series product, please refer to <u>Table 82</u> on page 143.

nbedded in Life

ILO O Imbedded in Life

If breakpoints are enabled, the OCD can be configured to automatically enter DEBUG Mode, or to loop on the break instruction. If the OCD is configured to loop on the BRK instruction, then the CPU is still enabled to service DMA and interrupt requests.

The loop on a BRK instruction can be used to service interrupts in the background. For interrupts to be serviced in the background, there cannot be any breakpoints in the ISR. Otherwise, the CPU stops on the breakpoint in the interrupt routine. For interrupts to be serviced in the background, interrupts must also be enabled. Debugging software should not automatically enable interrupts when using this feature, because interrupts are typically disabled during critical sections of code where interrupts should not occur (such as adjusting the stack pointer or modifying shared data).

Software can poll the IDLE bit of the OCDSTAT Register to determine if the OCD is looping on a BRK instruction. When software wants to stop the CPU on the BRK instruction it is looping on, software should not set the DBGMODE bit of the OCDCTL Register. The CPU can have vectored to and be in the middle of an ISR when this bit gets set. Instead, software must clear the BRKLP bit. This allows the CPU to finish the ISR it is in and return the BRK instruction. When the CPU returns to the BRK instruction it was previously looping on, it automatically sets the DBGMODE bit and enter DEBUG Mode.

Software should also note that the majority of the OCD commands are still disabled when the eZ8 CPU is looping on a BRK instruction. The eZ8 CPU must be stopped and the part must be in DEBUG Mode before these commands can be issued.

#### **Breakpoints in Flash Memory**

The BRK instruction is Op Code 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a Breakpoint, write 00H to the appropriate address, overwriting the current instruction. To remove a Breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

# **OCDCNTR Register**

The OCD contains a multipurpose 16-bit counter register. It can be used for the following:

- Count system clock cycles between breakpoints

- Generate a BRK when it counts down to zero

- Generate a BRK when its value matches the Program Counter

When configured as a counter, the OCDCNTR Register starts counting when the OCD leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH. The OCDCNTR Register automatically resets itself to 0000H when the OCD exits DEBUG Mode if it is configured to count clock cycles between breakpoints.

181

С

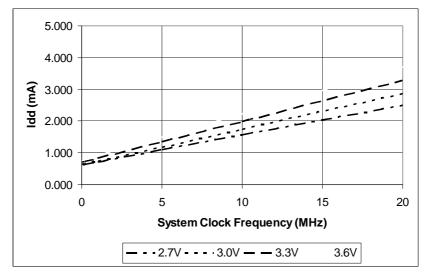

Figure 43 displays the typical current consumption in HALT Mode while operating at 25°C plotted opposite the system clock frequency. All GPIO pins are configured as outputs and driven High.

Figure 43. Typical HALT Mode  $I_{\text{DD}}$  vs. System Clock Frequency

Embedded in Life An LIXYS Company 213

| Assembly       | Symbolic                            |       | ress<br>ode | Op<br>Code(s) | Flags |   |   |   |   | _ Fetch | Instr. |        |

|----------------|-------------------------------------|-------|-------------|---------------|-------|---|---|---|---|---------|--------|--------|

| Mnemonic       | Operation                           | dst   | src         | (Hex)         | С     | Ζ | S | ۷ | D | Н       | Cycles | Cycles |

| LDX dst, src   | $dst \gets src$                     | r     | ER          | 84            | -     | - | - | - | - | -       | 3      | 2      |

|                |                                     | lr    | ER          | 85            | -     |   |   |   |   |         | 3      | 3      |

|                |                                     | R     | IRR         | 86            | -     |   |   |   |   |         | 3      | 4      |

|                |                                     | IR    | IRR         | 87            | -     |   |   |   |   |         | 3      | 5      |

|                |                                     | r     | X(rr)       | 88            | -     |   |   |   |   |         | 3      | 4      |

|                |                                     | X(rr) | r           | 89            | -     |   |   |   |   |         | 3      | 4      |

|                |                                     | ER    | r           | 94            | -     |   |   |   |   |         | 3      | 2      |

|                |                                     | ER    | Ir          | 95            | -     |   |   |   |   |         | 3      | 3      |

|                |                                     | IRR   | R           | 96            | -     |   |   |   |   |         | 3      | 4      |

|                |                                     | IRR   | IR          | 97            | -     |   |   |   |   |         | 3      | 5      |

|                |                                     | ER    | ER          | E8            | -     |   |   |   |   |         | 4      | 2      |

|                |                                     | ER    | IM          | E9            | -     |   |   |   |   |         | 4      | 2      |

| LEA dst, X(src | ) dst ← src + X                     | r     | X(r)        | 98            | -     | - | - | - | - | -       | 3      | 3      |

|                |                                     | rr    | X(rr)       | 99            | -     |   |   |   |   |         | 3      | 5      |

| MULT dst       | dst[15:0] ←<br>dst[15:8] * dst[7:0] | RR    |             | F4            | -     | - | - | - | - | -       | 2      | 8      |

| NOP            | No operation                        |       |             | 0F            | -     | - | - | - | - | -       | 1      | 2      |

| OR dst, src    | $dst \gets dst \ OR \ src$          | r     | r           | 42            | -     | * | * | 0 | - | -       | 2      | 3      |

|                |                                     | r     | Ir          | 43            | -     |   |   |   |   |         | 2      | 4      |

|                |                                     | R     | R           | 44            | -     |   |   |   |   |         | 3      | 3      |

|                |                                     | R     | IR          | 45            | -     |   |   |   |   |         | 3      | 4      |

|                |                                     | R     | IM          | 46            | -     |   |   |   |   |         | 3      | 3      |

|                |                                     | IR    | IM          | 47            | -     |   |   |   |   |         | 3      | 4      |

| ORX dst, src   | $dst \gets dst \ OR \ src$          | ER    | ER          | 48            | -     | * | * | 0 | - | -       | 4      | 3      |

|                |                                     | ER    | IM          | 49            | -     |   |   |   |   |         | 4      | 3      |

| POP dst        | dst ← @SP                           | R     |             | 50            | -     | - | - | - | - | -       | 2      | 2      |

|                | $SP \gets SP + 1$                   | IR    |             | 51            | -     |   |   |   |   |         | 2      | 3      |

## Table 127. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

# Hex Address: F0F

# Table 145. Timer 0–1 Control Registers (TxCTL)

| Bit     | 7   | 6    | 5 | 4     | 3    | 2     | 1 | 0 |  |  |  |

|---------|-----|------|---|-------|------|-------|---|---|--|--|--|

| Field   | TEN | TPOL |   | PRES  |      | TMODE |   |   |  |  |  |

| RESET   |     | 0    |   |       |      |       |   |   |  |  |  |

| R/W     |     |      |   | R/    | W    |       |   |   |  |  |  |

| Address |     |      |   | F07H, | F0FH |       |   |   |  |  |  |

# Hex Addresses: F10–F3F

This address range is reserved.

# **UART Control Registers**

For more information about the UART registers, see the <u>UART Control Register Defini-</u> tions section on page 88.

# Hex Address: F40

| Bit     | 7    | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------|-----|---|---|---|---|---|---|--|--|

| Field   |      | TXD |   |   |   |   |   |   |  |  |

| RESET   | Х    | Х   | Х | Х | Х | Х | Х | Х |  |  |

| R/W     | W    | W   | W | W | W | W | W | W |  |  |

| Address | F40H |     |   |   |   |   |   |   |  |  |

### Table 146. UART Transmit Data Register (U0TXD)

### Table 147. UART Receive Data Register (U0RXD)

| Bit     | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|---|-----|---|----|----|---|---|---|--|--|--|

| Field   |   | RXD |   |    |    |   |   |   |  |  |  |

| RESET   |   | X   |   |    |    |   |   |   |  |  |  |

| R/W     |   |     |   | F  | २  |   |   |   |  |  |  |

| Address |   |     |   | F4 | 0H |   |   |   |  |  |  |

245

# Table 195. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit        | 7             | 6                                                                                        | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|------------|---------------|------------------------------------------------------------------------------------------|---|----|----|---|---|---|--|--|--|

| Field      |               | WDTU                                                                                     |   |    |    |   |   |   |  |  |  |

| RESET      |               | 1                                                                                        |   |    |    |   |   |   |  |  |  |

| R/W        |               |                                                                                          |   | R/ | W* |   |   |   |  |  |  |

| Address    |               | FF1H                                                                                     |   |    |    |   |   |   |  |  |  |

| Note: *R/\ | N = a read re | = a read returns the current WDT count value; a write sets the appropriate reload value. |   |    |    |   |   |   |  |  |  |

# Hex Address: FF2

Hex Address: FF1

#### Table 196. Watchdog Timer Reload High Byte Register (WDTH)

| Bit        | 7             | 6                                                                                        | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|------------|---------------|------------------------------------------------------------------------------------------|---|----|----|---|---|---|--|--|--|

| Field      |               | WDTH                                                                                     |   |    |    |   |   |   |  |  |  |

| RESET      |               | 1                                                                                        |   |    |    |   |   |   |  |  |  |

| R/W        |               |                                                                                          |   | R/ | W* |   |   |   |  |  |  |

| Address    |               | FF2H                                                                                     |   |    |    |   |   |   |  |  |  |

| Note: *R/V | N = a read re | = a read returns the current WDT count value; a write sets the appropriate reload value. |   |    |    |   |   |   |  |  |  |

### Hex Address: FF3

# Table 197. Watchdog Timer Reload Low Byte Register (WDTL)

| Bit        | 7             | 6                                                                                        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|------------|---------------|------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|

| Field      |               | WDTL                                                                                     |   |   |   |   |   |   |  |  |

| RESET      |               | 1                                                                                        |   |   |   |   |   |   |  |  |

| R/W        |               | R/W*                                                                                     |   |   |   |   |   |   |  |  |

| Address    |               | FF3H                                                                                     |   |   |   |   |   |   |  |  |

| Note: *R/\ | N = a read re | = a read returns the current WDT count value; a write sets the appropriate reload value. |   |   |   |   |   |   |  |  |

# Hex Addresses: FF4–FF7

This address range is reserved.

Embedded in Life

247

#### Table 201. Flash Sector Protect Register (FPROT)

| Bit        | 7               | 6                                                                                                | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|------------|-----------------|--------------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|--|

| Field      | SECT7           | SECT7 SECT6 SECT5 SECT4 SECT3 SECT2 SECT1 SECT                                                   |   |   |   |   |   |   |  |  |  |

| RESET      |                 | 0                                                                                                |   |   |   |   |   |   |  |  |  |

| R/W        |                 | R/W*                                                                                             |   |   |   |   |   |   |  |  |  |

| Address    |                 | FF9H                                                                                             |   |   |   |   |   |   |  |  |  |

| Note: *R/V | V = this regist | = this register is accessible for read operations, but can only be written to 1 (via user code). |   |   |   |   |   |   |  |  |  |

### Hex Address: FFA

#### Table 202. Flash Frequency High Byte Register (FFREQH)

| Bit     | 7 | 6      | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|---------|---|--------|---|----|----|---|---|---|--|--|

| Field   |   | FFREQH |   |    |    |   |   |   |  |  |

| RESET   |   | 0      |   |    |    |   |   |   |  |  |

| R/W     |   |        |   | R/ | W  |   |   |   |  |  |

| Address |   |        |   | FF | AH |   |   |   |  |  |

# Hex Address: FFB

#### Table 203. Flash Frequency Low Byte Register (FFREQL)

| Bit     | 7 | 6      | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|---|--------|---|----|----|---|---|---|--|--|--|

| Field   |   | FFREQL |   |    |    |   |   |   |  |  |  |

| RESET   |   | 0      |   |    |    |   |   |   |  |  |  |

| R/W     |   | R/W    |   |    |    |   |   |   |  |  |  |

| Address |   |        |   | FF | BH |   |   |   |  |  |  |

# Hex Addresses: FFC-FFF

This address range is reserved.

250

# G

gated mode 69 general-purpose I/O 29 GPIO 4.29 alternate functions 29 architecture 29 control register definitions 31 input data sample timing 191 interrupts 31 port A-C pull-up enable sub-registers 38 port A-H address registers 32 port A-H alternate function sub-registers 34 port A-H control registers 33 port A-H data direction sub-registers 33 port A-H high drive enable sub-registers 36 port A-H input data registers 38 port A-H output control sub-registers 35 port A-H output data registers 39 port A-H stop mode recovery sub-registers 37 port availability by device 29 port input timing 191 port output timing 192

# Н

H 202 HALT 206 halt mode 27, 206 hexadecimal number prefix/suffix 202

# I

I2C 4

10-bit address read transaction 126

10-bit address transaction 123

10-bit addressed slave data transfer format 123

10-bit receive data format 126

7-bit address transaction 121

7-bit address, reading a transaction 125

7-bit addressed slave data transfer format 120, 121, 122

7-bit receive data transfer format 125

baud high and low byte registers 132, 133, 135

C status register 129, 233 control register definitions 128 controller 115 controller signals 10 interrupts 117 operation 116 SDA and SCL signals 117 stop and start conditions 119 I2CBRH register 132, 133, 135, 234 I2CBRL register 133, 234 I2CCTL register 131, 233 I2CDATA register 129, 233 I2CSTAT register 129, 233 IM 201 immediate data 201 immediate operand prefix 202 **INC 204** increment 204 increment word 204 **INCW 204** indexed 202 indirect address prefix 202 indirect register 201 indirect register pair 201 indirect working register 201 indirect working register pair 201 infrared encoder/decoder (IrDA) 97 instruction set, ez8 CPU 199 instructions ADC 204 **ADCX 204** ADD 204 **ADDX 204** AND 207 **ANDX 207** arithmetic 204 **BCLR 205 BIT 205** bit manipulation 205 block transfer 205 **BRK 207 BSET 205** BSWAP 205, 208 **BTJ 207**

253

RA 202 RR 202 rr 202 vector 202 X 202 notational shorthand 201

# 0

OCD architecture 158 autobaud detector/generator 161 baud rate limits 162 block diagram 158 breakpoints 162 commands 164 control register 169 data format 161 DBG pin to RS-232 Interface 159 debug mode 160 debugger break 207 interface 159 serial errors 162 status register 171 timing 193 OCD commands execute instruction (12H) 168 read data memory (0DH) 168 read OCD control register (05H) 166 read OCD revision (00H) 165 read OCD status register (02H) 165 read program counter (07H) 166 read program memory (0BH) 167 read program memory CRC (0EH) 168 read register (09H) 167 read runtime counter (03H) 165 step instruction (10H) 168 stuff instruction (11H) 168 write data memory (0CH) 167 write OCD control register (04H) 166 write program counter (06H) 166 write program memory (0AH) 167 write register (08H) 166 on-chip debugger 5

on-chip debugger (OCD) 158 on-chip debugger signals 12 on-chip oscillator 172 one-shot mode 68 opcode map abbreviations 218 cell description 218 first 219 second after 1FH 220 Operational Description 77 OR 207 ordering information 222 ORX 207 oscillator signals 11

# Ρ

Packaging 221 part selection guide 2 PC 202 peripheral AC and DC electrical characteristics 186 PHASE=0 timing (SPI) 105 PHASE=1 timing (SPI) 106 pin characteristics 13 polarity 201 **POP 206** pop using extended addressing 206 **POPX 206** port availability, device 29 port input timing (GPIO) 191 port output timing, GPIO 192 power supply signals 12 power-down, automatic (ADC) 137 power-on and voltage brown-out electrical characteristics and timing 186 power-on reset (POR) 22 program control instructions 207 program counter 202 program flash configurations 143 program memory 15, 143 PUSH 206 push using extended addressing 206 PUSHX 206