Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 11                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 2x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0421ph020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ilog Embedded in Life

2

0°C to +70°C standard temperature and -40°C to +105°C extended temperature operating ranges

# **Part Selection Guide**

Table 1 identifies the basic features and package styles available for each device within the Z8 Encore!  $XP^{\textcircled{B}}$  F0822 Series.

|                |               |             |     | 16-bit<br>Timers |               |                    |                  |     | Packa<br>Cou | ge Pin<br>unts |

|----------------|---------------|-------------|-----|------------------|---------------|--------------------|------------------|-----|--------------|----------------|

| Part<br>Number | Flash<br>(KB) | RAM<br>(KB) | I/O | with<br>PWM      | ADC<br>Inputs | UARTs<br>with IrDA | I <sup>2</sup> C | SPI | 20           | 28             |

| Z8F0822        | 8             | 1           | 19  | 2                | 5             | 1                  | 1                | 1   |              | Х              |

| Z8F0821        | 8             | 1           | 11  | 2                | 2             | 1                  | 1                |     | Х            |                |

| Z8F0812        | 8             | 1           | 19  | 2                | 0             | 1                  | 1                | 1   |              | Х              |

| Z8F0811        | 8             | 1           | 11  | 2                | 0             | 1                  | 1                |     | Х            |                |

| Z8F0422        | 4             | 1           | 19  | 2                | 5             | 1                  | 1                | 1   |              | Х              |

| Z8F0421        | 4             | 1           | 11  | 2                | 2             | 1                  | 1                |     | Х            |                |

| Z8F0412        | 4             | 1           | 19  | 2                | 0             | 1                  | 1                | 1   |              | Х              |

| Z8F0411        | 4             | 1           | 11  | 2                | 0             | 1                  | 1                |     | Х            |                |

## Table 1. Z8 Encore! XP<sup>®</sup> F0822 Series Part Selection Guide

nbedded in Life

15

# **Program Memory**

The eZ8 CPU supports 64KB of Program memory address space. Z8 Encore! XP<sup>®</sup> F0822 Series contain 4KB to 8KB on-chip Flash in the Program memory address space, depending on the device. Reading from Program memory addresses outside the available Flash addresses returns FFH. Writing to unimplemented Program memory addresses produces no effect. Table 5 describes the Program memory Maps for Z8 Encore! XP<sup>®</sup> F0822 Series devices.

| Program Memory Address (Hex)              | Function                    |

|-------------------------------------------|-----------------------------|

| Z8F082x and Z8F081x Products              |                             |

| 0000-0001                                 | Option Bits                 |

| 0002-0003                                 | Reset Vector                |

| 0004-0005                                 | WDT Interrupt Vector        |

| 0006-0007                                 | Illegal Instruction Trap    |

| 0008-0037                                 | Interrupt Vectors*          |

| 0038-1FFF                                 | Program Memory              |

| Z8F042x and Z8F041x Products              |                             |

| 0000-0001                                 | Option Bits                 |

| 0002-0003                                 | Reset Vector                |

| 0004-0005                                 | WDT Interrupt Vector        |

| 0006-0007                                 | Illegal Instruction Trap    |

| 0008-0037                                 | Interrupt Vectors*          |

| 0038-0FFF                                 | Program Memory              |

| Note: *See Table 24 on page 41 for a list | t of the interrupt vectors. |

## Table 5. Z8 Encore! XP<sup>®</sup> F0822 Series Program Memory Maps

# **Data Memory**

Z8 Encore! XP<sup>®</sup> F0822 Series does not use the eZ8 CPU's 64KB Data Memory address space.

# **Information Area**

Table 6 describes the Z8 Encore! XP<sup>®</sup> F0822 Series Information Area. This 512-byte Information Area is accessed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area is mapped into the Program memory and overlays the 512 bytes at addresses FE00H to FFFFH. When the Information Area access is enabled, all

#### Port A–C Pull-up Enable Subregisters

The Port A–C Pull-Up Enable Subregister, shown in Table 21, is accessed through the Port A–C Control Register by writing 06H to the Port A–C Address Register. Setting the bits in the Port A–C Pull-Up Enable subregisters enables a weak internal resistive pull-up on the specified Port pins.

| Bit         | 7         6         5         4         3         2         1         0                                                |  |  |  |  |  |  |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Field       | PPUE7 PPUE6 PPUE5 PPUE4 PPUE3 PPUE2 PPUE1 PPUE0                                                                        |  |  |  |  |  |  |  |  |  |

| RESET       | 0                                                                                                                      |  |  |  |  |  |  |  |  |  |

| R/W         | R/W                                                                                                                    |  |  |  |  |  |  |  |  |  |

| Address     | See footnote.                                                                                                          |  |  |  |  |  |  |  |  |  |

| Note: If 06 | Note: If 06H is written to the Port A–C Address Register, then it is accessible through the Port A–C Control Register. |  |  |  |  |  |  |  |  |  |

| Table 21. Po | ort A-C Pull- | Up Enable S | ubregisters |

|--------------|---------------|-------------|-------------|

|--------------|---------------|-------------|-------------|

| Bit   | Description                                       |

|-------|---------------------------------------------------|

| [7:0] | Port Pull-up Enabled                              |

| PPUEx | 0 = The weak pull-up on the port pin is disabled. |

|       | 1 = The weak pull-up on the port pin is enabled.  |

Note: x indicates register bits in the range [7:0].

# Port A–C Input Data Registers

Reading from the Port A–C Input Data registers, shown in Table 22, returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only.

| Bit     | 7 6 5 4 3 2 1 0                         |  |  |          |          |  |  |  |  |

|---------|-----------------------------------------|--|--|----------|----------|--|--|--|--|

| Field   | PIN7 PIN6 PIN5 PIN4 PIN3 PIN2 PIN1 PIN0 |  |  |          |          |  |  |  |  |

| RESET   | Х                                       |  |  |          |          |  |  |  |  |

| R/W     | R                                       |  |  |          |          |  |  |  |  |

| Address |                                         |  |  | FD2H, FD | 6H, FDAH |  |  |  |  |

| Table 22. Port A–C Input Data Registers (PxIN) |

|------------------------------------------------|

|------------------------------------------------|

| Bit   | Description                                         |

|-------|-----------------------------------------------------|

| [7:0] | Port Input Data                                     |

| PxIN  | Sampled data from the corresponding port pin input. |

|       | 0 = Input data is logical 0 (Low).                  |

|       | 1 = Input data is logical 1 (High).                 |

| Note: | x indicates register bits in the range [7:0].       |

# Embedded in Life

39

# Port A–C Output Data Register

The Port A–C Output Data Register, shown in Table 23, controls the output data to the pins.

#### Table 23. Port A–C Output Data Register (PxOUT)

| Bit     | 7                                               | 6 | 5 | 4        | 3        | 2 1 0 |  |  |  |  |  |

|---------|-------------------------------------------------|---|---|----------|----------|-------|--|--|--|--|--|

| Field   | POUT7 POUT6 POUT5 POUT4 POUT3 POUT2 POUT1 POUT0 |   |   |          |          |       |  |  |  |  |  |

| RESET   | 0                                               |   |   |          |          |       |  |  |  |  |  |

| R/W     | R/W                                             |   |   |          |          |       |  |  |  |  |  |

| Address |                                                 |   |   | FD3H, FD | 7H, FDBH |       |  |  |  |  |  |

| Bit        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]      | Port Output Data                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PxOUT      | <ul> <li>These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.</li> <li>0 = Drive a logical 0 (Low).</li> <li>1 = Drive a logical 1 (High). This High value is not driven if the drain has been disabled by setting the corresponding Port Output Control Register bit to 1.</li> </ul> |

| Note: x in | ndicates register bits in the range [7:0].                                                                                                                                                                                                                                                                                                                                                                                                  |

| Z8 Encore! XP <sup>®</sup> F0822<br>Product Speci |   | - |   |   |

|---------------------------------------------------|---|---|---|---|

|                                                   | i | l | 0 | ď |

bedded in Lif

nu IXYS Comp

42

# Architecture

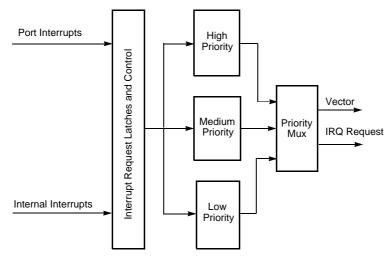

Figure 9 displays a block diagram of the interrupt controller.

Figure 9. Interrupt Controller Block Diagram

# Operation

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 42

Interrupt Vectors and Priority: see page 43

Interrupt Assertion: see page 43

Software Interrupt Assertion: see page 44

#### **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables interrupts.

Interrupts are globally enabled by any of the following actions:

- Execution of an Enable Interrupt (EI) instruction

- Execution of an Return from Interrupt (IRET) instruction

To avoid missing interrupts, use the coding style in Example 2 to clear bits in the Interrupt Request 0 Register:

**Example 2.** A good coding style that avoids lost interrupt requests:

ANDX IRQ0, MASK

#### **Software Interrupt Assertion**

Program code generates interrupts directly. Writing 1 to the appropriate bit in the Interrupt Request Register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request Register is automatically cleared to 0.

**Caution:** Zilog recommends not using a coding style to generate software interrupts by setting bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 3, which follows.

**Example 3.** A poor coding style that can result in lost interrupt requests:

```

LDX r0, IRQ0

OR r0, MASK

LDX IRQ0, r0

```

To avoid missing interrupts, use the coding style in Example 4 to set bits in the Interrupt Request registers:

**Example 4.** A good coding style that avoids lost interrupt requests:

ORX IRQ0, MASK

# Embedded in Life

53

# Interrupt Control Register

The Interrupt Control (IRQCTL) Register, shown in Table 38, contains the master enable bit for all interrupts.

#### Table 38. Interrupt Control Register (IRQCTL)

| Bit     | 7    | 6        | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------|----------|---|---|---|---|---|---|

| Field   | IRQE | Reserved |   |   |   |   |   |   |

| RESET   |      | 0        |   |   |   |   |   |   |

| R/W     | R/W  | R/W R    |   |   |   |   |   |   |

| Address |      | FCFH     |   |   |   |   |   |   |

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IRQE | <ul> <li>Interrupt Request Enable</li> <li>This bit is set to 1 by execution of an Enable Interrupts (EI) or Interrupt Return (IRET) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, Reset or by a direct register write of a 0 to this bit.</li> <li>0 = Interrupts are disabled.</li> <li>1 = Interrupts are enabled.</li> </ul> |

| [6:0]       | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                                                                                                                                                                                                                       |

# Embedded in Life An LIXYS Company 63

#### CAPTURE/COMPARE Mode

In CAPTURE/COMPARE Mode, the timer begins counting on the first external Timer Input transition. The required transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent transition of the Timer Input signal (after the first, and if appropriate) captures the current count value. The Capture value is written to the Timer PWM High and Low Byte registers. When the capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If no capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

Observe the following procedure for configuring a timer for CAPTURE/COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE Mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE Mode, the elapsed time from timer start to capture event is calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value)xPrescale}{System Clock Frequency (Hz)}$

# Universal Asynchronous Receiver/ Transmitter

The Universal Asynchronous Receiver/Transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer

- · Selectable even- and odd-parity generation and checking

- Option of one or two stop bits

- Separate transmit and receive interrupts

- Framing, parity, overrun, and break detection

- Separate transmit and receive enables

- 16-bit Baud Rate Generator

- Selectable MULTIPROCESSOR (9-Bit) Mode with three configurable interrupt schemes

- BRG timer mode

- Driver Enable output for external bus transceivers

# Architecture

The UART consists of three primary functional blocks: Transmitter, Receiver, and Baud Rate Generator. The UART's transmitter and receiver functions independently, but use the same baud rate and data format. Figure 11 displays the UART architecture.

# Embedded in Life

| Bit        | Description (Continued)                                                                                                                                                                                                                                                                                                                                       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]        | Transmitter Data Register Empty                                                                                                                                                                                                                                                                                                                               |

| TXE        | <ul> <li>This bit indicates that the UART Transmit Data Register is empty and ready for additional data.</li> <li>Writing to the UART Transmit Data Register resets this bit.</li> <li>0 = Do not write to the UART Transmit Data Register.</li> <li>1 = The UART Transmit Data Register is ready to receive an additional byte to be transmitted.</li> </ul> |

| [0]<br>CTS | <b>CTS Signal</b> When this bit is read it returns the level of the $\overline{\text{CTS}}$ signal.                                                                                                                                                                                                                                                           |

# **UART Status 1 Register**

The UART Status 1 Register, shown in Table 56, contains multiprocessor control and status bits.

#### Table 56. UART Status 1 Register (U0STAT1)

| Bit     | 7                    | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|----------------------|---|---|----|----|---|---|---|

| Field   | Reserved NEWFRM MPRX |   |   |    |    |   |   |   |

| RESET   | 0                    |   |   |    |    |   |   |   |

| R/W     | R R/W R              |   |   |    |    |   |   |   |

| Address |                      |   |   | F4 | 4H |   |   |   |

| Bit           | Description                                                                                                                                                                                                                                                                                     |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:2]         | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                                                                    |

| [1]<br>NEWFRM | <ul> <li>New Frame</li> <li>Status bit denoting the start of a new frame. Reading the UART Receive Data Register resets this bit to 0.</li> <li>0 = The current byte is not the first data byte of a new frame.</li> <li>1 = The current byte is the first data byte of a new frame.</li> </ul> |

| [0]<br>MPRX   | Multiprocessor Receive<br>Returns the value of the last multiprocessor bit received. Reading from the UART Receive<br>Data Register resets this bit to 0.                                                                                                                                       |

91

94

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2]<br>BRGCTL | <ul> <li>Baud Rate Control This bit causes different UART behavior depending on whether the UART receiver is enabled (REN = 1 in the UART Control 0 Register). When the UART receiver is not enabled, this bit determines whether the BRG will issue interrupts. 0 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value 1 = The BRG generates a receive interrupt when it counts down to zero. Reads from the Baud Rate High and Low Byte registers return the BRG count value. When the UART receiver is enabled, this bit allows reads from the Baud Rate registers to return the BRG count value instead of the reload value. 0 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value. 1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value. 1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value. 1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value. 1 = Reads from the Baud Rate High and Low Byte registers return the BRG reload value. 1 = Reads from the Baud Rate High and Low Byte registers return the bRG count value. 1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. 1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. 1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the Timers, there is no mechanism to latch the High Byte when the Low Byte is read.</li></ul> |

| [1]<br>RDAIRQ | <ul> <li>Receive Data Interrupt Enable</li> <li>0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.</li> <li>1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| [0]<br>IREN   | <ul> <li>Infrared Encoder/Decoder Enable</li> <li>0 = Infrared Encoder/Decoder is disabled. UART operates normally operation.</li> <li>1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

# **UART Address Compare Register**

The UART Address Compare Register, shown in Table 59, stores the multinode network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes will be compared to the value stored in the Address Compare Register. Receive interrupts and RDA assertions will only occur in the event of a match.

| Bit     | 7         | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-----------|-----|---|---|---|---|---|---|

| Field   | COMP_ADDR |     |   |   |   |   |   |   |

| RESET   | 0         |     |   |   |   |   |   |   |

| R/W     |           | R/W |   |   |   |   |   |   |

| Address | F45H      |     |   |   |   |   |   |   |

| Bit       | Description                                                 |

|-----------|-------------------------------------------------------------|

| [7:0]     | Compare Address                                             |

| COMP_ADDR | This 8-bit value is compared to the incoming address bytes. |

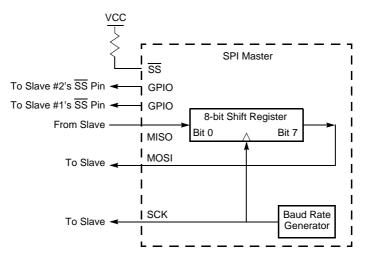

Figure 21. SPI Configured as a Master in a Single Master, Multiple Slave System

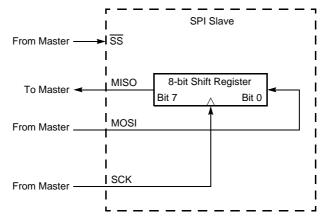

Figure 22. SPI Configured as a Slave

# Embedded in Life An TIXYS Company 107

## **Slave Operation**

The SPI block is configured for SLAVE Mode operation by setting the SPIEN bit to 1 and the MMEN bit to 0 in the SPICTL Register and setting the SSIO bit to 0 in the SPIMODE Register. The IRQE, PHASE, CLKPOL, and WOR bits in the SPICTL Register and the NUMBITS field in the SPIMODE Register must be set to be consistent with the other SPI devices. The STR bit in the SPICTL Register can be used, if appropriate, to force a *start-up* interrupt. The BIRQ bit in the SPICTL Register and the SSV bit in the SPIMODE Register is not used in SLAVE Mode. The SPI Baud Rate Generator is not used in SLAVE Mode; therefore, the SPIBRH and SPIBRL registers are not required to be initialized.

If the slave has data to send to the master, the data must be written to the SPIDAT Register before the transaction starts (first edge of SCK when  $\overline{SS}$  is asserted). If the SPIDAT Register is not written prior to the slave transaction, the MISO pin outputs whatever value is currently in the SPIDAT Register.

Due to the delay resulting from synchronization of the SPI input signals to the internal system clock, the maximum SPICLK baud rate that can be supported in SLAVE Mode is the system clock frequency ( $X_{IN}$ ) divided by 8. This rate is controlled by the SPI Master.

#### **Error Detection**

The SPI contains error detection logic to support SPI communication protocols and recognize when communication errors have occurred. The SPI Status Register indicates when a data transmission error has been detected.

#### **Overrun (Write Collision)**

An overrun error (write collision) indicates a write to the SPI Data Register was attempted while a data transfer is in progress (in either Master or Slave modes). An overrun sets the OVR bit in the SPI Status Register to 1. Writing a 1 to OVR clears this error flag. The data register is not altered when a write occurs while data transfer is in progress.

#### Mode Fault (Multimaster Collision)

A mode fault indicates when more than one Master is trying to communicate at the same time (a multimaster collision). The mode fault is detected when the enabled Master's  $\overline{SS}$  pin is asserted. A mode fault sets the COL bit in the SPI Status Register to 1. Writing a 1 to COL clears this error flag.

#### SLAVE Mode Abort

In SLAVE Mode, if the  $\overline{SS}$  pin deasserts before all bits in a character have been transferred, the transaction aborts. When this condition occurs, the ABT bit is set in the SPISTAT Register, and so is the IRQ bit (indicating that the transaction is complete). The next time  $\overline{SS}$  asserts, the MISO pin outputs SPIDAT[7], regardless of where the previous transaction left off. Writing a 1 to ABT clears this error flag.

#### ilog<sup>\*</sup> Embedded in Life An TIXYS Company 135

# I<sup>2</sup>C Diagnostic Control Register

The I<sup>2</sup>C Diagnostic Register, shown in Table 77, provides control over diagnostic modes. This register is a read/write register used for I<sup>2</sup>C diagnostics.

#### Table 77. I<sup>2</sup>C Diagnostic Control Register (I2CDIAG)

| Bit     | 7           | 6           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-------------|-------------|---|---|---|---|---|---|--|--|

| Field   |             | Reserved    |   |   |   |   |   |   |  |  |

| RESET   |             | 0           |   |   |   |   |   |   |  |  |

| R/W     | R           |             |   |   |   |   |   |   |  |  |

| Address |             | F56H        |   |   |   |   |   |   |  |  |

| Bit     | Description | Description |   |   |   |   |   |   |  |  |

| [7:1]   | Reserved    |             |   |   |   |   |   |   |  |  |

| [7.1] | These bits are reserved and must be programmed to 0000000.                                                                      |

|-------|---------------------------------------------------------------------------------------------------------------------------------|

| [0]   | Diagnostic Control Bit                                                                                                          |

| DIAG  | Selects the read-back value of the Baud Rate Reload registers.                                                                  |

|       | 0 = Normal Mode. Reading the Baud Rate High and Low Byte registers returns the baud rate<br>reload value.                       |

|       | <ol> <li>Diagnostic Mode. Reading the Baud Rate High and Low Byte registers returns the baud<br/>rate counter value.</li> </ol> |

# **Flash Control Register**

The Flash Control Register, shown in Table 84, is used to unlock the Flash Controller for programming and erase operations, or to select the Flash Sector Protect Register. The write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

| Bit     | 7    | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|------|---|---|----|----|---|---|---|

| Field   | FCMD |   |   |    |    |   |   |   |

| RESET   | 0    |   |   |    |    |   |   |   |

| R/W     | W    |   |   |    |    |   |   |   |

| Address |      |   |   | FF | 8H |   |   |   |

#### Table 84. Flash Control Register (FCTL)

| Bit      | Description                                                                    |  |

|----------|--------------------------------------------------------------------------------|--|

| [7:0]    | Flash Command*                                                                 |  |

| FCMD     | 73H = First unlock command.                                                    |  |

|          | 8CH = Second unlock command.                                                   |  |

|          | 95H = Page erase command.                                                      |  |

|          | 63H = Mass erase command.                                                      |  |

|          | 5EH = Flash Sector Protect Register select.                                    |  |

| Note: *A | All other commands, or any command out of sequence, lock the Flash Controller. |  |

llog

#### ilog<sup>°</sup> Embedded in Life An⊡IXYS Company 160

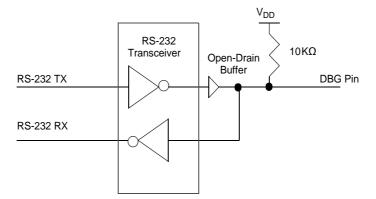

Figure 36. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #2 of 2

### **Debug Mode**

The operating characteristics of the Z8 Encore!  $XP^{\textcircled{0}}$  F0822 Series devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP Mode

- All enabled on-chip peripherals operate unless in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled

#### **Entering Debug Mode**

The device enters DEBUG Mode following any of the following operations:

- Writing the DBGMODE bit in the OCD Control Register to 1 using the OCD interface

- eZ8 CPU execution of a breakpoint (BRK) instruction

- Matching of the PC to the OCDCNTR Register (when enabled)

- The OCDCNTR Register decrements to 0000H (when enabled)

- If the DBG pin is Low when the device exits Reset, the OCD automatically places the device into DEBUG Mode

|          | Lower Nibble (Hex)      |                          |                              |                                |                            |                             |                               |                                |                               |                                |                            |                   |                           |                           |                  |                           |

|----------|-------------------------|--------------------------|------------------------------|--------------------------------|----------------------------|-----------------------------|-------------------------------|--------------------------------|-------------------------------|--------------------------------|----------------------------|-------------------|---------------------------|---------------------------|------------------|---------------------------|

|          | 0                       | 1                        | 2                            | 3                              | 4                          | 5                           | 6                             | 7                              | 8                             | 9                              | А                          | В                 | С                         | D                         | Е                | F                         |

| 0        | 1.2<br>BRK              | 2.2<br>SRP<br>IM         | 2.3<br>ADD<br>r1,r2          | 2.4<br>ADD<br>r1,lr2           | 3.3<br>ADD<br>R2,R1        | 3.4<br>ADD<br>IR2,R1        | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br>ADD<br>IR1,IM           | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br>JR<br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP                |

| 1        | 2.2<br>RLC<br>R1        | 2.3<br>RLC<br>IR1        | 2.3<br>ADC<br>r1,r2          | 2.4<br>ADC<br>r1,lr2           | 3.3<br>ADC<br>R2,R1        | 3.4<br>ADC<br>IR2,R1        | 3.3<br>ADC<br>R1,IM           | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                   |                           |                           |                  | See 2nd<br>Op Code<br>Map |

| 2        | 2.2<br>INC<br>R1        | 2.3<br>INC<br>IR1        | 2.3<br>SUB<br>r1,r2          | 2.4<br>SUB<br>r1,lr2           | 3.3<br><b>SUB</b><br>R2,R1 | 3.4<br>SUB<br>IR2,R1        | 3.3<br><b>SUB</b><br>R1,IM    | 3.4<br>SUB<br>IR1,IM           | 4.3<br><b>SUBX</b><br>ER2,ER1 | 4.3<br>SUBX<br>IM,ER1          |                            |                   |                           |                           |                  |                           |

| 3        | 2.2<br><b>DEC</b><br>R1 | 2.3<br>DEC<br>IR1        | 2.3<br>SBC<br>r1,r2          | 2.4<br>SBC<br>r1,lr2           | 3.3<br><b>SBC</b><br>R2,R1 | 3.4<br><b>SBC</b><br>IR2,R1 | 3.3<br><b>SBC</b><br>R1,IM    | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br>SBCX<br>IM,ER1          |                            |                   |                           |                           |                  |                           |

| 4        | 2.2<br><b>DA</b><br>R1  | 2.3<br><b>DA</b><br>IR1  | 2.3<br><b>OR</b><br>r1,r2    | 2.4<br><b>OR</b><br>r1,lr2     | 3.3<br><b>OR</b><br>R2,R1  | 3.4<br><b>OR</b><br>IR2,R1  | 3.3<br><b>OR</b><br>R1,IM     | 3.4<br><b>OR</b><br>IR1,IM     | 4.3<br><b>ORX</b><br>ER2,ER1  | 4.3<br><b>ORX</b><br>IM,ER1    |                            |                   |                           |                           |                  |                           |

| 5        | 2.2<br><b>POP</b><br>R1 | 2.3<br><b>POP</b><br>IR1 | 2.3<br>AND<br>r1,r2          | 2.4<br><b>AND</b><br>r1,lr2    | 3.3<br><b>AND</b><br>R2,R1 | 3.4<br><b>AND</b><br>IR2,R1 | 3.3<br><b>AND</b><br>R1,IM    | 3.4<br>AND<br>IR1,IM           | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1          |                            |                   |                           |                           |                  | 1.2<br>WDT                |

| 6        | 2.2<br>COM<br>R1        | 2.3<br>COM<br>IR1        | 2.3<br><b>TCM</b><br>r1,r2   | 2.4<br><b>TCM</b><br>r1,lr2    | 3.3<br><b>TCM</b><br>R2,R1 | 3.4<br><b>TCM</b><br>IR2,R1 | 3.3<br><b>TCM</b><br>R1,IM    | 3.4<br><b>TCM</b><br>IR1,IM    | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                   |                           |                           |                  | 1.2<br>STOP               |

| <b>7</b> | 2.2<br>PUSH<br>R2       | 2.3<br>PUSH<br>IR2       | 2.3<br><b>TM</b><br>r1,r2    | 2.4<br><b>TM</b><br>r1,lr2     | 3.3<br><b>TM</b><br>R2,R1  | 3.4<br><b>TM</b><br>IR2,R1  | 3.3<br><b>TM</b><br>R1,IM     | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                   |                           |                           |                  | 1.2<br>HALT               |

| 8        | 2.5<br>DECW<br>RR1      | 2.6<br>DECW<br>IRR1      | 2.5<br>LDE<br>r1,Irr2        | 2.9<br>LDEI<br>Ir1,Irr2        | 3.2<br>LDX<br>r1,ER2       | 3.3<br>LDX<br>lr1,ER2       | 3.4<br>LDX<br>IRR2,R1         | 3.5<br>LDX<br>IRR2,IR1         | 3.4<br><b>LDX</b><br>r1,rr2,X | 3.4<br><b>LDX</b><br>rr1,r2,X  |                            |                   |                           |                           |                  | 1.2<br>DI                 |

| 9        | 2.2<br><b>RL</b><br>R1  | 2.3<br><b>RL</b><br>IR1  | 2.5<br>LDE<br>r2,Irr1        | 2.9<br>LDEI<br>Ir2,Irr1        | 3.2<br>LDX<br>r2,ER1       | 3.3<br>LDX<br>Ir2,ER1       | 3.4<br><b>LDX</b><br>R2,IRR1  | 3.5<br>LDX<br>IR2,IRR1         | 3.3<br><b>LEA</b><br>r1,r2,X  | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                   |                           |                           |                  | 1.2<br>El                 |

| А        | 2.5<br>INCW<br>RR1      | 2.6<br>INCW<br>IRR1      | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1  | 3.4<br><b>CP</b><br>IR2,R1  | 3.3<br><b>CP</b><br>R1,IM     | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                   |                           |                           |                  | 1.4<br>RET                |

| в        | 2.2<br>CLR<br>R1        | 2.3<br>CLR<br>IR1        | 2.3<br>XOR<br>r1,r2          | 2.4<br>XOR<br>r1,lr2           | 3.3<br><b>XOR</b><br>R2,R1 | 3.4<br><b>XOR</b><br>IR2,R1 | 3.3<br><b>XOR</b><br>R1,IM    | 3.4<br><b>XOR</b><br>IR1,IM    | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br>XORX<br>IM,ER1          |                            |                   |                           |                           |                  | IRET                      |

| С        | 2.2<br><b>RRC</b><br>R1 | 2.3<br>RRC<br>IR1        | 2.5<br><b>LDC</b><br>r1,lrr2 | 2.9<br><b>LDCI</b><br>lr1,lrr2 | 2.3<br><b>JP</b><br>IRR1   | 2.9<br>LDC<br>lr1,lrr2      |                               | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           |                                |                            |                   |                           |                           |                  | 1.2<br>RCF                |

| D        | 2.2<br><b>SRA</b><br>R1 | 2.3<br><b>SRA</b><br>IR1 | 2.5<br>LDC<br>r2,Irr1        | 2.9<br><b>LDCI</b><br>lr2,lrr1 | 2.6<br>CALL<br>IRR1        | 2.2<br><b>BSWAP</b><br>R1   | DA                            | 3.4<br><b>LD</b><br>r2,r1,X    | 3.2<br><b>POPX</b><br>ER1     |                                |                            |                   |                           |                           |                  | 1.2<br>SCF                |

| Е        | 2.2<br><b>RR</b><br>R1  | 2.3<br><b>RR</b><br>IR1  | 2.2<br><b>BIT</b><br>p,b,r1  | 2.3<br><b>LD</b><br>r1,lr2     | 3.2<br><b>LD</b><br>R2,R1  | 3.3<br><b>LD</b><br>IR2,R1  | 3.2<br><b>LD</b><br>R1,IM     | 3.3<br><b>LD</b><br>IR1,IM     | 4.2<br>LDX<br>ER2,ER1         | 4.2<br>LDX<br>IM,ER1           |                            |                   |                           |                           |                  | 1.2<br>CCF                |

| F        | 2.2<br>SWAP<br>R1       | 2.3<br>SWAP<br>IR1       | 2.6<br>TRAP<br>Vector        | 2.3<br>LD<br>lr1,r2            | 2.8<br><b>MULT</b><br>RR1  | 3.3<br><b>LD</b><br>R2,IR1  | 3.3<br><b>BTJ</b><br>p,b,r1,X | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               |                                | <b>↓</b>                   | <b>V</b>          | <b>↓</b>                  | ¥                         | V                |                           |

Figure 58. First Op Code Map

Upper Nibble (Hex)

# 221

nbedded in Life

# Packaging

Zilog's Z8 Encore! XP<sup>®</sup> F0822 Series of MCUs includes the Z8F0411, Z8F0421, Z8F0811 and Z8F0821 devices, which are available in the following packages:

- 20-pin Small Shrink Outline Package (SSOP)

- 20-pin Plastic Dual-Inline Package (PDIP)

Zilog's Z8 Encore! XP<sup>®</sup> F0822 Series of MCUs also includes the Z8F0412, Z8F0422, Z8F0812 and Z8F0822 devices, which are available in the following packages:

- 28-pin Small Outline Integrated Circuit Package (SOIC)

- 28-pin Plastic Dual-Inline Package (PDIP)

Current diagrams for each of these packages are published in Zilog's <u>Packaging Product</u> <u>Specification (PS0072)</u>, which is available free for download from the Zilog website.

# Embedded in Life An TIXYS Company 241

#### Hex Addresses: FC9–FCE

This address range is reserved.

#### Hex Address: FCF

#### Table 181. Interrupt Control Register (IRQCTL)

| Bit     | 7     | 6             | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-------|---------------|---|---|---|---|---|---|--|--|

| Field   | IRQE  | IRQE Reserved |   |   |   |   |   |   |  |  |

| RESET   |       | 0             |   |   |   |   |   |   |  |  |

| R/W     | R/W R |               |   |   |   |   |   |   |  |  |

| Address |       | FCFH          |   |   |   |   |   |   |  |  |

# **GPIO Control Registers**

For more information about the GPIO control registers, see the <u>GPIO Control Register</u> <u>Definitions</u> section on page 31.

#### Hex Address: FD0

#### Table 182. Port A–C GPIO Address Registers (PxADDR)

| Bit     | 7          | 6 | 5 | 4        | 3        | 2 | 1 | 0 |  |  |

|---------|------------|---|---|----------|----------|---|---|---|--|--|

| Field   | PADDR[7:0] |   |   |          |          |   |   |   |  |  |

| RESET   | 00H        |   |   |          |          |   |   |   |  |  |

| R/W     | R/W        |   |   |          |          |   |   |   |  |  |

| Address |            |   |   | FD0H, FD | 4H, FD8H |   |   |   |  |  |

#### Hex Address: FD1

#### Table 183. Port A–C Control Registers (PxCTL)

| Bit     | 7    | 6 | 5 | 4        | 3        | 2 | 1 | 0 |  |  |

|---------|------|---|---|----------|----------|---|---|---|--|--|

| Field   | PCTL |   |   |          |          |   |   |   |  |  |

| RESET   | 00H  |   |   |          |          |   |   |   |  |  |

| R/W     | R/W  |   |   |          |          |   |   |   |  |  |

| Address |      |   |   | FD1H, FD | 5H, FD9H |   |   |   |  |  |

250

## G

gated mode 69 general-purpose I/O 29 GPIO 4.29 alternate functions 29 architecture 29 control register definitions 31 input data sample timing 191 interrupts 31 port A-C pull-up enable sub-registers 38 port A-H address registers 32 port A-H alternate function sub-registers 34 port A-H control registers 33 port A-H data direction sub-registers 33 port A-H high drive enable sub-registers 36 port A-H input data registers 38 port A-H output control sub-registers 35 port A-H output data registers 39 port A-H stop mode recovery sub-registers 37 port availability by device 29 port input timing 191 port output timing 192

# Н

H 202 HALT 206 halt mode 27, 206 hexadecimal number prefix/suffix 202

# I

I2C 4

10-bit address read transaction 126

10-bit address transaction 123

10-bit addressed slave data transfer format 123

10-bit receive data format 126

7-bit address transaction 121

7-bit address, reading a transaction 125

7-bit addressed slave data transfer format 120, 121, 122

7-bit receive data transfer format 125

baud high and low byte registers 132, 133, 135

C status register 129, 233 control register definitions 128 controller 115 controller signals 10 interrupts 117 operation 116 SDA and SCL signals 117 stop and start conditions 119 I2CBRH register 132, 133, 135, 234 I2CBRL register 133, 234 I2CCTL register 131, 233 I2CDATA register 129, 233 I2CSTAT register 129, 233 IM 201 immediate data 201 immediate operand prefix 202 **INC 204** increment 204 increment word 204 **INCW 204** indexed 202 indirect address prefix 202 indirect register 201 indirect register pair 201 indirect working register 201 indirect working register pair 201 infrared encoder/decoder (IrDA) 97 instruction set, ez8 CPU 199 instructions ADC 204 **ADCX 204** ADD 204 **ADDX 204** AND 207 **ANDX 207** arithmetic 204 **BCLR 205 BIT 205** bit manipulation 205 block transfer 205 **BRK 207 BSET 205** BSWAP 205, 208 **BTJ 207**