Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 19                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 5x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0422pj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links in the table below.

| Date        | Revision<br>Level | Description                                                                                                                                                                                                          | Page                                               |

|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Oct<br>2011 | 18                | Added LDWX information to Load Instructions table, eZ8 CPU Instruction<br>Summary table and to Second Op Code Map after 1FH figure; revised<br>Flash Sector Protect Register description; revised Packaging chapter. | <u>206, 212,</u><br><u>220, 152,</u><br><u>221</u> |

| May<br>2008 | 17                | Removed Flash Microcontrollers from the title throughout the document.                                                                                                                                               | All                                                |

| Feb<br>2008 | 16                | Updated the flag status for BCLR, BIT, and BSET in eZ8 CPU Instruction Summary table.                                                                                                                                | <u>208</u>                                         |

| Dec<br>2007 | 15                | Updated Zilog logo/text, Foreword section. Updated Z8 Encore! 8K Series to Z8 Encore! XP <sup>®</sup> F0822 Series Flash Microcontrollers throughout the document.                                                   | All                                                |

iii

Embedded in Life

n IXYS Company

# ilog Embedded in Life

2

0°C to +70°C standard temperature and -40°C to +105°C extended temperature operating ranges

# **Part Selection Guide**

Table 1 identifies the basic features and package styles available for each device within the Z8 Encore!  $XP^{\textcircled{B}}$  F0822 Series.

|                |               |             |     | 16-bit<br>Timers |               |                    |                  |     | Package Pin<br>Counts |    |

|----------------|---------------|-------------|-----|------------------|---------------|--------------------|------------------|-----|-----------------------|----|

| Part<br>Number | Flash<br>(KB) | RAM<br>(KB) | I/O | with<br>PWM      | ADC<br>Inputs | UARTs<br>with IrDA | I <sup>2</sup> C | SPI | 20                    | 28 |

| Z8F0822        | 8             | 1           | 19  | 2                | 5             | 1                  | 1                | 1   |                       | Х  |

| Z8F0821        | 8             | 1           | 11  | 2                | 2             | 1                  | 1                |     | Х                     |    |

| Z8F0812        | 8             | 1           | 19  | 2                | 0             | 1                  | 1                | 1   |                       | Х  |

| Z8F0811        | 8             | 1           | 11  | 2                | 0             | 1                  | 1                |     | Х                     |    |

| Z8F0422        | 4             | 1           | 19  | 2                | 5             | 1                  | 1                | 1   |                       | Х  |

| Z8F0421        | 4             | 1           | 11  | 2                | 2             | 1                  | 1                |     | Х                     |    |

| Z8F0412        | 4             | 1           | 19  | 2                | 0             | 1                  | 1                | 1   |                       | Х  |

| Z8F0411        | 4             | 1           | 11  | 2                | 0             | 1                  | 1                |     | Х                     |    |

## Table 1. Z8 Encore! XP<sup>®</sup> F0822 Series Part Selection Guide

# Embedded in Life

39

## Port A–C Output Data Register

The Port A–C Output Data Register, shown in Table 23, controls the output data to the pins.

### Table 23. Port A–C Output Data Register (PxOUT)

| Bit     | 7     | 6                                           | 5 | 4        | 3        | 2 | 1 | 0 |

|---------|-------|---------------------------------------------|---|----------|----------|---|---|---|

| Field   | POUT7 | 7 POUT6 POUT5 POUT4 POUT3 POUT2 POUT1 POUT0 |   |          |          |   |   |   |

| RESET   |       | 0                                           |   |          |          |   |   |   |

| R/W     |       | R/W                                         |   |          |          |   |   |   |

| Address |       |                                             |   | FD3H, FD | 7H, FDBH |   |   |   |

| Bit        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0]      | Port Output Data                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PxOUT      | <ul> <li>These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.</li> <li>0 = Drive a logical 0 (Low).</li> <li>1 = Drive a logical 1 (High). This High value is not driven if the drain has been disabled by setting the corresponding Port Output Control Register bit to 1.</li> </ul> |

| Note: x in | ndicates register bits in the range [7:0].                                                                                                                                                                                                                                                                                                                                                                                                  |

#### Table 39. Timer 0–1 High Byte Register (TxH)

| Bit     | 7 | 6   | 5 | 4     | 3    | 2 | 1 | 0 |

|---------|---|-----|---|-------|------|---|---|---|

| Field   |   | TH  |   |       |      |   |   |   |

| RESET   |   | 0   |   |       |      |   |   |   |

| R/W     |   | R/W |   |       |      |   |   |   |

| Address |   |     |   | F00H, | F08H |   |   |   |

#### Table 40. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7 | 6          | 5 | 4  | 3 | 2 | 1 | 0 |

|---------|---|------------|---|----|---|---|---|---|

| Field   |   | TL         |   |    |   |   |   |   |

| RESET   |   | 0 1        |   |    |   |   | 1 |   |

| R/W     |   |            |   | R/ | W |   |   |   |

| Address |   | F01H, F09H |   |    |   |   |   |   |

|         |   |            |   |    |   |   |   |   |

| Bit    | Description                                                                          |

|--------|--------------------------------------------------------------------------------------|

| [7:0]  | Timer High and Low Bytes                                                             |

| TH, TL | These 2 bytes, {TMRH[7:0], TMRL[7:0]}, contain the current 16-bit timer count value. |

### **Timer Reload High and Low Byte Registers**

The Timer 0–1 Reload High and Low Byte (TxRH and TxRL) registers, shown in Tables 41 and 42, store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte Register are stored in a temporary holding register. When a write to the Timer Reload Low Byte Register occurs, the temporary holding register value is written to the Timer High Byte Register. This operation allows simultaneous updates of the 16-bit Timer reload value.

In COMPARE Mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

| Bit     | 7 | 6 | 5 | 4     | 3    | 2 | 1 | 0 |

|---------|---|---|---|-------|------|---|---|---|

| Field   |   |   |   | TF    | RH   |   |   |   |

| RESET   |   | 1 |   |       |      |   |   |   |

| R/W     |   |   |   | R/    | W    |   |   |   |

| Address |   |   |   | F02H, | F0AH |   |   |   |

#### Table 41. Timer 0–1 Reload High Byte Register (TxRH)

# Embedded in Life An IXYS Company

# **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers, shown in Tables 57 and 58, configure the properties of the UART's transmit and receive operations. The UART Control registers must not been written while the UART is enabled.

#### Table 57. UART Control 0 Register (U0CTL0)

| Bit         | 7                                 | 6                                                                | 5              | 4             | 3               | 2              | 1                         | 0            |

|-------------|-----------------------------------|------------------------------------------------------------------|----------------|---------------|-----------------|----------------|---------------------------|--------------|

| Field       | TEN                               | REN                                                              | CTSE           | PEN           | PSEL            | SBRK           | STOP                      | LBEN         |

| RESET       |                                   | 0                                                                |                |               |                 |                |                           |              |

| R/W         |                                   | R/W                                                              |                |               |                 |                |                           |              |

| Address     |                                   | F42H                                                             |                |               |                 |                |                           |              |

| Bit         | Descriptio                        | n                                                                |                |               |                 |                |                           |              |

| [7]         | Transmit E                        |                                                                  |                |               |                 |                |                           |              |

| TEN         |                                   | ables or disa                                                    | bles the trar  | nsmitter. The | e enable is a   | lso controlle  | ed by the $\overline{CT}$ | S signal     |

|             | and the CT                        | SE bit. If the                                                   | CTS signal     |               |                 |                |                           | 0            |

|             |                                   | itter disable<br>itter enable                                    |                |               |                 |                |                           |              |

| [0]         | Receive Er                        |                                                                  | J.             |               |                 |                |                           |              |

| [6]<br>REN  |                                   | n <b>able</b><br>ables or disa                                   | bles the rec   | eiver         |                 |                |                           |              |

| 11211       | 0 = Receive                       |                                                                  |                |               |                 |                |                           |              |

|             | 1 = Receive                       | er enabled.                                                      |                |               |                 |                |                           |              |

| [5]         |                                   |                                                                  | <i></i>        |               |                 |                |                           |              |

| CTSE        |                                   | S signal has                                                     |                |               |                 | ntrol from the | e transmitter             |              |

| [4]         | Parity Ena                        |                                                                  |                | olgrial do al |                 |                |                           | ·            |

| PEN         |                                   | ables or disa                                                    | bles parity. I | Even or odd   | is determine    | ed by the PS   | SEL bit. This             | bit is over- |

|             | ,                                 | ne MPEN bit                                                      | •              |               |                 |                |                           |              |

|             | 0 = Parity is<br>1 = The training | s disabled.<br>nsmitter sen                                      | ds data with   | an addition   | al parity bit : | and the rece   | eiver receive             | s an addi-   |

|             |                                   | arity bit.                                                       |                |               | a party bit     |                |                           |              |

| [3]         | Parity Sele                       |                                                                  |                |               |                 |                |                           |              |

| PSEL        |                                   | arity is trans                                                   |                |               |                 |                |                           |              |

| [0]         | Send Brea                         | 1 = Odd parity is transmitted and expected on all received data. |                |               |                 |                |                           |              |

| [2]<br>SBRK |                                   | κ<br>ises or breał                                               | ks data trans  | mission by    | forcina the T   | ransmit data   | a output to 0             | . Sending a  |

|             | break interr                      | upts any tra                                                     | nsmission ir   | n progress, s | so ensure that  | at the transn  | nitter has fin            | ished send-  |

|             |                                   | fore setting                                                     |                |               |                 |                |                           |              |

|             |                                   | easserted. S                                                     |                |               | uration of the  | e break and    | the duration              | l of any     |

|             | 0 = No brea                       |                                                                  | e .onoming t   | broan         |                 |                |                           |              |

|             | 1 = The out                       | tput of the tr                                                   | ansmitter is   | zero.         |                 |                |                           |              |

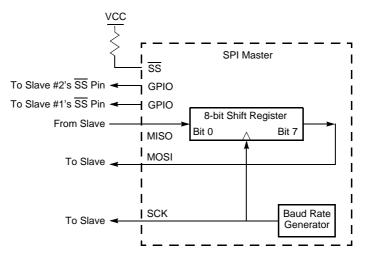

Figure 21. SPI Configured as a Master in a Single Master, Multiple Slave System

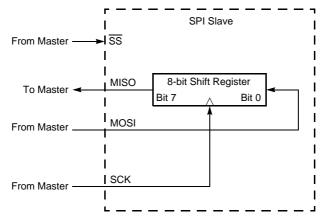

Figure 22. SPI Configured as a Slave

## Embedded in Life An TIXYS Company 108

## **SPI Interrupts**

When SPI interrupts are enabled, the SPI generates an interrupt after character transmission/reception completes in both Master and Slave modes. A character is defined to be 1 through 8 bits by the NUMBITS field in the SPI Mode Register. In SLAVE Mode it is not necessary for  $\overline{SS}$  to deassert between characters to generate the interrupt. The SPI in SLAVE Mode also generates an interrupt if the  $\overline{SS}$  signal deasserts prior to transfer of all of the bits in a character (see the previous paragraph). Writing a 1 to the IRQ bit in the SPI Status Register clears the pending SPI interrupt request. The IRQ bit must be cleared to 0 by the ISR to generate future interrupts. To start the transfer process, an SPI interrupt can be forced by software writing a 1 to the STR bit in the SPICTL Register.

If the SPI is disabled, an SPI interrupt can be generated by a BRG time-out. This timer function must be enabled by setting the BIRQ bit in the SPICTL Register. This BRG time-out does not set the IRQ bit in the SPISTAT Register, just the SPI interrupt bit in the interrupt controller.

## **SPI Baud Rate Generator**

In SPI MASTER Mode, the BRG creates a lower frequency serial clock (SCK) for data transmission synchronization between the Master and the external Slave. The input to the BRG is the system clock. The SPI Baud Rate High and Low Byte registers combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator. The SPI baud rate is calculated using the following equation:

SPI Baud Rate (bits/s) = <u>System Clock Frequency (Hz)</u> 2xBRG[15:0]

The minimum baud rate is obtained by setting BRG[15:0] to 0000H for a clock divisor value of (2 x 65536 = 131072).

When the SPI is disabled, BRG functions as a basic 16-bit timer with interrupt upon timeout. Observe the following procedure to configure BRG as a timer with interrupt upon time-out:

- 1. Disable the SPI by clearing the SPIEN bit in the SPI Control Register to 0.

- 2. Load the appropriate 16-bit count value into the SPI Baud Rate High and Low Byte registers.

- 3. Enable BRG timer function and associated interrupt by setting the BIRQ bit in the SPI Control Register to 1.

When configured as a general-purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) ×BRG[15:0]]

# Embedded in Life

## **SPI Mode Register**

The SPI Mode Register, shown in Table 67, configures the character bit width and the direction and value of the  $\overline{SS}$  pin.

#### Table 67. SPI Mode Register (SPIMODE)

| Bit     | 7    | 6     | 5    | 4  | 3           | 2  | 1    | 0   |

|---------|------|-------|------|----|-------------|----|------|-----|

| Field   | Rese | erved | DIAG | Ν  | IUMBITS[2:0 | 0] | SSIO | SSV |

| RESET   |      | 0     |      |    |             |    |      |     |

| R/W     | F    | R R/W |      |    |             |    |      |     |

| Address |      |       |      | F6 | 3H          |    |      |     |

| Bit          | Description                                                                                                                                                                                                                                                                                          |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:6]        | Reserved                                                                                                                                                                                                                                                                                             |

|              | These bits are reserved and must be programmed to 00.                                                                                                                                                                                                                                                |

| [5]          | Diagnostic Mode Control Bit                                                                                                                                                                                                                                                                          |

| DIAG         | This bit is for SPI diagnostics. Setting this bit allows the BRG value to be read using the SPIBRH and SPIBRL Register locations.                                                                                                                                                                    |

|              | 0 = Reading SPIBRH, SPIBRL returns the value in the SPIBRH and SPIBRL registers<br>1 = Reading SPIBRH returns bits [15:8] of the SPI Baud Rate Generator; and reading<br>SPIBRL returns bits [7:0] of the SPI Baud Rate Counter. The Baud Rate Counter High<br>and Low byte values are not buffered. |

|              | <b>Caution:</b> Be careful when reading these values while the BRG is counting, because the read may interfere with the operation of the BRG counter.                                                                                                                                                |

| [4:2]        | Number of Data Bits Per Character to Transfer                                                                                                                                                                                                                                                        |

| NUMBITS[2:0] | This field contains the number of bits to shift for each character transfer. See the the <u>SPI</u> <u>Data Register</u> section on page 109 for information about valid bit positions when the character length is less than 8 bits.                                                                |

|              | 000 = 8 bits.                                                                                                                                                                                                                                                                                        |

|              | 001 = 1 bit.                                                                                                                                                                                                                                                                                         |

|              | 010 = 2 bits.<br>011 = 3 bits.                                                                                                                                                                                                                                                                       |

|              | 100 = 4 bits.                                                                                                                                                                                                                                                                                        |

|              | 100 = 4 bits.<br>101 = 5 bits.                                                                                                                                                                                                                                                                       |

|              | 110 = 6 bits.                                                                                                                                                                                                                                                                                        |

|              | 111 = 7 bits.                                                                                                                                                                                                                                                                                        |

# Embedded in Life An TIXYS Company 114

## SPI Baud Rate High and Low Byte Registers

The SPI Baud Rate High and Low Byte registers, shown in Tables 69 and 70, combine to form a 16-bit reload value, BRG[15:0], for the SPI Baud Rate Generator. When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) × BRG[15:0]

| Bit     | 7   | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-----|------|---|---|---|---|---|---|--|--|

| Field   | BRH |      |   |   |   |   |   |   |  |  |

| RESET   | 1   |      |   |   |   |   |   |   |  |  |

| R/W     | R/W |      |   |   |   |   |   |   |  |  |

| Address |     | F66H |   |   |   |   |   |   |  |  |

#### Table 69. SPI Baud Rate High Byte Register (SPIBRH)

| Bit   | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| [7:0] | SPI Baud Rate High Byte                                                          |

| BRH   | Most significant byte, BRG[15:8], of the SPI Baud Rate Generator's reload value. |

#### Table 70. SPI Baud Rate Low Byte Register (SPIBRL)

| Bit     | 7   | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |

|---------|-----|---|---|----|----|---|---|---|--|

| Field   | BRL |   |   |    |    |   |   |   |  |

| RESET   | 1   |   |   |    |    |   |   |   |  |

| R/W     | R/W |   |   |    |    |   |   |   |  |

| Address |     |   |   | F6 | 7H |   |   |   |  |

| Bit   | Description                                                                      |

|-------|----------------------------------------------------------------------------------|

| [7:0] | SPI Baud Rate Low Byte                                                           |

| BRL   | Least significant byte, BRG[7:0], of the SPI Baud Rate Generator's reload value. |

loa

121

The NCKI interrupt does not occur in the not acknowledge case because the stop bit was set.

#### Write Transaction with a 7-Bit Address

Figure 27 displays the data transfer format for a 7-bit addressed slave. Shaded regions indicate data transferred from the  $I^2C$  Controller to slaves and unshaded regions indicate data transferred from the slaves to the  $I^2C$  Controller.

| Data A Data A/A P/S | А | Data | Α | W = 0 | Slave Address | S |  |

|---------------------|---|------|---|-------|---------------|---|--|

|---------------------|---|------|---|-------|---------------|---|--|

Observe the following procedure for a transmit operation to a 7-bit addressed slave:

- 1. Software asserts the IEN bit in the I<sup>2</sup>C Control Register.

- 2. Software asserts the TXI bit of the I<sup>2</sup>C Control Register to enable transmit interrupts.

- 3. The  $I^2C$  interrupt asserts, because the  $I^2C$  Data Register is empty.

- 4. Software responds to the TDRE bit by writing a 7-bit Slave address plus write bit (=0) to the I<sup>2</sup>C Data Register.

- 5. Software asserts the start bit of the  $I^2C$  Control Register.

- 6. The  $I^2C$  Controller sends the start condition to the  $I^2C$  Slave.

- The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register.

- 8. After one bit of address has been shifted out by the SDA signal, the transmit interrupt is asserted (TDRE = 1).

- 9. Software responds by writing the transmit data into the  $I^2C$  Data Register.

- 10. The I<sup>2</sup>C Controller shifts the rest of the address and write bit out by the SDA signal.

- If the I<sup>2</sup>C Slave sends an acknowledge (by pulling the SDA signal Low) during the next High period of SCL the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status Register. Continue to <u>Step 12</u>.

If the slave does not acknowledge, the Not Acknowledge interrupt occurs (NCKI bit is set in the Status Register, ACK bit is cleared). Software responds to the Not Acknowledge interrupt by setting the stop and flush bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the stop condition on the bus and clears the stop and NCKI bits. The transaction is complete; ignore the remaining steps in this sequence.

# Analog-to-Digital Converter

The Analog-to-Digital Converter (ADC) converts an analog input signal to a 10-bit binary number. The features of the sigma-delta ADC include:

- · Five analog input sources are multiplexed with GPIO ports

- Interrupt upon conversion complete

- Internal voltage reference generator

The ADC is available only in the Z8F0822, Z8F0821, Z8F0422, Z8F0421, Z8R0822, Z8R0821, Z8R0422 and Z8R0421 devices.

## Architecture

Figure 32 displays the three major functional blocks (converter, analog multiplexer and voltage reference generator) of the ADC. The ADC converts an analog input signal to its digital representation. The five-input analog multiplexer selects one of the five analog input sources. The ADC requires an input reference voltage for the conversion. The voltage reference for the conversion can be input through the external  $V_{REF}$  pin or generated internally by the voltage reference generator.

## nbedded in Life IIXYS Company 141

## ADC Data High Byte Register

The ADC Data High Byte Register, shown in Table 79, contains the upper eight bits of the 10-bit ADC output. During a SINGLE-SHOT conversion, this value is invalid. Access to the ADC Data High Byte Register is read-only. The full 10-bit ADC result is furnished by {ADCD\_H[7:0], ADCD\_L[7:6]}. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

| Bit     | 7          | 6      | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------------|--------|---|---|---|---|---|---|--|

| Field   |            | ADCD_H |   |   |   |   |   |   |  |

| RESET   |            | Х      |   |   |   |   |   |   |  |

| R/W     |            | R      |   |   |   |   |   |   |  |

| Address |            | F72H   |   |   |   |   |   |   |  |

| Bit     | Descriptio | n      |   |   |   |   |   |   |  |

| [7:0]   | ADC Data   |        |   |   |   |   |   |   |  |

#### Table 79. ADC Data High Byte Register (ADCD\_H)

ADCD\_H This byte contains the upper eight bits of the 10-bit ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the last conversion output is held in this register. These bits are undefined after a Reset.

## Page Select Register

The Page Select (FPS) Register, shown in Table 86, selects the Flash memory page to be erased or programmed. Each Flash page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory locations with the 7 most significant bits of the address provided by the PAGE field are erased to FFH.

The Page Select Register shares its Register File address with the Flash Sector Protect Register. The Page Select Register cannot be accessed when the Flash Sector Protect Register is enabled.

| Bit     | 7       | 6            | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|---------|---------|--------------|---|----|----|---|---|---|--|--|

| Field   | INFO_EN | INFO_EN PAGE |   |    |    |   |   |   |  |  |

| RESET   |         | 0            |   |    |    |   |   |   |  |  |

| R/W     |         | R/W          |   |    |    |   |   |   |  |  |

| Address |         |              |   | FF | 9H |   |   |   |  |  |

| Bit     | Description                                                                                                                               |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------|

| [7]     | Information Area Enable                                                                                                                   |

| INFO_EN | 0 = Information Area is not selected.                                                                                                     |

|         | 1 = Information Area is selected. The Information area is mapped into the Flash memory<br>address space at addresses FE00H through FFFFH. |

| [6:0]   | Page Select                                                                                                                               |

| PAGE    | This 7-bit field selects the Flash memory page for Programming and Page Erase operations.<br>Flash memory address[15:9] = PAGE[6:0].      |

## **Flash Sector Protect Register**

The Flash Sector Protect Register, shown in Table 87, protects Flash memory sectors from being programmed or erased from user code. The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register can be accessed only after writing the Flash Control Register with 5EH.

User code can only write bits in this register to 1 (bits cannot be cleared to 0 by user code). To determine the appropriate Flash memory sector address range and sector number for your F0822 Series product, please refer to <u>Table 82</u> on page 143.

nbedded in Life

157

| Bit        | Description (Continued)                                                             |  |  |  |  |  |

|------------|-------------------------------------------------------------------------------------|--|--|--|--|--|

| [1]        | Reserved                                                                            |  |  |  |  |  |

|            | This bit is reserved and must always be 1.                                          |  |  |  |  |  |

| [0]        | Flash Write Protect*                                                                |  |  |  |  |  |

| FWP        | These two option bits combine to provide three levels of Program memory protection. |  |  |  |  |  |

|            | 0 = Programming, Page Erase, and Mass Erase using User Code is disabled. Mass       |  |  |  |  |  |

|            | Erase is available through the OCD.                                                 |  |  |  |  |  |

|            | 1 = Programming and Page Erase are enabled for all of Flash program memory.         |  |  |  |  |  |

| Note: *App | plies only to the Flash versions of the F0822 Series of devices.                    |  |  |  |  |  |

# Flash Memory Address 0001H

#### Table 91. Options Bits at Flash Memory Address 0001H

| Bit       | 7                                               | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------|-------------------------------------------------|----------|---|---|---|---|---|---|--|--|

| Field     |                                                 | Reserved |   |   |   |   |   |   |  |  |

| RESET     |                                                 | U        |   |   |   |   |   |   |  |  |

| R/W       |                                                 | R/W      |   |   |   |   |   |   |  |  |

| Address   | Program Memory 0001H                            |          |   |   |   |   |   |   |  |  |

| Note: U = | Note: U = Unchanged by Reset; R/W = Read/Write. |          |   |   |   |   |   |   |  |  |

| Bit   | Description                                                                                                                               |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | <b>Reserved</b><br>These option bits are reserved and must always be 1. This setting is the default for unpro-<br>grammed (erased) Flash. |

#### ilog Embedded in Life An TIXYS Company 159

# Operation

The following section describes the operation of the OCD.

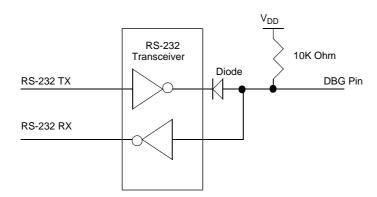

## **OCD** Interface

The OCD uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional open-drain interface that transmits and receives data. Data transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin can interface the Z8 Encore! XP<sup>®</sup> F0822 Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are shown in Figures 35 and 36.

**Caution:** For operation of the OCD, all power pins (V<sub>DD</sub> and AV<sub>DD</sub>) must be supplied with power, and all ground pins (V<sub>SS</sub> and AV<sub>SS</sub>) must be properly grounded. The DBG pin is opendrain and must always be connected to V<sub>DD</sub> through an external pull-up resistor to ensure proper operation.

Figure 35. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #1 of 2

#### TILOG Embedded in Life IXYS Company 166

or generate a BRK when its value matches the Program Counter. Because this register is really a down counter, the returned value is inverted when this register is read so the returned result appears to be an up counter. If the device is not in DEBUG Mode, this command returns FFFFH.

```

DBG \leftarrow 03H

DBG \rightarrow ~OCDCNTR[15:8]

DBG \rightarrow ~OCDCNTR[7:0]

```

Write OCD Control Register (04H). The Write OCD Control Register command writes the data that follows to the OCDCTL Register. When the Read Protect option bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of putting the device back into normal operating mode is to reset the device.

```

DBG \leftarrow 04H

DBG \leftarrow OCDCTL[7:0]

```

**Read OCD Control Register (05H).** The Read OCD Control Register command reads the value of the OCDCTL Register.

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

Write Program Counter (06H). The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter. If the device is not in DEBUG Mode or if the Read Protect option bit is enabled, the Program Counter values are discarded.

**Read Program Counter (07H).** The Read Program Counter command reads the value in the eZ8 CPU's Program Counter. If the device is not in DEBUG Mode or if the Read Protect option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

**Write Register (08H).** The Write Register command writes data to the Register File. Data can be written 1-256 bytes at a time (256 bytes can be written by setting size to zero). If the device is not in DEBUG Mode, the address and data values are discarded. If the Read Protect option bit is enabled, then only writes to the Flash Control registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

DBG  $\leftarrow$  Size[7:0] DBG  $\leftarrow$  1-65536 data bytes

**Read Data Memory (0DH).** The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1-65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG Mode, this command returns FFH for the data.

$\begin{array}{rcl} \text{DBG} &\leftarrow & \text{ODH} \\ \text{DBG} &\leftarrow & \text{Data} & \text{Memory Address[15:8]} \\ \text{DBG} &\leftarrow & \text{Data} & \text{Memory Address[7:0]} \\ \text{DBG} &\leftarrow & \text{Size[15:8]} \\ \text{DBG} &\leftarrow & \text{Size[7:0]} \\ \text{DBG} &\rightarrow & 1-65536 & \text{data} & \text{bytes} \end{array}$

**Read Program Memory CRC (0EH).** The Read Program Memory CRC command computes and returns the CRC (cyclic redundancy check) of Program memory using the 16-bit CRC-CCITT polynomial. If the device is not in DEBUG Mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program memory, calculates the CRC value, and returns the result. The delay is a function of the Program memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program memory.

```

DBG \leftarrow 0EH

DBG \rightarrow CRC[15:8]

DBG \rightarrow CRC[7:0]

```

**Step Instruction (10H).** The Step Instruction command steps one assembly instruction at the current Program Counter location. If the device is not in DEBUG Mode or the Read Protect option bit is enabled, the OCD ignores this command.

DBG  $\leftarrow$  10H

**Stuff Instruction (11H).** The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG Mode or the Read Protect option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

**Execute Instruction (12H).** The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over breakpoints. The number of bytes to send for the instruction depends on the Op Code. If the device is not in DEBUG Mode or the Read Protect option bit is enabled, the OCD ignores this command.

208

| dst | D:4 0                                  |

|-----|----------------------------------------|

|     | Bit Swap                               |

| dst | Rotate Left                            |

| dst | Rotate Left through Carry              |

| dst | Rotate Right                           |

| dst | Rotate Right through Carry             |

| dst | Shift Right Arithmetic                 |

| dst | Shift Right Logical                    |

| dst | Swap Nibbles                           |

|     | dst<br>dst<br>dst<br>dst<br>dst<br>dst |

#### Table 126. Rotate and Shift Instructions

# eZ8 CPU Instruction Summary

Table 127 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags Register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction.

| Assembly      | Symbolic                  | Address<br>Mode |     | Op<br>₋ Code(s) | Flags |   |   |   |   |   | Fetch  | Instr. |

|---------------|---------------------------|-----------------|-----|-----------------|-------|---|---|---|---|---|--------|--------|

| Mnemonic      | Operation                 | dst             | src | (Hex)           | С     | Ζ | S | ۷ | D | н | Cycles | Cycles |

| ADC dst, src  | $dst \gets dst + src + C$ | r               | r   | 12              | *     | * | * | * | 0 | * | 2      | 3      |

|               |                           | r               | lr  | 13              | -     |   |   |   |   |   | 2      | 4      |

|               |                           | R               | R   | 14              | -     |   |   |   |   |   | 3      | 3      |

|               |                           | R               | IR  | 15              | -     |   |   |   |   |   | 3      | 4      |

|               |                           | R               | IM  | 16              | -     |   |   |   |   |   | 3      | 3      |

|               |                           | IR              | IM  | 17              | -     |   |   |   |   |   | 3      | 4      |

| ADCX dst, src | $dst \gets dst + src + C$ | ER              | ER  | 18              | *     | * | * | * | 0 | * | 4      | 3      |

|               |                           | ER              | IM  | 19              | -     |   |   |   |   |   | 4      | 3      |

#### Table 127. eZ8 CPU Instruction Summary

Note: Flags Notation:

\* = Value is a function of the result of the operation.

– = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

### Hex Address: FD6

#### Table 188. Port A–C Input Data Registers (PxIN)

| Bit     | 7    | 6                | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |  |

|---------|------|------------------|------|------|------|------|------|------|--|--|--|--|

| Field   | PIN7 | PIN6             | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |  |  |  |

| RESET   | X    |                  |      |      |      |      |      |      |  |  |  |  |

| R/W     |      | R                |      |      |      |      |      |      |  |  |  |  |

| Address |      | FD2H, FD6H, FDAH |      |      |      |      |      |      |  |  |  |  |

#### Hex Address: FD7

#### Table 189. Port A–C Output Data Register (PxOUT)

| Bit     | 7     | 6     | 5     | 4        | 3        | 2     | 1     | 0     |  |  |  |

|---------|-------|-------|-------|----------|----------|-------|-------|-------|--|--|--|

| Field   | POUT7 | POUT6 | POUT5 | POUT4    | POUT3    | POUT2 | POUT1 | POUT0 |  |  |  |

| RESET   | 0     |       |       |          |          |       |       |       |  |  |  |

| R/W     | R/W   |       |       |          |          |       |       |       |  |  |  |

| Address |       |       |       | FD3H, FD | 7H, FDBH |       |       |       |  |  |  |

#### Hex Address: FD8

#### Table 190. Port A–C GPIO Address Registers (PxADDR)

| Bit     | 7          | 6   | 5 | 4        | 3        | 2 | 1 | 0 |  |  |  |  |

|---------|------------|-----|---|----------|----------|---|---|---|--|--|--|--|

| Field   | PADDR[7:0] |     |   |          |          |   |   |   |  |  |  |  |

| RESET   | 00H        |     |   |          |          |   |   |   |  |  |  |  |

| R/W     |            | R/W |   |          |          |   |   |   |  |  |  |  |

| Address |            |     |   | FD0H, FD | 4H, FD8H |   |   |   |  |  |  |  |

#### Hex Address: FD9

#### Table 191. Port A–C Control Registers (PxCTL)

| Bit     | 7    | 6 | 5 | 4        | 3                | 2 | 1 | 0 |  |  |  |  |  |  |  |

|---------|------|---|---|----------|------------------|---|---|---|--|--|--|--|--|--|--|

| Field   | PCTL |   |   |          |                  |   |   |   |  |  |  |  |  |  |  |

| RESET   | 00H  |   |   |          |                  |   |   |   |  |  |  |  |  |  |  |

| R/W     | R/W  |   |   |          |                  |   |   |   |  |  |  |  |  |  |  |

| Address |      |   |   | FD1H, FD | FD1H, FD5H, FD9H |   |   |   |  |  |  |  |  |  |  |

rotate right through carry 208 RP 202 RR 202, 208 rr 202 RRC 208

## S

**SBC 205** SCF 205, 206 **SCK 103** SDA and SCL (IrDA) signals 117 second opcode map after 1FH 220 serial clock 104 serial peripheral interface (SPI) 101 set carry flag 205, 206 set register pointer 206 shift right arithmetic 208 shift right logical 208 signal descriptions 10 single-shot conversion (ADC) 137 SIO 5 slave data transfer formats (I2C) 123 slave select 104 software trap 207 source operand 202 SP 202 SPI architecture 101 baud rate generator 108 baud rate high and low byte register 114 clock phase 104 configured as slave 102 control register 110 control register definitions 109 data register 109 error detection 107 interrupts 108 mode fault error 107 mode register 112 multi-master operation 106 operation 103 overrun error 107 signals 103

single master, multiple slave system 102 single master, single slave system 101 status register 111 timing, PHASE = 0.105timing, PHASE=1 106 SPI controller signals 10 SPI mode (SPIMODE) 112, 236 SPIBRH register 114, 236 SPIBRL register 114, 237 SPICTL register 110, 235 SPIDATA register 109, 235 SPIMODE register 112, 236 SPISTAT register 111, 235 **SRA 208** src 202 **SRL 208 SRP 206** SS, SPI signal 103 stack pointer 202 status register, I2C 129 **STOP 206** stop mode 27, 206 stop mode recovery sources 25 using a GPIO port pin transition 26 using watch-dog timer time-out 26 **SUB 205** subtract 205 subtract - extended addressing 205 subtract with carry 205 subtract with carry - extended addressing 205 SUBX 205 **SWAP 208** swap nibbles 208 symbols, additional 202 system and core resets 21

## Т

TCM 205 TCMX 205 test complement under mask 205 test complement under mask - extended addressing 205