Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 19                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 5x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | · .                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0422sj020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 70.  | SPI Baud Rate Low Byte Register (SPIBRL) 114                             |

|------------|--------------------------------------------------------------------------|

| Table 71.  | I <sup>2</sup> C Data Register (I2CDATA) 129                             |

| Table 72.  | I <sup>2</sup> C Status Register (I2CSTAT) 129                           |

| Table 73.  | l <sup>2</sup> C Control Register (I2CCTL) 131                           |

| Table 74.  | 1 <sup>2</sup> C Baud Rate High Byte Register (I2CBRH)                   |

| Table 75.  | I <sup>2</sup> C Baud Rate Low Byte Register (I2CBRL)                    |

| Table 76.  | I <sup>2</sup> C Diagnostic State Register (I2CDST) 133                  |

| Table 77.  | I <sup>2</sup> C Diagnostic Control Register (I2CDIAG)                   |

| Table 78.  | ADC Control Register (ADCCTL)                                            |

| Table 79.  | ADC Data High Byte Register (ADCD_H) 141                                 |

| Table 80.  | ADC Data Low Bits Register (ADCD_L) 142                                  |

| Table 81.  | Flash Memory Configurations 143                                          |

| Table 82.  | Flash Memory Sector Addresses 143                                        |

| Table 83.  | Z8 Encore! XP <sup>®</sup> F0822 Series Information Area Map 145         |

| Table 84.  | Flash Control Register (FCTL) 150                                        |

| Table 85.  | Flash Status Register (FSTAT) 151                                        |

| Table 86.  | Page Select Register (FPS) 152                                           |

| Table 87.  | Flash Sector Protect Register (FPROT) 153                                |

| Table 88.  | Flash Frequency High Byte Register (FFREQH) 154                          |

| Table 89.  | Flash Frequency Low Byte Register (FFREQL) 154                           |

| Table 90.  | Option Bits at Flash Memory Address 0000H for 8K Series Flash<br>Devices |

| Table 91.  | Options Bits at Flash Memory Address 0001H                               |

| Table 92.  | OCD Baud-Rate Limits                                                     |

| Table 93.  | On-Chip Debugger Commands                                                |

| Table 94.  | OCD Control Register (OCDCTL)                                            |

| Table 95.  | OCD Status Register (OCDSTAT)                                            |

| Table 96.  | Recommended Crystal Oscillator Specifications (20MHz Operation) 173      |

| Table 97.  | Absolute Maximum Ratings                                                 |

| Table 98.  | DC Characteristics                                                       |

| Table 99.  | AC Characteristics                                                       |

| Table 100. | Power-On Reset and Voltage Brown-Out Electrical Characteristics          |

|            | and Timing                                                               |

| Table 101. | External RC Oscillator Electrical Characteristics and Timing             |

| Table 102. | Flash Memory Electrical Characteristics and Timing 187                   |

| Table 103. | Reset and Stop Mode Recovery Pin Timing 188                              |

ilog Embedded in Life An DIXYS Company 41

| Priority | Program Memory<br>Vector Address | Interrupt Source                                |

|----------|----------------------------------|-------------------------------------------------|

| Highest  | 0002H                            | Reset (not an interrupt)                        |

|          | 0004H                            | WDT (see the Watchdog Timer chapter on page 70) |

|          | 0006H                            | Illegal Instruction Trap (not an interrupt)     |

|          | 0008H                            | Reserved                                        |

|          | 000AH                            | Timer 1                                         |

|          | 000CH                            | Timer 0                                         |

|          | 000EH                            | UART 0 receiver                                 |

|          | 0010H                            | UART 0 transmitter                              |

|          | 0012H                            | l <sup>2</sup> C                                |

|          | 0014H                            | SPI                                             |

|          | 0016H                            | ADC                                             |

|          | 0018H                            | Port A7, rising or falling input edge           |

|          | 001AH                            | Port A6, rising or falling input edge           |

|          | 001CH                            | Port A5, rising or falling input edge           |

|          | 001EH                            | Port A4, rising or falling input edge           |

|          | 0020H                            | Port A3, rising or falling input edge           |

|          | 0022H                            | Port A2, rising or falling input edge           |

|          | 0024H                            | Port A1, rising or falling input edge           |

|          | 0026H                            | Port A0, rising or falling input edge           |

|          | 0028H                            | Reserved                                        |

|          | 002AH                            | Reserved                                        |

|          | 002CH                            | Reserved                                        |

|          | 002EH                            | Reserved                                        |

|          | 0030H                            | Port C3, both input edges                       |

|          | 0032H                            | Port C2, both input edges                       |

|          | 0034H                            | Port C1, both input edges                       |

| Lowest   | 0036H                            | Port C0, both input edges                       |

### Table 24. Interrupt Vectors in Order of Priority

• Writing a 1 to the IRQE bit in the Interrupt Control Register

Interrupts are globally disabled by any of the following actions:

- Execution of a Disable Interrupt (DI) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control Register

- Reset

- Execution of a trap instruction

- Illegal instruction trap

### **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority, and Level 1 is the lowest priority. If all of the interrupts were enabled with identical interrupt priority (all as Level 2 interrupts), then interrupt priority would be assigned from highest to lowest as specified in <u>Table 24</u>. Level 3 interrupts always have higher priority than Level 2 interrupts which in turn always have higher priority than Level 1 interrupt priority level (Level 1, Level 2, or Level 3), priority is assigned as specified in <u>Table 24</u>. A Reset, WDT interrupt (if enabled), and an Illegal Instruction Trap will always have the highest priority.

### **Interrupt Assertion**

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Request Register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request Register likewise clears the interrupt request.

**Caution:** Zilog recommends not using a coding style that clears bits in the Interrupt Request registers. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost. See Example 1, which follows.

**Example 1.** A poor coding style that can result in lost interrupt requests:

LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control Register is set to 1, the Timer Output signal begins as a High (1) and then transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the reload value and is reset to 0001H.

If the TPOL bit in the Timer Control Register is set to 0, the Timer Output signal begins as a Low (0) and then transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the reload value and is reset to 0001H.

Observe the following procedure for configuring a timer for PWM Mode and initiating the PWM operation:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for PWM Mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM Mode. After the first timer reset in PWM Mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the reload value (PWM period). The reload value must be greater than the PWM value.

- 5. If required, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

The PWM period is calculated using the following equation.

PWM Period (s) = <u>Reload ValuexPrescale</u> System Clock Frequency (Hz)

69

| Bit                      | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [6]<br>TPOL<br>(cont'd.) | <ul> <li>GATED Mode</li> <li>0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.</li> <li>1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.</li> </ul>                                                                                                                |

|                          | <ul> <li>CAPTURE/COMPARE Mode</li> <li>0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.</li> <li>1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.</li> </ul>                              |

| [5:3]<br>PRES            | Prescale Value<br>The timer input clock is divided by 2 <sup>PRES</sup> , where PRES is set from 0 to 7. The prescaler is reset<br>each time the timer is disabled to ensure proper clock division each time the timer is restarted.<br>000 = Divide by 1.<br>001 = Divide by 2.<br>010 = Divide by 4.<br>011 = Divide by 8.<br>100 = Divide by 16.<br>101 = Divide by 32.<br>110 = Divide by 64.<br>111 = Divide by 128. |

| [2:0]<br>TMODE           | Timer Mode<br>000 = ONE-SHOT Mode.<br>001 = CONTINUOUS Mode.<br>010 = COUNTER Mode.<br>011 = PWM Mode.<br>100 = CAPTURE Mode.<br>101 = COMPARE Mode.<br>110 = GATED Mode.<br>111 = CAPTURE/COMPARE Mode.                                                                                                                                                                                                                  |

| WDT Reload<br>Value | WDT Reload<br>Value |         | te Time-Out Delay<br>WDT Oscillator Frequency) |

|---------------------|---------------------|---------|------------------------------------------------|

| (Hex)               | (Decimal)           | Typical | Description                                    |

| 000004              | 4                   | 400µs   | Minimum time-out delay                         |

| FFFFF               | 16,777,215          | 1677.5s | Maximum time-out delay                         |

#### Table 47. Watchdog Timer Approximate Time-Out Delays

### Watchdog Timer Refresh

When first enabled, the WDT is loaded with the value in the WDT Reload registers. The WDT then counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the downcounter to be reloaded with the WDT reload value stored in the WDT Reload registers. Counting resumes following the reload operation.

When Z8 Encore! XP<sup>®</sup> F0822 Series device is operating in DEBUG Mode (using the OCD), the WDT is continuously refreshed to prevent spurious WDT time-outs.

### Watchdog Timer Time-Out Response

The WDT times out when the counter reaches 000000H. A WDT time-out generates either an Interrupt or a Reset. The WDT\_RES option bit determines the time-out response of the WDT. For information regarding programming of the WDT\_RES option bit, see the <u>Option Bits</u> chapter on page 155.

### **WDT Interrupt in Normal Operation**

If configured to generate an interrupt when a time-out occurs, the WDT issues an interrupt request to the interrupt controller and sets the WDT status bit in the WDT Control Register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the WDT interrupt vector and executing the code from the vector address. After time-out and interrupt generation, the WDT counter rolls over to its maximum value of FFFFFH and continues counting. The WDT counter is not automatically returned to its reload value.

#### WDT Reset in STOP Mode

If enabled in STOP Mode and configured to generate a Reset when a time-out occurs and the device is in STOP Mode, the WDT initiates a Stop Mode Recovery. Both the WDT status bit and the stop bit in the WDT Control Register is set to 1 following the WDT time-out in STOP Mode. For more information, see the <u>Reset and Stop Mode Recovery</u> chapter on page 21. Default operation is for the WDT and its RC oscillator to be enabled during STOP Mode.

#### ilog<sup>\*</sup> Embedded in Life An TXYS Company 79

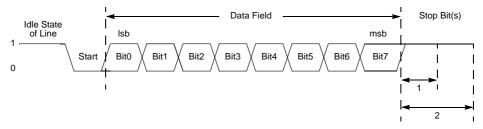

Figure 12. UART Asynchronous Data Format without Parity

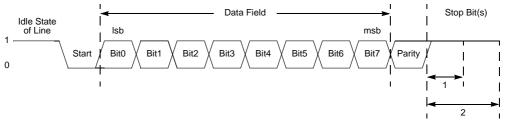

Figure 13. UART Asynchronous Data Format with Parity

# **Transmitting Data using Polled Method**

Observe the following procedure to transmit data using polled method of operation:

- 1. Write to the UART Baud Rate High Byte and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. If MULTIPROCESSOR Mode is required, write to the UART Control 1 Register to enable multiprocessor (9-bit) mode functions.

- Set the Multiprocessor Mode Select (MPEN) to enable MULTIPROCESSOR Mode.

- 4. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- If parity is required, and MULTIPROCESSOR Mode is not enabled, set the parity enable bit (PEN) and select either even or odd parity (PSEL).

The UART is now configured for interrupt-driven data reception. When the UART Receiver Interrupt is detected, the associated ISR performs the following operations:

- 1. Check the UART Status 0 Register to determine the source of the interrupt, whether error, break or received data.

- 2. If the interrupt was due to data available, read the data from the UART Receive Data Register. If operating in MULTIPROCESSOR (9-Bit) Mode, further actions may be required depending on the Multiprocessor Mode bits MPMD[1:0].

- 3. Clear the UART Receiver Interrupt in the applicable Interrupt Request Register.

- 4. Execute the IRET instruction to return from the ISR and await more data.

### **Clear To Send Operation**

The CTS pin, if enabled by the CTSE bit of the UART Control 0 Register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this would be done during stop bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

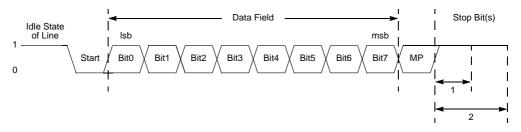

### Multiprocessor (9-Bit) Mode

The UART features a MULTIPROCESSOR (9-Bit) Mode that uses an extra (9th) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR Mode (also referred to as 9-bit mode), the multiprocessor bit is transmitted following the 8 bits of data and immediately preceding the stop bit(s); this character format is shown in Figure 14.

Figure 14. UART Asynchronous Multiprocessor Mode Data Format

83

00

- 12. The I<sup>2</sup>C Controller loads the contents of the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register.

- 13. The I<sup>2</sup>C Controller shifts the data out of using the SDA signal. After the first bit is sent, the transmit interrupt is asserted.

- 14. If more bytes remain to be sent, return to Step 9.

- 15. Software responds by setting the stop bit of the I<sup>2</sup>C Control Register (or start bit to initiate a new transaction). In the STOP case, software clears the TXI bit of the I<sup>2</sup>C Control Register at the same time.

- 16. The I<sup>2</sup>C Controller completes transmission of the data on the SDA signal.

- 17. The slave can either Acknowledge or Not Acknowledge the last byte. Because either the stop or start bit is already set, the NCKI interrupt does not occur.

- 18. The I<sup>2</sup>C Controller sends the stop (or restart) condition to the I<sup>2</sup>C bus. The stop or start bit is cleared.

# Address-Only Transaction with a 10-Bit Address

In situations in which software must determine if a slave with a 10-bit address is responding without sending or receiving data, a transaction is performed which only consists of an address phase. Figure 28 displays this *address only* transaction to determine if a slave with a 10-bit address will acknowledge.

As an example, this transaction is used after a write has been executed to an EEPROM to determine when the EEPROM completes its internal write operation and is again responding to  $I^2C$  transactions. If the slave does not acknowledge, the transaction is repeated until the slave is able to acknowledge.

| S | Slave Address<br>1st Seven Bits | W = 0 | A/A | Slave Address<br>2nd Byte | A/A |

|---|---------------------------------|-------|-----|---------------------------|-----|

|---|---------------------------------|-------|-----|---------------------------|-----|

Figure 28. 10-Bit Address Only Transaction Format

Observe the following procedure for an address-only transaction to a 10-bit addressed slave:

- 1. Software asserts the IEN bit in the  $I^2C$  Control Register.

- 2. Software asserts the TXI bit of the  $I^2C$  Control Register to enable transmit interrupts.

- 3. The I<sup>2</sup>C interrupt asserts, because the I<sup>2</sup>C Data Register is empty (TDRE = 1).

- 4. Software responds to the TDRE interrupt by writing the first slave address byte. The least-significant bit must be 0 for the write operation.

- 5. Software asserts the start bit of the  $I^2C$  Control Register.

Iloa

126

- 5. The  $I^2C$  Controller shifts the address and read bit out the SDA signal.

- If the I<sup>2</sup>C Slave acknowledges the address by pulling the SDA signal Low during the next High period of SCL, the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status Register. Continue to <u>Step 7</u>.

If the slave does not acknowledge, the Not Acknowledge interrupt occurs (NCKI bit is set in the Status Register, ACK bit is cleared). Software responds to the Not Acknowledge interrupt by setting the stop bit and clearing the TXI bit. The  $I^2C$  Controller sends the stop condition on the bus and clears the stop and NCKI bits. The transaction is complete; ignore the remainder of this sequence.

- The I<sup>2</sup>C Controller shifts in the byte of data from the I<sup>2</sup>C Slave on the SDA signal. The I<sup>2</sup>C Controller sends a Not Acknowledge to the I<sup>2</sup>C Slave if the NAK bit is set (last byte), else it sends an Acknowledge.

- 8. The I<sup>2</sup>C Controller asserts the Receive interrupt (RDRF bit set in the Status Register).

- 9. Software responds by reading the I<sup>2</sup>C Data Register which clears the RDRF bit. If there is only one more byte to receive, set the NAK bit of the I<sup>2</sup>C Control Register.

- 10. If there are more bytes to transfer, return to Step 7.

- 11. After the last byte is shifted in, a Not Acknowledge interrupt is generated by the I<sup>2</sup>C Controller.

- 12. Software responds by setting the stop bit of the I<sup>2</sup>C Control Register.

- 13. A stop condition is sent to the I<sup>2</sup>C Slave, the stop and NCKI bits are cleared.

### **Read Transaction with a 10-Bit Address**

Figure 31 displays the read transaction format for a 10-bit addressed slave. The shaded regions indicate data transferred from the  $I^2C$  Controller to slaves and unshaded regions indicate data transferred from the slaves to the  $I^2C$  Controller.

| S | Slave Address | W=0 | А | Slave Address | А | S | Slave Address | R=1 | А | Data | А | Data | А | Ρ |

|---|---------------|-----|---|---------------|---|---|---------------|-----|---|------|---|------|---|---|

|   | 1st 7 bits    |     |   | 2nd Byte      |   |   | 1st 7 bits    |     |   |      |   |      |   |   |

#### Figure 31. Receive Data Format for a 10-Bit Addressed Slave

The first seven bits transmitted in the first byte are 11110XX. The two XX bits are the two most significant bits of the 10-bit address. The lowest bit of the first byte transferred is the write control bit.

Observe the following procedure for the data transfer procedure for a read operation to a 10-bit addressed slave:

129

# I<sup>2</sup>C Data Register

The I<sup>2</sup>C Data Register, shown in Table 71, holds the data that is to be loaded into the I<sup>2</sup>C Shift Register during a write to a slave. This register also holds data that is loaded from the I<sup>2</sup>C Shift Register during a read from a slave. The I<sup>2</sup>C Shift Register is not accessible in the Register File address space, but is used only to buffer incoming and outgoing data.

| Table 71. I <sup>2</sup> | Data Register | (I2CDATA) |

|--------------------------|---------------|-----------|

|--------------------------|---------------|-----------|

| Bit     | 7   | 6    | 5 | 4  | 3  | 2 | 1 | 0 |  |

|---------|-----|------|---|----|----|---|---|---|--|

| Field   |     | DATA |   |    |    |   |   |   |  |

| RESET   | 0   |      |   |    |    |   |   |   |  |

| R/W     | R/W |      |   |    |    |   |   |   |  |

| Address |     |      |   | F5 | 0H |   |   |   |  |

# I<sup>2</sup>C Status Register

The read-only I<sup>2</sup>C Status Register, shown in Table 72, indicates the status of the I<sup>2</sup>C Controller.

Table 72. I<sup>2</sup>C Status Register (I2CSTAT)

| Bit     | 7    | 6    | 5   | 4   | 3  | 2   | 1   | 0    |  |  |

|---------|------|------|-----|-----|----|-----|-----|------|--|--|

| Field   | TDRE | RDRF | ACK | 10B | RD | TAS | DSS | NCKI |  |  |

| RESET   | 1    |      | 0   |     |    |     |     |      |  |  |

| R/W     |      | R    |     |     |    |     |     |      |  |  |

| Address |      | F51H |     |     |    |     |     |      |  |  |

#### Bit Description

| [7] | Transmit Data Register Empty |

|-----|------------------------------|

|     |                              |

TDRE When the I<sup>2</sup>C Controller is enabled, this bit is 1 when the I<sup>2</sup>C Data Register is empty. When this bit is set, an interrupt is generated if the TXI bit is set, except when the I<sup>2</sup>C Controller is shifting in data during the reception of a byte or when shifting an address and the RD bit is set. This bit is cleared by writing to the I2CDATA Register.

# [6] Receive Data Register Full RDRF This bit is set = 1 when the I<sup>2</sup>C Controller is enabled and the I<sup>2</sup>C Controller has received a byte of data. When asserted, this bit causes the I<sup>2</sup>C Controller to generate an interrupt. This bit is

of data. When asserted, this bit causes the I<sup>2</sup>C Controller to generate an interrupt. This bit is cleared by reading the I<sup>2</sup>C Data Register (unless the read is performed using execution of the OCD's Read Register command).

# Embedded in Life An UXYS Company 132

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]<br>FLUSH  | <b>Flush Data</b><br>Setting this bit to 1 clears the $I^2C$ Data Register and sets the TDRE bit to 1. This bit allows flushing of the $I^2C$ Data Register when a Not Acknowledge interrupt is received after the data has been sent to the $I^2C$ Data Register. Reading this bit always returns 0.                                                                                          |

| [0]<br>FILTEN | <ul> <li>I<sup>2</sup>C Signal Filter Enable</li> <li>This bit enables low-pass digital filters on the SDA and SCL input signals. These filters reject any input pulse with periods less than a full system clock cycle. The filters introduce a 3-system clock cycle latency on the inputs.</li> <li>1 = Low-pass filters are enabled.</li> <li>0 = Low-pass filters are disabled.</li> </ul> |

# I<sup>2</sup>C Baud Rate High and Low Byte Registers

The I<sup>2</sup>C Baud Rate High and Low Byte registers, shown in Tables 74 and 75, combine to form a 16-bit reload value, BRG[15:0], for the I<sup>2</sup>C Baud Rate Generator. When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) ×BRG[15:0]

|  | Table 74. I <sup>2</sup> C Baud | Rate High Byt | te Register (I2CBI | RH) |

|--|---------------------------------|---------------|--------------------|-----|

|--|---------------------------------|---------------|--------------------|-----|

| Bit     | 7    | 7 6 5 4 3 2 1 0 |  |  |  |  |  | 0 |

|---------|------|-----------------|--|--|--|--|--|---|

| Field   | BRH  |                 |  |  |  |  |  |   |

| RESET   | FFH  |                 |  |  |  |  |  |   |

| R/W     | R/W  |                 |  |  |  |  |  |   |

| Address | F53H |                 |  |  |  |  |  |   |

Bit Description

#### [7:0] I<sup>2</sup>C Baud Rate High Byte

BRH Most significant byte, BRG[15:8], of the I<sup>2</sup>C Baud Rate Generator's reload value.

**Note:** If the DIAG bit in the  $I^2C$  Diagnostic Control Register is set to 1, a read of the I2CBRH Register returns the current value of the  $I^2C$  Baud Rate Counter[15:8].

# Flash Memory Address 0000H

Table 90. Option Bits at Flash Memory Address 0000H for 8K Series Flash Devices

| Bit                                             | 7                    | 6      | 6         5         4         3         2         1         0 |  |          |     |  | 0 |

|-------------------------------------------------|----------------------|--------|---------------------------------------------------------------|--|----------|-----|--|---|

| Field                                           | WDT_RES              | WDT_AO | OSC_SEL[1:0] VBO_AO RP Reserve                                |  | Reserved | FWP |  |   |

| RESET                                           | U                    |        |                                                               |  |          |     |  |   |

| R/W                                             | R/W                  |        |                                                               |  |          |     |  |   |

| Address                                         | Program Memory 0000H |        |                                                               |  |          |     |  |   |

| Note: U = Unchanged by Reset; R/W = Read/Write. |                      |        |                                                               |  |          |     |  |   |

| Sit C                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDT_RES 0                | <ul> <li>Watchdog Timer Reset</li> <li>Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.</li> <li>Watchdog Timer time-out causes a Reset. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                                                                                                                             |

| VDT_AO 0                 | <ul> <li>Vatchdog Timer Always On</li> <li>Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled.</li> <li>Watchdog Timer is enabled upon execution of the WDT instruction. After it is enabled, the Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                                     |

| OSC_SEL[1:0] 0<br>0<br>1 | <ul> <li>DSCILLATOR Mode Selection</li> <li>00 = On-chip oscillator configured for use with external RC networks (&lt;4MHz).</li> <li>01 = Minimum power for use with very-low-frequency crystals (32kHz to 1.0MHz).</li> <li>0 = Medium power for use with medium frequency crystals or ceramic resonators (0.5MHz to 10.0MHz).</li> <li>1 = Maximum power for use with high-frequency crystals (8.0MHz to 20.0MHz). This setting is the default for unprogrammed (erased) Flash.</li> </ul> |

| BO_AO 0                  | <ul> <li>Voltage Brown-Out Protection Always On</li> <li>Voltage Brown-Out Protection is disabled in STOP Mode to reduce total power consumption.</li> <li>Voltage Brown-Out Protection is always enabled including during STOP Mode. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                                                                                                                                 |

| P 0                      | <ul> <li>Read Protect</li> <li>User program code is inaccessible. Limited control features are available through the OCD.</li> <li>User program code is accessible. All OCD commands are enabled. This setting is the default for unprogrammed (erased) Flash.</li> </ul>                                                                                                                                                                                                                     |

|                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### TILOG Embedded in Life IXYS Company 166

or generate a BRK when its value matches the Program Counter. Because this register is really a down counter, the returned value is inverted when this register is read so the returned result appears to be an up counter. If the device is not in DEBUG Mode, this command returns FFFFH.

```

DBG \leftarrow 03H

DBG \rightarrow ~OCDCNTR[15:8]

DBG \rightarrow ~OCDCNTR[7:0]

```

Write OCD Control Register (04H). The Write OCD Control Register command writes the data that follows to the OCDCTL Register. When the Read Protect option bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of putting the device back into normal operating mode is to reset the device.

```

DBG \leftarrow 04H

DBG \leftarrow OCDCTL[7:0]

```

**Read OCD Control Register (05H).** The Read OCD Control Register command reads the value of the OCDCTL Register.

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

Write Program Counter (06H). The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter. If the device is not in DEBUG Mode or if the Read Protect option bit is enabled, the Program Counter values are discarded.

**Read Program Counter (07H).** The Read Program Counter command reads the value in the eZ8 CPU's Program Counter. If the device is not in DEBUG Mode or if the Read Protect option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

**Write Register (08H).** The Write Register command writes data to the Register File. Data can be written 1-256 bytes at a time (256 bytes can be written by setting size to zero). If the device is not in DEBUG Mode, the address and data values are discarded. If the Read Protect option bit is enabled, then only writes to the Flash Control registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

195

n IXYS Company

# SPI SLAVE Mode Timing

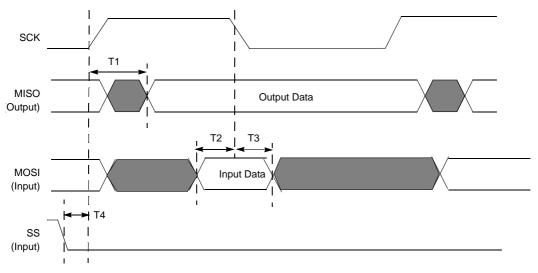

Figure 52 and Table 110 provide timing information for the SPI SLAVE Mode pins. Timing is shown with SCK rising edge used to source MISO output data, SCK falling edge used to sample MOSI input data.

#### Table 110. SPI SLAVE Mode Timing

|                |                                                | Dela                       | y (ns)                               |

|----------------|------------------------------------------------|----------------------------|--------------------------------------|

| Parameter      | Abbreviation                                   | Minimum                    | Maximum                              |

| SPI SLAVE      |                                                |                            |                                      |

| T <sub>1</sub> | SCK (transmit edge) to MISO output Valid Delay | 2 * X <sub>IN</sub> period | 3 * X <sub>IN</sub> period +<br>20ns |

| T <sub>2</sub> | MOSI input to SCK (receive edge) Setup Time    | 0                          |                                      |

| T <sub>3</sub> | MOSI input to SCK (receive edge) Hold Time     | 3 * X <sub>IN</sub> period |                                      |

| T <sub>4</sub> | SS input assertion to SCK setup                | 1 * X <sub>IN</sub> period |                                      |

198

С

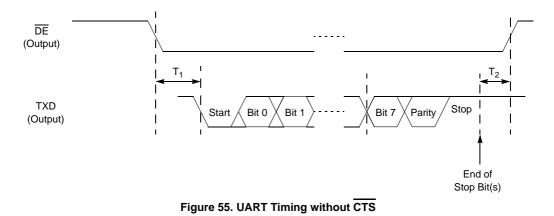

resented here by  $\overline{DE}$ .  $\overline{DE}$  asserts after the UART Transmit Data Register has been written.  $\overline{DE}$  remains asserted for multiple characters as long as the Transmit Data Register is written with the next character before the current character has completed.

|                |                                                | Delay (ns)                 |                                              |

|----------------|------------------------------------------------|----------------------------|----------------------------------------------|

| Parameter      | Abbreviation                                   | Minimum                    | Maximum                                      |

| T <sub>1</sub> | DE Assertion to TXD Falling Edge (Start) Delay | 1 Bit period               | 1 Bit period +<br>1 * X <sub>IN</sub> period |

| T <sub>2</sub> | End of Stop Bit(s) to DE Deassertion Delay     | 1 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period                   |

#### 204

# eZ8 CPU Instruction Classes

eZ8 CPU instructions are divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

- Block Transfer

- CPU Control

- Load

- Logical

- Program Control

- Rotate and Shift

Tables 119 through 126 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                  |

|----------|----------|----------------------------------------------|

| ADC      | dst, src | Add with Carry                               |

| ADCX     | dst, src | Add with Carry using Extended Addressing     |

| ADD      | dst, src | Add                                          |

| ADDX     | dst, src | Add using Extended Addressing                |

| CP       | dst, src | Compare                                      |

| CPC      | dst, src | Compare with Carry                           |

| CPCX     | dst, src | Compare with Carry using Extended Addressing |

| CPX      | dst, src | Compare using Extended Addressing            |

| DA       | dst      | Decimal Adjust                               |

| DEC      | dst      | Decrement                                    |

| DECW     | dst      | Decrement Word                               |

| INC      | dst      | Increment                                    |

| INCW     | dst      | Increment Word                               |

Table 119. Arithmetic Instructions

207

| Mnemonic | Operands | Instruction                                       |

|----------|----------|---------------------------------------------------|

| AND      | dst, src | Logical AND                                       |

| ANDX     | dst, src | Logical AND using Extended Addressing             |

| COM      | dst      | Complement                                        |

| OR       | dst, src | Logical OR                                        |

| ORX      | dst, src | Logical OR using Extended Addressing              |

| XOR      | dst, src | Logical Exclusive OR                              |

| XORX     | dst, src | Logical Exclusive OR using Extended<br>Addressing |

### Table 124. Logical Instructions

### Table 125. Program Control Instructions

| Operands        | Instruction                                                                                                         |

|-----------------|---------------------------------------------------------------------------------------------------------------------|

| —               | On-Chip Debugger Break                                                                                              |

| p, bit, src, DA | Bit Test and Jump                                                                                                   |

| bit, src, DA    | Bit Test and Jump if Non-Zero                                                                                       |

| bit, src, DA    | Bit Test and Jump if Zero                                                                                           |

| dst             | Call Procedure                                                                                                      |

| dst, src, RA    | Decrement and Jump Non-Zero                                                                                         |

| —               | Interrupt Return                                                                                                    |

| dst             | Jump                                                                                                                |

| dst             | Jump Conditional                                                                                                    |

| DA              | Jump Relative                                                                                                       |

| DA              | Jump Relative Conditional                                                                                           |

| —               | Return                                                                                                              |

| vector          | Software Trap                                                                                                       |

|                 | <br>p, bit, src, DA<br>bit, src, DA<br>dst, src, DA<br>dst<br>dst, src, RA<br><br>dst<br>dst<br>dst<br>DA<br>DA<br> |

249

condition code 201 continuous conversion (ADC) 138 continuous mode 68 control register definition, UART 88 control register, I2C 131 counter modes 68 CP 204 CPC 204 CPCX 204 CPU and peripheral overview 4 CPU control instructions 206 CPX 204 Customer Feedback Form 258 customer feedback form 224 Customer Information 258

# D

DA 201, 204 data register, I2C 129 DC characteristics 178 debugger, on-chip 158 **DEC 204** decimal adjust 204 decrement 204 and jump non-zero 207 word 204 **DECW 204** destination operand 202 device, port availability 29 DI 206 direct address 201 disable interrupts 206 **DINZ 207** DMA controller 5 dst 202

# Ε

EI 206 electrical characteristics 176 ADC 190 flash memory and timing 187 GPIO input data sample timing 191 watch-dog timer 188 enable interrupt 206 ER 201 extended addressing register 201 external pin reset 24 external RC oscillator electrical characteristics 187 eZ8 CPU features 4 eZ8 CPU instruction classes 204 eZ8 CPU instruction notation 201 eZ8 CPU instruction set 199 eZ8 CPU instruction summary 208

# F

FCTL register 150, 246 features, Z8 Encore! 1 first opcode map 219 FLAGS 202 flags register 202 flash controller 4 option bit address space 155 option bit configuration - reset 155 program memory address 0001H 157 flash memory arrangement 144 byte programming 147 code protection 146 control register definitions 149 controller bypass 148 electrical characteristics and timing 187 flash control register 150, 246 flash status register 151 frequency high and low byte registers 153 mass erase 148 operation 145 operation timing 145 page erase 148 page select register 152 FPS register 152 FSTAT register 151

rotate right through carry 208 RP 202 RR 202, 208 rr 202 RRC 208

### S

**SBC 205** SCF 205, 206 **SCK 103** SDA and SCL (IrDA) signals 117 second opcode map after 1FH 220 serial clock 104 serial peripheral interface (SPI) 101 set carry flag 205, 206 set register pointer 206 shift right arithmetic 208 shift right logical 208 signal descriptions 10 single-shot conversion (ADC) 137 SIO 5 slave data transfer formats (I2C) 123 slave select 104 software trap 207 source operand 202 SP 202 SPI architecture 101 baud rate generator 108 baud rate high and low byte register 114 clock phase 104 configured as slave 102 control register 110 control register definitions 109 data register 109 error detection 107 interrupts 108 mode fault error 107 mode register 112 multi-master operation 106 operation 103 overrun error 107 signals 103

single master, multiple slave system 102 single master, single slave system 101 status register 111 timing, PHASE = 0.105timing, PHASE=1 106 SPI controller signals 10 SPI mode (SPIMODE) 112, 236 SPIBRH register 114, 236 SPIBRL register 114, 237 SPICTL register 110, 235 SPIDATA register 109, 235 SPIMODE register 112, 236 SPISTAT register 111, 235 **SRA 208** src 202 **SRL 208 SRP 206** SS, SPI signal 103 stack pointer 202 status register, I2C 129 **STOP 206** stop mode 27, 206 stop mode recovery sources 25 using a GPIO port pin transition 26 using watch-dog timer time-out 26 **SUB 205** subtract 205 subtract - extended addressing 205 subtract with carry 205 subtract with carry - extended addressing 205 SUBX 205 **SWAP 208** swap nibbles 208 symbols, additional 202 system and core resets 21

# Т

TCM 205 TCMX 205 test complement under mask 205 test complement under mask - extended addressing 205