# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 11                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                |                                                           |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            |                                                           |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0811hh020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ILO G

13

## **Pin Characteristics**

Table 4 provides detailed information about the characteristics for each pin available on Z8 Encore!  $XP^{\textcircled{B}}$  F0822 Series products. The data in Table 4 is sorted alphabetically by pin symbol mnemonic.

| Symbol<br>Mnemonic | Direction | Reset<br>Direction | Active<br>Low or<br>Active<br>High | Tri-State<br>Output | Internal<br>Pull-Up or<br>Pull-Down | Schmitt-Trigger<br>Input | Open Drain<br>Output   |

|--------------------|-----------|--------------------|------------------------------------|---------------------|-------------------------------------|--------------------------|------------------------|

| AV <sub>DD</sub>   | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| AV <sub>SS</sub>   | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| DBG                | I/O       | I                  | N/A                                | Yes                 | No                                  | Yes                      | Yes                    |

| PA[7:0]            | I/O       | I                  | N/A                                | Yes                 | Programma-<br>ble pull-up           | Yes                      | Yes, pro-<br>grammable |

| PB[4:0]            | I/O       | I                  | N/A                                | Yes                 | Programma-<br>ble pull-up           | Yes                      | Yes, pro-<br>grammable |

| PC[5:0]            | I/O       | I                  | N/A                                | Yes                 | Programma-<br>ble pull-up           | Yes                      | Yes, pro-<br>grammable |

| RESET              | I         | I                  | Low                                | N/A                 | Pull-up                             | Yes                      | N/A                    |

| V <sub>DD</sub>    | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| V <sub>REF</sub>   | Analog    | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| V <sub>SS</sub>    | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| X <sub>IN</sub>    | I         | I                  | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| X <sub>OUT</sub>   | 0         | 0                  | N/A                                | No                  | No                                  | No                       | No                     |

#### **Table 4. Pin Characteristics**

Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

## Stop Mode Recovery Using WDT Time-Out

If the WDT times out during STOP Mode, the device undergoes a Stop Mode Recovery sequence. In the WDT Control Register, the WDT and stop bits are set to 1. If the WDT is configured to generate an interrupt upon time-out and the Z8 Encore! XP<sup>®</sup> F0822 Series device is configured to respond to interrupts, the eZ8 CPU services the WDT interrupt request following the normal Stop Mode Recovery sequence.

## Stop Mode Recovery Using a GPIO Port Pin Transition

Each of the GPIO port pins can be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a STOP Mode Recover source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery. The GPIO Stop Mode Recovery signals are filtered to reject pulses less than 10ns (typical) in duration. In the WDT Control Register, the stop bit is set to 1.

**Caution:** In STOP Mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the Port transition only if the signal stays on the port pin through the end of the Stop Mode Recovery delay. Therefore, short pulses on the port pin initiates Stop Mode Recovery without being written to the Port Input Data Register or without initiating an interrupt (if enabled for that pin).

ilog Embedded in Life An DIXYS Company 41

| Priority | Program Memory<br>Vector Address | Interrupt Source                                |

|----------|----------------------------------|-------------------------------------------------|

| Highest  | 0002H                            | Reset (not an interrupt)                        |

|          | 0004H                            | WDT (see the Watchdog Timer chapter on page 70) |

|          | 0006H                            | Illegal Instruction Trap (not an interrupt)     |

|          | 0008H                            | Reserved                                        |

|          | 000AH                            | Timer 1                                         |

|          | 000CH                            | Timer 0                                         |

|          | 000EH                            | UART 0 receiver                                 |

|          | 0010H                            | UART 0 transmitter                              |

|          | 0012H                            | l <sup>2</sup> C                                |

|          | 0014H                            | SPI                                             |

|          | 0016H                            | ADC                                             |

|          | 0018H                            | Port A7, rising or falling input edge           |

|          | 001AH                            | Port A6, rising or falling input edge           |

|          | 001CH                            | Port A5, rising or falling input edge           |

|          | 001EH                            | Port A4, rising or falling input edge           |

|          | 0020H                            | Port A3, rising or falling input edge           |

|          | 0022H                            | Port A2, rising or falling input edge           |

|          | 0024H                            | Port A1, rising or falling input edge           |

|          | 0026H                            | Port A0, rising or falling input edge           |

|          | 0028H                            | Reserved                                        |

|          | 002AH                            | Reserved                                        |

|          | 002CH                            | Reserved                                        |

|          | 002EH                            | Reserved                                        |

|          | 0030H                            | Port C3, both input edges                       |

|          | 0032H                            | Port C2, both input edges                       |

|          | 0034H                            | Port C1, both input edges                       |

| Lowest   | 0036H                            | Port C0, both input edges                       |

#### Table 24. Interrupt Vectors in Order of Priority

| Z8 Encore! XP <sup>®</sup> F0822<br>Product Speci |   | - |   |   |

|---------------------------------------------------|---|---|---|---|

|                                                   | i | l | 0 | ď |

bedded in Lif

nu IXYS Comp

42

## Architecture

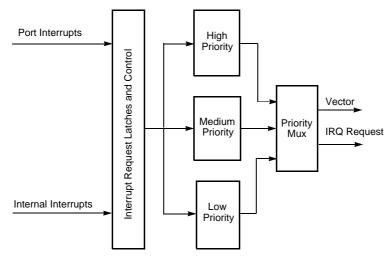

Figure 9 displays a block diagram of the interrupt controller.

Figure 9. Interrupt Controller Block Diagram

## Operation

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 42

Interrupt Vectors and Priority: see page 43

Interrupt Assertion: see page 43

Software Interrupt Assertion: see page 44

#### **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables interrupts.

Interrupts are globally enabled by any of the following actions:

- Execution of an Enable Interrupt (EI) instruction

- Execution of an Return from Interrupt (IRET) instruction

# Embedded in Life

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT Mode equation is used to determine the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is calculated using the following equation:

$PWM \text{ Output High Time Ratio (\%)} = \frac{\text{Reload Value} - PWM \text{ Value}}{\text{Reload Value}} x100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is calculated using the following equation:

PWM Output High Time Ratio (%) =  $\frac{PWM \text{ Value}}{\text{Reload Value}} \times 100$

#### CAPTURE Mode

In CAPTURE Mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The capture count value is written to the Timer PWM High and Low Byte registers. The timer input is the system clock. The TPOL bit in the Timer Control Register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the capture event occurs, an interrupt is generated and the timer continues counting.

The timer continues counting up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the reload value, the timer generates an interrupt and continues counting.

Observe the following procedure for configuring a timer for CAPTURE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for CAPTURE Mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. This allows user software to determine if interrupts were generated by either a capture event or a reload. If

## nbedded in Life IXYS Company 61

the PWM High and Low Byte registers still contains 0000H after the interrupt, then the interrupt was generated by a reload.

- 5. If required, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control Register to enable the timer and initiate counting.

In CAPTURE Mode, the elapsed time from timer start to capture event is calculated using the following equation:

Capture Elapsed Time (s) = (Capture Value – Start Value)xPrescale System Clock Frequency (Hz)

#### **COMPARE Mode**

In COMPARE Mode, the timer counts up to the 16-bit maximum Compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Compare value, the timer generates an interrupt and counting continues (the timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon Compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting.

Observe the following procedure for configuring a timer for COMPARE Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for COMPARE Mode

- Set the prescale value

- Set the initial logic level (High or Low) for the Timer Output alternate function, if required

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. If required, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control Register to enable the timer and initiate counting.

## **UART Status 0 Register**

The UART Status 0 and Status 1 registers, shown in Tables 55 and 56, identify the current UART operating configuration and status.

#### Table 55. UART Status 0 Register (U0STAT0)

| Bit         | 7                                                                                                                                                                                                                                                                                                                                              | 6                                                                                                                                                                                                                                                                                 | 5  | 4  | 3    | 2    | 1   | 0           |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|------|------|-----|-------------|--|--|

| Field       | RDA                                                                                                                                                                                                                                                                                                                                            | PE                                                                                                                                                                                                                                                                                | OE | FE | BRKD | TDRE | TXE | CTS         |  |  |

| RESET       |                                                                                                                                                                                                                                                                                                                                                | 0 1 X                                                                                                                                                                                                                                                                             |    |    |      |      |     |             |  |  |

| R/W         |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                   |    | I  | २    |      |     |             |  |  |

| Address     |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                   |    | F4 | 1H   |      |     |             |  |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                   |    |    |      |      |     |             |  |  |

|             |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                   | •  |    |      |      |     |             |  |  |

| [7]<br>RDA  | This bit indi<br>Receive Da<br>0 = The UA                                                                                                                                                                                                                                                                                                      | Receive Data Available<br>This bit indicates that the UART Receive Data Register has received data. Reading the UART<br>Receive Data Register clears this bit.<br>0 = The UART Receive Data Register is empty.<br>1 = There is a byte in the UART Receive Data Register.          |    |    |      |      |     |             |  |  |

| [6]<br>PE   | This bit indi<br>clears this $0 = No pari$                                                                                                                                                                                                                                                                                                     | Parity Error<br>This bit indicates that a parity error has occurred. Reading the UART Receive Data Register<br>clears this bit.<br>0 = No parity error has occurred.<br>1 = A parity error has occurred.                                                                          |    |    |      |      |     |             |  |  |

| [5]<br>OE   | Overrun Error<br>This bit indicates that an overrun error has occurred. An overrun occurs when new data is<br>received and the UART Receive Data Register has not been read. If the RDA bit is reset to 0,<br>then reading the UART Receive Data Register clears this bit.<br>0 = No overrun error occurred.<br>1 = An overrun error occurred. |                                                                                                                                                                                                                                                                                   |    |    |      |      |     |             |  |  |

| [4]<br>FE   | Framing Error<br>This bit indicates that a framing error (no stop bit following data reception) was detected. Read<br>ing the UART Receive Data Register clears this bit.<br>0 = No framing error occurred.<br>1 = A framing error occurred.                                                                                                   |                                                                                                                                                                                                                                                                                   |    |    |      |      |     | cted. Read- |  |  |

| [3]<br>BRKD | This bit indi<br>are all zero<br>0 = No brea                                                                                                                                                                                                                                                                                                   | <b>Break Detect</b><br>This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and stop bit(s) are all zeros then this bit is set to 1. Reading the UART Receive Data Register clears this bit.<br>0 = No break occurred.<br>1 = A break occurred. |    |    |      |      |     |             |  |  |

| [2]<br>TDRE |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                   |    |    |      |      |     |             |  |  |

90

ILO G

ILOG nbedded in Life IIXYS Company

100

clock periods since the previous pulse was detected). This period allows the endec a sampling window of -4 to +8 baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window, this process is repeated. If the incoming data is a logical 1 (no pulse), the endec returns to its initial state and waits for the next falling edge. As each falling edge is detected, the endec clock counter is reset to resynchronize the endec to the incoming data stream. Resynchronizing the endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a start bit is received.

## **Infrared Endec Control Register Definitions**

All infrared endec configuration and status information is set by the UART control registers as defined in the UART Control Register Definitions section on page 88.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 Register to 1 to enable the infrared endec before enabling the GPIO port alternate function for the corresponding pin.

## Embedded in Life An UXYS Company 132

| Bit           | Description (Continued)                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]<br>FLUSH  | <b>Flush Data</b><br>Setting this bit to 1 clears the $I^2C$ Data Register and sets the TDRE bit to 1. This bit allows flushing of the $I^2C$ Data Register when a Not Acknowledge interrupt is received after the data has been sent to the $I^2C$ Data Register. Reading this bit always returns 0.                                                                                          |

| [0]<br>FILTEN | <ul> <li>I<sup>2</sup>C Signal Filter Enable</li> <li>This bit enables low-pass digital filters on the SDA and SCL input signals. These filters reject any input pulse with periods less than a full system clock cycle. The filters introduce a 3-system clock cycle latency on the inputs.</li> <li>1 = Low-pass filters are enabled.</li> <li>0 = Low-pass filters are disabled.</li> </ul> |

## I<sup>2</sup>C Baud Rate High and Low Byte Registers

The I<sup>2</sup>C Baud Rate High and Low Byte registers, shown in Tables 74 and 75, combine to form a 16-bit reload value, BRG[15:0], for the I<sup>2</sup>C Baud Rate Generator. When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s) ×BRG[15:0]

|  | Table 74. I <sup>2</sup> C Baud | Rate High B | yte Register ( | (I2CBRH) |

|--|---------------------------------|-------------|----------------|----------|

|--|---------------------------------|-------------|----------------|----------|

| Bit     | 7   | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |

|---------|-----|-----------------|--|--|--|--|--|--|--|--|

| Field   | BRH |                 |  |  |  |  |  |  |  |  |

| RESET   | FFH |                 |  |  |  |  |  |  |  |  |

| R/W     | R/W |                 |  |  |  |  |  |  |  |  |

| Address |     | F53H            |  |  |  |  |  |  |  |  |

Bit Description

#### [7:0] I<sup>2</sup>C Baud Rate High Byte

BRH Most significant byte, BRG[15:8], of the I<sup>2</sup>C Baud Rate Generator's reload value.

**Note:** If the DIAG bit in the  $I^2C$  Diagnostic Control Register is set to 1, a read of the I2CBRH Register returns the current value of the  $I^2C$  Baud Rate Counter[15:8].

Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

## nbedded in Life IIXYS Company 141

## ADC Data High Byte Register

The ADC Data High Byte Register, shown in Table 79, contains the upper eight bits of the 10-bit ADC output. During a SINGLE-SHOT conversion, this value is invalid. Access to the ADC Data High Byte Register is read-only. The full 10-bit ADC result is furnished by {ADCD\_H[7:0], ADCD\_L[7:6]}. Reading the ADC Data High Byte Register latches data in the ADC Low Bits Register.

| Bit     | 7          | 6      | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------------|--------|---|---|---|---|---|---|--|--|

| Field   |            | ADCD_H |   |   |   |   |   |   |  |  |

| RESET   |            | Х      |   |   |   |   |   |   |  |  |

| R/W     |            | R      |   |   |   |   |   |   |  |  |

| Address | F72H       |        |   |   |   |   |   |   |  |  |

| Bit     | Descriptio | n      |   |   |   |   |   |   |  |  |

| [7:0]   | ADC Data   |        |   |   |   |   |   |   |  |  |

#### Table 79. ADC Data High Byte Register (ADCD\_H)

ADCD\_H This byte contains the upper eight bits of the 10-bit ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the last conversion output is held in this register. These bits are undefined after a Reset.

## Flash Memory

The products in the Z8 Encore! XP<sup>®</sup> F0822 Series feature either 8KB (8192) or 4KB (4096) bytes of Flash memory with Read/Write/Erase capability. Flash memory is programmed and erased in-circuit by either user code or through the OCD.

The Flash memory array is arranged in 512-byte per page. The 512-byte page is the minimum Flash block size that can be erased. Flash memory is divided into eight sectors which is protected from programming and erase operations on a per sector basis.

Table 81 describes the Flash memory configuration for each device in the Z8F082xfamily. Table 82 lists the sector address ranges. Figure 33 displays the Flash memory arrangement.

| Part Number | Flash Size | Number<br>of Pages | Flash Memory<br>Addresses | Sector Size | Number of<br>Sectors | Pages<br>per<br>Sector |

|-------------|------------|--------------------|---------------------------|-------------|----------------------|------------------------|

| Z8F08xx     | 8KB (8192) | 16                 | 0000H-1FFFH               | 1 KB (1024) | 8                    | 2                      |

| Z8F04xx     | 4KB (4096) | 8                  | 0000H-0FFFH               | 0.5KB (512) | 8                    | 1                      |

Table 82. Flash Memory Sector Addresses

#### Table 81. Flash Memory Configurations

|               | Flash Sector Address Ranges |             |  |  |  |  |

|---------------|-----------------------------|-------------|--|--|--|--|

| Sector Number | Z8F04xx                     | Z8F08xx     |  |  |  |  |

| 0             | 0000H-01FFH                 | 0000H-03FFH |  |  |  |  |

| 1             | 0200H-03FFH                 | 0400H–07FFH |  |  |  |  |

| 2             | 0400H-05FFH                 | 0800H-0BFFH |  |  |  |  |

| 3             | 0600H-07FFH                 | 0C00H-0FFFH |  |  |  |  |

| 4             | 0800H-09FFH                 | 1000H–13FFH |  |  |  |  |

| 5             | 0A00H-0BFFH                 | 1400H–17FFH |  |  |  |  |

| 6             | 0C00H-0DFFH                 | 1800H–1BFFH |  |  |  |  |

| 7             | 0E00H-0FFFH                 | 1C00H-1FFFH |  |  |  |  |

143

nbedded in Life

ilog Embedded in Life An TIXYS Company 149

For more information about bypassing the Flash Controller, refer to the <u>Third Party Flash</u> <u>Programming Support for Z8 Encore! MCU Application Note (AN0117)</u>, available for download at <u>www.zilog.com</u>.

## Flash Controller Behavior in Debug Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the OCD:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect Register is ignored for programming and erase operations

- Programming operations are not limited to the page selected in the Page Select Register

- Bits in the Flash Sector Protect Register can be written to 1 or 0

- The second write of the Page Select Register to unlock the Flash Controller is not necessary

- The Page Select Register is written when the Flash Controller is unlocked

- The Mass Erase command is enabled

## **Flash Control Register Definitions**

This section defines the features of the following Flash Control registers.

Flash Control Register: see page 150

Flash Status Register: see page 151

Page Select Register: see page 152

Flash Sector Protect Register: see page 152

Flash Frequency High and Low Byte Registers: see page 153

Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

#### 186

ilog<sup>®</sup>

## **On-Chip Peripheral AC and DC Electrical Characteristics**

Table 100 provides information about the Power-On Reset and Voltage Brown-Out electrical characteristics.

| Table 100. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing |  |

|---------------------------------------------------------------------------------------|--|

|---------------------------------------------------------------------------------------|--|

|                   |                                                                             | T <sub>A</sub> = | –40°C to 1 | 05°C    |       |                                                                                                       |  |

|-------------------|-----------------------------------------------------------------------------|------------------|------------|---------|-------|-------------------------------------------------------------------------------------------------------|--|

| Symbol            | Parameter                                                                   | Minimum          | Typical*   | Maximum | Units | Conditions                                                                                            |  |

| V <sub>POR</sub>  | Power-On Reset<br>Voltage Threshold                                         | 2.15             | 2.40       | 2.60    | V     | $V_{DD} = V_{POR}$                                                                                    |  |

| V <sub>VBO</sub>  | Voltage Brown-Out<br>Reset Voltage<br>Threshold                             | 2.05             | 2.30       | 2.55    | V     | $V_{DD} = V_{VBO}$                                                                                    |  |

|                   | V <sub>POR</sub> to V <sub>VBO</sub> hys-<br>teresis                        | 50               | 100        | -       | mV    |                                                                                                       |  |

|                   | Starting V <sub>DD</sub> voltage to ensure valid POR                        | -                | $V_{SS}$   | -       | V     |                                                                                                       |  |

| T <sub>ANA</sub>  | POR Analog Delay                                                            | -                | 50         | _       | μs    | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |  |

| T <sub>POR</sub>  | POR Digital Delay                                                           | -                | 5.0        | -       | ms    | 50 WDT Oscillator cycles<br>(10kHz) + 16 System Clock<br>cycles (20MHz)                               |  |

| Т <sub>VBO</sub>  | Voltage Brown-Out<br>Pulse Rejection<br>Period                              | -                | 10         | _       | μs    | V <sub>DD</sub> < V <sub>VBO</sub> to generate a<br>Reset.                                            |  |

| T <sub>RAMP</sub> | Time for VDD to transition from $V_{SS}$ to $V_{POR}$ to ensure valid Reset | 0.10             | _          | 100     | ms    |                                                                                                       |  |

Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

O g

An IXYS Company

192

## General Purpose I/O Port Output Timing

X<sub>IN</sub>

Figure 49 and Table 107 provide timing information for GPIO port pins.

|                |                                                 | Delay (ns) |         |  |  |

|----------------|-------------------------------------------------|------------|---------|--|--|

| Parameter      | Abbreviation                                    | Minimum    | Maximum |  |  |

| GPIO Port I    | Pins                                            |            |         |  |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | _          | 15      |  |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2          | _       |  |  |

#### Table 107. GPIO Port Output Timing

#### Assembly Language Source Program Example

| JP START     | ; Everything after the semicolon is a comment.                                                                                                                                                                                                                                             |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:       | ; A label called "START". The first instruction (JP<br>; START) in this example causes program execution to<br>; jump to the point within the program where the<br>; START label occurs.                                                                                                   |

| LD R4, R7    | ; A Load (LD) instruction with two operands. The<br>; first operand, Working Register R4, is the<br>; destination. The second operand, Working Register<br>; R7, is the source. The contents of R7 is written<br>; into R4.                                                                |

| LD 234H, 01H | <pre>; Another Load (LD) instruction with two operands.<br/>; The first operand, Extended Mode Register Address<br/>; 234H, is the destination. The second operand,<br/>; Immediate Data value 01H, is the source. The value<br/>; 01H is written into the Register at address 234H.</pre> |

## Assembly Language Syntax

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is op code-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. This binary format must be followed by users that prefer manual program coding or intend to implement their own assembler.

**Example 1.** If the contents of registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code result is shown in Table 114.

#### Table 114. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H | 08H | (ADD dst, src) |

|------------------------|-----|-----|-----|----------------|

| Object Code            | 04  | 08  | 43  | (OPC src, dst) |

**Example 2.** In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code result is shown in Table 115.

| Z8 Encore! XP® | F0822  | Series  |

|----------------|--------|---------|

| Product        | Specif | ication |

226

#### Hex Address: F01

#### Table 131. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7     | 6   | 5 | 4     | 3    | 2 | 1 | 0 |  |  |  |

|---------|-------|-----|---|-------|------|---|---|---|--|--|--|

| Field   | TL TL |     |   |       |      |   |   |   |  |  |  |

| RESET   |       |     |   | 0     |      |   |   | 1 |  |  |  |

| R/W     |       | R/W |   |       |      |   |   |   |  |  |  |

| Address |       |     |   | F01H, | F09H |   |   |   |  |  |  |

#### Hex Address: F02

#### Table 132. Timer 0–1 Reload High Byte Register (TxRH)

| Bit     | 7 | 6   | 5 | 4     | 3    | 2 | 1 | 0 |  |  |  |

|---------|---|-----|---|-------|------|---|---|---|--|--|--|

| Field   |   | TRH |   |       |      |   |   |   |  |  |  |

| RESET   |   |     |   |       | 1    |   |   |   |  |  |  |

| R/W     |   | R/W |   |       |      |   |   |   |  |  |  |

| Address |   |     |   | F02H, | F0AH |   |   |   |  |  |  |

#### Hex Address: F03

#### Table 133. Timer 0–1 Reload Low Byte Register (TxRL)

| Bit     | 7 | 6   | 5 | 4     | 3    | 2 | 1 | 0 |  |  |  |

|---------|---|-----|---|-------|------|---|---|---|--|--|--|

| Field   |   | TRL |   |       |      |   |   |   |  |  |  |

| RESET   |   |     |   |       | 1    |   |   |   |  |  |  |

| R/W     |   | R/W |   |       |      |   |   |   |  |  |  |

| Address |   |     |   | F03H, | F0BH |   |   |   |  |  |  |

#### Hex Address: F45

#### Table 152. UART Address Compare Register (U0ADDR)

| Bit     | 7 | 6         | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|---|-----------|---|----|----|---|---|---|--|--|--|

| Field   |   | COMP_ADDR |   |    |    |   |   |   |  |  |  |

| RESET   |   |           |   | (  | )  |   |   |   |  |  |  |

| R/W     |   | R/W       |   |    |    |   |   |   |  |  |  |

| Address |   |           |   | F4 | 5H |   |   |   |  |  |  |

#### Hex Address: F46

#### Table 153. UART Baud Rate High Byte Register (U0BRH)

| Bit     | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|---|-----|---|----|----|---|---|---|--|--|--|

| Field   |   | BRH |   |    |    |   |   |   |  |  |  |

| RESET   |   |     |   |    | 1  |   |   |   |  |  |  |

| R/W     |   | R/W |   |    |    |   |   |   |  |  |  |

| Address |   |     |   | F4 | 6H |   |   |   |  |  |  |

#### Hex Address: F47

#### Table 154. UART Baud Rate Low Byte Register (U0BRL)

| Bit     | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|---------|---|-----|---|----|----|---|---|---|--|--|--|

| Field   |   | BRL |   |    |    |   |   |   |  |  |  |

| RESET   |   |     |   |    | 1  |   |   |   |  |  |  |

| R/W     |   | R/W |   |    |    |   |   |   |  |  |  |

| Address |   |     |   | F4 | 7H |   |   |   |  |  |  |

#### Hex Addresses: F48–F4F

This address range is reserved.

### Hex Address: FC1

#### Table 173. IRQ0 Enable High Bit Register (IRQ0ENH)

| Bit     | 7        | 6     | 5     | 4             | 3             | 2      | 1      | 0      |  |

|---------|----------|-------|-------|---------------|---------------|--------|--------|--------|--|

| Field   | Reserved | T1ENH | T0ENH | <b>U0RENH</b> | <b>U0TENH</b> | I2CENH | SPIENH | ADCENH |  |

| RESET   | 0        |       |       |               |               |        |        |        |  |

| R/W     | R/W      |       |       |               |               |        |        |        |  |

| Address | FC1H     |       |       |               |               |        |        |        |  |

#### Hex Address: FC2

#### Table 174. IRQ0 Enable Low Bit Register (IRQ0ENL)

| Bit     | 7        | 6     | 5     | 4             | 3             | 2      | 1      | 0      |  |

|---------|----------|-------|-------|---------------|---------------|--------|--------|--------|--|

| Field   | Reserved | T1ENL | T0ENL | <b>U0RENL</b> | <b>U0TENL</b> | I2CENL | SPIENL | ADCENL |  |

| RESET   | 0        |       |       |               |               |        |        |        |  |

| R/W     | R/W      |       |       |               |               |        |        |        |  |

| Address | FC2H     |       |       |               |               |        |        |        |  |

#### Hex Address: FC3

#### Table 175. Interrupt Request 1 Register (IRQ1)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|---------|------|------|------|------|------|------|------|------|--|

| Field   | PA7I | PA6I | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |  |

| RESET   | 0    |      |      |      |      |      |      |      |  |

| R/W     | R/W  |      |      |      |      |      |      |      |  |

| Address |      | FC3H |      |      |      |      |      |      |  |

#### Hex Address: FC4

#### Table 176. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7      | 6      | 5      | 4      | 3             | 2      | 1      | 0      |  |  |

|---------|--------|--------|--------|--------|---------------|--------|--------|--------|--|--|

| Field   | PA7ENH | PA6ENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |  |  |

| RESET   | 0      |        |        |        |               |        |        |        |  |  |

| R/W     | R/W    |        |        |        |               |        |        |        |  |  |

| Address |        | FC4H   |        |        |               |        |        |        |  |  |

256

test under mask 205 test under mask - extended addressing 205 timer signals 11 timers 5, 54 architecture 55 block diagram 55 capture mode 60, 68 capture/compare mode 63, 69 compare mode 61, 68 continuous mode 56, 68 counter mode 57 counter modes 68 gated mode 62, 69 one-shot mode 55, 68 operating mode 55 PWM mode 58, 68 reading the timer count values 64 reload high and low byte registers 65 timer control register definitions 64 timer output signal operation 64 timers 0-3 control 0 registers 67 control registers 68 high and low byte registers 64, 66 TM 205 TMX 205 transmit IrDA data 98 transmit interrupt 117 transmitting UART data-interrupt-driven method 80 transmitting UART data-polled method 79 **TRAP 207**

## U

UART 4 architecture 77 baud rate generator 88 baud rates table 96 control register definitions 88 controller signals 11 interrupts 86 multiprocessor mode 83

receiving data using interrupt-driven method 82 receiving data using the polled method 81 transmitting data using the interrupt-driven method 80 transmitting data using the polled method 79 x baud rate high and low registers 95 x control 0 and control 1 registers 92 x status 0 and status 1 registers 90, 91 UxBRH register 95, 232 UxBRL register 95, 232 UxCTL0 register 92, 94, 231, 232 UxCTL1 register 93, 231 UxRXD register 89, 230 UxSTAT0 register 90, 231 UxSTAT1 register 91, 231 UxTXD register 89, 230

## ۷

vector 202 voltage brown-out reset (VBR) 23

## W

watch-dog timer approximate time-out delay 71 CNTL 24 control register 73 electrical characteristics and timing 188 interrupt in normal operation 71 refresh 71, 206 reload unlock sequence 73 reload upper, high and low registers 75 reset 24 reset in normal operation 72 reset in STOP mode 71, 72 time-out response 71 WDTCTL register 74, 244 WDTH register 75, 245 WDTL register 76, 245 working register 201 working register pair 202 WTDU register 75, 245

nbedded in Life

258

## **Customer Support**

To share comments, get your technical questions answered or report issues you may be experiencing with our products, please visit Zilog's Technical Support page at <a href="http://support.zilog.com">http://support.zilog.com</a>.

To learn more about this product, find additional documentation or to discover other facets about Zilog product offerings, please visit the Zilog Knowledge Base at <u>http://zilog.com/</u><u>kb</u> or consider participating in the Zilog Forum at <u>http://zilog.com/forum</u>.

This publication is subject to replacement by a later edition. To determine whether a later edition exists, please visit the Zilog website at <u>http://www.zilog.com</u>.