# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 11                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0811hh020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Timer Output Signal Operation    64                      |   |

|----------------------------------------------------------|---|

| Timer Control Register Definitions                       |   |

| Timer 0–1 High and Low Byte Registers                    |   |

| Timer Reload High and Low Byte Registers                 |   |

| Timer 0–1 PWM High and Low Byte Registers                |   |

| Timer 0–3 Control 0 Registers                            |   |

| Timer 0–1 Control 1 Registers                            |   |

| Watchdog Timer                                           |   |

| Operation                                                |   |

| Watchdog Timer Refresh                                   |   |

| Watchdog Timer Time-Out Response                         |   |

| Watchdog Timer Reload Unlock Sequence                    |   |

| Watchdog Timer Control Register Definitions              |   |

| Watchdog Timer Control Register                          |   |

| Watchdog Timer Reload Upper, High and Low Byte Registers |   |

| Universal Asynchronous Receiver/Transmitter              |   |

| Architecture                                             |   |

| Operation                                                | , |

| Transmitting Data using Polled Method                    |   |

| Transmitting Data Using Interrupt-Driven Method          |   |

| Receiving Data using the Polled Method                   |   |

| Receiving Data Using Interrupt-Driven Method             | , |

| Clear To Send Operation                                  |   |

| Multiprocessor (9-Bit) Mode                              |   |

| External Driver Enable                                   |   |

| UART Interrupts                                          |   |

| UART Baud Rate Generator                                 |   |

| UART Control Register Definitions                        |   |

| UART Transmit Data Register                              |   |

| UART Receive Data Register 89                            |   |

| UART Status 0 Register                                   |   |

| UART Status 1 Register                                   |   |

| UART Control 0 and Control 1 Registers                   |   |

| UART Address Compare Register                            |   |

| UART Baud Rate High and Low Byte Registers               |   |

| Infrared Encoder/Decoder                                 |   |

| Architecture                                             |   |

| Operation                                                |   |

| Transmitting IrDA Data                                   |   |

| Receiving IrDA Data                                      |   |

|                                                          |   |

| Breakpoints                                             |

|---------------------------------------------------------|

| On-Chip Debugger Commands 164                           |

| On-Chip Debugger Control Register Definitions           |

| OCD Status Register                                     |

|                                                         |

| On-Chip Oscillator                                      |

| Crystal Oscillator Operation                            |

| Oscillator Operation with an External RC Network        |

| Electrical Characteristics                              |

| Absolute Maximum Ratings                                |

| DC Characteristics                                      |

| AC Characteristics                                      |

| On-Chip Peripheral AC and DC Electrical Characteristics |

| General Purpose I/O Port Input Data Sample Timing       |

| General Purpose I/O Port Output Timing                  |

| On-Chip Debugger Timing                                 |

| SPI MASTER Mode Timing 194                              |

| SPI SLAVE Mode Timing 195                               |

| I2C Timing 196                                          |

| UART Timing                                             |

| eZ8 CPU Instruction Set 199                             |

| Assembly Language Programming Introduction              |

| Assembly Language Syntax 200                            |

| eZ8 CPU Instruction Notation                            |

| Condition Codes                                         |

| eZ8 CPU Instruction Classes                             |

| eZ8 CPU Instruction Summary                             |

| Flags Register                                          |

| Op Code Maps                                            |

| Packaging 221                                           |

| Ordering Information                                    |

| Part Number Suffix Designations 224                     |

| General Purpose RAM                                     |

| Timer 0 Control Registers                               |

| UART Control Registers                                  |

| I2C Control Registers                                   |

| SPI Control Registers                                   |

| Analog-to-Digital Converter Control Registers           |

ix

### **CPU and Peripheral Overview**

Zilog's latest eZ8 8-bit CPU meets the continuing demand for faster and more code-efficient microcontrollers. The eZ8 CPU executes a superset of the original  $Z8^{$ ® instruction set.

The eZ8 CPU features:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required Program memory

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks

- Compatible with existing Z8<sup>®</sup> code

- Expanded internal Register File allows access of up to 4KB

- New instructions improve execution efficiency for code developed using higher-level programming languages, including C

- Pipelined instruction fetch and execution

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT and SRL

- New instructions support 12-bit linear addressing of the Register File

- Up to 10 MIPS operation

- C-Compiler friendly

- 2 to 9 clock cycles per instruction

For more information about the eZ8 CPU, refer to the <u>eZ8 CPU Core User Manual</u> (<u>UM0128</u>), which is available for download at <u>www.zilog.com</u>.

### **General Purpose Input/Output**

Z8 Encore! XP<sup>®</sup> F0822 Series features 11 to 19 port pins (Ports A–C) for General-Purpose Input/Output (GPIO). The number of available GPIO pins is a function of package type. Each pin is individually programmable. Ports A and C support 5V-tolerant inputs.

### **Flash Controller**

The Flash Controller programs and erases the contents of Flash memory.

#### bedded in Life IXYS Company 22

of Reset, all GPIO pins are configured as inputs. All GPIO programmable pull-ups are disabled.

During Reset, the eZ8 CPU and the on-chip peripherals are idle; however, the on-chip crystal oscillator and WDT oscillator continue to run. The system clock begins operating following the WDT oscillator cycle count. The eZ8 CPU and on-chip peripherals remain idle through all of the 16 cycles of the system clock.

Upon Reset, control registers within the Register File which have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following the Reset. The eZ8 CPU fetches the Reset vector at Program memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

### **Reset Sources**

Table 9 lists the reset sources as a function of the operating mode. The remainder of this section provides more detail about the individual reset sources.

• Note: A POR/VBO event always has priority over all other possible reset sources to ensure a full system reset occurs.

| Operating Mode | Reset Source                             | Reset Type                                             |

|----------------|------------------------------------------|--------------------------------------------------------|

| NORMAL or HALT | POR/VBO                                  | System Reset                                           |

| modes          | WDT time-out when configured for Reset   | System Reset                                           |

|                | RESET pin assertion                      | System Reset                                           |

|                | OCD-initiated Reset (OCDCTL[0] set to 1) | System Reset except the OCD is unaffected by the reset |

| STOP Mode      | POR/VBO                                  | System Reset                                           |

|                | RESET pin assertion                      | System Reset                                           |

|                | DBG pin driven Low                       | System Reset                                           |

#### Table 9. Reset Sources and Resulting Reset Type

### **Power-On Reset**

Each device in the Z8 Encore! XP<sup>®</sup> F0822 Series contains an internal POR circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR

- System clock is enabled and continues to operate

- eZ8 CPU is stopped

- Program counter stops incrementing

- WDT's internal RC oscillator continues to operate

- If enabled, the WDT continues to operate

- All other on-chip peripherals continue to operate

The eZ8 CPU can be brought out of HALT Mode by any of the following operations:

- Interrupt

- WDT time-out (interrupt or reset)

- Power-On Reset

- Voltage Brown-Out reset

- External RESET pin assertion

To minimize current in HALT Mode, all GPIO pins which are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

#### Port A–C Pull-up Enable Subregisters

The Port A–C Pull-Up Enable Subregister, shown in Table 21, is accessed through the Port A–C Control Register by writing 06H to the Port A–C Address Register. Setting the bits in the Port A–C Pull-Up Enable subregisters enables a weak internal resistive pull-up on the specified Port pins.

| Bit         | 7                                                                                                                      | 7 6 5 4 3 2 1 0                                 |  |  |  |  |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|--|--|--|--|

| Field       | PPUE7                                                                                                                  | PPUE7 PPUE6 PPUE5 PPUE4 PPUE3 PPUE2 PPUE1 PPUE0 |  |  |  |  |  |  |

| RESET       | 0                                                                                                                      |                                                 |  |  |  |  |  |  |

| R/W         | R/W                                                                                                                    |                                                 |  |  |  |  |  |  |

| Address     | See footnote.                                                                                                          |                                                 |  |  |  |  |  |  |

| Note: If 06 | Note: If 06H is written to the Port A–C Address Register, then it is accessible through the Port A–C Control Register. |                                                 |  |  |  |  |  |  |

| Table 21. Po | ort A-C Pull- | Up Enable S | ubregisters |

|--------------|---------------|-------------|-------------|

|--------------|---------------|-------------|-------------|

| Bit   | Description                                       |

|-------|---------------------------------------------------|

| [7:0] | Port Pull-up Enabled                              |

| PPUEx | 0 = The weak pull-up on the port pin is disabled. |

|       | 1 = The weak pull-up on the port pin is enabled.  |

Note: x indicates register bits in the range [7:0].

### Port A–C Input Data Registers

Reading from the Port A–C Input Data registers, shown in Table 22, returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only.

| Bit     | 7    | 7 6 5 4 3 2 1 0                        |  |  |  |  |  |  |  |

|---------|------|----------------------------------------|--|--|--|--|--|--|--|

| Field   | PIN7 | IN7 PIN6 PIN5 PIN4 PIN3 PIN2 PIN1 PIN0 |  |  |  |  |  |  |  |

| RESET   |      | Х                                      |  |  |  |  |  |  |  |

| R/W     | R    |                                        |  |  |  |  |  |  |  |

| Address |      | FD2H, FD6H, FDAH                       |  |  |  |  |  |  |  |

| Table 22. Port A–C Input Data Registers (PxIN) |

|------------------------------------------------|

|------------------------------------------------|

| Bit   | Description                                         |

|-------|-----------------------------------------------------|

| [7:0] | Port Input Data                                     |

| PxIN  | Sampled data from the corresponding port pin input. |

|       | 0 = Input data is logical 0 (Low).                  |

|       | 1 = Input data is logical 1 (High).                 |

| Note: | x indicates register bits in the range [7:0].       |

#### Table 32. IRQ1 Enable High Bit Register (IRQ1ENH)

| Bit     | 7      | 7 6 5 4 3 2 1 0                                        |  |  |  |  |  |  |  |

|---------|--------|--------------------------------------------------------|--|--|--|--|--|--|--|

| Field   | PA7ENH | A7ENH PA6ENH PA5ENH PA4ENH PA3ENH PA2ENH PA1ENH PA0ENH |  |  |  |  |  |  |  |

| RESET   |        | 0                                                      |  |  |  |  |  |  |  |

| R/W     |        | R/W                                                    |  |  |  |  |  |  |  |

| Address |        | FC4H                                                   |  |  |  |  |  |  |  |

| Bit             | Description                                     |

|-----------------|-------------------------------------------------|

| [7:0]<br>PAxENH | Port A Bit[x] Interrupt Request Enable High Bit |

|                 |                                                 |

Note: x indicates register bits in the range [7:0].

#### Table 33. IRQ1 Enable Low Bit Register (IRQ1ENL)

| Bit     | 7      | 7 6 5 4 3 2 1 O |        |        |               |        |        |        |

|---------|--------|-----------------|--------|--------|---------------|--------|--------|--------|

| Field   | PA7ENL | PA6ENL          | PA5ENL | PA4ENL | <b>PA3ENL</b> | PA2ENL | PA1ENL | PA0ENL |

| RESET   |        | 0               |        |        |               |        |        |        |

| R/W     |        | R/W             |        |        |               |        |        |        |

| Address |        | FC5H            |        |        |               |        |        |        |

| Bit             | Description                                    |

|-----------------|------------------------------------------------|

| [7:0]<br>PAxENL | Port A Bit[x] Interrupt Request Enable Low Bit |

Note: x indicates register bits in the range [7:0].

#### Table 39. Timer 0–1 High Byte Register (TxH)

| Bit     | 7   | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|-----|------------|---|---|---|---|---|---|

| Field   |     |            |   | Т | Н |   |   |   |

| RESET   |     | 0          |   |   |   |   |   |   |

| R/W     | R/W |            |   |   |   |   |   |   |

| Address |     | F00H, F08H |   |   |   |   |   |   |

#### Table 40. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7   | 6 | 5 | 4     | 3    | 2 | 1 | 0 |

|---------|-----|---|---|-------|------|---|---|---|

| Field   |     |   |   | Т     | L    |   |   |   |

| RESET   | 0 1 |   |   |       |      | 1 |   |   |

| R/W     | R/W |   |   |       |      |   |   |   |

| Address |     |   |   | F01H, | F09H |   |   |   |

|         |     |   |   |       |      |   |   |   |

| Bit    | Description                                                                          |

|--------|--------------------------------------------------------------------------------------|

| [7:0]  | Timer High and Low Bytes                                                             |

| TH, TL | These 2 bytes, {TMRH[7:0], TMRL[7:0]}, contain the current 16-bit timer count value. |

#### **Timer Reload High and Low Byte Registers**

The Timer 0–1 Reload High and Low Byte (TxRH and TxRL) registers, shown in Tables 41 and 42, store a 16-bit reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte Register are stored in a temporary holding register. When a write to the Timer Reload Low Byte Register occurs, the temporary holding register value is written to the Timer High Byte Register. This operation allows simultaneous updates of the 16-bit Timer reload value.

In COMPARE Mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

| Bit     | 7 | 6 | 5 | 4     | 3    | 2 | 1 | 0 |

|---------|---|---|---|-------|------|---|---|---|

| Field   |   |   |   | TF    | RH   |   |   |   |

| RESET   | 1 |   |   |       |      |   |   |   |

| R/W     |   |   |   | R/    | W    |   |   |   |

| Address |   |   |   | F02H, | F0AH |   |   |   |

#### Table 41. Timer 0–1 Reload High Byte Register (TxRH)

### **UART** Interrupts

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the BRG also functions as a basic timer with interrupt capability.

#### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit Shift Register has shifted the first bit of data out. At this point, the Transmit Data Register can be written with the next character to send. This provides 7 bit periods of latency to load the Transmit Data Register before the Transmit Shift Register completes shifting the current character. Writing to the UART Transmit Data Register clears the TDRE bit to 0.

#### **Receiver Interrupts**

The receiver generates an interrupt when any of the following occurs:

- A data byte is received and is available in the UART Receive Data Register. This interrupt can be disabled independent of the other receiver interrupt sources. The received data interrupt occurs after the receive character is received and placed in the Receive Data Register. Software must respond to this received data available condition before the next character is completely received to avoid an overrun error. In MULTIPRO-CESSOR Mode (MPEN = 1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received.

- An overrun is detected.

- A data framing error is detected.

#### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data Register. The break detect and overrun status bits are not displayed until the valid data is read.

After the valid data has been read, the UART Status 0 Register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data Register contains a data byte. However, because the overrun error occurred, this byte cannot contain valid data and should be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status byte indicating an overrun error, the Receive Data Register must be read again to clear the error bits is the UART Status 0 Register. Updates to the Receive Data Register occur only when the next data word is received.

### **SPI Control Register Definitions**

This section defines the features of the following Serial Peripheral Interface registers.

SPI Data Register: see page 109

SPI Control Register: see page 110

SPI Status Register: see page 111

SPI Mode Register: see page 112

SPI Diagnostic State Register: see page 113

SPI Baud Rate High and Low Byte Registers: see page 114

### **SPI Data Register**

The SPI Data Register, shown in Table 64, stores both the outgoing (transmit) data and the incoming (receive) data. Reads from the SPI Data Register always return the current contents of the 8-bit Shift Register. Data is shifted out starting with bit 7. The last bit received resides in bit position 0.

With the SPI configured as a Master, writing a data byte to this register initiates the data transmission. With the SPI configured as a Slave, writing a data byte to this register loads the shift register in preparation for the next data transfer with the external Master. In either the Master or Slave modes, if a transmission is already in progress, writes to this register are ignored and the Overrun error flag, OVR, is set in the SPI Status Register.

When the character length is less than 8 bits (as set by the NUMBITS field in the SPI Mode Register), the transmit character must be set as *left-justified* in the SPI Data Register. A received character of less than 8 bits is right justified (last bit received is in bit position 0). For example, if the SPI is configured for 4-bit characters, the transmit characters must be written to SPIDATA[7:4] and the received characters are read from SPI-DATA[3:0].

| Field DATA RESET X |   |  |  |  |  |

|--------------------|---|--|--|--|--|

| DECET              |   |  |  |  |  |

|                    | Х |  |  |  |  |

| R/W R/W            |   |  |  |  |  |

| Address F60H       |   |  |  |  |  |

| Table 64.  | SPI Data  | Register   | (SPIDATA)      |

|------------|-----------|------------|----------------|

| 10010 0 11 | or i bata | ittogiotoi | (01 107 (17 () |

| Bit   | Description                   |

|-------|-------------------------------|

| [7:0] | SPI Data                      |

| DATA  | Transmit and/or receive data. |

> ilog Embedded in Life

An IXYS Company

111

### **SPI Status Register**

The SPI Status Register, shown in Table 66, indicates the current state of the SPI. All bits revert to their reset state if the SPIEN bit in the SPICTL Register equals 0.

#### Table 66. SPI Status Register (SPISTAT)

| Bit         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                                                                                                                                                                                                                                                                                                             | 5              | 4                                    | 3             | 2                           | 1    | 0    |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------|---------------|-----------------------------|------|------|--|

| Field       | IRQ                                                                                                                                                                                                                                                                                                                                                                                                                                                     | OVR                                                                                                                                                                                                                                                                                                           | COL            | ABT                                  | Res           | erved                       | TXST | SLAS |  |

| RESET       |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                               |                | 0                                    |               |                             |      | 1    |  |

| R/W         |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W* R                                                                                                                                                                                                                                                                                                        |                |                                      |               |                             |      |      |  |

| Address     |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | F62H                                                                                                                                                                                                                                                                                                          |                |                                      |               |                             |      |      |  |

| Note: *R/   | W = read acce                                                                                                                                                                                                                                                                                                                                                                                                                                           | ess; write a 1                                                                                                                                                                                                                                                                                                | to clear the b | it to 0.                             |               |                             |      |      |  |

| Bit         | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                                                              | Description                                                                                                                                                                                                                                                                                                   |                |                                      |               |                             |      |      |  |

| [7]<br>IRQ  | an SPI Mas<br>Generator i<br>0 = No SPI                                                                                                                                                                                                                                                                                                                                                                                                                 | 1, this bit is<br>ster or Slave<br>s used as a<br>interrupt re                                                                                                                                                                                                                                                |                | . This bit do<br>nerate the S<br>ng. | es not set if | gister is set,<br>SPIEN = 0 |      |      |  |

| [6]<br>OVR  |                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Overrun<br>0 = An overrun error has not occurred.<br>1 = An overrun error has been detected.                                                                                                                                                                                                                  |                |                                      |               |                             |      |      |  |

| [5]<br>COL  | Collision<br>0 = A multimaster collision (mode fault) has not occurred.<br>1 = A multimaster collision (mode fault) has been detected.                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                               |                |                                      |               |                             |      |      |  |

| [4]<br>ABT  | <b>SLAVE Mode Transaction Abort</b><br>This bit is set if the SPI is configured in SLAVE Mode, a transaction is occurring and $\overline{SS}$ deasserts before all bits of a character have been transferred as defined by the NUMBITS field of the SPIMODE Register. The IRQ bit also sets, indicating the transaction has completed.<br>0 = A SLAVE Mode transaction abort has not occurred.<br>1 = A SLAVE Mode transaction abort has been detected. |                                                                                                                                                                                                                                                                                                               |                |                                      |               |                             |      |      |  |

| [3:2]       | Reserved<br>These bits                                                                                                                                                                                                                                                                                                                                                                                                                                  | Reserved<br>These bits are reserved and must be programmed to 00.                                                                                                                                                                                                                                             |                |                                      |               |                             |      |      |  |

| [1]<br>TXST | Transmit Status         0 = No data transmission currently in progress.         1 = Data transmission currently in progress.                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                               |                |                                      |               |                             |      |      |  |

| [0]<br>SLAS | If SPI is end<br>$0 = \overline{SS}$ input<br>$1 = \overline{SS}$ input                                                                                                                                                                                                                                                                                                                                                                                 | 1 = Data transmission currently in progress.<br>Slave Select<br>If SPI is enabled as a Slave, then the following bit settings are true:<br>0 = $\overline{SS}$ input pin is asserted (Low)<br>1 = $\overline{SS}$ input is not asserted (High).<br>If SPI is enabled as a Master, this bit is not applicable. |                |                                      |               |                             |      |      |  |

### Embedded in Life An TIXYS Company 1177

### **SDA and SCL Signals**

$I^2C$  sends all addresses, data and acknowledge signals over the SDA line, most-significant bit first. SCL is the common clock for the  $I^2C$  Controller. When the SDA and SCL pin alternate functions are selected for their respective GPIO ports, the pins are automatically configured for open-drain operation.

The master  $(I^2C)$  is responsible for driving the SCL clock signal, although the clock signal becomes skewed by a slow slave device. During the Low period of the clock, the slave pulls the SCL signal Low to suspend the transaction. The master releases the clock at the end of the Low period and notices that the clock remains Low instead of returning to a High level. When the slave releases the clock, the  $I^2C$  Controller continues the transaction. All data is transferred in bytes and there is no limit to the amount of data transferred in one operation. When transmitting data or acknowledging read data from the slave, the SDA signal changes in the middle of the Low period of SCL and is sampled in the middle of the High period of SCL.

### I<sup>2</sup>C Interrupts

The I<sup>2</sup>C Controller contains four sources of interrupts: Transmit, Receive, Not Acknowledge and Baud Rate Generator. These four interrupt sources are combined into a single interrupt request signal to the interrupt controller. The transmit interrupt is enabled by the IEN and TXI bits of the control register. The Receive and Not Acknowledge interrupts are enabled by the IEN bit of the control register. BRG interrupt is enabled by the BIRQ and IEN bits of the control register.

Not Acknowledge interrupts occur when a Not Acknowledge condition is received from the slave or sent by the I<sup>2</sup>C Controller and neither the start or stop bit is set. The Not Acknowledge event sets the NCKI bit of the I<sup>2</sup>C Status Register and can only be cleared by setting the start or stop bit in the I<sup>2</sup>C Control Register. When this interrupt occurs, the I<sup>2</sup>C Controller waits until either the stop or start bit is set before performing any action. In an ISR, the NCKI bit should always be checked prior to servicing transmit or receive interrupt conditions because it indicates the transaction is being terminated.

Receive interrupts occur when a byte of data has been received by the  $I^2C$  Controller (Master reading data from Slave). This procedure sets the RDRF bit of the  $I^2C$  Status Register. The RDRF bit is cleared by reading the  $I^2C$  Data Register. The RDRF bit is set during the acknowledge phase. The  $I^2C$  Controller pauses after the acknowledge phase until the receive interrupt is cleared before performing any other action.

Transmit interrupts occur when the TDRE bit of the  $I^2C$  Status Register sets and the TXI bit in the  $I^2C$  Control Register is set. Transmit interrupts occur under the following conditions when the Transmit Data Register is empty:

• The I<sup>2</sup>C Controller is enabled

| y | 140 |

|---|-----|

| Bit               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>CEN        | <ul> <li>Conversion Enable</li> <li>0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion has been completed.</li> <li>1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.</li> </ul>                                                                                                                             |

| [6]               | Reserved<br>This bit is reserved and must be programmed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| [5]<br>VREF       | <ul> <li>Voltage Reference</li> <li>0 = Internal reference generator enabled. The V<sub>REF</sub> pin must remain unconnected or capacitively coupled to analog ground (AV<sub>SS</sub>).</li> <li>1 = Internal voltage reference generator disabled. An external voltage reference must be provided through the V<sub>REF</sub> pin.</li> </ul>                                                                                                                                                                          |

| [4]<br>CONT       | <ul> <li>Conversion</li> <li>0 = SINGLE-SHOT conversion. ADC data is output one time at completion of the 5129 system clock cycles.</li> <li>1 = Continuous conversion. ADC data updated every 256 system clock cycles.</li> </ul>                                                                                                                                                                                                                                                                                        |

| [3]<br>ANAIN[3:0] | Analog Input Select<br>These bits select the analog input for conversion. Not all Port pins in this list are available in<br>all packages for Z8 Encore! XP <sup>®</sup> F0822 Series. See the <u>Signal and Pin Descriptions</u> chapter<br>on page 7 for information regarding the port pins available with each package style.<br>Do not enable unavailable analog inputs.<br>0000 = ANA0.<br>0001 = ANA1.<br>0010 = ANA2.<br>0011 = ANA3.<br>0100 = ANA4.<br>0101 = Reserved.<br>011X = Reserved.<br>1XXX = Reserved. |

#### ilog Embedded in Life An TIXYS Company 161

#### **Exiting Debug Mode**

The device exits DEBUG Mode following any of the following operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

- Asserting the RESET pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP Mode initiates a System Reset

### **OCD Data Format**

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 start bit, 8 data bits (least-significant bit first), and 1 stop bit; see Figure 37.

| START         D0         D1         D2         D3         D4         D5         D6         D7         STC | START |

|-----------------------------------------------------------------------------------------------------------|-------|

|-----------------------------------------------------------------------------------------------------------|-------|

#### Figure 37. OCD Data Format

### **OCD** Autobaud Detector/Generator

To run over a range of baud rates (bits per second) with various system clock frequencies, the OCD contains an Autobaud Detector/Generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one start bit plus 7 data bits). The Autobaud Detector measures this period and sets the OCD Baud Rate Generator accordingly.

The Autobaud Detector/Generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation, the maximum recommended baud rate is the system clock frequency divided by 8. The theoretical maximum baud rate is the system clock frequency divided by 4. This theoretical maximum is possible for low-noise designs with clean signals. Table 92 lists minimum and recommended maximum baud rates for sample crystal frequencies.

> ilog mbedded in Life

S Company

171

### **OCD Status Register**

The OCD Status Register, shown in Table 95, reports status information about the current state of the debugger and the system.

#### Table 95. OCD Status Register (OCDSTAT)

| Bit   | 7    | 6    | 5    | 4 | 3 | 2        | 1 | 0 |

|-------|------|------|------|---|---|----------|---|---|

| Field | IDLE | HALT | RPEN |   |   | Reserved |   |   |

| RESET |      |      |      | ( | ) |          |   |   |

| R/W   |      |      |      | F | र |          |   |   |

|       |      |      |      |   |   |          |   |   |

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IDLE | <ul> <li>CPU Idling</li> <li>This bit is set if the part is in DEBUG Mode (DBGMODE is 1), or if a BRK instruction occurred since the last time OCDCTL was written. This can be used to determine if the CPU is running or if it is idling.</li> <li>0 = The eZ8 CPU is running.</li> <li>1 = The eZ8 CPU is either stopped or looping on a BRK instruction.</li> </ul> |

| [6]<br>HALT | HALT Mode       0 = The device is not in HALT Mode.       1 = The device is in HALT Mode.                                                                                                                                                                                                                                                                              |

| [5]<br>RPEN | Read Protect Option Bit Enabled0 = The Read Protect option bit is disabled (1).1 = The Read Protect option bit is enabled (0), disabling many OCD commands.                                                                                                                                                                                                            |

| [4:0]       | Reserved<br>These bits are reserved and must be programmed to 00000.                                                                                                                                                                                                                                                                                                   |

187

ilog<sup>®</sup>

Table 101 provides information about the external RC oscillator electrical characteristics and timing, and Table 102 provides information about the Flash memory electrical characteristics and timing.

|                  |                                                                                                     | T <sub>A</sub> = | –40°C to 1  | 05°C    |       |            |  |

|------------------|-----------------------------------------------------------------------------------------------------|------------------|-------------|---------|-------|------------|--|

| Symbol           | Parameter                                                                                           | Minimum          | Typical*    | Maximum | Units | Conditions |  |

| V <sub>DD</sub>  | Operating Voltage Range                                                                             | 2.70             | -           | -       | V     |            |  |

| R <sub>EXT</sub> | External Resistance from $X_{IN}$ to $V_{DD}$                                                       | 40               | 45          | 200     | kΩ    |            |  |

| C <sub>EXT</sub> | External Capacitance from $X_{IN}$ to $V_{SS}$                                                      | 0                | 20          | 1000    | pF    |            |  |

| F <sub>OSC</sub> | External RC Oscillation<br>Frequency                                                                | -                | -           | 4       | MHz   |            |  |

| 2.7              | hen using the external RC oscill<br>V, but before the power supply<br>as soon as the supply voltage | drops to the v   | oltage brow | •       | •     |            |  |

#### Table 101. External RC Oscillator Electrical Characteristics and Timing

| Table 102. Flash Memory | v Electrical | Characteristics | and Timing |

|-------------------------|--------------|-----------------|------------|

|                         | y Liecuicai  | Characteristics | and mining |

|                                               |         | <sub>DD</sub> = 2.7–3.<br>–40°C to 1 |         |        |                                                                                                                                                                  |

|-----------------------------------------------|---------|--------------------------------------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                     | Minimum | Typical                              | Maximum | Units  | Notes                                                                                                                                                            |

| Flash Byte Read Time                          | 50      | _                                    | _       | μs     |                                                                                                                                                                  |

| Flash Byte Program Time                       | 20      | _                                    | 40      | μs     |                                                                                                                                                                  |

| Flash Page Erase Time                         | 10      | _                                    | _       | ms     |                                                                                                                                                                  |

| Flash Mass Erase Time                         | 200     | -                                    | _       | ms     |                                                                                                                                                                  |

| Writes to Single Address<br>Before Next Erase | -       | -                                    | 2       |        |                                                                                                                                                                  |

| Flash Row Program Time                        | -       | _                                    | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This param-<br>eter is only an issue when<br>bypassing the Flash Controller. |

| Data Retention                                | 100     | -                                    | _       | years  | 25°C                                                                                                                                                             |

| Endurance                                     | 10,000  | -                                    | _       | cycles | Program/erase cycles                                                                                                                                             |

194

### **SPI MASTER Mode Timing**

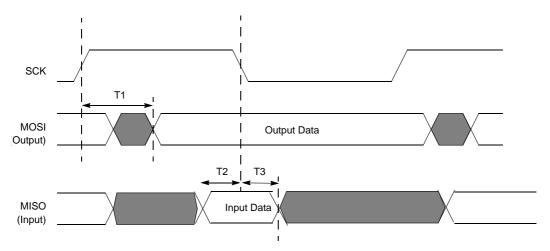

Figure 51 and Table 109 provide timing information for SPI MASTER Mode pins. Timing is shown with SCK rising edge used to source MOSI output data, SCK falling edge used to sample MISO input data. Timing on the SS output pin(s) is controlled by software.

Figure 51. SPI MASTER Mode Timing

|           |                                     | Dela    | y (ns)  |

|-----------|-------------------------------------|---------|---------|

| Parameter | Abbreviation                        | Minimum | Maximum |

| SPI MASTE | R                                   |         |         |

| T.        | SCK Rise to MOSI output Valid Delay | -5      | +5      |

#### Table 109. SPI MASTER Mode Timing

SPI MASTER

T1

SCK Rise to MOSI output Valid Delay

-5

+5

T2

MISO input to SCK (receive edge) Setup Time

20

T3

MISO input to SCK (receive edge) Hold Time

0

198

С

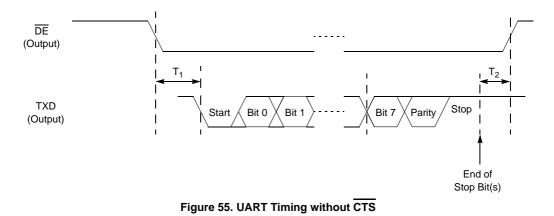

resented here by  $\overline{DE}$ .  $\overline{DE}$  asserts after the UART Transmit Data Register has been written.  $\overline{DE}$  remains asserted for multiple characters as long as the Transmit Data Register is written with the next character before the current character has completed.

|                |                                                | Delay (ns)                 |                                              |  |

|----------------|------------------------------------------------|----------------------------|----------------------------------------------|--|

| Parameter      | Abbreviation                                   | Minimum                    | Maximum                                      |  |

| T <sub>1</sub> | DE Assertion to TXD Falling Edge (Start) Delay | 1 Bit period               | 1 Bit period +<br>1 * X <sub>IN</sub> period |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE Deassertion Delay     | 1 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period                   |  |

Embedded in Life

211

| Assembly     | Symbolic                                                                                                                                           |     | Address<br>Mode |                  | Flags |   |   |   |   |   | Fetch  | Instr. |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|------------------|-------|---|---|---|---|---|--------|--------|

| Mnemonic     | Operation                                                                                                                                          | dst | src             | Code(s)<br>(Hex) | С     | Ζ | S | ۷ | D | н | Cycles | Cycles |

| DECW dst     | dst ← dst – 1                                                                                                                                      | RR  |                 | 80               | -     | * | * | * | - | - | 2      | 5      |

|              |                                                                                                                                                    | IRR |                 | 81               | -     |   |   |   |   |   | 2      | 6      |

| DI           | $IRQCTL[7] \leftarrow 0$                                                                                                                           |     |                 | 8F               | -     | - | - | - | - | - | 1      | 2      |

| DJNZ dst, RA | $dst \leftarrow dst - 1$<br>if dst $\neq 0$<br>PC $\leftarrow$ PC + X                                                                              | r   |                 | 0A-FA            | -     | - | - | - | - | - | 2      | 3      |

| EI           | IRQCTL[7] ← 1                                                                                                                                      |     |                 | 9F               | -     | - | - | - | - | - | 1      | 2      |

| HALT         | HALT Mode                                                                                                                                          |     |                 | 7F               | -     | - | - | - | - | - | 1      | 2      |

| INC dst      | dst ← dst + 1                                                                                                                                      | R   |                 | 20               | -     | * | * | * | - | - | 2      | 2      |

|              |                                                                                                                                                    | IR  |                 | 21               | -     |   |   |   |   | - | 2      | 3      |

|              |                                                                                                                                                    | r   |                 | 0E-FE            | -     |   |   |   |   | - | 1      | 2      |

| INCW dst     | dst ← dst + 1                                                                                                                                      | RR  |                 | A0               | -     | * | * | * | - | - | 2      | 5      |

|              |                                                                                                                                                    | IRR |                 | A1               | -     |   |   |   |   | - | 2      | 6      |

| IRET         | $\begin{array}{l} FLAGS \leftarrow @SP \\ SP \leftarrow SP + 1 \\ PC \leftarrow @SP \\ SP \leftarrow SP + 2 \\ IRQCTL[7] \leftarrow 1 \end{array}$ |     |                 | BF               | *     | * | * | * | * | * | 1      | 5      |

| JP dst       | $PC \gets dst$                                                                                                                                     | DA  |                 | 8D               | -     | - | - | - | - | - | 3      | 2      |

|              |                                                                                                                                                    | IRR |                 | C4               | -     |   |   |   |   | - | 2      | 3      |

| JP cc, dst   | if cc is true<br>PC $\leftarrow$ dst                                                                                                               | DA  |                 | 0D-FD            | -     | - | - | - | - | - | 3      | 2      |

| JR dst       | $PC \gets PC + X$                                                                                                                                  | DA  |                 | 8B               | -     | - | - | - | - | - | 2      | 2      |

| JR cc, dst   | if cc is true<br>PC $\leftarrow$ PC + X                                                                                                            | DA  |                 | 0B-FB            | -     | - | - | - | - | - | 2      | 2      |

#### Table 127. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

248

## Index

### **Numerics**

10-bit ADC 4

### A

absolute maximum ratings 176 AC characteristics 185 ADC 204 architecture 136 automatic power-down 137 block diagram 137 continuous conversion 138 control register 139 control register definitions 139 data high byte register 141 data low bits register 142 electrical characteristics and timing 190 operation 137 single-shot conversion 137 ADCCTL register 139 ADCDH register 141 ADCDL register 142 **ADCX 204** ADD 204 additional symbols 202 address space 14 **ADDX 204** analog signals 11 analog-to-digital converter (ADC) 136 AND 207 **ANDX 207** arithmetic instructions 204 assembly language programming 199 assembly language syntax 200

### В

B 202 b 201 baud rate generator, UART 88 **BCLR 205** binary number suffix 202 BIT 205 bit 201 clear 205 manipulation instructions 205 set 205 set or clear 205 swap 205, 208 test and jump 207 test and jump if non-zero 207 test and jump if zero 207 block diagram 3 block transfer instructions 205 **BRK 207 BSET 205** BSWAP 205, 208 **BTJ 207** BTJNZ 207 **BTJZ 207**

### С

CALL procedure 207 capture mode 68 capture/compare mode 69 cc 201 CCF 206 characteristics, electrical 176 clear 206 clock phase (SPI) 104 **CLR 206** COM 207 compare 68 compare - extended addressing 204 compare mode 68 compare with carry 204 compare with carry - extended addressing 204 complement 207 complement carry flag 205, 206