Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I²C, IrDA, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 11                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0811ph020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links in the table below.

| Date        | Revision<br>Level | Description                                                                                                                                                                                                          | Page                                               |

|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Oct<br>2011 | 18                | Added LDWX information to Load Instructions table, eZ8 CPU Instruction<br>Summary table and to Second Op Code Map after 1FH figure; revised<br>Flash Sector Protect Register description; revised Packaging chapter. | <u>206, 212,</u><br><u>220, 152,</u><br><u>221</u> |

| May<br>2008 | 17                | Removed Flash Microcontrollers from the title throughout the document.                                                                                                                                               | All                                                |

| Feb<br>2008 | 16                | Updated the flag status for BCLR, BIT, and BSET in eZ8 CPU Instruction Summary table.                                                                                                                                | <u>208</u>                                         |

| Dec<br>2007 | 15                | Updated Zilog logo/text, Foreword section. Updated Z8 Encore! 8K Series to Z8 Encore! XP <sup>®</sup> F0822 Series Flash Microcontrollers throughout the document.                                                   | All                                                |

iii

Embedded in Life

n IXYS Company

# Embedded in Life

5

### **10-Bit Analog-to-Digital Converter**

The optional Analog-to-Digital Converter (ADC) converts an analog input signal to a 10bit binary number. The ADC accepts inputs from 2 to 5 different analog input sources.

### UART

The Universal Asynchronous Receiver/Transmitter (UART) is full-duplex and capable of handling asynchronous data transfers. The UART supports 8-bit and 9-bit data modes and selectable parity.

### I<sup>2</sup>C

The Inter-Integrated Circuit ( $I^2C$ ) controller makes the Z8 Encore! XP compatible with the  $I^2C$  protocol. The  $I^2C$  Controller consists of two bidirectional bus lines, a serial data (SDA) line, and a serial clock (SCL) line.

### **Serial Peripheral Interface**

The Serial Peripheral Interface (SPI) allows the Z8 Encore! XP to exchange data between other peripheral devices such as EEPROMs, A/D converters, and ISDN devices. The SPI is a full-duplex, synchronous, and character-oriented channel that supports a four-wire interface.

### Timers

Two 16-bit reloadable timers are used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in One-Shot, Continuous, Gated, Capture, Compare, Capture and Compare, and PWM modes.

### **Interrupt Controller**

Z8 Encore! XP<sup>®</sup> F0822 Series products support up to 18 interrupts. These interrupts consist of 7 internal peripheral interrupts and 11 GPIO pin interrupt sources. The interrupts have 3 levels of programmable interrupt priority.

### **Reset Controller**

Z8 Encore! XP<sup>®</sup> F0822 Series products are reset using the RESET pin, POR, WDT, STOP Mode exit, or VBO warning signal.

ilog Embedded in Life An IXYS Company

| Address (He  | ex) Register Description | Mnemonic | Reset (Hex) | Page No    |

|--------------|--------------------------|----------|-------------|------------|

| Analog-to-D  | igital Converter (ADC)   |          |             |            |

| F70          | ADC Control              | ADCCTL   | 20          | <u>139</u> |

| F71          | Reserved                 | _        | XX          |            |

| F72          | ADC Data High Byte       | ADCD_H   | XX          | <u>141</u> |

| F73          | ADC Data Low Bits        | ADCD_L   | XX          | <u>142</u> |

| F74–FBF      | Reserved                 | —        | XX          |            |

| Interrupt Co | ntroller                 |          |             |            |

| FC0          | Interrupt Request 0      | IRQ0     | 00          | <u>45</u>  |

| FC1          | IRQ0 Enable High Bit     | IRQ0ENH  | 00          | <u>48</u>  |

| FC2          | IRQ0 Enable Low Bit      | IRQ0ENL  | 00          | <u>48</u>  |

| FC3          | Interrupt Request 1      | IRQ1     | 00          | <u>46</u>  |

| FC4          | IRQ1 Enable High Bit     | IRQ1ENH  | 00          | <u>49</u>  |

| FC5          | IRQ1 Enable Low Bit      | IRQ1ENL  | 00          | <u>49</u>  |

| FC6          | Interrupt Request 2      | IRQ2     | 00          | <u>47</u>  |

| FC7          | IRQ2 Enable High Bit     | IRQ2ENH  | 00          | <u>51</u>  |

| FC8          | IRQ2 Enable Low Bit      | IRQ2ENL  | 00          | <u>51</u>  |

| FC9–FCC      | Reserved                 | —        | XX          |            |

| FCD          | Interrupt Edge Select    | IRQES    | 00          | <u>52</u>  |

| FCE          | Reserved                 | —        | 00          |            |

| FCF          | Interrupt Control        | IRQCTL   | 00          | <u>53</u>  |

| GPIO Port A  |                          |          |             |            |

| FD0          | Port A Address           | PAADDR   | 00          | <u>32</u>  |

| FD1          | Port A Control           | PACTL    | 00          | <u>33</u>  |

| FD2          | Port A Input Data        | PAIN     | XX          | <u>38</u>  |

| FD3          | Port A Output Data       | PAOUT    | 00          | <u>39</u>  |

| GPIO Port B  |                          |          |             |            |

| FD4          | Port B Address           | PBADDR   | 00          | <u>32</u>  |

| FD5          | Port B Control           | PBCTL    | 00          | <u>33</u>  |

| FD6          | Port B Input Data        | PBIN     | XX          | <u>38</u>  |

| FD7          | Port B Output Data       | PBOUT    | 00          | <u>39</u>  |

### Table 7. Register File Address Map (Continued)

Note: XX = undefined.

19

### Embedded in Life An TIXYS Company 21

# Reset and Stop Mode Recovery

The Reset Controller within the Z8 Encore! XP<sup>®</sup> F0822 Series controls Reset and Stop Mode Recovery operation. In typical operation, the following events cause a Reset to occur:

- Power-On Reset (POR)

- Voltage Brown-Out

- WDT time-out (when configured through the WDT\_RES option bit to initiate a Reset)

- External **RESET** pin assertion

- On-Chip Debugger initiated Reset (OCDCTL[0] set to 1)

When the Z8 Encore! XP<sup>®</sup> F0822 Series device is in STOP Mode, a Stop Mode Recovery is initiated by any of the following events:

- WDT time-out

- GPIO Port input pin transition on an enabled Stop Mode Recovery source

- DBG pin driven Low

### **Reset Types**

Z8 Encore! XP<sup>®</sup> F0822 Series provides two types of reset operation (System Reset and Stop Mode Recovery). The type of reset is a function of both the current operating mode of the Z8 Encore! XP<sup>®</sup> F0822 Series device and the source of the Reset. Table 8 lists the types of Resets and their operating characteristics.

#### Table 8. Reset and Stop Mode Recovery Characteristics and Latency

| Reset Characteristics and Latency |                                             |         |                                                   |  |  |

|-----------------------------------|---------------------------------------------|---------|---------------------------------------------------|--|--|

| Reset Type                        | <b>Control Registers</b>                    | eZ8 CPU | Reset Latency (Delay)                             |  |  |

| System Reset                      | Reset (as applicable)                       | Reset   | 66 WDT Oscillator cycles + 16 System Clock cycles |  |  |

| Stop Mode<br>Recovery             | Unaffected, except for the WDT_CTL Register | Reset   | 66 WDT Oscillator cycles + 16 System Clock cycles |  |  |

### System Reset

During a System Reset, a Z8 Encore! XP<sup>®</sup> F0822 Series device is held in Reset for 66 cycles of the WDT oscillator followed by 16 cycles of the system clock. At the beginning

In COMPARE Mode, the system clock always provides the timer input. The Compare time is calculated by the following equation:

Compare Mode Time (s) = (Compare Value – Start Value)xPrescale System Clock Frequency (Hz)

#### GATED Mode

In GATED Mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control Register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the Timer Input signal is still asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

Observe the following procedure for configuring a timer for GATED Mode and initiating the count:

- 1. Write to the Timer Control Register to:

- Disable the timer

- Configure the timer for GATED Mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in GATED Mode. After the first timer reset in GATED Mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control Register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

# Universal Asynchronous Receiver/ Transmitter

The Universal Asynchronous Receiver/Transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. Features of the UART include:

- 8-bit asynchronous data transfer

- · Selectable even- and odd-parity generation and checking

- Option of one or two stop bits

- Separate transmit and receive interrupts

- Framing, parity, overrun, and break detection

- Separate transmit and receive enables

- 16-bit Baud Rate Generator

- Selectable MULTIPROCESSOR (9-Bit) Mode with three configurable interrupt schemes

- BRG timer mode

- Driver Enable output for external bus transceivers

### Architecture

The UART consists of three primary functional blocks: Transmitter, Receiver, and Baud Rate Generator. The UART's transmitter and receiver functions independently, but use the same baud rate and data format. Figure 11 displays the UART architecture.

- Read data from the UART Receive Data Register. If operating in MULTIPROCES-SOR (9-Bit) Mode, further actions may be required depending on the Multiprocessor Mode bits MPMD[1:0].

- 7. Return to <u>Step 5</u> to receive additional data.

### **Receiving Data Using Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Observe the following procedure to configure the UART receiver for interruptdriven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt Control registers to enable the UART Receiver interrupt and set the required priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request Register.

- 6. Write to the UART Control 1 Register to enable MULTIPROCESSOR (9-Bit) Mode functions, if appropriate.

- Set the Multiprocessor Mode Select (MPEN) to enable MULTIPROCESSOR Mode.

- Set the Multiprocessor Mode bits, MPMD[1:0], to select the required address matching scheme.

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! XP devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic multiprocessor modes only).

- 8. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if required, and if MULTIPROCESSOR Mode is not enabled, and select either even or odd parity.

- 9. Execute an EI instruction to enable interrupts.

| Bit     | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|---------|---|---|---|----|----|---|---|---|

| Field   |   |   |   | Tک | (D |   |   |   |

| RESET   | Х | Х | Х | Х  | Х  | Х | Х | Х |

| R/W     | W | W | W | W  | W  | W | W | W |

| Address |   |   |   | F4 | ОН | • |   |   |

#### Table 53. UART Transmit Data Register (U0TXD)

| Bit   | Description                                                        |

|-------|--------------------------------------------------------------------|

| [7:0] | Transmit Data                                                      |

| TXD   | UART transmitter data byte to be shifted out through the TXDx pin. |

### **UART Receive Data Register**

Data bytes received through the RXDx pin are stored in the UART Receive Data Register, which is shown in Table 54. The read-only UART Receive Data Register shares a Register File address with the write-only UART Transmit Data Register.

### Table 54. UART Receive Data Register (U0RXD)

| 7    | 6   | 5   | 4     | 3  | 2        | 1                                                                                         | 0                                                                                                   |

|------|-----|-----|-------|----|----------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

|      | RXD |     |       |    |          |                                                                                           |                                                                                                     |

|      | Х   |     |       |    |          |                                                                                           |                                                                                                     |

|      | R   |     |       |    |          |                                                                                           |                                                                                                     |

| F40H |     |     |       |    |          |                                                                                           |                                                                                                     |

|      | 7   | 7 6 | 7 6 5 | R) | RXD<br>R | 7         6         3         4         3         2           RXD           X           R | 7         6         5         4         3         2         1           RXD           X           R |

| Bit   | Description                                |

|-------|--------------------------------------------|

| [7:0] | Receive Data                               |

| RXD   | UART receiver data byte from the RXDx pin. |

### Embedded in Life An IXYS Company

### **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers, shown in Tables 57 and 58, configure the properties of the UART's transmit and receive operations. The UART Control registers must not been written while the UART is enabled.

#### Table 57. UART Control 0 Register (U0CTL0)

| Bit         | 7                                                                                                                 | 6                              | 5              | 4             | 3               | 2              | 1                         | 0            |

|-------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|---------------|-----------------|----------------|---------------------------|--------------|

| Field       | TEN                                                                                                               | REN                            | CTSE           | PEN           | PSEL            | SBRK           | STOP                      | LBEN         |

| RESET       |                                                                                                                   |                                |                | (             | )               |                |                           |              |

| R/W         |                                                                                                                   |                                |                | R/            | W               |                |                           |              |

| Address     |                                                                                                                   |                                |                | F4            | 2H              |                |                           |              |

| Bit         | Descriptio                                                                                                        | n                              |                |               |                 |                |                           |              |

| [7]         | Transmit E                                                                                                        |                                |                |               |                 |                |                           |              |

| TEN         |                                                                                                                   | ables or disa                  | bles the trar  | nsmitter. The | e enable is a   | lso controlle  | ed by the $\overline{CT}$ | S signal     |

|             | and the CT                                                                                                        | SE bit. If the                 | CTS signal     |               |                 |                |                           | 0            |

|             |                                                                                                                   | itter disable<br>itter enable  |                |               |                 |                |                           |              |

| [0]         | Receive Er                                                                                                        |                                | J.             |               |                 |                |                           |              |

| [6]<br>REN  |                                                                                                                   | n <b>able</b><br>ables or disa | bles the rec   | eiver         |                 |                |                           |              |

| 11211       | 0 = Receive                                                                                                       |                                |                |               |                 |                |                           |              |

|             | 1 = Receive                                                                                                       | er enabled.                    |                |               |                 |                |                           |              |

| [5]         |                                                                                                                   |                                | <i></i>        |               |                 |                |                           |              |

| CTSE        |                                                                                                                   | S signal has                   |                |               |                 | ntrol from the | e transmitter             |              |

| [4]         | Parity Ena                                                                                                        |                                |                | olgrial do al |                 |                |                           | ·            |

| PEN         |                                                                                                                   | ables or disa                  | bles parity. I | Even or odd   | is determine    | ed by the PS   | SEL bit. This             | bit is over- |

|             | ,                                                                                                                 | ne MPEN bit                    |                |               |                 |                |                           |              |

|             | 0 = Parity is<br>1 = The training                                                                                 |                                | ds data with   | an addition   | al parity bit : | and the rece   | eiver receive             | s an addi-   |

|             | 1 = The transmitter sends data with an additional parity bit and the receiver receives an a<br>tional parity bit. |                                |                |               |                 |                |                           |              |

| [3]         | Parity Sele                                                                                                       |                                |                |               |                 |                |                           |              |

| PSEL        | 0 = Even parity is transmitted and expected on all received data.                                                 |                                |                |               |                 |                |                           |              |

| [0]         | 1 = Odd parity is transmitted and expected on all received data. Send Break                                       |                                |                |               |                 |                |                           |              |

| [2]<br>SBRK |                                                                                                                   | κ<br>ises or breał             | ks data trans  | mission by    | forcina the T   | ransmit data   | a output to 0             | . Sending a  |

|             | break interr                                                                                                      | upts any tra                   | nsmission ir   | n progress, s | so ensure that  | at the transn  | nitter has fin            | ished send-  |

|             |                                                                                                                   | fore setting                   |                |               |                 |                |                           |              |

|             |                                                                                                                   | easserted. S                   |                |               | uration of the  | e break and    | the duration              | l of any     |

|             | 0 = No brea                                                                                                       |                                | e .onoming t   | broan         |                 |                |                           |              |

|             | 1 = The out                                                                                                       | tput of the tr                 | ansmitter is   | zero.         |                 |                |                           |              |

#### ilog° Embedded in Life An∎IXYS Company

| Bit         | Description (Continued)                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------|

| [1]<br>STOP | Stop Bit Select<br>0 = The transmitter sends one stop bit.<br>1 = The transmitter sends two stop bits. |

| [0]<br>LBEN | Loop Back Enable<br>0 = Normal operation.<br>1 = All transmitted data is looped back to the receiver.  |

#### Table 58. UART Control 1 Register (U0CTL1)

| Bit     | 7       | 6    | 5       | 4    | 3     | 2      | 1      | 0    |

|---------|---------|------|---------|------|-------|--------|--------|------|

| Field   | MPMD[1] | MPEN | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |

| RESET   |         | 0    |         |      |       |        |        |      |

| R/W     |         | R/W  |         |      |       |        |        |      |

| Address |         | F43H |         |      |       |        |        |      |

| Bit                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7,5]<br>MPMD[1,0] | <ul> <li>00 = The UART generates an interrupt request on all received bytes (data and address).</li> <li>01 = The UART generates an interrupt request only on received address bytes.</li> <li>10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs.</li> <li>11 = The UART generates an interrupt request on all received data bytes for which the most</li> </ul> |

| [6]<br>MPEN        | recent address byte matched the value in the Address Compare Register.<br>Multiprocessor (9-Bit) Enable<br>This bit is used to enable MULTIPROCESSOR (9-Bit) Mode.<br>0 = Disable MULTIPROCESSOR (9-Bit) Mode.<br>1 = Enable MULTIPROCESSOR (9-Bit) Mode.                                                                                                                                                                                                                                                           |

| [4]<br>MPBT        | Multiprocessor Bit TransmitThis bit is applicable only when MULTIPROCESSOR (9-Bit) Mode is enabled.0 = Send a 0 in the multiprocessor bit location of the data stream (9th bit).1 = Send a 1 in the multiprocessor bit location of the data stream (9th bit).                                                                                                                                                                                                                                                       |

| [3]<br>DEPOL       | Driver Enable Polarity<br>0 = DE signal is Active High.<br>1 = DE signal is Active Low.                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### ILO Embedded in Life IXYS Company 119

### **Start and Stop Conditions**

The Master ( $I^2C$ ) drives all Start and Stop signals and initiates all transactions. To start a transaction, the  $I^2C$  Controller generates a start condition by pulling the SDA signal Low while SCL is High. To complete a transaction, the  $I^2C$  Controller generates a Stop condition by creating a Low-to-High transition of the SDA signal while the SCL signal is High. The start and stop bits in the  $I^2C$  Control Register control the sending of start and stop conditions. A Master is also allowed to end one transaction and begin a new one by issuing a restart. This restart issuance is accomplished by setting the start bit at the end of a transaction rather than setting the stop bit.

**Note:** The start condition is not sent until the start bit is set and data has been written to the I<sup>2</sup>C Data Register.

### Master Write and Read Transactions

The following sections provide Zilog's recommended procedure for performing  $I^2C$  write and read transactions from the  $I^2C$  Controller (Master) to slave  $I^2C$  devices. In general, software should rely on the TDRE, RDRF and NCKI bits of the status register (these bits generate interrupts) to initiate software actions. When using interrupts or DMA, the TXI bit is set to start each transaction and cleared at the end of each transaction to eliminate a *trailing* transmit interrupt.

**Caution:** Caution should be used in using the ACK status bit within a transaction because it is difficult for software to tell when it is updated by hardware.

When writing data to a slave, the  $I^2C$  pauses at the beginning of the Acknowledge cycle if the data register has not been written with the next value to be sent (TDRE bit in the  $I^2C$ Status Register equal to 1). In this scenario where software is not keeping up with the  $I^2C$ bus (TDRE asserted longer than one byte time), the Acknowledge clock cycle for byte *n* is delayed until the data register is written with byte n+1, and appears to be grouped with the data clock cycles for byte n+1. If either the start or stop bit is set, the  $I^2C$  does not pause prior to the Acknowledge cycle because no additional data is sent.

When a Not Acknowledge condition is received during a write (either during the address or data phases), the I<sup>2</sup>C Controller generates the Not Acknowledge interrupt (NCKI = 1) and pause until either the stop or start bit is set. Unless the Not Acknowledge was received on the last byte, the data register will already have been written with the next address or data byte to send. In this case the FLUSH bit of the control register should be set at the same time the stop or start bit is set to remove the stale transmit data and enable subsequent transmit interrupts.

174

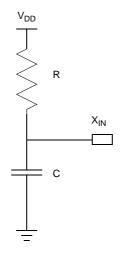

### **Oscillator Operation with an External RC Network**

The External RC oscillator mode is applicable to timing insensitive applications. Figure 39 displays a recommended configuration for connection with an external resistorcapacitor (RC) network.

Figure 39. Connecting the On-Chip Oscillator to an External RC Network

An external resistance value of 45 k $\Omega$  is recommended for oscillator operation with an external RC network. The minimum resistance value to ensure operation is 40 k $\Omega$ . The typical oscillator frequency can be estimated from the values of the resistor (*R* in k $\Omega$ ) and capacitor (*C* in pF) elements using the below equation:

Oscillator Frequency (kHz) =

$$\frac{1 \times 10^{6}}{(0.4 \times R \times C) + (4 \times C)}$$

Figure 40 displays the typical  $(3.3 \text{ V} \text{ and } 25^{\circ}\text{C})$  oscillator frequency as a function of the capacitor (*C* in pF) employed in the RC network assuming a 45 k $\Omega$  external resistor. For very small values of C, the parasitic capacitance of the oscillator X<sub>IN</sub> pin and the printed circuit board should be included in the estimation of the oscillator frequency.

It is possible to operate the RC oscillator using only the parasitic capacitance of the package and printed circuit board. To minimize sensitivity to external parasites, external capacitance values in excess of 20pF are recommended.

#### 186

ilog<sup>®</sup>

### **On-Chip Peripheral AC and DC Electrical Characteristics**

Table 100 provides information about the Power-On Reset and Voltage Brown-Out electrical characteristics.

| Table 100. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing |  |

|---------------------------------------------------------------------------------------|--|

|---------------------------------------------------------------------------------------|--|

|                   |                                                                             | T <sub>A</sub> = | –40°C to 1 | 05°C           |    |                                                                                                       |  |  |

|-------------------|-----------------------------------------------------------------------------|------------------|------------|----------------|----|-------------------------------------------------------------------------------------------------------|--|--|

| Symbol            | Parameter                                                                   | Minimum          | Typical*   | pical* Maximum |    | Conditions                                                                                            |  |  |

| V <sub>POR</sub>  | Power-On Reset<br>Voltage Threshold                                         | 2.15             | 2.40       | 2.60           | V  | $V_{DD} = V_{POR}$                                                                                    |  |  |

| V <sub>VBO</sub>  | Voltage Brown-Out<br>Reset Voltage<br>Threshold                             | 2.05             | 2.30       | 2.55           | V  | $V_{DD} = V_{VBO}$                                                                                    |  |  |

|                   | V <sub>POR</sub> to V <sub>VBO</sub> hys-<br>teresis                        | 50               | 100        | -              | mV |                                                                                                       |  |  |

|                   | Starting V <sub>DD</sub> voltage to ensure valid POR                        | -                | $V_{SS}$   | -              | V  |                                                                                                       |  |  |

| T <sub>ANA</sub>  | POR Analog Delay                                                            | _                | 50         | _              | μs | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |  |  |

| T <sub>POR</sub>  | POR Digital Delay                                                           | -                | 5.0        | -              | ms | 50 WDT Oscillator cycles<br>(10kHz) + 16 System Clock<br>cycles (20MHz)                               |  |  |

| Т <sub>VBO</sub>  | Voltage Brown-Out<br>Pulse Rejection<br>Period                              | -                | 10         | _              | μs | V <sub>DD</sub> < V <sub>VBO</sub> to generate a<br>Reset.                                            |  |  |

| T <sub>RAMP</sub> | Time for VDD to transition from $V_{SS}$ to $V_{POR}$ to ensure valid Reset | 0.10             | _          | 100            | ms |                                                                                                       |  |  |

.

Embedded in Life

Table 103 lists Reset and Stop Mode Recovery pin timing data; Table 104 lists Watchdog Timer Electrical Characteristics and Timing data.

|                    |                                                  | T <sub>A</sub> = | -40°C to 1 | 05°C    |                  |                                                                 |

|--------------------|--------------------------------------------------|------------------|------------|---------|------------------|-----------------------------------------------------------------|

| Symbol             | Parameter                                        | Minimum          | Typical*   | Maximum | Units            | Conditions                                                      |

| T <sub>RESET</sub> | Reset pin assertion to initiate a System Reset   | 4                | -          | -       | T <sub>CLK</sub> | Not in STOP Mode.<br>T <sub>CLK</sub> = System Clock<br>period. |

| T <sub>SMR</sub>   | Stop Mode Recovery pin<br>Pulse Rejection Period | 10               | 20         | 40      | ns               | RESET, DBG and<br>GPIO pins configured<br>as SMR sources.       |

#### Table 103. Reset and Stop Mode Recovery Pin Timing

| Table 104. | Watchdog | Timer Electrica | I Characterist | ics and Timing |  |

|------------|----------|-----------------|----------------|----------------|--|

|            |          |                 |                |                |  |

. . .

\_--

|                  |                                                         |         | <sub>D</sub> = 2.7–3.<br>–40°C to 1 |         |       |            |

|------------------|---------------------------------------------------------|---------|-------------------------------------|---------|-------|------------|

| Symbol           | Parameter                                               | Minimum | Typical                             | Maximum | Units | Conditions |

| F <sub>WDT</sub> | WDT Oscillator Frequency                                | 5       | 10                                  | 20      | kHz   |            |

| I <sub>WDT</sub> | WDT Oscillator Current including internal RC oscillator | -       | < 1                                 | 5       | μA    |            |

ilog<sup>°</sup> Embedded in Life

190

Table 105 lists ADC electrical characteristics and timing data.

| Table 105. Analog-to-Digital Converter Electrical Characteristics and Timing |

|------------------------------------------------------------------------------|

|------------------------------------------------------------------------------|

|                   |                                                                                 | V <sub>D</sub><br>T <sub>A</sub> = | <sub>D</sub> = 3.0–3.<br>–40°C to 1 | 6 V<br>105°C     |                                                                      |                                                                                                                                                                |  |  |

|-------------------|---------------------------------------------------------------------------------|------------------------------------|-------------------------------------|------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol            | Parameter                                                                       | Minimum                            | Typical                             | Maximum          | Units                                                                | Conditions                                                                                                                                                     |  |  |

|                   | Resolution                                                                      | 10                                 | -                                   | -                | bits                                                                 | External V <sub>REF</sub> = 3.0V                                                                                                                               |  |  |

|                   | Differential Nonlinearity (DNL)                                                 | -0.25                              | -                                   | 0.25             | lsb                                                                  | Guaranteed by design                                                                                                                                           |  |  |

|                   | Integral Nonlinearity<br>(INL)                                                  | -2.0                               | -                                   | 2.0              | lsb                                                                  | External $V_{REF} = 3.0 V$                                                                                                                                     |  |  |

|                   | DC Offset Error                                                                 | -35                                | -                                   | 25               | mV                                                                   | 80-pin QFP and 64-pin<br>LQFP packages.                                                                                                                        |  |  |

| V <sub>REF</sub>  | Internal Reference<br>Voltage                                                   | 1.9                                | 2.0                                 | 2.4              | V                                                                    | $V_{DD} = 3.0-3.6V$<br>$T_A = -40^{\circ}C \text{ to } 105^{\circ}C$                                                                                           |  |  |

| VC <sub>REF</sub> | Voltage Coefficient of – 78 –<br>Internal Reference<br>Voltage                  |                                    | -                                   | mV/V             | $V_{\text{REF}}$ variation as a function of $\text{AV}_{\text{DD}}.$ |                                                                                                                                                                |  |  |

| TC <sub>REF</sub> | Temperature<br>Coefficient of Internal<br>Reference Voltage                     | -                                  | 1                                   | -                | mV/°C                                                                |                                                                                                                                                                |  |  |

|                   | Single-Shot<br>Conversion Period                                                |                                    | 5129                                |                  | cycles                                                               | System clock cycles                                                                                                                                            |  |  |

|                   | Continuous Conversion<br>Period                                                 |                                    | 256                                 |                  | cycles                                                               | System clock cycles                                                                                                                                            |  |  |

| R <sub>S</sub>    | Analog Source<br>Impedance                                                      | -                                  | -                                   | 150              | Ω                                                                    | Recommended                                                                                                                                                    |  |  |

| Zin               | Input Impedance                                                                 |                                    | 150                                 |                  | ΚΩ                                                                   | 20MHz system clock.<br>Input impedance<br>increases with lower sys-<br>tem clock frequency.                                                                    |  |  |

| V <sub>REF</sub>  | External Reference<br>Voltage                                                   |                                    |                                     | AV <sub>DD</sub> | V                                                                    | $AV_{DD} \le V_{DD}$ . When<br>using an external refer-<br>ence voltage, decoupling<br>capacitance should be<br>placed from V <sub>REF</sub> to<br>$AV_{SS}$ . |  |  |

| I <sub>REF</sub>  | Current draw into V <sub>REF</sub><br>pin when driving with<br>external source. |                                    | 25.0                                | 40.0             | μA                                                                   |                                                                                                                                                                |  |  |

207

| Mnemonic | Operands | Instruction                                       |

|----------|----------|---------------------------------------------------|

| AND      | dst, src | Logical AND                                       |

| ANDX     | dst, src | Logical AND using Extended Addressing             |

| COM      | dst      | Complement                                        |

| OR       | dst, src | Logical OR                                        |

| ORX      | dst, src | Logical OR using Extended Addressing              |

| XOR      | dst, src | Logical Exclusive OR                              |

| XORX     | dst, src | Logical Exclusive OR using Extended<br>Addressing |

#### Table 124. Logical Instructions

#### Table 125. Program Control Instructions

| Operands        | Instruction                                                                                                         |

|-----------------|---------------------------------------------------------------------------------------------------------------------|

| _               | On-Chip Debugger Break                                                                                              |

| p, bit, src, DA | Bit Test and Jump                                                                                                   |

| bit, src, DA    | Bit Test and Jump if Non-Zero                                                                                       |

| bit, src, DA    | Bit Test and Jump if Zero                                                                                           |

| dst             | Call Procedure                                                                                                      |

| dst, src, RA    | Decrement and Jump Non-Zero                                                                                         |

| —               | Interrupt Return                                                                                                    |

| dst             | Jump                                                                                                                |

| dst             | Jump Conditional                                                                                                    |

| DA              | Jump Relative                                                                                                       |

| DA              | Jump Relative Conditional                                                                                           |

| —               | Return                                                                                                              |

| vector          | Software Trap                                                                                                       |

|                 | <br>p, bit, src, DA<br>bit, src, DA<br>dst, src, DA<br>dst<br>dst, src, RA<br><br>dst<br>dst<br>dst<br>DA<br>DA<br> |

|          |                         |                           |                              |                                |                            |                             | Lo                            | ower Nil                       | oble (He                      | x)                             |                            |                   |                           |                           |                  |                           |

|----------|-------------------------|---------------------------|------------------------------|--------------------------------|----------------------------|-----------------------------|-------------------------------|--------------------------------|-------------------------------|--------------------------------|----------------------------|-------------------|---------------------------|---------------------------|------------------|---------------------------|

|          | 0                       | 1                         | 2                            | 3                              | 4                          | 5                           | 6                             | 7                              | 8                             | 9                              | А                          | В                 | С                         | D                         | Е                | F                         |

| 0        | 1.2<br>BRK              | 2.2<br>SRP<br>IM          | 2.3<br>ADD<br>r1,r2          | 2.4<br>ADD<br>r1,lr2           | 3.3<br><b>ADD</b><br>R2,R1 | 3.4<br>ADD<br>IR2,R1        | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br>ADD<br>IR1,IM           | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br>JR<br>cc,X | 2.2<br><b>LD</b><br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP                |

| 1        | 2.2<br>RLC<br>R1        | 2.3<br>RLC<br>IR1         | 2.3<br>ADC<br>r1,r2          | 2.4<br>ADC<br>r1,lr2           | 3.3<br><b>ADC</b><br>R2,R1 | 3.4<br>ADC<br>IR2,R1        | 3.3<br>ADC<br>R1,IM           | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                   |                           |                           |                  | See 2nd<br>Op Code<br>Map |

| 2        | 2.2<br>INC<br>R1        | 2.3<br>INC<br>IR1         | 2.3<br>SUB<br>r1,r2          | 2.4<br>SUB<br>r1,lr2           | 3.3<br><b>SUB</b><br>R2,R1 | 3.4<br>SUB<br>IR2,R1        | 3.3<br><b>SUB</b><br>R1,IM    | 3.4<br>SUB<br>IR1,IM           | 4.3<br><b>SUBX</b><br>ER2,ER1 | 4.3<br>SUBX<br>IM,ER1          |                            |                   |                           |                           |                  |                           |

| 3        | 2.2<br><b>DEC</b><br>R1 | 2.3<br>DEC<br>IR1         | 2.3<br>SBC<br>r1,r2          | 2.4<br>SBC<br>r1,lr2           | 3.3<br><b>SBC</b><br>R2,R1 | 3.4<br>SBC<br>IR2,R1        | 3.3<br><b>SBC</b><br>R1,IM    | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br>SBCX<br>IM,ER1          |                            |                   |                           |                           |                  |                           |

| 4        | 2.2<br><b>DA</b><br>R1  | 2.3<br><b>DA</b><br>IR1   | 2.3<br><b>OR</b><br>r1,r2    | 2.4<br><b>OR</b><br>r1,lr2     | 3.3<br><b>OR</b><br>R2,R1  | 3.4<br><b>OR</b><br>IR2,R1  | 3.3<br><b>OR</b><br>R1,IM     | 3.4<br><b>OR</b><br>IR1,IM     | 4.3<br><b>ORX</b><br>ER2,ER1  | 4.3<br><b>ORX</b><br>IM,ER1    |                            |                   |                           |                           |                  |                           |

| 5        | 2.2<br><b>POP</b><br>R1 | 2.3<br><b>POP</b><br>IR1  | 2.3<br>AND<br>r1,r2          | 2.4<br><b>AND</b><br>r1,lr2    | 3.3<br><b>AND</b><br>R2,R1 | 3.4<br>AND<br>IR2,R1        | 3.3<br><b>AND</b><br>R1,IM    | 3.4<br>AND<br>IR1,IM           | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1          |                            |                   |                           |                           |                  | 1.2<br>WDT                |

| 6        | 2.2<br>COM<br>R1        | 2.3<br>COM<br>IR1         | 2.3<br><b>TCM</b><br>r1,r2   | 2.4<br><b>TCM</b><br>r1,lr2    | 3.3<br><b>TCM</b><br>R2,R1 | 3.4<br><b>TCM</b><br>IR2,R1 | 3.3<br><b>TCM</b><br>R1,IM    | 3.4<br><b>TCM</b><br>IR1,IM    | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                   |                           |                           |                  | 1.2<br>STOP               |

| <b>7</b> | 2.2<br>PUSH<br>R2       | 2.3<br><b>PUSH</b><br>IR2 | 2.3<br><b>TM</b><br>r1,r2    | 2.4<br><b>TM</b><br>r1,lr2     | 3.3<br><b>TM</b><br>R2,R1  | 3.4<br><b>TM</b><br>IR2,R1  | 3.3<br><b>TM</b><br>R1,IM     | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                   |                           |                           |                  | 1.2<br>HALT               |

| 8        | 2.5<br>DECW<br>RR1      | 2.6<br>DECW<br>IRR1       | 2.5<br>LDE<br>r1,lrr2        | 2.9<br>LDEI<br>Ir1,Irr2        | 3.2<br>LDX<br>r1,ER2       | 3.3<br>LDX<br>Ir1,ER2       | 3.4<br>LDX<br>IRR2,R1         | 3.5<br>LDX<br>IRR2,IR1         | 3.4<br>LDX<br>r1,rr2,X        | 3.4<br>LDX<br>rr1,r2,X         |                            |                   |                           |                           |                  | 1.2<br>DI                 |

| 9        | 2.2<br><b>RL</b><br>R1  | 2.3<br><b>RL</b><br>IR1   | 2.5<br>LDE<br>r2,Irr1        | 2.9<br>LDEI<br>Ir2,Irr1        | 3.2<br>LDX<br>r2,ER1       | 3.3<br>LDX<br>Ir2,ER1       | 3.4<br>LDX<br>R2,IRR1         | 3.5<br>LDX<br>IR2,IRR1         | 3.3<br><b>LEA</b><br>r1,r2,X  | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                   |                           |                           |                  | 1.2<br>El                 |

| А        | 2.5<br>INCW<br>RR1      | 2.6<br>INCW<br>IRR1       | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1  | 3.4<br><b>CP</b><br>IR2,R1  | 3.3<br><b>CP</b><br>R1,IM     | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                   |                           |                           |                  | 1.4<br>RET                |

| в        | 2.2<br>CLR<br>R1        | 2.3<br>CLR<br>IR1         | 2.3<br>XOR<br>r1,r2          | 2.4<br><b>XOR</b><br>r1,lr2    | 3.3<br><b>XOR</b><br>R2,R1 | 3.4<br>XOR<br>IR2,R1        | 3.3<br><b>XOR</b><br>R1,IM    | 3.4<br><b>XOR</b><br>IR1,IM    | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br>XORX<br>IM,ER1          |                            |                   |                           |                           |                  | IRET                      |

| С        | 2.2<br><b>RRC</b><br>R1 | 2.3<br>RRC<br>IR1         | 2.5<br><b>LDC</b><br>r1,lrr2 | 2.9<br><b>LDCI</b><br>lr1,lrr2 | 2.3<br><b>JP</b><br>IRR1   | 2.9<br>LDC<br>lr1,lrr2      |                               | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           |                                |                            |                   |                           |                           |                  | 1.2<br>RCF                |

| D        | 2.2<br>SRA<br>R1        | 2.3<br>SRA<br>IR1         | 2.5<br>LDC<br>r2,Irr1        | 2.9<br><b>LDCI</b><br>lr2,lrr1 | 2.6<br>CALL<br>IRR1        | 2.2<br><b>BSWAP</b><br>R1   | DA                            | 3.4<br><b>LD</b><br>r2,r1,X    | 3.2<br><b>POPX</b><br>ER1     |                                |                            |                   |                           |                           |                  | 1.2<br>SCF                |

| Е        | 2.2<br><b>RR</b><br>R1  | 2.3<br><b>RR</b><br>IR1   | 2.2<br><b>BIT</b><br>p,b,r1  | 2.3<br><b>LD</b><br>r1,lr2     | 3.2<br><b>LD</b><br>R2,R1  | 3.3<br>LD<br>IR2,R1         | 3.2<br><b>LD</b><br>R1,IM     | 3.3<br><b>LD</b><br>IR1,IM     | 4.2<br>LDX<br>ER2,ER1         | 4.2<br>LDX<br>IM,ER1           |                            |                   |                           |                           |                  | 1.2<br>CCF                |

| F        | 2.2<br>SWAP<br>R1       | 2.3<br>SWAP<br>IR1        | 2.6<br>TRAP<br>Vector        | 2.3<br>LD<br>lr1,r2            | 2.8<br>MULT<br>RR1         | 3.3<br><b>LD</b><br>R2,IR1  | 3.3<br><b>BTJ</b><br>p,b,r1,X | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               |                                | ¥                          | <b>↓</b>          | <b>↓</b>                  | <b>↓</b>                  | <b>V</b>         |                           |

Figure 58. First Op Code Map

Upper Nibble (Hex)

#### ilog Embedded in Life An∎IXYS Company

# **Ordering Information**

Order your Z8 Encore! XP<sup>®</sup> F0822 Series products from Zilog using the part numbers shown in Table 129. For more information about ordering, please consult your local Zilog sales office. The <u>Sales Location page</u> on the Zilog website lists all regional offices.

| Table 125. 20 Encore: AT 1 0000 Certes of defining matrix |              |        |           |            |                     |                     |     |     |                 |                     |

|-----------------------------------------------------------|--------------|--------|-----------|------------|---------------------|---------------------|-----|-----|-----------------|---------------------|

| Part Number                                               | Flash        | RAM    | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | l²C | SPI | UARTs with IrDA | Description         |

| Z8F08xx with 8KB Flas                                     |              | -      | to-Di     | gital      | Conv                | /erte               | r   |     |                 |                     |

| Standard Temperature                                      |              |        |           |            |                     |                     |     |     |                 |                     |

| Z8F0821HH020SG                                            | 8KB          | 1KB    | 11        | 16         | 2                   | 2                   | 1   | 0   | 1               | SSOP 20-pin package |

| Z8F0821PH020SG                                            | 8KB          | 1KB    | 11        | 16         | 2                   | 2                   | 1   | 0   | 1               | PDIP 20-pin package |

| Z8F0822SJ020SG                                            | 8KB          | 1KB    | 19        | 19         | 2                   | 5                   | 1   | 1   | 1               | SOIC 28-pin package |

| Z8F0822PJ020SG                                            | 8KB          | 1KB    | 19        | 19         | 2                   | 5                   | 1   | 1   | 1               | PDIP 28-pin package |

| Extended Temperature                                      | e: –40° to + | -105°C |           |            |                     |                     |     |     |                 |                     |

| Z8F0821HH020EG                                            | 8KB          | 1KB    | 11        | 16         | 2                   | 2                   | 1   | 0   | 1               | SSOP 20-pin package |

| Z8F0821PH020EG                                            | 8KB          | 1KB    | 11        | 16         | 2                   | 2                   | 1   | 0   | 1               | PDIP 20-pin package |

| Z8F0822SJ020EG                                            | 8KB          | 1KB    | 19        | 19         | 2                   | 5                   | 1   | 1   | 1               | SOIC 28-pin package |

| Z8F0822PJ020EG                                            | 8KB          | 1KB    | 19        | 19         | 2                   | 5                   | 1   | 1   | 1               | PDIP 28-pin package |

| Z8F08xx with 8KB Flas                                     | sh           |        |           |            |                     |                     |     |     |                 |                     |

| Standard Temperature: (                                   | 0°C to 70°C  | )      |           |            |                     |                     |     |     |                 |                     |

| Z8F0811HH020SG                                            | 8KB          | 1KB    | 11        | 16         | 2                   | 0                   | 1   | 0   | 1               | SSOP 20-pin package |

| Z8F0811PH020SG                                            | 8KB          | 1KB    | 11        | 16         | 2                   | 0                   | 1   | 0   | 1               | PDIP 20-pin package |

| Z8F0812SJ020SG                                            | 8KB          | 1KB    | 19        | 19         | 2                   | 0                   | 1   | 1   | 1               | SOIC 28-pin package |

| Z8F0812PJ020SG                                            | 8KB          | 1KB    | 19        | 19         | 2                   | 0                   | 1   | 1   | 1               | PDIP 28-pin package |

| Extended Temperature                                      | e: -40°C to  | +105°C | ;         |            |                     |                     |     |     |                 |                     |

| Z8F0811HH020EG                                            | 8KB          | 1KB    | 11        | 16         | 2                   | 0                   | 1   | 0   | 1               | SSOP 20-pin package |

| Z8F0811PH020EG                                            | 8KB          | 1KB    | 11        | 16         | 2                   | 0                   | 1   | 0   | 1               | PDIP 20-pin package |

| Z8F0812SJ020EG                                            | 8KB          | 1KB    | 19        | 19         | 2                   | 0                   | 1   | 1   | 1               | SOIC 28-pin package |

| Z8F0812PJ020EG                                            | 8KB          | 1KB    | 19        | 19         | 2                   | 0                   | 1   | 1   | 1               | PDIP 28-pin package |

#### Table 129. Z8 Encore! XP F0830 Series Ordering Matrix

PS022518-1011

Embedded in Life

| <b>^</b> | ^ | •  |  |

|----------|---|----|--|

| ,        |   | ٠. |  |

|          |   |    |  |

| Part Number                                                | Flash                                       | RAM   | I/O Lines | Interrupts | 16-Bit Timers w/PWM | 10-Bit A/D Channels | I <sup>2</sup> C | SPI | UARTs with IrDA | Description         |  |

|------------------------------------------------------------|---------------------------------------------|-------|-----------|------------|---------------------|---------------------|------------------|-----|-----------------|---------------------|--|

| Z8F04xx with 4KB Flash, 10-Bit Analog-to-Digital Converter |                                             |       |           |            |                     |                     |                  |     |                 |                     |  |

| Standard Temperature:                                      |                                             |       |           |            |                     |                     |                  | -   |                 | 0000000             |  |

| Z8F0421HH020SG                                             | 4KB                                         | 1KB   | 11        | 16         | 2                   | 2                   | 1                | 0   | 1               | SSOP 20-pin package |  |

| Z8F0421PH020SG                                             | 4KB                                         | 1KB   | 11        | 16         | 2                   | 2                   | 1                | 0   | 1               | PDIP 20-pin package |  |

| Z8F0422SJ020SG                                             | 4KB                                         | 1KB   | 19        | 19         | 2                   | 5                   | 1                | 1   | 1               | SOIC 28-pin package |  |

| Z8F0422PJ020SG                                             | 4KB                                         | 1KB   | 19        | 19         | 2                   | 5                   | 1                | 1   | 1               | PDIP 28-pin package |  |

| Extended Temperature:                                      | –40°C to                                    |       |           |            |                     |                     |                  |     |                 |                     |  |

| Z8F0421HH020EG                                             | 4KB                                         | 1KB   | 11        | 16         | 2                   | 2                   | 1                | 0   | 1               | SSOP 20-pin package |  |

| Z8F0421PH020EG                                             | 4KB                                         | 1KB   | 11        | 16         | 2                   | 2                   | 1                | 0   | 1               | PDIP 20-pin package |  |

| Z8F0422SJ020EG                                             | 4KB                                         | 1KB   | 19        | 19         | 2                   | 5                   | 1                | 1   | 1               | SOIC 28-pin package |  |

| Z8F0422PJ020EG                                             | 4KB                                         | 1KB   | 19        | 19         | 2                   | 5                   | 1                | 1   | 1               | PDIP 28-pin package |  |

| Z8F04xx with 4KB Flash                                     | 1                                           |       |           |            |                     |                     |                  |     |                 |                     |  |

| Standard Temperature:                                      | 0°C to 70                                   | )°C   |           |            |                     |                     |                  |     |                 |                     |  |

| Z8F0411HH020SG                                             | 4KB                                         | 1KB   | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | SSOP 20-pin package |  |

| Z8F0411PH020SG                                             | 4KB                                         | 1KB   | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | PDIP 20-pin package |  |

| Z8F0412SJ020SG                                             | 4KB                                         | 1KB   | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | SOIC 28-pin package |  |

| Z8F0412PJ020SG                                             | 4KB                                         | 1KB   | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | PDIP 28-pin package |  |

| Extended Temperature:                                      | –40°C to                                    | 105°C |           |            |                     |                     |                  |     |                 |                     |  |

| Z8F0411HH020EG                                             | 4KB                                         | 1KB   | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | SSOP 20-pin package |  |

| Z8F0411PH020EG                                             | 4KB                                         | 1KB   | 11        | 16         | 2                   | 0                   | 1                | 0   | 1               | PDIP 20-pin package |  |

| Z8F0412SJ020EG                                             | 4KB                                         | 1KB   | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | SOIC 28-pin package |  |

| Z8F0412PJ020EG                                             | 4KB                                         | 1KB   | 19        | 19         | 2                   | 0                   | 1                | 1   | 1               | PDIP 28-pin package |  |

| Z8F08200100KITG                                            | Development Kit (20- and 28-pin)            |       |           |            |                     |                     |                  |     |                 |                     |  |

| ZUSBSC00100ZACG                                            | USB Smart Cable Accessory Kit               |       |           |            |                     |                     |                  |     |                 |                     |  |

| ZUSBOPTSC01ZACG                                            | Opto-Isolated USB Smart Cable Accessory Kit |       |           |            |                     |                     |                  |     |                 |                     |  |

#### Table 129. Z8 Encore! XP F0830 Series Ordering Matrix

Visit the Zilog website at <u>http://www.zilog.com</u> for ordering information about Z8 Encore! XP<sup>®</sup> F0822 Series development tools and accessories.

249

condition code 201 continuous conversion (ADC) 138 continuous mode 68 control register definition, UART 88 control register, I2C 131 counter modes 68 CP 204 CPC 204 CPCX 204 CPU and peripheral overview 4 CPU control instructions 206 CPX 204 Customer Feedback Form 258 customer feedback form 224 Customer Information 258

### D

DA 201, 204 data register, I2C 129 DC characteristics 178 debugger, on-chip 158 **DEC 204** decimal adjust 204 decrement 204 and jump non-zero 207 word 204 **DECW 204** destination operand 202 device, port availability 29 DI 206 direct address 201 disable interrupts 206 **DINZ 207** DMA controller 5 dst 202

### Ε

EI 206 electrical characteristics 176 ADC 190 flash memory and timing 187 GPIO input data sample timing 191 watch-dog timer 188 enable interrupt 206 ER 201 extended addressing register 201 external pin reset 24 external RC oscillator electrical characteristics 187 eZ8 CPU features 4 eZ8 CPU instruction classes 204 eZ8 CPU instruction notation 201 eZ8 CPU instruction set 199 eZ8 CPU instruction summary 208

### F

FCTL register 150, 246 features, Z8 Encore! 1 first opcode map 219 FLAGS 202 flags register 202 flash controller 4 option bit address space 155 option bit configuration - reset 155 program memory address 0001H 157 flash memory arrangement 144 byte programming 147 code protection 146 control register definitions 149 controller bypass 148 electrical characteristics and timing 187 flash control register 150, 246 flash status register 151 frequency high and low byte registers 153 mass erase 148 operation 145 operation timing 145 page erase 148 page select register 152 FPS register 152 FSTAT register 151