Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |  |

|----------------------------|-----------------------------------------------------------|--|

| Product Status             | Active                                                    |  |

| Core Processor             | eZ8                                                       |  |

| Core Size                  | 8-Bit                                                     |  |

| Speed                      | 20MHz                                                     |  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |  |

| Number of I/O              | 19                                                        |  |

| Program Memory Size        | 8KB (8K x 8)                                              |  |

| Program Memory Type        | FLASH                                                     |  |

| EEPROM Size                | -                                                         |  |

| RAM Size                   | 1K x 8                                                    |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |

| Data Converters            | -                                                         |  |

| Oscillator Type            | Internal                                                  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |  |

| Mounting Type              | Through Hole                                              |  |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |  |

| Supplier Device Package    | -                                                         |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0812pj020eg |  |

### Z8 Encore! XP<sup>®</sup> F0822 Series Product Specification

vii

| Infrared Endec Control Register Definitions    | 00 |

|------------------------------------------------|----|

| Serial Peripheral Interface                    | 01 |

| Architecture                                   | 01 |

| Operation                                      | 03 |

| SPI Signals                                    | 03 |

| SPI Clock Phase and Polarity Control           | 04 |

| Multimaster Operation                          | 06 |

| Slave Operation                                | 07 |

| Error Detection                                | 07 |

| SPI Interrupts                                 | 08 |

| SPI Baud Rate Generator                        | 08 |

| SPI Control Register Definitions               | 09 |

| SPI Data Register                              | 09 |

| SPI Control Register                           | 10 |

| SPI Status Register                            | 11 |

| SPI Mode Register                              | 12 |

| SPI Diagnostic State Register                  | 13 |

| SPI Baud Rate High and Low Byte Registers      | 14 |

| I2C Controller                                 | 15 |

| Architecture                                   |    |

| Operation                                      | 16 |

| SDA and SCL Signals                            |    |

| I <sup>2</sup> C Interrupts                    | 17 |

| Software Control of I2C Transactions           | 18 |

| Start and Stop Conditions                      | 19 |

| Master Write and Read Transactions             | 19 |

| Address Only Transaction with a 7-Bit Address  | 20 |

| Write Transaction with a 7-Bit Address         | 21 |

| Address-Only Transaction with a 10-Bit Address | 22 |

| Write Transaction with a 10-Bit Address        | 23 |

| Read Transaction with a 7-Bit Address          | 25 |

| Read Transaction with a 10-Bit Address         | 26 |

| I2C Control Register Definitions               |    |

| I2C Data Register                              |    |

| I2C Status Register                            | 29 |

| I2C Control Register                           |    |

| I2C Baud Rate High and Low Byte Registers      | 32 |

| I2C Diagnostic State Register                  |    |

| I2C Diagnostic Control Register                | 35 |

| Analog-to-Digital Converter                    | 36 |

#### Z8 Encore! XP<sup>®</sup> F0822 Series **Product Specification**

| Figure 34. | On-Chip Debugger Block Diagram                                                                        |

|------------|-------------------------------------------------------------------------------------------------------|

| Figure 35. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #1 of 2                          |

| Figure 36. | Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #2 of 2                          |

| Figure 37. | OCD Data Format                                                                                       |

| Figure 38. | Recommended 20MHz Crystal Oscillator Configuration 173                                                |

| Figure 39. | Connecting the On-Chip Oscillator to an External RC Network 174                                       |

| Figure 40. | Typical RC Oscillator Frequency as a Function of External Capacitance with a $45k\Omega$ Resistor 175 |

| Figure 41. | Typical Active Mode IDD vs. System Clock Frequency                                                    |

| Figure 42. | Maximum Active Mode IDD vs. System Clock Frequency                                                    |

| Figure 43. | Typical HALT Mode IDD vs. System Clock Frequency                                                      |

| Figure 44. | Maximum HALT Mode ICC vs. System Clock Frequency 182                                                  |

| Figure 45. | Maximum STOP Mode I <sub>DD</sub> with VBO Enabled vs. Power Supply Voltage                           |

| Figure 46. | Maximum STOP Mode IDD with VBO Disabled vs. Power Supply                                              |

|            | Voltage                                                                                               |

| Figure 47. | Analog-to-Digital Converter Frequency Response                                                        |

| Figure 48. | Port Input Sample Timing                                                                              |

| Figure 49. | GPIO Port Output Timing                                                                               |

| Figure 50. | On-Chip Debugger Timing                                                                               |

| Figure 51. | SPI MASTER Mode Timing                                                                                |

| Figure 52. | SPI SLAVE Mode Timing                                                                                 |

| Figure 53. | I <sup>2</sup> C Timing                                                                               |

| Figure 54. | UART Timing with CTS                                                                                  |

| Figure 55. | UART Timing without CTS                                                                               |

| Figure 56. | Flags Register                                                                                        |

| Figure 57. | Op Code Map Cell Description                                                                          |

| Figure 58. | First Op Code Map                                                                                     |

| Figure 59. | Second Op Code Map after 1FH                                                                          |

#### xiii

# List of Tables

| Table 1.  | Z8 Encore! XP® F0822 Series Part Selection Guide            | 2  |

|-----------|-------------------------------------------------------------|----|

| Table 2.  | Z8 Encore! XP <sup>®</sup> F0822 Series Package Options     | 7  |

| Table 3.  | Signal Descriptions                                         | 10 |

| Table 4.  | Pin Characteristics                                         | 13 |

| Table 5.  | Z8 Encore! XP <sup>®</sup> F0822 Series Program Memory Maps | 15 |

| Table 6.  | Information Area Map                                        | 16 |

| Table 7.  | Register File Address Map                                   | 17 |

| Table 8.  | Reset and Stop Mode Recovery Characteristics and Latency    | 21 |

| Table 9.  | Reset Sources and Resulting Reset Type                      | 22 |

| Table 10. | Stop Mode Recovery Sources and Resulting Action             | 25 |

| Table 11. | Port Availability by Device and Package Type                | 29 |

| Table 12. | Port Alternate Function Mapping                             | 30 |

| Table 13. | GPIO Port Registers and Subregisters                        | 31 |

| Table 14. | Port A–C GPIO Address Registers (PxADDR)                    | 32 |

| Table 15. | Port A–C Control Registers (PxCTL)                          | 33 |

| Table 16. | Port A–C Data Direction Subregisters                        | 33 |

| Table 17. | Port A-CA-C Alternate Function Subregisters                 | 34 |

| Table 18. | Port A–C Output Control Subregisters                        | 35 |

| Table 19. | Port A–C High Drive Enable Subregisters                     | 36 |

| Table 20. | Port A–C Stop Mode Recovery Source Enable Subregisters      | 37 |

| Table 21. | Port A–C Pull-Up Enable Subregisters                        | 38 |

| Table 22. | Port A–C Input Data Registers (PxIN)                        | 38 |

| Table 23. | Port A–C Output Data Register (PxOUT)                       | 39 |

| Table 24. | Interrupt Vectors in Order of Priority                      | 41 |

| Table 25. | Interrupt Request 0 Register (IRQ0)                         | 45 |

| Table 26. | Interrupt Request 1 Register (IRQ1)                         | 46 |

| Table 27. | Interrupt Request 2 Register (IRQ2)                         | 47 |

| Table 28. | IRQ0 Enable and Priority Encoding                           | 48 |

| Table 29. | IRQ0 Enable High Bit Register (IRQ0ENH)                     | 48 |

| Table 30. | IRQ0 Enable Low Bit Register (IRQ0ENL)                      | 49 |

| Table 31. | IRQ1 Enable and Priority Encoding                           | 49 |

| Table 32. | IRQ1 Enable High Bit Register (IRQ1ENH)                     | 50 |

| Table 33. | IRQ1 Enable Low Bit Register (IRQ1ENL)                      | 50 |

#### 10-Bit Analog-to-Digital Converter

The optional Analog-to-Digital Converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from 2 to 5 different analog input sources.

#### **UART**

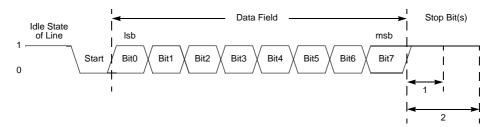

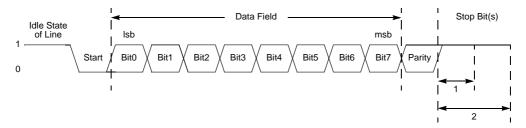

The Universal Asynchronous Receiver/Transmitter (UART) is full-duplex and capable of handling asynchronous data transfers. The UART supports 8-bit and 9-bit data modes and selectable parity.

#### I<sup>2</sup>C

The Inter-Integrated Circuit ( $I^2C$ ) controller makes the Z8 Encore! XP compatible with the  $I^2C$  protocol. The  $I^2C$  Controller consists of two bidirectional bus lines, a serial data (SDA) line, and a serial clock (SCL) line.

#### **Serial Peripheral Interface**

The Serial Peripheral Interface (SPI) allows the Z8 Encore! XP to exchange data between other peripheral devices such as EEPROMs, A/D converters, and ISDN devices. The SPI is a full-duplex, synchronous, and character-oriented channel that supports a four-wire interface.

#### **Timers**

Two 16-bit reloadable timers are used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in One-Shot, Continuous, Gated, Capture, Compare, Capture and Compare, and PWM modes.

# **Interrupt Controller**

Z8 Encore! XP<sup>®</sup> F0822 Series products support up to 18 interrupts. These interrupts consist of 7 internal peripheral interrupts and 11 GPIO pin interrupt sources. The interrupts have 3 levels of programmable interrupt priority.

#### **Reset Controller**

Z8 Encore! XP<sup>®</sup> F0822 Series products are reset using the RESET pin, POR, WDT, STOP Mode exit, or VBO warning signal.

of Reset, all GPIO pins are configured as inputs. All GPIO programmable pull-ups are disabled.

During Reset, the eZ8 CPU and the on-chip peripherals are idle; however, the on-chip crystal oscillator and WDT oscillator continue to run. The system clock begins operating following the WDT oscillator cycle count. The eZ8 CPU and on-chip peripherals remain idle through all of the 16 cycles of the system clock.

Upon Reset, control registers within the Register File which have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following the Reset. The eZ8 CPU fetches the Reset vector at Program memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

#### **Reset Sources**

Table 9 lists the reset sources as a function of the operating mode. The remainder of this section provides more detail about the individual reset sources.

**Note:** A POR/VBO event always has priority over all other possible reset sources to ensure a full system reset occurs.

Table 9. Reset Sources and Resulting Reset Type

| Operating Mode | Reset Source                             | Reset Type                                             |

|----------------|------------------------------------------|--------------------------------------------------------|

| NORMAL or HALT | POR/VBO                                  | System Reset                                           |

| modes          | WDT time-out when configured for Reset   | System Reset                                           |

|                | RESET pin assertion                      | System Reset                                           |

|                | OCD-initiated Reset (OCDCTL[0] set to 1) | System Reset except the OCD is unaffected by the reset |

| STOP Mode      | POR/ VBO                                 | System Reset                                           |

|                | RESET pin assertion                      | System Reset                                           |

|                | DBG pin driven Low                       | System Reset                                           |

#### Power-On Reset

Each device in the Z8 Encore! XP<sup>®</sup> F0822 Series contains an internal POR circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR

| Bit         | Description (Continued)                                                                                                                                                 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]<br>SPII | <ul> <li>SPI Interrupt Request</li> <li>0 = No interrupt request is pending for the SPI.</li> <li>1 = An interrupt request from the SPI is awaiting service.</li> </ul> |

| [0]<br>ADCI | ADC Interrupt Request 0 = No interrupt request is pending for the ADC. 1 = An interrupt request from the ADC is awaiting service.                                       |

#### **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) Register, shown in Table 26, stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 Register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the IRQ1 Register to determine if any interrupt requests are pending.

Table 26. Interrupt Request 1 Register (IRQ1)

| Bit     | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|---------|------|------|------|------|------|------|------|------|--|

| Field   | PA7I | PA6I | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |  |

| RESET   | 0    |      |      |      |      |      |      |      |  |

| R/W     |      | R/W  |      |      |      |      |      |      |  |

| Address |      |      |      | FC   | 3H   |      |      |      |  |

| Bit   | Description                                                            |

|-------|------------------------------------------------------------------------|

| [7:0] | Port A Pin x Interrupt Request                                         |

| PAxI  | 0 = No interrupt request is pending for GPIO Port A pin x.             |

|       | 1 = An interrupt request from GPIO Port A pin $x$ is awaiting service. |

| Note: | x indicates register bits in the range [7:0].                          |

# Embedded in Life An IXYS Company

### IRQ2 Enable High and Low Bit Registers

Table 34 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit registers, shown in Tables 35 and 36, form a priority-encoded enabling for interrupts in the Interrupt Request 2 Register. Priority is generated by setting bits in each register.

Table 34. IRQ2 Enable and Priority Encoding

| IRQ2ENH[x]                                          | IRQ2ENL[x] | Priority | Description |  |  |  |  |

|-----------------------------------------------------|------------|----------|-------------|--|--|--|--|

| 0                                                   | 0          | Disabled | Disabled    |  |  |  |  |

| 0                                                   | 1          | Level 1  | Low         |  |  |  |  |

| 1                                                   | 0          | Level 2  | Nominal     |  |  |  |  |

| 1                                                   | 1          | Level 3  | High        |  |  |  |  |

| Note: x indicates register bits in the range [7:0]. |            |          |             |  |  |  |  |

Table 35. IRQ2 Enable High Bit Register (IRQ2ENH)

| Bit     | 7 | 6    | 5     | 4  | 3     | 2     | 1     | 0     |  |

|---------|---|------|-------|----|-------|-------|-------|-------|--|

| Field   |   | Rese | erved |    | C3ENH | C2ENH | C1ENH | C0ENH |  |

| RESET   | 0 |      |       |    |       |       |       |       |  |

| R/W     |   | R/W  |       |    |       |       |       |       |  |

| Address |   |      |       | FC | 7H    |       |       |       |  |

| Bit          | Description                                                      |

|--------------|------------------------------------------------------------------|

| [7:4]        | Reserved These bits are reserved and must be programmed to 0000. |

| [3]<br>C3ENH | Port C3 Interrupt Request Enable High Bit                        |

| [2]<br>C2ENH | Port C2 Interrupt Request Enable High Bit                        |

| [1]<br>C1ENH | Port C1 Interrupt Request Enable High Bit                        |

| [0]<br>C0ENH | Port C0 Interrupt Request Enable High Bit                        |

# Embedded in Life An IXYS Company

## Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers, shown in Tables 50 through 52, form the 24-bit reload value that is loaded into the WDT, when a WDT instruction executes. The 24-bit reload value is {WDTU[7:0], WDTH[7:0]}. Writing to these registers sets the required reload value. Reading from these registers returns the current WDT count value.

**Caution:** The 24-bit WDT reload value must not be set to a value less than 000004H.

Table 50. Watchdog Timer Reload Upper Byte Register (WDTU)

| Bit        | 7                                                                                                   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|------------|-----------------------------------------------------------------------------------------------------|---|---|---|---|---|---|---|--|

| Field      | WDTU                                                                                                |   |   |   |   |   |   |   |  |

| RESET      |                                                                                                     | 1 |   |   |   |   |   |   |  |

| R/W        | R/W*                                                                                                |   |   |   |   |   |   |   |  |

| Address    | FF1H                                                                                                |   |   |   |   |   |   |   |  |

| Note: *R/\ | Note: *R/W = a read returns the current WDT count value; a write sets the appropriate reload value. |   |   |   |   |   |   |   |  |

| Bit   | Description                                                               |

|-------|---------------------------------------------------------------------------|

| [7:0] | WDT Reload Upper Byte                                                     |

| WDTU  | Most significant byte (MSB), bits [23:16] of the 24-bit WDT reload value. |

#### Table 51. Watchdog Timer Reload High Byte Register (WDTH)

| Bit                                                                                                 | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------------------------------------------------------------------------------------------------|------|------|---|---|---|---|---|---|--|--|

| Field                                                                                               |      | WDTH |   |   |   |   |   |   |  |  |

| RESET                                                                                               |      | 1    |   |   |   |   |   |   |  |  |

| R/W                                                                                                 | R/W* |      |   |   |   |   |   |   |  |  |

| Address                                                                                             | FF2H |      |   |   |   |   |   |   |  |  |

| Note: *R/W = a read returns the current WDT count value; a write sets the appropriate reload value. |      |      |   |   |   |   |   |   |  |  |

| Bit   | Description                                              |

|-------|----------------------------------------------------------|

| [7:0] | WDT Reload High Byte                                     |

| WDTH  | Middle byte, bits [15:8] of the 24-bit WDT reload value. |

Figure 12. UART Asynchronous Data Format without Parity

Figure 13. UART Asynchronous Data Format with Parity

# **Transmitting Data using Polled Method**

Observe the following procedure to transmit data using polled method of operation:

- 1. Write to the UART Baud Rate High Byte and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. If MULTIPROCESSOR Mode is required, write to the UART Control 1 Register to enable multiprocessor (9-bit) mode functions.

- Set the Multiprocessor Mode Select (MPEN) to enable MULTIPROCESSOR Mode.

- 4. Write to the UART Control 0 Register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- If parity is required, and MULTIPROCESSOR Mode is not enabled, set the parity enable bit (PEN) and select either even or odd parity (PSEL).

- 6. The I<sup>2</sup>C Controller sends the start condition to the I<sup>2</sup>C Slave.

- The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register

- 8. After one bit of an address is shifted out by the SDA signal, the transmit interrupt is asserted.

- Software responds by writing the second byte of the address into the contents of the I<sup>2</sup>C Data Register.

- The I<sup>2</sup>C Controller shifts the rest of the first byte of address and write bit out the SDA signal.

- 11. If the I<sup>2</sup>C Slave sends an acknowledge by pulling the SDA signal Low during the next High period of SCL and the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status Register, continue to Step 12.

If the slave does not acknowledge the first address byte, the I<sup>2</sup>C Controller sets the NCKI bit and clears the ACK bit in the I<sup>2</sup>C Status Register. Software responds to the Not Acknowledge interrupt by setting the stop and flush bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the stop condition on the bus and clears the stop and NCKI bits. The transaction is complete; ignore the remaining steps in this sequence.

- 12. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register (2nd byte of address).

- 13. The I<sup>2</sup>C Controller shifts the second address byte out the SDA signal. After the first bit has been sent, the transmit interrupt is asserted.

- 14. Software responds by setting the stop bit in the I<sup>2</sup>C Control Register. The TXI bit can be cleared at the same time.

- 15. Software polls the stop bit of the I<sup>2</sup>C Control Register. Hardware deasserts the stop bit when the transaction is completed (stop condition has been sent).

- 16. Software checks the ACK bit of the I<sup>2</sup>C Status Register. If the slave acknowledged, the ACK bit is equal to 1. If the slave does not acknowledge, the ACK bit is equal to 0. The NCKI interrupt do not occur because the stop bit was set.

#### Write Transaction with a 10-Bit Address

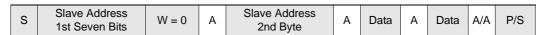

Figure 29 displays the data transfer format for a 10-bit addressed slave. Shaded regions indicate data transferred from the I<sup>2</sup>C Controller to slaves and unshaded regions indicate data transferred from the slaves to the I<sup>2</sup>C Controller.

Figure 29. 10-Bit Addressed Slave Data Transfer Format

- 16. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register (third address transfer).

- 17. The I<sup>2</sup>C Controller sends 11110B followed by the two most significant bits of the slave read address and a 1 (read).

- 18. The I<sup>2</sup>C Slave sends an acknowledge by pulling the SDA signal Low during the next High period of SCL.

If the slave were to Not Acknowledge at this point (this should not happen because the slave did acknowledge the first two address bytes), software would respond by setting the stop and flush bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the stop condition on the bus and clears the stop and NCKI bits. The transaction is complete; ignore the remainder of this sequence.

- 19. The I<sup>2</sup>C Controller shifts in a byte of data from the I<sup>2</sup>C Slave on the SDA signal. The I<sup>2</sup>C Controller sends a Not Acknowledge to the I<sup>2</sup>C Slave if the NAK bit is set (last byte), else it sends an Acknowledge.

- 20. The I<sup>2</sup>C Controller asserts the Receive interrupt (RDRF bit set in the Status Register).

- 21. Software responds by reading the I<sup>2</sup>C Data Register which clears the RDRF bit. If there is only one more byte to receive, set the NAK bit of the I<sup>2</sup>C Control Register.

- 22. If there are one or more bytes to transfer, return to <u>Step 19</u>.

- 23. After the last byte is shifted in, a Not Acknowledge interrupt is generated by the I<sup>2</sup>C Controller.

- 24. Software responds by setting the stop bit of the I<sup>2</sup>C Control Register.

- 25. A stop condition is sent to the I<sup>2</sup>C Slave and the stop and NCKI bits are cleared.

# I<sup>2</sup>C Control Register Definitions

This section defines the features of the following I<sup>2</sup>C Control registers.

I2C Data Register: see page 129

I2C Status Register: see page 129

I2C Control Register: see page 131

I2C Baud Rate High and Low Byte Registers: see page 132

I2C Diagnostic State Register: see page 133

I2C Diagnostic Control Register: see page 135

160

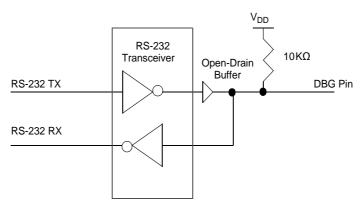

Figure 36. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface, #2 of 2

#### **Debug Mode**

The operating characteristics of the Z8 Encore!  $XP^{\text{\tiny{IB}}}$  F0822 Series devices in DEBUG Mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP Mode

- All enabled on-chip peripherals operate unless in STOP Mode

- Automatically exits HALT Mode

- Constantly refreshes the Watchdog Timer, if enabled

#### **Entering Debug Mode**

The device enters DEBUG Mode following any of the following operations:

- Writing the DBGMODE bit in the OCD Control Register to 1 using the OCD interface

- eZ8 CPU execution of a breakpoint (BRK) instruction

- Matching of the PC to the OCDCNTR Register (when enabled)

- The OCDCNTR Register decrements to 0000H (when enabled)

- If the DBG pin is Low when the device exits Reset, the OCD automatically places the device into DEBUG Mode

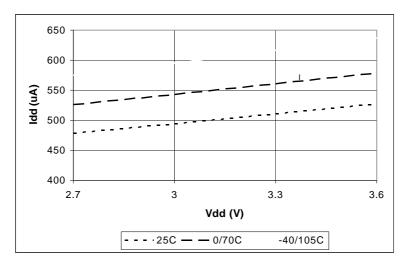

Figure 45 displays the maximum current consumption in STOP Mode with the VBO and Watchdog Timer enabled plotted opposite the power supply voltage. All GPIO pins are configured as outputs and driven High.

Figure 45. Maximum STOP Mode  $I_{\mbox{\scriptsize DD}}$  with VBO Enabled vs. Power Supply Voltage

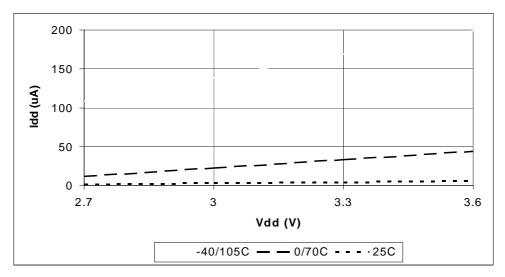

Figure 46 displays the maximum current consumption in STOP Mode with the VBO disabled and Watchdog Timer enabled plotted opposite the power supply voltage. All GPIO pins are configured as outputs and driven High. Disabling the Watchdog Timer and its internal RC oscillator in STOP Mode will provide some additional reduction in STOP Mode current consumption. This small current reduction is indistinquishable on the scale of Figure 46.

Figure 46. Maximum STOP Mode I<sub>DD</sub> with VBO Disabled vs. Power Supply Voltage

# On-Chip Peripheral AC and DC Electrical Characteristics

Table 100 provides information about the Power-On Reset and Voltage Brown-Out electrical characteristics.

Table 100. Power-On Reset and Voltage Brown-Out Electrical Characteristics and Timing

|                   |                                                                                           | T <sub>A</sub> = | –40°C to 1      | 05°C    |       |                                                                                                       |  |  |

|-------------------|-------------------------------------------------------------------------------------------|------------------|-----------------|---------|-------|-------------------------------------------------------------------------------------------------------|--|--|

| Symbol            | Parameter                                                                                 | Minimum          | Typical*        | Maximum | Units | Conditions                                                                                            |  |  |

| $V_{POR}$         | Power-On Reset<br>Voltage Threshold                                                       | 2.15             | 2.40            | 2.60    | V     | $V_{DD} = V_{POR}$                                                                                    |  |  |

| V <sub>VBO</sub>  | Voltage Brown-Out<br>Reset Voltage<br>Threshold                                           | 2.05             | 2.30            | 2.55    | V     | $V_{DD} = V_{VBO}$                                                                                    |  |  |

|                   | V <sub>POR</sub> to V <sub>VBO</sub> hysteresis                                           | 50               | 100             | -       | mV    |                                                                                                       |  |  |

|                   | Starting V <sub>DD</sub> voltage to ensure valid POR                                      | _                | V <sub>SS</sub> | -       | V     |                                                                                                       |  |  |

| T <sub>ANA</sub>  | POR Analog Delay                                                                          | _                | 50              | -       | μs    | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |  |  |

| T <sub>POR</sub>  | POR Digital Delay                                                                         | -                | 5.0             | _       | ms    | 50 WDT Oscillator cycles<br>(10kHz) + 16 System Clock<br>cycles (20MHz)                               |  |  |

| T <sub>VBO</sub>  | Voltage Brown-Out<br>Pulse Rejection<br>Period                                            | -                | 10              | _       | μs    | V <sub>DD</sub> < V <sub>VBO</sub> to generate a Reset.                                               |  |  |

| T <sub>RAMP</sub> | Time for VDD to transition from V <sub>SS</sub> to V <sub>POR</sub> to ensure valid Reset | 0.10             | -               | 100     | ms    |                                                                                                       |  |  |

Note: \*Data in the typical column is from characterization at 3.3 V and 25°C. These values are provided for design guidance only and are not tested in production.

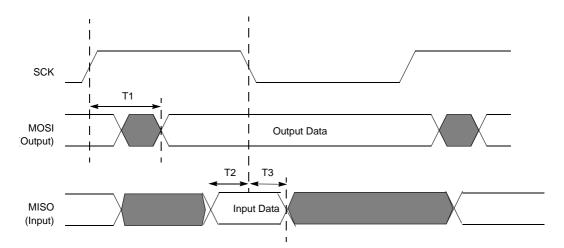

### **SPI MASTER Mode Timing**

Figure 51 and Table 109 provide timing information for SPI MASTER Mode pins. Timing is shown with SCK rising edge used to source MOSI output data, SCK falling edge used to sample MISO input data. Timing on the SS output pin(s) is controlled by software.

Figure 51. SPI MASTER Mode Timing

**Table 109. SPI MASTER Mode Timing**

|                |                                             | Dela    | y (ns)  |

|----------------|---------------------------------------------|---------|---------|

| Parameter      | Abbreviation                                | Minimum | Maximum |

| SPI MASTE      | R                                           |         |         |

| T <sub>1</sub> | SCK Rise to MOSI output Valid Delay         | -5      | +5      |

| T <sub>2</sub> | MISO input to SCK (receive edge) Setup Time | 20      |         |

| T <sub>3</sub> | MISO input to SCK (receive edge) Hold Time  | 0       |         |

Table 126. Rotate and Shift Instructions

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| BSWAP    | dst      | Bit Swap                   |

| RL       | dst      | Rotate Left                |

| RLC      | dst      | Rotate Left through Carry  |

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right through Carry |

| SRA      | dst      | Shift Right Arithmetic     |

| SRL      | dst      | Shift Right Logical        |

| SWAP     | dst      | Swap Nibbles               |

# **eZ8 CPU Instruction Summary**

Table 127 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags Register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction execution.

Table 127. eZ8 CPU Instruction Summary

| Assembly      | Symbolic                       | Addre:<br>Mode |     | Op<br>Code(s) |   |   | Fla | ags |   | Fetch | Instr. |        |

|---------------|--------------------------------|----------------|-----|---------------|---|---|-----|-----|---|-------|--------|--------|

| Mnemonic      | Operation                      | dst            | src | (Hex)         | С | Z | S   | ٧   | D | Н     | Cycles | Cycles |

| ADC dst, src  | $dst \leftarrow dst + src + C$ | r              | r   | 12            | * | * | *   | *   | 0 | *     | 2      | 3      |

|               |                                | r              | lr  | 13            | - |   |     |     |   |       | 2      | 4      |

|               |                                | R              | R   | 14            | _ |   |     |     |   |       | 3      | 3      |

|               |                                | R              | IR  | 15            | - |   |     |     |   | •     | 3      | 4      |

|               |                                | R              | IM  | 16            | - |   |     |     |   |       | 3      | 3      |

|               |                                | IR             | IM  | 17            | _ |   |     |     |   |       | 3      | 4      |

| ADCX dst, src | $dst \leftarrow dst + src + C$ | ER             | ER  | 18            | * | * | *   | *   | 0 | *     | 4      | 3      |

|               |                                | ER             | IM  | 19            | - |   |     |     |   | •     | 4      | 3      |

Note: Flags Notation:

<sup>\* =</sup> Value is a function of the result of the operation.

<sup>- =</sup> Unaffected.

X = Undefined.

<sup>0 =</sup> Reset to 0.

<sup>1 =</sup> Set to 1.

227

Hex Address: F67

Table 168. SPI Baud Rate Low Byte Register (SPIBRL)

| Bit     | 7    | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|------|-----|---|---|---|---|---|---|--|--|

| Field   |      | BRL |   |   |   |   |   |   |  |  |

| RESET   | 1    |     |   |   |   |   |   |   |  |  |

| R/W     | R/W  |     |   |   |   |   |   |   |  |  |

| Address | F67H |     |   |   |   |   |   |   |  |  |

Hex Addresses: F68–F6F This address range is reserved.

# **Analog-to-Digital Converter Control Registers**

For more information about these ADC registers, see the <u>ADC Control Register Definitions</u> section on page 139.

Hex Address: F70

Table 169. ADC Control Register (ADCCTL)

| Bit     | 7   | 6        | 5    | 4    | 3          | 0 |  |  |  |

|---------|-----|----------|------|------|------------|---|--|--|--|

| Field   | CEN | Reserved | VREF | CONT | ANAIN[3:0] |   |  |  |  |

| RESET   | (   | )        | 1    |      |            | 0 |  |  |  |

| R/W     |     | R/W      |      |      |            |   |  |  |  |

| Address |     | F70H     |      |      |            |   |  |  |  |

Hex Address: F71

This address is reserved.

| G                                               | C status register 129, 233         |

|-------------------------------------------------|------------------------------------|

| gated mode 69                                   | control register definitions 128   |

| general-purpose I/O 29                          | controller 115                     |

| GPIO 4, 29                                      | controller signals 10              |

| alternate functions 29                          | interrupts 117                     |

| architecture 29                                 | operation 116                      |

| control register definitions 31                 | SDA and SCL signals 117            |

| input data sample timing 191                    | stop and start conditions 119      |

| interrupts 31                                   | I2CBRH register 132, 133, 135, 234 |

| port A-C pull-up enable sub-registers 38        | I2CBRL register 133, 234           |

| port A-H address registers 32                   | I2CCTL register 131, 233           |

| port A-H alternate function sub-registers 34    | I2CDATA register 129, 233          |

| port A-H control registers 33                   | I2CSTAT register 129, 233          |

| port A-H data direction sub-registers 33        | IM 201                             |

| port A-H high drive enable sub-registers 36     | immediate data 201                 |

| port A-H input data registers 38                | immediate operand prefix 202       |

| port A-H output control sub-registers 35        | INC 204                            |

| port A-H output data registers 39               | increment 204                      |

| port A-H stop mode recovery sub-registers 37    | increment word 204                 |

| port availability by device 29                  | INCW 204                           |

| port input timing 191                           | indexed 202                        |

| port output timing 192                          | indirect address prefix 202        |

| L 222 2 2 2 4 2 2 2 2 2 2 2 2 2 2 2 2 2         | indirect register 201              |

|                                                 | indirect register pair 201         |

| Н                                               | indirect working register 201      |

| H 202                                           | indirect working register pair 201 |

| HALT 206                                        | infrared encoder/decoder (IrDA) 97 |

| halt mode 27, 206                               | instruction set, ez8 CPU 199       |

| hexadecimal number prefix/suffix 202            | instructions                       |

| nexudeeman nameer premy surrix 202              | ADC 204                            |

|                                                 | ADCX 204                           |

| I                                               | ADD 204                            |

| I2C 4                                           | ADDX 204                           |

| 10-bit address read transaction 126             | AND 207                            |

| 10-bit address transaction 123                  | ANDX 207                           |

| 10-bit addressed slave data transfer format 123 | arithmetic 204                     |

| 10-bit receive data format 126                  | BCLR 205                           |

| 7-bit address transaction 121                   | BIT 205                            |

| 7-bit address, reading a transaction 125        | bit manipulation 205               |

| 7-bit addressed slave data transfer format 120, | block transfer 205                 |

| 121, 122                                        | BRK 207                            |

| 7-bit receive data transfer format 125          | BSET 205                           |

| baud high and low byte registers 132, 133, 135  | BSWAP 205, 208<br>BTI 207          |

| , , , , , , , , , , , , , , , , , , , ,         | DII /U/                            |

| IrDA                                                  | logical exclusive OR/extended addressing 207 |

|-------------------------------------------------------|----------------------------------------------|

| architecture 97                                       | logical instructions 207                     |

| block diagram 97                                      | logical OR 207                               |

| control register definitions 100                      | logical OR/extended addressing 207           |

| operation 97                                          | low power modes 27                           |

| receiving data 99                                     |                                              |

| transmitting data 98                                  |                                              |

| IRET 207                                              | M                                            |

| IRQ0 enable high and low bit registers 48             | master interrupt enable 42                   |

| IRQ1 enable high and low bit registers 49             | master-in, slave-out and-in 103              |

| IRQ2 enable high and low bit registers 51             | memory                                       |

| IRR 201                                               | program 15                                   |

| Irr 201                                               | MISO 103                                     |

|                                                       | mode                                         |

|                                                       | capture 68                                   |

| J                                                     | capture/compare 69                           |

| JP 207                                                | continuous 68                                |

| jump, conditional, relative, and relative conditional | counter 68                                   |

| 207                                                   | gated 69                                     |

|                                                       | one-shot 68                                  |

|                                                       | PWM 68                                       |

| L                                                     | modes 68                                     |

| LD 206                                                | MOSI 103                                     |

| LDC 206                                               | MULT 205                                     |

| LDCI 205, 206                                         | multiply 205                                 |

| LDE 206                                               | multiprocessor mode, UART 83                 |

| LDEI 205, 206                                         |                                              |

| LDX 206                                               |                                              |

| LEA 206                                               | N                                            |

| load 206                                              | NOP (no operation) 206                       |

| load constant 205                                     | not acknowledge interrupt 117                |

| load constant to/from program memory 206              | notation                                     |

| load constant with auto-increment addresses 206       | b 201                                        |

| load effective address 206                            | cc 201                                       |

| load external data 206                                | DA 201                                       |

| load external data to/from data memory and auto-      | ER 201                                       |

| increment addresses 205                               | IM 201                                       |

| load external to/from data memory and auto-incre-     | IR 201                                       |

| ment addresses 206                                    | Ir 201                                       |

| load instructions 206                                 | IRR 201                                      |

| load using extended addressing 206                    | Irr 201                                      |

| logical AND 207                                       | p 201                                        |

| logical AND/extended addressing 207                   | R 201                                        |

| logical exclusive OR 207                              | r 201                                        |