# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 11                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | ·                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 2x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0821hh020sg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of Figures

| Figure 1.  | Z8 Encore! XP <sup>®</sup> F0822 Series Block Diagram                    |

|------------|--------------------------------------------------------------------------|

| Figure 2.  | The Z8F0821 and Z8F0421 MCUs in 20-Pin SSOP and PDIP Packages 8          |

| Figure 3.  | The Z8F0822 and Z8F0422 MCUs in 28-Pin SOIC and PDIP Packages 8          |

| Figure 4.  | The Z8F0811 and Z8F0411 MCUs in 20-Pin SSOP and PDIP Packages 9          |

| Figure 5.  | The Z8F0812 and Z8F0412 MCUs in 28-Pin SOIC and PDIP Packages $\ldots 9$ |

| Figure 6.  | Power-On Reset Operation                                                 |

| Figure 7.  | Voltage Brown-Out Reset Operation                                        |

| Figure 8.  | GPIO Port Pin Block Diagram                                              |

| Figure 9.  | Interrupt Controller Block Diagram                                       |

| Figure 10. | Timer Block Diagram 55                                                   |

| Figure 11. | UART Block Diagram                                                       |

| Figure 12. | UART Asynchronous Data Format without Parity                             |

| Figure 13. | UART Asynchronous Data Format with Parity                                |

| Figure 14. | UART Asynchronous Multiprocessor Mode Data Format                        |

| Figure 15. | UART Driver Enable Signal Timing (with 1 Stop Bit and Parity) 85         |

| Figure 16. | UART Receiver Interrupt Service Routine Flow                             |

| Figure 17. | Infrared Data Communication System Block Diagram                         |

| Figure 18. | Infrared Data Transmission                                               |

| Figure 19. | Infrared Data Reception                                                  |

| Figure 20. | SPI Configured as a Master in a Single Master, Single Slave System 101   |

| Figure 21. | SPI Configured as a Master in a Single Master, Multiple Slave System 102 |

| Figure 22. | SPI Configured as a Slave 102                                            |

| Figure 23. | SPI Timing When PHASE is 0 105                                           |

| Figure 24. | SPI Timing When PHASE is 1 106                                           |

| Figure 25. | I <sup>2</sup> C Controller Block Diagram 116                            |

| Figure 26. | 7-Bit Address Only Transaction Format 120                                |

| Figure 27. | 7-Bit Addressed Slave Data Transfer Format                               |

| Figure 28. | 10-Bit Address Only Transaction Format                                   |

| Figure 29. | 10-Bit Addressed Slave Data Transfer Format 123                          |

| Figure 30. | Receive Data Transfer Format for a 7-Bit Addressed Slave 125             |

| Figure 31. | Receive Data Format for a 10-Bit Addressed Slave                         |

| Figure 32. | Analog-to-Digital Converter Block Diagram                                |

| Figure 33. | Flash Memory Arrangement 144                                             |

#### xiii

# List of Tables

| Table 1.  | Z8 Encore! XP <sup>®</sup> F0822 Series Part Selection Guide 2 |

|-----------|----------------------------------------------------------------|

| Table 2.  | Z8 Encore! XP <sup>®</sup> F0822 Series Package Options        |

| Table 3.  | Signal Descriptions 10                                         |

| Table 4.  | Pin Characteristics                                            |

| Table 5.  | Z8 Encore! XP <sup>®</sup> F0822 Series Program Memory Maps 15 |

| Table 6.  | Information Area Map 16                                        |

| Table 7.  | Register File Address Map 17                                   |

| Table 8.  | Reset and Stop Mode Recovery Characteristics and Latency 21    |

| Table 9.  | Reset Sources and Resulting Reset Type 22                      |

| Table 10. | Stop Mode Recovery Sources and Resulting Action 25             |

| Table 11. | Port Availability by Device and Package Type 29                |

| Table 12. | Port Alternate Function Mapping 30                             |

| Table 13. | GPIO Port Registers and Subregisters                           |

| Table 14. | Port A-C GPIO Address Registers (PxADDR) 32                    |

| Table 15. | Port A-C Control Registers (PxCTL)                             |

| Table 16. | Port A–C Data Direction Subregisters                           |

| Table 17. | Port A-CA-C Alternate Function Subregisters                    |

| Table 18. | Port A–C Output Control Subregisters                           |

| Table 19. | Port A–C High Drive Enable Subregisters                        |

| Table 20. | Port A–C Stop Mode Recovery Source Enable Subregisters         |

| Table 21. | Port A–C Pull-Up Enable Subregisters                           |

| Table 22. | Port A-C Input Data Registers (PxIN)                           |

| Table 23. | Port A-C Output Data Register (PxOUT) 39                       |

| Table 24. | Interrupt Vectors in Order of Priority                         |

| Table 25. | Interrupt Request 0 Register (IRQ0)                            |

| Table 26. | Interrupt Request 1 Register (IRQ1)                            |

| Table 27. | Interrupt Request 2 Register (IRQ2)                            |

| Table 28. | IRQ0 Enable and Priority Encoding                              |

| Table 29. | IRQ0 Enable High Bit Register (IRQ0ENH)                        |

| Table 30. | IRQ0 Enable Low Bit Register (IRQ0ENL)                         |

| Table 31. | IRQ1 Enable and Priority Encoding                              |

| Table 32. | IRQ1 Enable High Bit Register (IRQ1ENH)                        |

| Table 33. | IRQ1 Enable Low Bit Register (IRQ1ENL) 50                      |

dded in Life

6

## **On-Chip Debugger**

Z8 Encore! XP<sup>®</sup> F0822 Series products feature an integrated On-Chip Debugger (OCD). The OCD provides a rich-set of debugging capabilities, such as, reading and writing registers, programming Flash memory, setting breakpoints, and executing code. A single-pin interface provides communication to the OCD.

nbedded in Life

15

# **Program Memory**

The eZ8 CPU supports 64KB of Program memory address space. Z8 Encore! XP<sup>®</sup> F0822 Series contain 4KB to 8KB on-chip Flash in the Program memory address space, depending on the device. Reading from Program memory addresses outside the available Flash addresses returns FFH. Writing to unimplemented Program memory addresses produces no effect. Table 5 describes the Program memory Maps for Z8 Encore! XP<sup>®</sup> F0822 Series devices.

| Program Memory Address (Hex)              | Function                    |

|-------------------------------------------|-----------------------------|

| Z8F082x and Z8F081x Products              |                             |

| 0000-0001                                 | Option Bits                 |

| 0002-0003                                 | Reset Vector                |

| 0004-0005                                 | WDT Interrupt Vector        |

| 0006-0007                                 | Illegal Instruction Trap    |

| 0008-0037                                 | Interrupt Vectors*          |

| 0038-1FFF                                 | Program Memory              |

| Z8F042x and Z8F041x Products              |                             |

| 0000-0001                                 | Option Bits                 |

| 0002-0003                                 | Reset Vector                |

| 0004-0005                                 | WDT Interrupt Vector        |

| 0006-0007                                 | Illegal Instruction Trap    |

| 0008-0037                                 | Interrupt Vectors*          |

| 0038-0FFF                                 | Program Memory              |

| Note: *See Table 24 on page 41 for a list | t of the interrupt vectors. |

## Table 5. Z8 Encore! XP<sup>®</sup> F0822 Series Program Memory Maps

## **Data Memory**

Z8 Encore! XP<sup>®</sup> F0822 Series does not use the eZ8 CPU's 64KB Data Memory address space.

## **Information Area**

Table 6 describes the Z8 Encore! XP<sup>®</sup> F0822 Series Information Area. This 512-byte Information Area is accessed by setting bit 7 of the Page Select Register to 1. When access is enabled, the Information Area is mapped into the Program memory and overlays the 512 bytes at addresses FE00H to FFFFH. When the Information Area access is enabled, all

| Port   | Pin             | Mnemonic | Alternate Function Description |

|--------|-----------------|----------|--------------------------------|

| Port C | Port C PC0 T1IN |          | Timer 1 Input                  |

|        | PC1 T1OUT       |          | Timer 1 Output                 |

|        | PC2             | SS       | SPI Slave Select               |

|        | PC3             | SCK      | SPI Serial Clock               |

|        | PC4             | MOSI     | SPI Master Out Slave In        |

|        | PC5             | MISO     | SPI Master In Slave Out        |

|        |                 |          |                                |

Table 12. Port Alternate Function Mapping (Continued)

## **GPIO Interrupts**

Many of GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupts generate an interrupt when any edge occurs (both rising and falling). For more details about interrupts using the GPIO pins, see Figure 8.

## **GPIO Control Register Definitions**

Four registers for each port provide access to GPIO control, input data, and output data. Table 13 lists the GPIO port registers and subregisters. Use the Port A–C Address and Control registers together to provide access to subregisters for Port configuration and control.

| Port Register Mnemonic    | Port Register Name                                          |

|---------------------------|-------------------------------------------------------------|

| PxADDR                    | Port A–C Address Register (selects subregisters)            |

| PxCTL                     | Port A–C Control Register (provides access to subregisters) |

| PxIN                      | Port A–C Input Data Register                                |

| PxOUT                     | Port A–C Output Data Register                               |

| Port Subregister Mnemonic | Port Register Name                                          |

| PxDD                      | Data Direction                                              |

| PxAF                      | Alternate Function                                          |

| PxOC                      | Output Control (Open-Drain)                                 |

| PxHDE                     | High Drive Enable                                           |

| PxSMRE                    | Stop Mode Recovery Source Enable                            |

| PxPUE                     | Pull-up Enable                                              |

Table 13. GPIO Port Registers and Subregisters

## Port A–C Stop Mode Recovery Source Enable Subregisters

The Port A–C Stop Mode Recovery Source Enable Subregister, shown in Table 20, is accessed through the Port A–C Control Register by writing 05H to the Port A–C Address Register. Setting the bits in the Port A–C Stop Mode Recovery Source Enable subregisters to 1 configures the specified Port pins as a Stop Mode Recovery source. During STOP Mode, any logic transition on a Port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

#### Table 20. Port A–C Stop Mode Recovery Source Enable Subregisters

| Bit                                                                                                                    | 7             | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|------------------------------------------------------------------------------------------------------------------------|---------------|--------|--------|--------|--------|--------|--------|--------|

| Field                                                                                                                  | PSMRE7        | PSMRE6 | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |

| RESET                                                                                                                  | 0             |        |        |        |        |        |        |        |

| R/W                                                                                                                    |               | R/W    |        |        |        |        |        |        |

| Address                                                                                                                | See footnote. |        |        |        |        |        |        |        |

| Note: If 05H is written to the Port A–C Address Register, then it is accessible through the Port A–C Control Register. |               |        |        |        |        |        |        |        |

|                                                                                                                        |               |        |        |        |        |        |        |        |

#### Bit Description

#### [7:0] Port Stop Mode Recovery Source Enabled

PSMREx 0 = The port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP Mode does not initiate Stop Mode Recovery.

1 = The port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP Mode initiates Stop Mode Recovery.

Note: x indicates register bits in the range [7:0].

37

ILO G

# Embedded in Life

53

## Interrupt Control Register

The Interrupt Control (IRQCTL) Register, shown in Table 38, contains the master enable bit for all interrupts.

## Table 38. Interrupt Control Register (IRQCTL)

| Bit     | 7    | 6          | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|------|------------|---|---|---|---|---|---|

| Field   | IRQE | E Reserved |   |   |   |   |   |   |

| RESET   |      | 0          |   |   |   |   |   |   |

| R/W     | R/W  | R/W R      |   |   |   |   |   |   |

| Address | FCFH |            |   |   |   |   |   |   |

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IRQE | <ul> <li>Interrupt Request Enable</li> <li>This bit is set to 1 by execution of an Enable Interrupts (EI) or Interrupt Return (IRET) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, Reset or by a direct register write of a 0 to this bit.</li> <li>0 = Interrupts are disabled.</li> <li>1 = Interrupts are enabled.</li> </ul> |

| [6:0]       | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                                                                                                                                                                                                                       |

# **Timers**

Z8 Encore! XP<sup>®</sup> F0822 Series products contain up to two 16-bit reloadable timers that can be used for timing, event counting, or generation of pulse-width modulated signals. The timer features include:

- 16-bit reload counter

- Programmable prescaler with prescale values from 1 to 128

- PWM output generation

- Capture and compare capability

- External input pin for timer input, clock gating, or capture signal; external input pin signal frequency is limited to a maximum of one-fourth the system clock frequency

- Timer output pin

- Timer interrupt

In addition to the timers described in this chapter, the Baud Rate Generators for any unused UART, SPI, or  $I^2C$  peripherals can also be used to provide basic timing functionality. See the respective serial communication peripheral chapters for information about using the Baud Rate Generators as timers.

| Z8 Encore! XP <sup>®</sup> F0822<br>Product Speci |   |

|---------------------------------------------------|---|

|                                                   | J |

#### ilog° Embedded in Life An □IXYS Company 55

## Architecture

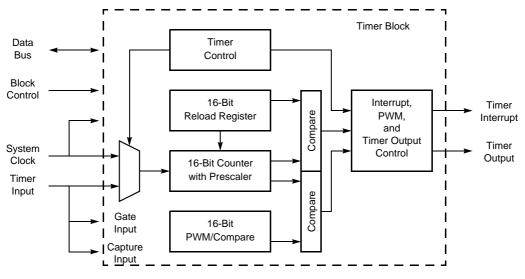

Figure 10 displays the architecture of the timers.

Figure 10. Timer Block Diagram

# Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

## **Timer Operating Modes**

The timers are configured to operate in the following modes:

## **ONE-SHOT Mode**

In ONE-SHOT Mode, the timer counts up to the 16-bit reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the reload value, the timer generates an interrupt and the count value in the Timer High

# nbedded in Life

# Watchdog Timer

Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which can place the Z8 Encore! XP<sup>®</sup> F0822 Series device into unsuitable operating states. It includes the following features:

- On-chip RC oscillator

- A selectable time-out response; either Reset or Interrupt

- 24-bit programmable time-out value

## Operation

WDT is a retriggerable one-shot timer that resets or interrupts the Z8 Encore! XP<sup>®</sup> F0822 Series device when the WDT reaches its terminal count. It uses its own dedicated on-chip RC oscillator as its clock source. The WDT has only two modes of operation: ON and OFF. When enabled, it always counts and must be refreshed to prevent a time-out. An enable is performed by executing the WDT instruction or by setting the WDT\_AO option bit. The WDT\_AO bit enables the WDT to operate all of the time, even if a WDT instruction has not been executed.

The WDT is a 24-bit reloadable downcounter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is calculated using the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

In this equation, the WDT reload value is the decimal value of the 24-bit value furnished by {WDTU[7:0], WDTH[7:0], WDTL[7:0]}; the typical Watchdog Timer RC oscillator frequency is 10kHz. WDT cannot be refreshed after it reaches 000002H. The WDT reload value must not be set to values below 000004H.

Table 47 lists the approximate time-out delays based on minimum and maximum WDT reload values.

## 98

l O G

then passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's Baud Rate Generator and supports IrDA standard baud rates from 9600 baud to 115.2 Kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the infrared endec. The infrared endec data rate is calculated using the following equation.

Infrared Data Rate (bits/s) = <u>System Clock Frequency (Hz)</u> <u>16xUART Baud Rate Divisor Value</u>

## **Transmitting IrDA Data**

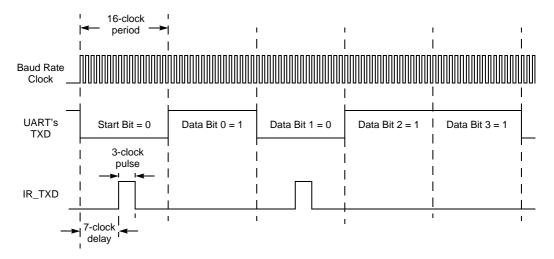

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16-clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains Low for the full 16-clock period. If the data to be transmitted is 0, a 3-clock High pulse is output following a 7-clock Low period. After the 3-clock High pulse, a 6-clock Low pulse is output to complete the full 16-clock data period. Figure 18 displays IrDA data transmission. When the infrared endec is enabled, the UART's TXD signal is internal to the Z8 Encore! XP<sup>®</sup> F0822 Series products while the IR\_TXD signal is output through the TXD pin.

145

#### Table 83. Z8 Encore! XP<sup>®</sup> F0822 Series Information Area Map

| Flash Memory<br>Address (Hex) | Function                                                                                    |

|-------------------------------|---------------------------------------------------------------------------------------------|

| FE00H–FE3FH                   | Reserved                                                                                    |

| FE40H–FE53H                   | Part Number<br>20-character ASCII alphanumeric code<br>Left-justified and filled with zeros |

| FE54H–FFFFH                   | Reserved                                                                                    |

## Operation

The Flash Controller provides the proper signals and timing for the Byte Programming, Page Erase, and Mass Erase functions within Flash memory. The Flash Controller contains a protection mechanism, using the Flash Control Register (FCTL), to prevent accidental programming or erasure. The following subsections provide details about the various operations (Lock, Unlock, Sector Protect, Byte Programming, Page Erase and Mass Erase).

## **Timing Using the Flash Frequency Registers**

Before performing a program or erase operation in Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasure of Flash memory with system clock frequencies ranging from 20kHz through 20MHz (the valid range is limited to the device operating frequencies).

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit Flash Frequency value must contain the system clock frequency in kHz. This value is calculated using the following equation:

FFREQ[15:0] = System Clock Frequency (Hz) 1000

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 20kHz, above 20MHz, or outside of the device operating frequency range. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper Flash programming and erase operations.

#### ilog Embedded in Life An TIXYS Company 146

## **Flash Read Protection**

The user code contained within Flash memory can be protected from external access. Programming the Flash Read Protect option bit prevents reading of user code by the OCD or by using the Flash Controller Bypass mode. For more information, see the <u>Option Bits</u> chapter on page 155 and the <u>On-Chip Debugger</u> chapter on page 158.

## **Flash Write/Erase Protection**

Z8 Encore! XP<sup>®</sup> F0822 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by the Flash Controller unlock mechanism, the Flash Sector Protect Register, and the Flash Write Protect option bit.

### Flash Controller Unlock Mechanism

At Reset, the Flash Controller locks to prevent accidental program or erasure of Flash memory. To program or erase Flash memory, the Flash Controller must be unlocked. After unlocking the Flash Controller, the Flash can be programmed or erased. Any value written by user code to the Flash Control Register or Page Select Register out of sequence locks the Flash Controller.

Observe the following procedure to unlock the Flash Controller from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write the page to be programmed or erased to the Page Select Register.

- 3. Write the first unlock command 73H to the Flash Control Register.

- 4. Write the second unlock command 8CH to the Flash Control Register.

- 5. Rewrite the page written in <u>Step 2</u> to the Page Select Register.

### **Flash Sector Protection**

The Flash Sector Protect Register is configured to prevent sectors from being programmed or erased. After a sector is protected, it cannot be unprotected by user code. The Flash Sector Protect Register is cleared after reset and any previously written protection values is lost. User code must write this register in the initialization routine if enable sector protection is appropriate.

The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register is accessed by writing the Flash Control Register with 5EH. After the Flash Sector Protect Register is selected, it can be accessed at the Page Select Register address. When the user code writes the Flash Sector Protect Register, bits can only be set to 1. Sectors can be protected, but not unprotected, using register write operations. Writing a value other than 5EH to the Flash Control Register deselects the Flash Sector Protect Register and reenables access to the Page Select Register.

nbedded in Life

151

## **Flash Status Register**

The Flash Status Register, shown in Table 85, indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its Register File address with the write-only Flash Control Register.

### Table 85. Flash Status Register (FSTAT)

| Bit     | 7    | 6     | 5     | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|-------|-------|---|---|---|---|---|--|

| Field   | Rese | erved | FSTAT |   |   |   |   |   |  |

| RESET   |      | 0     |       |   |   |   |   |   |  |

| R/W     |      | R     |       |   |   |   |   |   |  |

| Address |      | FF8H  |       |   |   |   |   |   |  |

| Bit   | Description                                           |  |  |  |  |  |

|-------|-------------------------------------------------------|--|--|--|--|--|

| [7:6] | Reserved                                              |  |  |  |  |  |

|       | These bits are reserved and must be programmed to 00. |  |  |  |  |  |

| [5:0] | Flash Controller Status                               |  |  |  |  |  |

| FSTAT | 00_0000 = Flash Controller locked.                    |  |  |  |  |  |

|       | 00_0001 = First unlock command received.              |  |  |  |  |  |

|       | 00_0010 = Second unlock command received.             |  |  |  |  |  |

|       | 00_0011 = Flash Controller unlocked.                  |  |  |  |  |  |

|       | 00_0100 = Flash Sector Protect Register selected.     |  |  |  |  |  |

|       | 00_1xxx = Program operation in progress.              |  |  |  |  |  |

|       | 01_0xxx = Page erase operation in progress.           |  |  |  |  |  |

|       | 10_0xxx = Mass erase operation in progress.           |  |  |  |  |  |

#### ilog Embedded in Life An TIXYS Company 161

## **Exiting Debug Mode**

The device exits DEBUG Mode following any of the following operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brown-Out reset

- Asserting the RESET pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP Mode initiates a System Reset

## **OCD Data Format**

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 start bit, 8 data bits (least-significant bit first), and 1 stop bit; see Figure 37.

| START         D0         D1         D2         D3         D4         D5         D6         D7         STC | START |

|-----------------------------------------------------------------------------------------------------------|-------|

|-----------------------------------------------------------------------------------------------------------|-------|

#### Figure 37. OCD Data Format

## **OCD** Autobaud Detector/Generator

To run over a range of baud rates (bits per second) with various system clock frequencies, the OCD contains an Autobaud Detector/Generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one start bit plus 7 data bits). The Autobaud Detector measures this period and sets the OCD Baud Rate Generator accordingly.

The Autobaud Detector/Generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation, the maximum recommended baud rate is the system clock frequency divided by 8. The theoretical maximum baud rate is the system clock frequency divided by 4. This theoretical maximum is possible for low-noise designs with clean signals. Table 92 lists minimum and recommended maximum baud rates for sample crystal frequencies.

#### TILOG TILOG TIXYS Company 166

or generate a BRK when its value matches the Program Counter. Because this register is really a down counter, the returned value is inverted when this register is read so the returned result appears to be an up counter. If the device is not in DEBUG Mode, this command returns FFFFH.

```

DBG \leftarrow 03H

DBG \rightarrow ~OCDCNTR[15:8]

DBG \rightarrow ~OCDCNTR[7:0]

```

Write OCD Control Register (04H). The Write OCD Control Register command writes the data that follows to the OCDCTL Register. When the Read Protect option bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of putting the device back into normal operating mode is to reset the device.

```

DBG \leftarrow 04H

DBG \leftarrow OCDCTL[7:0]

```

**Read OCD Control Register (05H).** The Read OCD Control Register command reads the value of the OCDCTL Register.

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

Write Program Counter (06H). The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter. If the device is not in DEBUG Mode or if the Read Protect option bit is enabled, the Program Counter values are discarded.

**Read Program Counter (07H).** The Read Program Counter command reads the value in the eZ8 CPU's Program Counter. If the device is not in DEBUG Mode or if the Read Protect option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

**Write Register (08H).** The Write Register command writes data to the Register File. Data can be written 1-256 bytes at a time (256 bytes can be written by setting size to zero). If the device is not in DEBUG Mode, the address and data values are discarded. If the Read Protect option bit is enabled, then only writes to the Flash Control registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

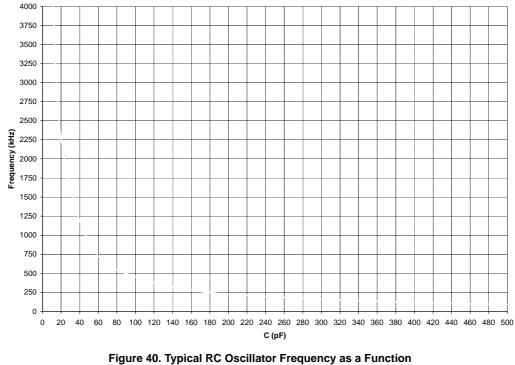

of External Capacitance with a 45kΩ Resistor

**Caution:** When using the external RC oscillator mode, the oscillator can stop oscillating if the power supply drops below 2.7 V, but before the power supply drops to the Voltage Brown-Out threshold. The oscillator resumes oscillation when the supply voltage exceeds 2.7 V.

194

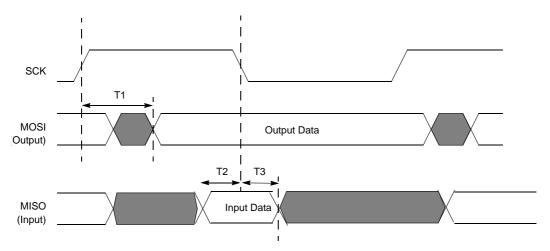

## **SPI MASTER Mode Timing**

Figure 51 and Table 109 provide timing information for SPI MASTER Mode pins. Timing is shown with SCK rising edge used to source MOSI output data, SCK falling edge used to sample MISO input data. Timing on the SS output pin(s) is controlled by software.

Figure 51. SPI MASTER Mode Timing

|           |                                     | Delay (ns) |         |  |  |

|-----------|-------------------------------------|------------|---------|--|--|

| Parameter | Abbreviation                        | Minimum    | Maximum |  |  |

| SPI MASTE | R                                   |            |         |  |  |

| T.        | SCK Rise to MOSI output Valid Delay | -5         | +5      |  |  |

#### Table 109. SPI MASTER Mode Timing

SPI MASTER

T1

SCK Rise to MOSI output Valid Delay

-5

+5

T2

MISO input to SCK (receive edge) Setup Time

20

T3

MISO input to SCK (receive edge) Hold Time

0

# Appendix A. Register Summary

For the reader's convenience, this appendix lists all Z8 Encore! XP<sup>®</sup> F0822 Series registers numerically by hexadecimal address.

## **General Purpose RAM**

In the Z8 Encore! XP<sup>®</sup> F0822 Series, the 000–EFF hexadecimal address range is partitioned for general-purpose random access memory, as follows.

### Hex Addresses: 000–1FF

This address range is reserved for general-purpose register file RAM. For more details, see the <u>Register File Address Map</u> chapter on page 17.

### Hex Addresses: 200-EFF

This address range is reserved.

## **Timer 0 Control Registers**

For more information about these Timer Control registers, see the <u>Timer Control Register</u> <u>Definitions</u> section on page 64.

### Hex Address: F00

#### Table 130. Timer 0–1 High Byte Register (TxH)

| Bit     | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------------|---|---|---|---|---|---|---|--|

| Field   | TH         |   |   |   |   |   |   |   |  |

| RESET   | 0          |   |   |   |   |   |   |   |  |

| R/W     | R/W        |   |   |   |   |   |   |   |  |

| Address | F00H, F08H |   |   |   |   |   |   |   |  |

#### ilog Embedded in Life An LIXYS Company 237

## Hex Address: F67

#### Table 168. SPI Baud Rate Low Byte Register (SPIBRL)

| Bit     | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|---|---|---|---|---|---|---|--|

| Field   | BRL  |   |   |   |   |   |   |   |  |

| RESET   | 1    |   |   |   |   |   |   |   |  |

| R/W     | R/W  |   |   |   |   |   |   |   |  |

| Address | F67H |   |   |   |   |   |   |   |  |

#### Hex Addresses: F68–F6F

This address range is reserved.

## **Analog-to-Digital Converter Control Registers**

For more information about these ADC registers, see the <u>ADC Control Register Defini-</u> tions section on page 139.

### Hex Address: F70

#### Table 169. ADC Control Register (ADCCTL)

| Bit     | 7   | 6        | 5    | 4    | 3          | 2 | 1 | 0 |   |  |  |

|---------|-----|----------|------|------|------------|---|---|---|---|--|--|

| Field   | CEN | Reserved | VREF | CONT | ANAIN[3:0] |   |   |   |   |  |  |

| RESET   | (   | )        | 1    |      | 0          |   |   |   | 0 |  |  |

| R/W     | R/W |          |      |      |            |   |   |   |   |  |  |

| Address |     | F70H     |      |      |            |   |   |   |   |  |  |

### Hex Address: F71

This address is reserved.