Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Active                                                    |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 11                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 2x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0821ph020eg |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Timer Output Signal Operation    64                      |   |

|----------------------------------------------------------|---|

| Timer Control Register Definitions                       |   |

| Timer 0–1 High and Low Byte Registers                    |   |

| Timer Reload High and Low Byte Registers                 |   |

| Timer 0–1 PWM High and Low Byte Registers                |   |

| Timer 0–3 Control 0 Registers                            |   |

| Timer 0–1 Control 1 Registers                            |   |

| Watchdog Timer                                           |   |

| Operation                                                |   |

| Watchdog Timer Refresh                                   |   |

| Watchdog Timer Time-Out Response                         |   |

| Watchdog Timer Reload Unlock Sequence                    |   |

| Watchdog Timer Control Register Definitions              |   |

| Watchdog Timer Control Register                          |   |

| Watchdog Timer Reload Upper, High and Low Byte Registers |   |

| Universal Asynchronous Receiver/Transmitter              |   |

| Architecture                                             |   |

| Operation                                                | , |

| Transmitting Data using Polled Method                    |   |

| Transmitting Data Using Interrupt-Driven Method          |   |

| Receiving Data using the Polled Method                   |   |

| Receiving Data Using Interrupt-Driven Method             | , |

| Clear To Send Operation                                  |   |

| Multiprocessor (9-Bit) Mode                              |   |

| External Driver Enable                                   |   |

| UART Interrupts                                          |   |

| UART Baud Rate Generator                                 |   |

| UART Control Register Definitions                        |   |

| UART Transmit Data Register                              |   |

| UART Receive Data Register 89                            |   |

| UART Status 0 Register                                   |   |

| UART Status 1 Register                                   |   |

| UART Control 0 and Control 1 Registers                   |   |

| UART Address Compare Register                            |   |

| UART Baud Rate High and Low Byte Registers               |   |

| Infrared Encoder/Decoder                                 |   |

| Architecture                                             |   |

| Operation                                                |   |

| Transmitting IrDA Data                                   |   |

| Receiving IrDA Data                                      |   |

|                                                          |   |

ILO G

13

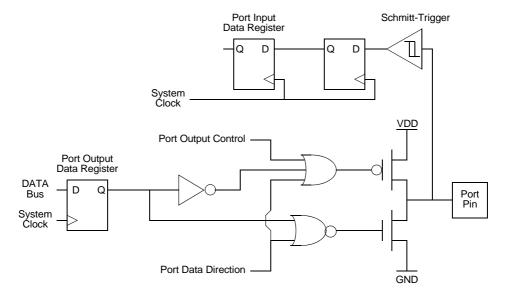

# **Pin Characteristics**

Table 4 provides detailed information about the characteristics for each pin available on Z8 Encore!  $XP^{\textcircled{B}}$  F0822 Series products. The data in Table 4 is sorted alphabetically by pin symbol mnemonic.

| Symbol<br>Mnemonic | Direction | Reset<br>Direction | Active<br>Low or<br>Active<br>High | Tri-State<br>Output | Internal<br>Pull-Up or<br>Pull-Down | Schmitt-Trigger<br>Input | Open Drain<br>Output   |

|--------------------|-----------|--------------------|------------------------------------|---------------------|-------------------------------------|--------------------------|------------------------|

| AV <sub>DD</sub>   | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| AV <sub>SS</sub>   | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| DBG                | I/O       | I                  | N/A                                | Yes                 | No                                  | Yes                      | Yes                    |

| PA[7:0]            | I/O       | I                  | N/A                                | Yes                 | Programma-<br>ble pull-up           | Yes                      | Yes, pro-<br>grammable |

| PB[4:0]            | I/O       | I                  | N/A                                | Yes                 | Programma-<br>ble pull-up           | Yes                      | Yes, pro-<br>grammable |

| PC[5:0]            | I/O       | I                  | N/A                                | Yes                 | Programma-<br>ble pull-up           | Yes                      | Yes, pro-<br>grammable |

| RESET              | I         | I                  | Low                                | N/A                 | Pull-up                             | Yes                      | N/A                    |

| V <sub>DD</sub>    | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| V <sub>REF</sub>   | Analog    | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| V <sub>SS</sub>    | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| X <sub>IN</sub>    | I         | I                  | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| X <sub>OUT</sub>   | 0         | 0                  | N/A                                | No                  | No                                  | No                       | No                     |

### **Table 4. Pin Characteristics**

# Embedded in Life An TIXYS Company 30

| Port   | Pin      | Mnemonic   | Alternate Function Description                    |

|--------|----------|------------|---------------------------------------------------|

| Port A | PA0 TOIN |            | Timer 0 Input                                     |

|        | PA1      | T0OUT      | Timer 0 Output                                    |

|        | PA2      | DE         | UART 0 Driver Enable                              |

|        | PA3      | CTS0       | UART 0 Clear to Send                              |

|        | PA4      | RXD0/IRRX0 | UART 0/IrDA 0 Receive Data                        |

|        | PA5      | TXD0/IRTX0 | UART 0/IrDA 0 Transmit Data                       |

|        | PA6      | SCL        | I <sup>2</sup> C Clock (automatically open-drain) |

|        | PA7      | SDA        | I <sup>2</sup> C Data (automatically open-drain)  |

| Port B | PB0      | ANA0       | ADC Analog Input 0                                |

|        | PB1      | ANA1       | ADC Analog Input 1                                |

|        | PB2      | ANA2       | ADC Analog Input 2                                |

|        | PB3      | ANA3       | ADC Analog Input 3                                |

|        | PB4      | ANA4       | ADC Analog Input 4                                |

|        |          |            |                                                   |

### Table 12. Port Alternate Function Mapping

### ilog° Embedded in Life An∎IXYS Company

33

# Port A–C Control Registers

The Port A–C Control registers, shown in Table 15, set the GPIO port operation. The value in the corresponding Port A–C Address Register determines the control subregisters accessible using the Port A–C Control Register.

### Table 15. Port A–C Control Registers (PxCTL)

| Bit     | 7                | 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |

|---------|------------------|-----------------|--|--|--|--|--|--|

| Field   |                  | PCTL            |  |  |  |  |  |  |

| RESET   |                  | 00H             |  |  |  |  |  |  |

| R/W     | R/W              |                 |  |  |  |  |  |  |

| Address | FD1H, FD5H, FD9H |                 |  |  |  |  |  |  |

| Bit   | Description                                                                                           |

|-------|-------------------------------------------------------------------------------------------------------|

| [7:0] | <b>Port Control</b>                                                                                   |

| PCTL  | The Port Control Register provides access to all subregisters that configure the GPIO port operation. |

# Port A–C Data Direction Subregisters

The Port A–C Data Direction Subregister, shown in Table 16, is accessed through the Port A–C Control Register by writing 01H to the Port A–C Address Register.

| Table 16. F | Port A–C Data | Direction | Subregisters |

|-------------|---------------|-----------|--------------|

|-------------|---------------|-----------|--------------|

| Bit                                                                                                                | 7             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------------------------------------------------------------------------------------------------------------------|---------------|-----|-----|-----|-----|-----|-----|-----|

| Field                                                                                                              | DD7           | DD6 | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |

| RESET                                                                                                              |               | 1   |     |     |     |     |     |     |

| R/W                                                                                                                | R/W           |     |     |     |     |     |     |     |

| Address                                                                                                            | See footnote. |     |     |     |     |     |     |     |

| Note: If 01H is written to the Port A–C Address Register, then it is accessible via the Port A–C Control Register. |               |     |     |     |     |     |     |     |

| Bit   | Description                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | Data Direction                                                                                                                                                                                                                                                                                                                                                                                          |

| DDx   | <ul> <li>These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction Register setting.</li> <li>0 = Output. Data in the Port A–C Output Data Register is driven onto the port pin.</li> <li>1 = Input. The port pin is sampled and the value written into the Port A–C Input Data Register. The output driver is tri-stated.</li> </ul> |

| Note: | x indicates register bits in the range [7:0].                                                                                                                                                                                                                                                                                                                                                           |

### Port A–C High Drive Enable Subregisters

The Port A–C High Drive Enable Subregister, shown in Table 19, is accessed through the Port A–C Control Register by writing 04H to the Port A–C Address Register. Setting the bits in the Port A-C High Drive Enable subregisters to 1 configures the specified port pins for high-output current drive operation. The Port A-C High Drive Enable Subregister affects the pins directly and, as a result, alternate functions are also affected.

### Table 19. Port A–C High Drive Enable Subregisters

| Bit         | 7                                                                                                         | 6             | 5     | 4     | 3     | 2     | 1     | 0     |

|-------------|-----------------------------------------------------------------------------------------------------------|---------------|-------|-------|-------|-------|-------|-------|

| Field       | PHDE7                                                                                                     | PHDE6         | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |

| RESET       |                                                                                                           | 0             |       |       |       |       |       |       |

| R/W         |                                                                                                           | R/W           |       |       |       |       |       |       |

| Address     |                                                                                                           | See footnote. |       |       |       |       |       |       |

| Note: If 04 | 04H is written to the Port A–C Address Register, then it is accessible via the Port A–C Control Register. |               |       |       |       |       |       |       |

| Bit         | Descriptio                                                                                                | n             |       |       |       |       |       |       |

# Description

#### [7:0] Port High Drive Enabled

PHDEx 0 = The port pin is configured for standard-output current drive. 1 = The port pin is configured for high-output current drive.

Note: x indicates register bits in the range [7:0].

# Embedded in Life

53

# Interrupt Control Register

The Interrupt Control (IRQCTL) Register, shown in Table 38, contains the master enable bit for all interrupts.

# Table 38. Interrupt Control Register (IRQCTL)

| Bit     | 7    | 6    | 5        | 4 | 3 | 2 | 1 | 0 |

|---------|------|------|----------|---|---|---|---|---|

| Field   | IRQE |      | Reserved |   |   |   |   |   |

| RESET   |      | 0    |          |   |   |   |   |   |

| R/W     | R/W  | R    |          |   |   |   |   |   |

| Address |      | FCFH |          |   |   |   |   |   |

| Bit         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]<br>IRQE | <ul> <li>Interrupt Request Enable</li> <li>This bit is set to 1 by execution of an Enable Interrupts (EI) or Interrupt Return (IRET) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, Reset or by a direct register write of a 0 to this bit.</li> <li>0 = Interrupts are disabled.</li> <li>1 = Interrupts are enabled.</li> </ul> |

| [6:0]       | <b>Reserved</b><br>These bits are reserved and must be programmed to 000000.                                                                                                                                                                                                                                                                                                                                                                       |

ilog° Embedded in Life An∎IXYS Company 72

To minimize power consumption in STOP Mode, the WDT and its RC oscillator is disabled in STOP Mode. The following sequence configures the WDT to be disabled when the Z8F082x family device enters STOP Mode following execution of a stop instruction:

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write 81H to the Watchdog Timer Control Register (WDTCTL) to configure the WDT and its oscillator to be disabled during STOP Mode. Alternatively, write 00H to the WDTCTL as the third step in this sequence to reconfigure the WDT and its oscillator to be enabled during STOP Mode. This sequence only affects WDT operation in STOP Mode.

### WDT Reset in Normal Operation

If configured to generate a Reset when a time-out occurs, the WDT forces the device into the Reset state. The WDT status bit in the WDT Control Register is set to 1. For more information about Reset, see the <u>Reset and Stop Mode Recovery</u> chapter on page 21.

### WDT Reset in STOP Mode

If enabled in STOP Mode and configured to generate a Reset when a time-out occurs and the device is in STOP Mode, the WDT initiates a Stop Mode Recovery. Both the WDT status bit and the stop bit in the WDT Control Register is set to 1 following WDT time-out in STOP Mode. For more information about Reset, see the <u>Reset and Stop Mode Recovery</u> chapter on page 21. Default operation is for the WDT and its RC oscillator to be enabled during STOP Mode.

### WDT RC Disable in STOP Mode

To minimize power consumption in STOP Mode, the WDT and its RC oscillator can be disabled in STOP Mode. The following sequence configures the WDT to be disabled when the Z8F082x family device enters STOP Mode following execution of a stop instruction:

- 1. Write 55H to the Watchdog Timer Control Register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control Register (WDTCTL).

- 3. Write 81H to the Watchdog Timer Control Register (WDTCTL) to configure the WDT and its oscillator to be disabled during STOP Mode. Alternatively, write 00H to the Watchdog Timer Control Register (WDTCTL) as the third step in this sequence to reconfigure the WDT and its oscillator to be enabled during STOP Mode. This sequence only affects WDT operation in STOP Mode.

# Embedded in Life An IXYS Company

# **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers, shown in Tables 57 and 58, configure the properties of the UART's transmit and receive operations. The UART Control registers must not been written while the UART is enabled.

## Table 57. UART Control 0 Register (U0CTL0)

| Bit        | 7                                                                                                                                                                                                | 6                                                                    | 5              | 4            | 3               | 2                               | 1             | 0            |  |  |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------|--------------|-----------------|---------------------------------|---------------|--------------|--|--|--|--|--|

| Field      | TEN                                                                                                                                                                                              | REN                                                                  | CTSE           | PEN          | PSEL            | SBRK                            | STOP          | LBEN         |  |  |  |  |  |

| RESET      |                                                                                                                                                                                                  |                                                                      |                | (            | )               |                                 |               |              |  |  |  |  |  |

| R/W        |                                                                                                                                                                                                  |                                                                      |                | R/           | W               |                                 |               |              |  |  |  |  |  |

| Address    |                                                                                                                                                                                                  |                                                                      |                | F4           | 2H              |                                 |               |              |  |  |  |  |  |

| Bit        | Descriptio                                                                                                                                                                                       | n                                                                    |                |              |                 |                                 |               |              |  |  |  |  |  |

| [7]        | -                                                                                                                                                                                                | Transmit Enable                                                      |                |              |                 |                                 |               |              |  |  |  |  |  |

| TEN        | This bit enables or disables the transmitter. The enable is also controlled by the $\overline{\text{CTS}}$ signal                                                                                |                                                                      |                |              |                 |                                 |               |              |  |  |  |  |  |

|            | and the CTSE bit. If the CTS signal is Low and the CTSE bit is 1, the transmitter is enabled.                                                                                                    |                                                                      |                |              |                 |                                 |               |              |  |  |  |  |  |

|            | 0 = Transmitter disabled.<br>1 = Transmitter enabled.                                                                                                                                            |                                                                      |                |              |                 |                                 |               |              |  |  |  |  |  |

| [6]        | 1 = Transmitter enabled. Receive Enable                                                                                                                                                          |                                                                      |                |              |                 |                                 |               |              |  |  |  |  |  |

| [6]<br>REN |                                                                                                                                                                                                  |                                                                      | bles the rec   | eiver.       |                 |                                 |               |              |  |  |  |  |  |

|            |                                                                                                                                                                                                  | This bit enables or disables the receiver.<br>0 = Receiver disabled. |                |              |                 |                                 |               |              |  |  |  |  |  |

|            | 1 = Receiver enabled.                                                                                                                                                                            |                                                                      |                |              |                 |                                 |               |              |  |  |  |  |  |

| [5]        | CTS Enabl                                                                                                                                                                                        |                                                                      |                |              |                 |                                 |               |              |  |  |  |  |  |

| CTSE       |                                                                                                                                                                                                  | S signal has                                                         |                |              |                 | trol from the                   | a transmitter |              |  |  |  |  |  |

| [4]        | Parity Ena                                                                                                                                                                                       |                                                                      |                | Signal as al |                 |                                 |               | •            |  |  |  |  |  |

| PEN        |                                                                                                                                                                                                  | ables or disa                                                        | bles parity. I | Even or odd  | is determine    | ed by the PS                    | SEL bit. This | bit is over- |  |  |  |  |  |

|            | ridden by th                                                                                                                                                                                     | ne MPEN bit                                                          |                |              |                 |                                 |               |              |  |  |  |  |  |

|            | 0 = Parity is                                                                                                                                                                                    |                                                                      | da data with   | on addition  | ol pority bit   | and the read                    |               | o on oddi    |  |  |  |  |  |

|            |                                                                                                                                                                                                  | nsmitter sen<br>arity bit.                                           | us uala will   | an addition  | ai panty bit a  |                                 |               | s an auui-   |  |  |  |  |  |

| [3]        | Parity Sele                                                                                                                                                                                      | -                                                                    |                |              |                 |                                 |               |              |  |  |  |  |  |

| PSEL       |                                                                                                                                                                                                  | arity is trans                                                       |                |              |                 |                                 |               |              |  |  |  |  |  |

|            | •                                                                                                                                                                                                | rity is transn                                                       | nitted and ex  | pected on a  | all received of | data.                           |               |              |  |  |  |  |  |

| [2]        | Send Brea                                                                                                                                                                                        |                                                                      |                |              | (               | · · · · · · · · · · · · · · · · |               | 0            |  |  |  |  |  |

| SBRK       | This bit pauses or breaks data transmission by forcing the Transmit data output to 0. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished send- |                                                                      |                |              |                 |                                 |               |              |  |  |  |  |  |

|            |                                                                                                                                                                                                  | fore setting                                                         |                |              |                 |                                 |               |              |  |  |  |  |  |

|            |                                                                                                                                                                                                  | easserted. S                                                         |                |              | uration of the  | e break and                     | the duration  | of any       |  |  |  |  |  |

|            | appropriate<br>0 = No brea                                                                                                                                                                       | e stop bit tim<br>ek is sent                                         | e following t  | he break.    |                 |                                 |               |              |  |  |  |  |  |

|            |                                                                                                                                                                                                  | tput of the tr                                                       | ansmitter is   | zero.        |                 |                                 |               |              |  |  |  |  |  |

|            |                                                                                                                                                                                                  |                                                                      | -              |              |                 |                                 |               |              |  |  |  |  |  |

# Embedded in Life

97

# Infrared Encoder/Decoder

Z8 Encore! XP<sup>®</sup> F0822 Series products contain a fully-functional, high-performance UART to Infrared Encoder/Decoder (endec). The infrared endec is integrated with an onchip UART to allow easy communication between the Z8 Encore! XP and IrDA Physical Layer Specification, v1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers, and other infrared enabled devices.

# Architecture

Figure 17 displays the architecture of the infrared endec.

Figure 17. Infrared Data Communication System Block Diagram

# Operation

When the infrared endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Similarly, data received from the infrared transceiver is passed to the infrared endec through the RXD pin, decoded by the infrared endec, and

- 1. Software writes 11110B followed by the two address bits and a 0 (write) to the I<sup>2</sup>C Data Register.

- 2. Software asserts the start and TXI bits of the I<sup>2</sup>C Control Register.

- 3. The  $I^2C$  Controller sends the start condition.

- 4. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register.

- 5. After the first bit has been shifted out, a transmit interrupt is asserted.

- 6. Software responds by writing the lower eight bits of address to the  $I^2C$  Data Register.

- 7. The  $I^2C$  Controller completes shifting of the two address bits and a 0 (write).

- If the I<sup>2</sup>C Slave acknowledges the first address byte by pulling the SDA signal Low during the next High period of SCL, the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status Register. Continue to <u>Step 9</u>.

If the slave does not acknowledge the first address byte, the  $I^2C$  Controller sets the NCKI bit and clears the ACK bit in the  $I^2C$  Status Register. Software responds to the Not Acknowledge interrupt by setting the stop and flush bits and clearing the TXI bit. The  $I^2C$  Controller sends the stop condition on the bus and clears the stop and NCKI bits. The transaction is complete (ignore following steps).

- 9. The I<sup>2</sup>C Controller loads the I<sup>2</sup>C Shift Register with the contents of the I<sup>2</sup>C Data Register (second address byte).

- 10. The I<sup>2</sup>C Controller shifts out the second address byte. After the first bit is shifted, the I<sup>2</sup>C Controller generates a transmit interrupt.

- 11. Software responds by setting the start bit of the I<sup>2</sup>C Control Register to generate a repeated start and by clearing the TXI bit.

- 12. Software responds by writing 11110B followed by the 2-bit Slave address and a 1 (read) to the I<sup>2</sup>C Data Register.

- 13. If only one byte is to be read, software sets the NAK bit of the  $I^2C$  Control Register.

- 14. After the I<sup>2</sup>C Controller shifts out the 2nd address byte, the I<sup>2</sup>C Slave sends an acknowledge by pulling the SDA signal Low during the next High period of SCL, the I<sup>2</sup>C Controller sets the ACK bit in the I<sup>2</sup>C Status Register. Continue to <u>Step 15</u>.

If the slave does not acknowledge the second address byte, the I<sup>2</sup>C Controller sets the NCKI bit and clears the ACK bit in the I<sup>2</sup>C Status Register. Software responds to the Not Acknowledge interrupt by setting the stop and flush bits and clearing the TXI bit. The I<sup>2</sup>C Controller sends the stop condition on the bus and clears the stop and NCKI bits. The transaction is complete; ignore the remainder of this sequence.

15. The I<sup>2</sup>C Controller sends the repeated start condition.

- 1. Enable the appropriate analog inputs by configuring the GPIO pins for alternate function. This configuration disables the digital input and output drivers.

- 2. Write to the ADC Control Register to configure the ADC and begin the conversion. The following bit fields in the ADC Control Register are written simultaneously:

- Write to the ANAIN[3:0] field to select one of the 5 analog input sources

- Clear CONT to 0 to select a single-shot conversion

- Write to the  $\overline{\text{VREF}}$  bit to enable or disable the internal voltage reference generator

- Set CEN to 1 to start the conversion

- 3. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power-up before beginning the 5129 cycle conversion.

- 4. When the conversion is complete, the ADC control logic performs the following operations:

- 10-bit data result written to {ADCD\_H[7:0], ADCD\_L[7:6]}

- CEN resets to 0 to indicate the conversion is complete

- An interrupt request is sent to the Interrupt Controller

- 5. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

# **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analog-to-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS Mode, ensure that ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not seen at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Observe the following procedure for setting up the ADC and initiating continuous conversion:

1. Enable the appropriate analog input by configuring the GPIO pins for alternate function. This disables the digital input and output driver.

Observe the following procedure to setup the Flash Sector Protect Register from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write 5EH to the Flash Control Register to select the Flash Sector Protect Register.

- 3. Read and/or write the Flash Sector Protect Register which is now at Register File address FF9H.

- 4. Write 00H to the Flash Control Register to return the Flash Controller to its reset state.

### **Flash Write Protection Option Bit**

The Flash Write Protect option bit can block all program and erase operations from user code. For more information, see the <u>Option Bits</u> chapter on page 155.

# **Byte Programming**

When the Flash Controller is unlocked, writes to Flash memory from user code programs a byte into the Flash if the address is located in the unlocked page. An erased Flash byte contains all 1s (FFH). The programming operation is used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from zero to one requires a Page Erase or Mass Erase operation.

Byte programming is accomplished using the eZ8 CPU's LDC or LDCI instructions. Refer to the <u>eZ8 CPU Core User Manual (UM0128)</u> for a description of the LDC and LDCI instructions.

While the Flash Controller programs the contents of Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Interrupts that occur when a programming operation is in progress are serviced after the programming operation is complete. To exit programming mode and lock the Flash Controller, write 00H to the Flash Control Register.

User code cannot program Flash memory on a page that is located in a protected sector. When user code writes memory locations, only addresses located in the unlocked page are programmed. Memory writes outside of the unlocked page are ignored.

**Caution:** Each memory location must not be programmed more than twice before an erase occurs.

Observe the following procedure to program the Flash from user code:

- 1. Write 00H to the Flash Control Register to reset the Flash Controller.

- 2. Write the page of memory to be programmed to the Page Select Register.

- 3. Write the first unlock command 73H to the Flash Control Register.

# ilog Embedded in Life

# **DC Characteristics**

Table 98 lists the DC characteristics of the Z8 Encore!  $XP^{\mbox{\ensuremath{\mathbb{R}}}}$  F0822 Series products. All voltages are referenced to  $V_{SS}$ , the primary system ground.

|                  |                                            | T <sub>A</sub> =    | <b>-40°C to</b> 1 | 105°C                |       |                                                                                                                                              |  |  |  |  |

|------------------|--------------------------------------------|---------------------|-------------------|----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol           | Parameter                                  | Minimum             | Typical           | Maximum              | Units | Conditions                                                                                                                                   |  |  |  |  |

| V <sub>DD</sub>  | Supply Voltage                             | 2.7                 | _                 | 3.6                  | V     |                                                                                                                                              |  |  |  |  |

| V <sub>IL1</sub> | Low Level Input<br>Voltage                 | -0.3                | -                 | 0.3*V <sub>DD</sub>  | V     | For all input pins except RESET, DBG, and X <sub>IN</sub> .                                                                                  |  |  |  |  |

| V <sub>IL2</sub> | Low Level Input<br>Voltage                 | -0.3                | -                 | 0.2*V <sub>DD</sub>  | V     | For RESET, DBG, and X <sub>IN</sub> .                                                                                                        |  |  |  |  |

| V <sub>IH1</sub> | High Level Input<br>Voltage                | 0.7*V <sub>DD</sub> | -                 | 5.5                  | V     | Ports A and C pins when their programmable pull-ups are disabled.                                                                            |  |  |  |  |

| V <sub>IH2</sub> | High Level Input<br>Voltage                | 0.7*V <sub>DD</sub> | -                 | V <sub>DD</sub> +0.3 | V     | Port B pins. Ports A and C pins when their programmable pull-<br>ups are enabled.                                                            |  |  |  |  |

| V <sub>IH3</sub> | High Level Input<br>Voltage                | 0.8*V <sub>DD</sub> | -                 | V <sub>DD</sub> +0.3 | V     | RESET, DBG, and X <sub>IN</sub> pins.                                                                                                        |  |  |  |  |

| V <sub>OL1</sub> | Low Level Output<br>Voltage                | -                   | _                 | 0.4                  | V     | I <sub>OL</sub> = 2 mA; V <sub>DD</sub> = 3.0V<br>High Output Drive disabled.                                                                |  |  |  |  |

| V <sub>OH1</sub> | High Level Output<br>Voltage               | 2.4                 | -                 | _                    | V     | $I_{OH} = -2 \text{ mA}; V_{DD} = 3.0 \text{ V}$<br>High Output Drive disabled.                                                              |  |  |  |  |

| V <sub>OL2</sub> | Low Level Output<br>Voltage High<br>Drive  | -                   | _                 | 0.6                  | V     | $I_{OL} = 20 \text{ mA}; V_{DD} = 3.3 \text{ V}$<br>High Output Drive enabled<br>$T_A = -40^{\circ}\text{C} \text{ to } +70^{\circ}\text{C}$ |  |  |  |  |

| V <sub>OH2</sub> | High Level Output<br>Voltage High<br>Drive | 2.4                 | -                 | -                    | V     | $I_{OH} = -20$ mA; $V_{DD} = 3.3$ V<br>High Output Drive enabled;<br>$T_A = -40^{\circ}$ C to +70°C                                          |  |  |  |  |

| V <sub>OL3</sub> | Low Level Output<br>Voltage High<br>Drive  | -                   | -                 | 0.6                  | V     | $I_{OL} = 15$ mA; $V_{DD} = 3.3$ V<br>High Output Drive enabled;<br>$T_A = +70^{\circ}$ C to $+105^{\circ}$ C                                |  |  |  |  |

| V <sub>OH3</sub> | High Level Output<br>Voltage High<br>Drive | 2.4                 | _                 | _                    | V     | $I_{OH}$ = 15 mA; $V_{DD}$ = 3.3V<br>High Output Drive enabled;<br>$T_A$ = +70°C to +105°C                                                   |  |  |  |  |

| V <sub>RAM</sub> | RAM Data<br>Retention                      | 0.7                 | -                 | _                    | V     |                                                                                                                                              |  |  |  |  |

| I <sub>IL</sub>  | Input Leakage<br>Current                   | -5                  | _                 | +5                   | μA    | $V_{DD} = 3.6 \text{ V};$<br>$V_{IN} = V_{DD} \text{ or } V_{SS}^{1}$                                                                        |  |  |  |  |

### Table 98. DC Characteristics

O g

An IXYS Company

192

# General Purpose I/O Port Output Timing

X<sub>IN</sub>

Figure 49 and Table 107 provide timing information for GPIO port pins.

|                |                                                 | Dela    | ay (ns) |  |  |

|----------------|-------------------------------------------------|---------|---------|--|--|

| Parameter      | Abbreviation                                    | Minimum | Maximum |  |  |

| GPIO Port I    | Pins                                            |         |         |  |  |

| T <sub>1</sub> | X <sub>IN</sub> Rise to Port Output Valid Delay | _       | 15      |  |  |

| T <sub>2</sub> | X <sub>IN</sub> Rise to Port Output Hold Time   | 2       | _       |  |  |

### Table 107. GPIO Port Output Timing

### ilog Embedded in Life An LIXYS Company 203

# **Condition Codes**

The C, Z, S, and V flags control the operation of the conditional jump (JP cc and JR cc) instructions. Sixteen frequently useful functions of the flag settings are encoded in a 4-bit field called the condition code (cc), which forms Bits 7:4 of the conditional jump instructions. The condition codes are summarized in Table 118. Some binary condition codes can be created using more than one assembly code mnemonic. The result of the flag test operation decides if the conditional jump is executed.

| Binary | Hex | Assembly<br>Mnemonic | Definition                        | Flag Test Operation   |

|--------|-----|----------------------|-----------------------------------|-----------------------|

| 0000   | 0   | F                    | Always False                      | -                     |

| 0001   | 1   | LT                   | Less Than                         | (S XOR V) = 1         |

| 0010   | 2   | LE                   | Less Than or Equal                | (Z OR (S XOR V)) = 1  |

| 0011   | 3   | ULE                  | Unsigned Less Than or Equal       | (C OR Z) = 1          |

| 0100   | 4   | OV                   | Overflow                          | V = 1                 |

| 0101   | 5   | MI                   | Minus                             | S = 1                 |

| 0110   | 6   | Z                    | Zero                              | Z = 1                 |

| 0110   | 6   | EQ                   | Equal                             | Z = 1                 |

| 0111   | 7   | С                    | Carry                             | C = 1                 |

| 0111   | 7   | ULT                  | Unsigned Less Than                | C = 1                 |

| 1000   | 8   | T (or blank)         | Always True                       | -                     |

| 1001   | 9   | GE                   | Greater Than or Equal             | (S XOR V) = 0         |

| 1010   | А   | GT                   | Greater Than                      | (Z OR (S XOR V)) = 0  |

| 1011   | В   | UGT                  | Unsigned Greater Than             | (C = 0 AND Z = 0) = 1 |

| 1100   | С   | NOV                  | No Overflow                       | V = 0                 |

| 1101   | D   | PL                   | Plus                              | S = 0                 |

| 1110   | Е   | NZ                   | Non-Zero                          | Z = 0                 |

| 1110   | Е   | NE                   | Not Equal                         | Z = 0                 |

| 1111   | F   | NC                   | No Carry                          | C = 0                 |

| 1111   | F   | UGE                  | Unsigned Greater Than or<br>Equal | C = 0                 |

### Table 118. Condition Codes

Embedded in Life

211

| Assembly     | Symbolic                                                                                                                                           | Address<br>Mode |     | Op<br>₋ Code(s) |   |   | Fla | ıgs | Fetch | Instr. |        |        |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----------------|---|---|-----|-----|-------|--------|--------|--------|

| Mnemonic     | Operation                                                                                                                                          | dst             | src | (Hex)           | С | Ζ | S   | ۷   | D     | н      | Cycles | Cycles |

| DECW dst     | dst ← dst – 1                                                                                                                                      | RR              |     | 80              | - | * | *   | *   | -     | -      | 2      | 5      |

|              |                                                                                                                                                    | IRR             |     | 81              | - |   |     |     |       |        | 2      | 6      |

| DI           | $IRQCTL[7] \leftarrow 0$                                                                                                                           |                 |     | 8F              | - | - | -   | -   | -     | -      | 1      | 2      |

| DJNZ dst, RA | $dst \leftarrow dst - 1$<br>if dst $\neq 0$<br>PC $\leftarrow$ PC + X                                                                              | r               |     | 0A-FA           | - | - | -   | -   | -     | -      | 2      | 3      |

| EI           | IRQCTL[7] ← 1                                                                                                                                      |                 |     | 9F              | - | - | -   | -   | -     | -      | 1      | 2      |

| HALT         | HALT Mode                                                                                                                                          |                 |     | 7F              | - | - | -   | -   | -     | -      | 1      | 2      |

| INC dst      | dst ← dst + 1                                                                                                                                      | R               |     | 20              | - | * | *   | *   | -     | -      | 2      | 2      |

|              |                                                                                                                                                    | IR              |     | 21              | - |   |     |     |       | -      | 2      | 3      |

|              |                                                                                                                                                    | r               |     | 0E-FE           | - |   |     |     |       | -      | 1      | 2      |

| INCW dst     | dst ← dst + 1                                                                                                                                      | RR              |     | A0              | - | * | *   | *   | -     | -      | 2      | 5      |

|              |                                                                                                                                                    | IRR             |     | A1              | - |   |     |     |       | -      | 2      | 6      |

| IRET         | $\begin{array}{l} FLAGS \leftarrow @SP \\ SP \leftarrow SP + 1 \\ PC \leftarrow @SP \\ SP \leftarrow SP + 2 \\ IRQCTL[7] \leftarrow 1 \end{array}$ |                 |     | BF              | * | * | *   | *   | *     | *      | 1      | 5      |

| JP dst       | PC ← dst                                                                                                                                           | DA              |     | 8D              | - | - | -   | -   | -     | -      | 3      | 2      |

|              |                                                                                                                                                    | IRR             |     | C4              | - |   |     |     |       | -      | 2      | 3      |

| JP cc, dst   | if cc is true<br>PC $\leftarrow$ dst                                                                                                               | DA              |     | 0D-FD           | - | - | -   | -   | -     | -      | 3      | 2      |

| JR dst       | $PC \gets PC + X$                                                                                                                                  | DA              |     | 8B              | - | - | -   | -   | -     | -      | 2      | 2      |

| JR cc, dst   | if cc is true<br>PC $\leftarrow$ PC + X                                                                                                            | DA              |     | 0B-FB           | - | - | -   | -   | -     | -      | 2      | 2      |

## Table 127. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

Embedded in Life

214

| Assembly      | Symbolic                                                                 | Mor |     | Address Op<br>Mode Code(s) |   |   | Fla | ıgs |   | Fetch | Instr. |        |

|---------------|--------------------------------------------------------------------------|-----|-----|----------------------------|---|---|-----|-----|---|-------|--------|--------|

| Mnemonic      | Operation                                                                | dst | src | (Hex)                      | С | Ζ | S   | ۷   | D | н     | Cycles | Cycles |

| POPX dst      | dst $\leftarrow @SP$<br>SP $\leftarrow$ SP + 1                           | ER  |     | D8                         | - | - | -   | -   | - | -     | 3      | 2      |

| PUSH src      | $SP \leftarrow SP - 1$                                                   | R   |     | 70                         | - | - | -   | -   | - | -     | 2      | 2      |

|               | $@SP \leftarrow src$                                                     | IR  |     | 71                         | - |   |     |     |   | -     | 2      | 3      |

| PUSHX src     | $SP \leftarrow SP - 1$<br>@SP ← src                                      | ER  |     | C8                         | - | - | -   | -   | - | -     | 3      | 2      |

| RCF           | C ← 0                                                                    |     |     | CF                         | 0 | - | -   | -   | - | -     | 1      | 2      |

| RET           | $\begin{array}{l} PC \leftarrow @SP \\ SP \leftarrow SP + 2 \end{array}$ |     |     | AF                         | - | - | -   | -   | - | -     | 1      | 4      |

| RL dst        |                                                                          | R   |     | 90                         | * | * | *   | *   | - | -     | 2      | 2      |

|               | □                                                                        | IR  |     | 91                         | - |   |     |     |   | -     | 2      | 3      |

| RLC dst       |                                                                          | R   |     | 10                         | * | * | *   | *   | - | -     | 2      | 2      |

|               | C  D7D6D5D4D3D2D1D0 dst                                                  | IR  |     | 11                         | - |   |     |     |   | -     | 2      | 3      |

| RR dst        |                                                                          | R   |     | E0                         | * | * | *   | *   | - | -     | 2      | 2      |

|               | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C<br>dst                                     | IR  |     | E1                         | - |   |     |     |   | -     | 2      | 3      |

| RRC dst       |                                                                          | R   |     | C0                         | * | * | *   | *   | - | -     | 2      | 2      |

|               | ► D7 D6 D5 D4 D3 D2 D1 D0 - C                                            | IR  |     | C1                         | - |   |     |     |   | -     | 2      | 3      |

| SBC dst, src  | $dst \gets dst - src - C$                                                | r   | r   | 32                         | * | * | *   | *   | 1 | *     | 2      | 3      |

|               |                                                                          | r   | Ir  | 33                         | _ |   |     |     |   | -     | 2      | 4      |

|               | _                                                                        | R   | R   | 34                         | _ |   |     |     |   | -     | 3      | 3      |

|               | _                                                                        | R   | IR  | 35                         | _ |   |     |     |   | _     | 3      | 4      |

|               | _                                                                        | R   | IM  | 36                         | _ |   |     |     |   | -     | 3      | 3      |

|               |                                                                          | IR  | IM  | 37                         |   |   |     |     |   |       | 3      | 4      |

| SBCX dst, src | $dst \leftarrow dst - src - C$                                           | ER  | ER  | 38                         | * | * | *   | *   | 1 | *     | 4      | 3      |

|               |                                                                          | ER  | IM  | 39                         |   |   |     |     |   |       | 4      | 3      |

| SCF           | C ← 1                                                                    |     |     | DF                         | 1 | - | -   | -   | - | -     | 1      | 2      |

| SRA dst       | <u> </u>                                                                 | R   |     | D0                         | * | * | *   | 0   | - |       | 2      | 2      |

|               | −D7 D6 D5 D4 D3 D2 D1 D0 → C<br>dst                                      | IR  |     | D1                         |   |   |     |     |   |       | 2      | 3      |

### Table 127. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

– = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

Embedded in Life An LIXYS Company 216

| Assembly      | Symbolic                                                                                                               |     | dress<br>ode | Op<br>Code(s) |   |   | Fla | ıgs |   |   | Fetch  | Instr.<br>Cycles |

|---------------|------------------------------------------------------------------------------------------------------------------------|-----|--------------|---------------|---|---|-----|-----|---|---|--------|------------------|

| Mnemonic      | Operation                                                                                                              | dst | src          |               | С | Ζ | S   | ۷   | D | н | Cycles |                  |

| TM dst, src   | dst AND src                                                                                                            | r   | r            | 72            | - | * | *   | 0   | - | - | 2      | 3                |

|               |                                                                                                                        | r   | lr           | 73            | - |   |     |     |   |   | 2      | 4                |

|               |                                                                                                                        | R   | R            | 74            | - |   |     |     |   |   | 3      | 3                |

|               |                                                                                                                        | R   | IR           | 75            | - |   |     |     |   |   | 3      | 4                |

|               |                                                                                                                        | R   | IM           | 76            | - |   |     |     |   |   | 3      | 3                |

|               |                                                                                                                        | IR  | IM           | 77            | - |   |     |     |   |   | 3      | 4                |

| TMX dst, src  | dst AND src                                                                                                            | ER  | ER           | 78            | - | * | *   | 0   | - | - | 4      | 3                |

|               |                                                                                                                        | ER  | IM           | 79            | - |   |     |     |   |   | 4      | 3                |

| TRAP Vector   | $SP \leftarrow SP - 2$<br>@SP \leftarrow PC<br>$SP \leftarrow SP - 1$<br>@SP \leftarrow FLAGS<br>PC \leftarrow @Vector |     | Vecto<br>r   | F2            | - | - | -   | -   | - | - | 2      | 6                |

| WDT           |                                                                                                                        |     |              | 5F            | - | - | -   | -   | - | - | 1      | 2                |

| XOR dst, src  | $dst \gets dst \ XOR \ src$                                                                                            | r   | r            | B2            | - | * | *   | 0   | - | - | 2      | 3                |

|               |                                                                                                                        | r   | lr           | B3            | _ |   |     |     |   |   | 2      | 4                |

|               |                                                                                                                        | R   | R            | B4            | - |   |     |     |   |   | 3      | 3                |

|               |                                                                                                                        | R   | IR           | B5            | - |   |     |     |   |   | 3      | 4                |

|               |                                                                                                                        | R   | IM           | B6            | - |   |     |     |   |   | 3      | 3                |

|               |                                                                                                                        | IR  | IM           | B7            | - |   |     |     |   |   | 3      | 4                |

| XORX dst, src | $dst \gets dst \ XOR \ src$                                                                                            | ER  | ER           | B8            | - | * | *   | 0   | - | - | 4      | 3                |

|               |                                                                                                                        | ER  | IM           | B9            | - |   |     |     |   |   | 4      | 3                |

# Table 127. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

# 221

nbedded in Life

# Packaging

Zilog's Z8 Encore! XP<sup>®</sup> F0822 Series of MCUs includes the Z8F0411, Z8F0421, Z8F0811 and Z8F0821 devices, which are available in the following packages:

- 20-pin Small Shrink Outline Package (SSOP)

- 20-pin Plastic Dual-Inline Package (PDIP)

Zilog's Z8 Encore! XP<sup>®</sup> F0822 Series of MCUs also includes the Z8F0412, Z8F0422, Z8F0812 and Z8F0822 devices, which are available in the following packages:

- 28-pin Small Outline Integrated Circuit Package (SOIC)

- 28-pin Plastic Dual-Inline Package (PDIP)

Current diagrams for each of these packages are published in Zilog's <u>Packaging Product</u> <u>Specification (PS0072)</u>, which is available free for download from the Zilog website.

# Embedded in Life An IXYS Company 224

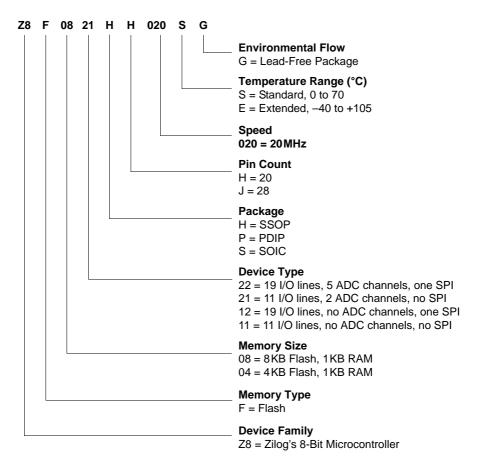

# Part Number Suffix Designations

Zilog part numbers consist of a number of components, as indicated in the following example.

**Example.** Part number Z8F0821HH020SG is an 8-bit Flash Motor Controller with 8KB of Program Memory, equipped with 11 I/O lines and 2 ADC channels in a 20-pin SSOP package, operating within a 0°C to +70°C temperature range and built using lead-free solder.