Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Due durch Chabura          | A - 12 - 12                                               |  |  |  |

|----------------------------|-----------------------------------------------------------|--|--|--|

| Product Status             | Active                                                    |  |  |  |

| Core Processor             | eZ8                                                       |  |  |  |

| Core Size                  | 8-Bit                                                     |  |  |  |

| Speed                      | 20MHz                                                     |  |  |  |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                   |  |  |  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |  |  |  |

| Number of I/O              | 19                                                        |  |  |  |

| Program Memory Size        | 8KB (8K × 8)                                              |  |  |  |

| Program Memory Type        | FLASH                                                     |  |  |  |

| EEPROM Size                | -                                                         |  |  |  |

| RAM Size                   | 1K x 8                                                    |  |  |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |  |  |

| Data Converters            | A/D 5x10b                                                 |  |  |  |

| Oscillator Type            | Internal                                                  |  |  |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |  |  |  |

| Mounting Type              | Surface Mount                                             |  |  |  |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |  |  |  |

| Supplier Device Package    | -                                                         |  |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0822sj020eg |  |  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 176. | IRQ1 Enable High Bit Register (IRQ1ENH)            |

|------------|----------------------------------------------------|

| Table 177. | IRQ1 Enable Low Bit Register (IRQ1ENL)             |

| Table 178. | Interrupt Request 2 Register (IRQ2)                |

| Table 179. | IRQ2 Enable High Bit Register (IRQ2ENH)            |

| Table 180. | IRQ2 Enable Low Bit Register (IRQ2ENL)             |

| Table 181. | Interrupt Control Register (IRQCTL) 241            |

| Table 182. | Port A–C GPIO Address Registers (PxADDR)           |

| Table 183. | Port A–C Control Registers (PxCTL)                 |

| Table 184. | Port A–C Input Data Registers (PxIN)               |

| Table 185. | Port A–C Output Data Register (PxOUT) 242          |

| Table 186. | Port A–C GPIO Address Registers (PxADDR)           |

| Table 187. | Port A–C Control Registers (PxCTL)                 |

| Table 188. | Port A–C Input Data Registers (PxIN)               |

| Table 189. | Port A–C Output Data Register (PxOUT) 243          |

| Table 190. | Port A–C GPIO Address Registers (PxADDR)           |

|            | Port A–C Control Registers (PxCTL)                 |

| Table 192. | Port A–C Input Data Registers (PxIN)               |

| Table 193. | Port A–C Output Data Register (PxOUT) 244          |

| Table 194. | Watchdog Timer Control Register (WDTCTL)           |

| Table 195. | Watchdog Timer Reload Upper Byte Register (WDTU)   |

| Table 196. | Watchdog Timer Reload High Byte Register (WDTH)    |

| Table 197. | Watchdog Timer Reload Low Byte Register (WDTL) 245 |

| Table 198. | Flash Control Register (FCTL)    246               |

| Table 199. | Flash Status Register (FSTAT)    246               |

| Table 200. | Page Select Register (FPS)                         |

| Table 201. | Flash Sector Protect Register (FPROT) 247          |

| Table 202. | Flash Frequency High Byte Register (FFREQH)        |

| Table 203. | Flash Frequency Low Byte Register (FFREQL)         |

|            |                                                    |

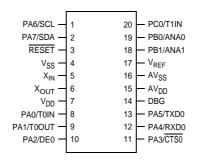

Figure 2. The Z8F0821 and Z8F0421 MCUs in 20-Pin SSOP and PDIP Packages

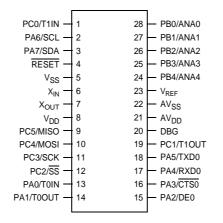

Figure 3. The Z8F0822 and Z8F0422 MCUs in 28-Pin SOIC and PDIP Packages

ILO G

13

# **Pin Characteristics**

Table 4 provides detailed information about the characteristics for each pin available on Z8 Encore!  $XP^{\textcircled{B}}$  F0822 Series products. The data in Table 4 is sorted alphabetically by pin symbol mnemonic.

| Symbol<br>Mnemonic | Direction | Reset<br>Direction | Active<br>Low or<br>Active<br>High | Tri-State<br>Output | Internal<br>Pull-Up or<br>Pull-Down | Schmitt-Trigger<br>Input | Open Drain<br>Output   |

|--------------------|-----------|--------------------|------------------------------------|---------------------|-------------------------------------|--------------------------|------------------------|

| AV <sub>DD</sub>   | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| AV <sub>SS</sub>   | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| DBG                | I/O       | I                  | N/A                                | Yes                 | No                                  | Yes                      | Yes                    |

| PA[7:0]            | I/O       | I                  | N/A                                | Yes                 | Programma-<br>ble pull-up           | Yes                      | Yes, pro-<br>grammable |

| PB[4:0]            | I/O       | I                  | N/A                                | Yes                 | Programma-<br>ble pull-up           | Yes                      | Yes, pro-<br>grammable |

| PC[5:0]            | I/O       | I                  | N/A                                | Yes                 | Programma-<br>ble pull-up           | Yes                      | Yes, pro-<br>grammable |

| RESET              | I         | I                  | Low                                | N/A                 | Pull-up                             | Yes                      | N/A                    |

| V <sub>DD</sub>    | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| V <sub>REF</sub>   | Analog    | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| V <sub>SS</sub>    | N/A       | N/A                | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| X <sub>IN</sub>    | I         | I                  | N/A                                | N/A                 | No                                  | No                       | N/A                    |

| X <sub>OUT</sub>   | 0         | 0                  | N/A                                | No                  | No                                  | No                       | No                     |

#### **Table 4. Pin Characteristics**

Embedded in Life An TXYS Company 24

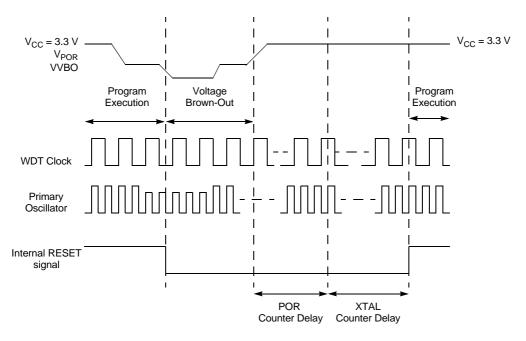

the POR status bit in the Watchdog Timer Control Register (WDTCTL) is set to 1. Figure 7 displays the VBO operation. See the <u>Electrical Characteristics</u> chapter on page 176 for the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ).

The VBO circuit can be either enabled or disabled during STOP Mode. Operation during STOP Mode is set by the VBO\_AO option bit. For information about configuring VBO\_AO, see the <u>Option Bits</u> chapter on page 155.

Figure 7. Voltage Brown-Out Reset Operation

# Watchdog Timer Reset

If the device is in NORMAL or HALT Mode, WDT initiates a System Reset at time-out, if the WDT\_RES option bit is set to 1. This setting is the default (unprogrammed) setting of the WDT\_RES option bit. The WDT status bit in the WDT Control Register is set to signify that the reset was initiated by the WDT.

# **External Pin Reset**

The RESET pin contains a Schmitt-triggered input, an internal pull-up, an analog filter, and a digital filter to reject noise. After the RESET pin is asserted for at least 4 system

| Z8 Encore! XP <sup>®</sup> F0822<br>Product Speci |   | - |   |   |

|---------------------------------------------------|---|---|---|---|

|                                                   | i | l | 0 | ď |

bedded in Lif

nu IXYS Comp

42

# Architecture

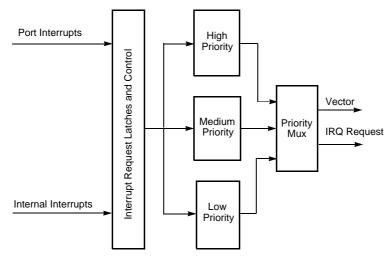

Figure 9 displays a block diagram of the interrupt controller.

Figure 9. Interrupt Controller Block Diagram

# Operation

This section describes the operational aspects of the following functions.

Master Interrupt Enable: see page 42

Interrupt Vectors and Priority: see page 43

Interrupt Assertion: see page 43

Software Interrupt Assertion: see page 44

# **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control Register globally enables and disables interrupts.

Interrupts are globally enabled by any of the following actions:

- Execution of an Enable Interrupt (EI) instruction

- Execution of an Return from Interrupt (IRET) instruction

# inbedded in Life IXYS Company 64

# **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte Register is read, the contents of the Timer Low Byte Register are placed in a holding register. A subsequent read from the Timer Low Byte Register returns the value in the holding register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte Register returns the actual value in the counter.

# **Timer Output Signal Operation**

Timer Output is a GPIO port pin alternate function. Generally, the Timer Output is toggled every time the counter is reloaded.

# **Timer Control Register Definitions**

This section defines the features of the following Timer Control registers.

Timer 0-1 High and Low Byte Registers: see page 64

Timer Reload High and Low Byte Registers: see page 65

Timer 0-1 PWM High and Low Byte Registers: see page 66

Timer 0-3 Control 0 Registers: see page 67

Timer 0-1 Control 1 Registers: see page 68

# Timer 0–1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers, shown in Tables 39 and 40, contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TMRL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TMRL reads the register directly.

Zilog does not recommend writing to the Timer High and Low Byte registers while the timer is enabled. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

ilog<sup>®</sup> Embedded in Life An⊡IXYS Company **74**

## Table 48. Watchdog Timer Control Register (WDTCTL)

| Bit         | 7                                                                                                                                                                                                                                 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5            | 4           | 3           | 2 | 1 | 0 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|-------------|---|---|---|

| Field       | POR                                                                                                                                                                                                                               | STOP                                                                                                                                                                                                                                                                                                                                                                                                                                 | WDT          | EXT         | Reserved    |   |   | · |

| RESET       |                                                                                                                                                                                                                                   | See Ta                                                                                                                                                                                                                                                                                                                                                                                                                               | ble 49.      |             |             | ( | ) |   |

| R/W         |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                      |              | I           | ۲           |   |   |   |

| Address     |                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                      |              | FF          | ЮH          |   |   |   |

| Bit         | Descriptio                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |              |             |             |   |   |   |

| [7]<br>POR  | If this bit is                                                                                                                                                                                                                    | <b>Power-On Reset Indicator</b><br>If this bit is set to 1, a POR event occurred. This bit is reset to 0, if a WDT time-out or Stop<br>Mode Recovery occurs. This bit is also reset to 0, when the register is read.                                                                                                                                                                                                                 |              |             |             |   |   |   |

| [6]<br>STOP | If this bit is<br>1, the Stop<br>is 0, the Sto                                                                                                                                                                                    | <b>Stop Mode Recovery Indicator</b><br>If this bit is set to 1, a Stop Mode Recovery occurred. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurred due to a WDT time-out. If the stop bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a POR or a WDT time-out that occurred while not in STOP Mode. Reading this register also resets this bit. |              |             |             |   |   |   |

| [5]<br>WDT  | If this bit is                                                                                                                                                                                                                    | Watchdog Timer Time-Out Indicator<br>If this bit is set to 1, a WDT time-out occurred. A POR resets this pin. A Stop Mode Recovery<br>due a change in an input pin also resets this bit. Reading this register resets this bit.                                                                                                                                                                                                      |              |             |             |   |   |   |

| [4]<br>EXT  | External Reset Indicator<br>If this bit is set to 1, a Reset initiated by the external RESET pin occurred. A POR or a Stop<br>Mode Recovery from a change in an input pin resets this bit. Reading this register resets this bit. |                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |             |             |   |   |   |

| [3:0]       | Reserved<br>These bits                                                                                                                                                                                                            | are reserved                                                                                                                                                                                                                                                                                                                                                                                                                         | d and must b | be programn | ned to 0000 |   |   |   |

# Table 49. Watchdog Timer Events

| Reset or Stop Mode Recovery Event                   | POR | STOP | WDT | EXT |

|-----------------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                      | 1   | 0    | 0   | 0   |

| Reset through RESET pin assertion                   | 0   | 0    | 0   | 1   |

| Reset through WDT time-out                          | 0   | 0    | 1   | 0   |

| Reset through the OCD (OCTCTL[1] set to 1)          | 1   | 0    | 0   | 0   |

| Reset from STOP Mode through the DBG Pin driven Low | 1   | 0    | 0   | 0   |

| Stop Mode Recovery through GPIO pin transition      | 0   | 1    | 0   | 0   |

| Stop Mode Recovery through WDT time-out             | 0   | 1    | 1   | 0   |

- ilog<sup>\*</sup> Embedded in Life n⊒IXYS Company 81

- Set or clear the CTSE bit to enable or disable control from the remote receiver through the CTS pin.

- 7. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data transmission. Because the UART Transmit Data Register is empty, an interrupt is generated immediately. When the UART transmit interrupt is detected, the associated ISR performs the following:

- 1. Write the UART Control 1 Register to select the outgoing address bit:

- Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte; clear it if sending a data byte.

- 2. Write the data byte to the UART Transmit Data Register. The transmitter automatically transfers data to the Transmit Shift Register and then transmits the data.

- 3. Clear the UART transmit interrupt bit in the applicable Interrupt Request Register.

- 4. Execute the IRET instruction to return from the ISR and waits for the Transmit Data Register to again become empty.

# **Receiving Data using the Polled Method**

Observe the following procedure to configure the UART for polled data reception:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 Register to enable Multiprocessor mode functions, if appropriate.

- 4. Write to the UART Control 0 Register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if required, and if MULTIPROCESSOR Mode is not enabled, and select either even or odd parity.

- 5. Check the RDA bit in the UART Status 0 Register to determine if the Receive Data Register contains a valid data byte (indicated by 1). If RDA is set to 1 to indicate available data, continue to <u>Step 6</u>. If the Receive Data Register is empty (indicated by a 0), continue to monitor the RDA bit awaiting reception of the valid data.

ILOG Embedded in Life An TIXYS Company 105

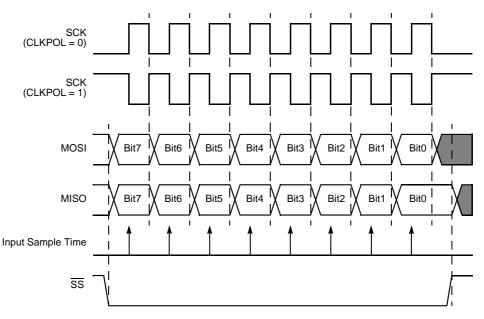

| PHASE | CLKPOL | SCK Transmit<br>Edge | SCK Receive<br>Edge | SCK Idle<br>State |

|-------|--------|----------------------|---------------------|-------------------|

| 0     | 0      | Falling              | Rising              | Low               |

| 0     | 1      | Rising               | Falling             | High              |

| 1     | 0      | Rising               | Falling             | Low               |

| 1     | 1      | Falling              | Rising              | High              |

#### Table 63. SPI Clock Phase (PHASE) and Clock Polarity (CLKPOL) Operation

#### Transfer Format PHASE is 0

Figure 23 displays the timing diagram for an SPI transfer in which PHASE is cleared to 0. The two SCK waveforms show polarity with CLKPOL reset to 0 and with CLKPOL set to one. The diagram can be interpreted as either a Master or Slave timing diagram, because the SCK Master-In/Slave-Out (MISO) and Master-Out/Slave-In (MOSI) pins are directly connected between the Master and the Slave.

Figure 23. SPI Timing When PHASE is 0

nbedded in Life

152

# Page Select Register

The Page Select (FPS) Register, shown in Table 86, selects the Flash memory page to be erased or programmed. Each Flash page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory locations with the 7 most significant bits of the address provided by the PAGE field are erased to FFH.

The Page Select Register shares its Register File address with the Flash Sector Protect Register. The Page Select Register cannot be accessed when the Flash Sector Protect Register is enabled.

| Bit     | 7       | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---------|------|---|---|---|---|---|---|

| Field   | INFO_EN | PAGE |   |   |   |   |   |   |

| RESET   |         | 0    |   |   |   |   |   |   |

| R/W     |         | R/W  |   |   |   |   |   |   |

| Address |         | FF9H |   |   |   |   |   |   |

| Table 86. P | Page Select | Register ( | (FPS) |

|-------------|-------------|------------|-------|

|-------------|-------------|------------|-------|

| Bit     | Description                                                                                                                                                |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7]     | Information Area Enable                                                                                                                                    |

| INFO_EN | 0 = Information Area is not selected.                                                                                                                      |

|         | <ol> <li>Information Area is selected. The Information area is mapped into the Flash memory<br/>address space at addresses FE00H through FFFFH.</li> </ol> |

| [6:0]   | Page Select                                                                                                                                                |

| PAGE    | This 7-bit field selects the Flash memory page for Programming and Page Erase operations.<br>Flash memory address[15:9] = PAGE[6:0].                       |

# **Flash Sector Protect Register**

The Flash Sector Protect Register, shown in Table 87, protects Flash memory sectors from being programmed or erased from user code. The Flash Sector Protect Register shares its Register File address with the Page Select Register. The Flash Sector Protect Register can be accessed only after writing the Flash Control Register with 5EH.

User code can only write bits in this register to 1 (bits cannot be cleared to 0 by user code). To determine the appropriate Flash memory sector address range and sector number for your F0822 Series product, please refer to <u>Table 82</u> on page 143.

ILO O Imbedded in Life

If breakpoints are enabled, the OCD can be configured to automatically enter DEBUG Mode, or to loop on the break instruction. If the OCD is configured to loop on the BRK instruction, then the CPU is still enabled to service DMA and interrupt requests.

The loop on a BRK instruction can be used to service interrupts in the background. For interrupts to be serviced in the background, there cannot be any breakpoints in the ISR. Otherwise, the CPU stops on the breakpoint in the interrupt routine. For interrupts to be serviced in the background, interrupts must also be enabled. Debugging software should not automatically enable interrupts when using this feature, because interrupts are typically disabled during critical sections of code where interrupts should not occur (such as adjusting the stack pointer or modifying shared data).

Software can poll the IDLE bit of the OCDSTAT Register to determine if the OCD is looping on a BRK instruction. When software wants to stop the CPU on the BRK instruction it is looping on, software should not set the DBGMODE bit of the OCDCTL Register. The CPU can have vectored to and be in the middle of an ISR when this bit gets set. Instead, software must clear the BRKLP bit. This allows the CPU to finish the ISR it is in and return the BRK instruction. When the CPU returns to the BRK instruction it was previously looping on, it automatically sets the DBGMODE bit and enter DEBUG Mode.

Software should also note that the majority of the OCD commands are still disabled when the eZ8 CPU is looping on a BRK instruction. The eZ8 CPU must be stopped and the part must be in DEBUG Mode before these commands can be issued.

#### **Breakpoints in Flash Memory**

The BRK instruction is Op Code 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a Breakpoint, write 00H to the appropriate address, overwriting the current instruction. To remove a Breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

# **OCDCNTR Register**

The OCD contains a multipurpose 16-bit counter register. It can be used for the following:

- Count system clock cycles between breakpoints

- Generate a BRK when it counts down to zero

- Generate a BRK when its value matches the Program Counter

When configured as a counter, the OCDCNTR Register starts counting when the OCD leaves DEBUG Mode and stops counting when it enters DEBUG Mode again or when it reaches the maximum count of FFFFH. The OCDCNTR Register automatically resets itself to 0000H when the OCD exits DEBUG Mode if it is configured to count clock cycles between breakpoints.

Embedded in Life

|   | ~ -        |

|---|------------|

| L | <b>h</b> n |

|   |            |

| Debug Command           | Command<br>Byte | Enabled When<br>Not in DEBUG<br>Mode? | Disabled by Read Protect Option Bit                                                  |

|-------------------------|-----------------|---------------------------------------|--------------------------------------------------------------------------------------|

| Read Register           | 09H             | _                                     | Only reads of the peripheral control reg-<br>isters at address F00H–FFH are allowed. |

| Write Program Memory    | 0AH             | -                                     | Disabled                                                                             |

| Read Program Memory     | 0BH             | -                                     | Disabled                                                                             |

| Write Data Memory       | 0CH             | _                                     | Disabled                                                                             |

| Read Data Memory        | 0DH             | -                                     | Disabled                                                                             |

| Read Program Memory CRC | 0EH             | -                                     | -                                                                                    |

| Reserved                | 0FH             | _                                     | -                                                                                    |

| Step Instruction        | 10H             | -                                     | Disabled                                                                             |

| Stuff Instruction       | 11H             | -                                     | Disabled                                                                             |

| Execute Instruction     | 12H             | _                                     | Disabled                                                                             |

| Reserved                | 13H–FFH         | _                                     | -                                                                                    |

#### Table 93. On-Chip Debugger Commands (Continued)

In the following bulleted list of OCD Commands, data and commands sent from the host to the OCD are identified by DBG  $\leftarrow$  Command/Data. Data sent from the OCD back to the host is identified by DBG  $\rightarrow$  Data.

**Read OCD Revision (00H).** The Read OCD Revision command determines the version of the OCD. If OCD commands are added, removed, or changed, this revision number changes.

```

DEG \leftarrow 00H

DEG \rightarrow OCDREV[15:8] (Major revision number)

DEG \rightarrow OCDREV[7:0] (Minor revision number)

```

Write OCD Counter Register (01H). The Write OCD Counter Register command writes the data that follows to the OCDCNTR Register. If the device is not in DEBUG Mode, the data is discarded.

```

DBG \leftarrow 01H

DBG \leftarrow OCDCNTR[15:8]

DBG \leftarrow OCDCNTR[7:0]

```

**Read OCD Status Register (02H).** The Read OCD Status Register command reads the OCDSTAT Register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

**Read OCD Counter Register (03H).** The OCD Counter Register can be used to count system clock cycles in between breakpoints, generate a BRK when it counts down to zero,

DBG  $\leftarrow$  12H DBG  $\leftarrow$  1-5 byte opcode

# **On-Chip Debugger Control Register Definitions**

This section describes the features of the On-Chip Debugger Control and Status registers.

# **OCD Control Register**

The OCD Control Register, shown in Table 94, controls the state of the OCD. This register enters or exits DEBUG Mode and enables the BRK instruction. It can also reset the Z8 Encore! XP<sup>®</sup> F0822 Series device.

A *reset and stop* function can be achieved by writing 81H to this register. A *reset and go* function can be achieved by writing 41H to this register. If the device is in DEBUG Mode, a *run* function can be implemented by writing 40H to this register.

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                                                                                                                                                                                                                                                | 5      | 4       | 3     | 2      | 1        | 0   |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|-------|--------|----------|-----|--|--|

| Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | DBGMODE                                                                                                                                                                                                                                                                                                                                                                                                             | BRKEN                                                                                                                                                                                                                                                                            | DBGACK | BRKLOOP | BRKPC | BRKZRO | Reserved | RST |  |  |

| RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                  |        | 0       |       |        |          |     |  |  |

| R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W                                                                                                                                                                                                                                                                              |        |         | R     |        |          | R/W |  |  |

| Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Descriptio                                                                                                                                                                                                                                                                                                                                                                                                          | on                                                                                                                                                                                                                                                                               |        |         |       |        |          |     |  |  |

| <ul> <li>[7] Debug Mode</li> <li>DBGMODE Setting this bit to 1 causes the device to enter DEBUG Mode. When in DEBUG Mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to start running again. This bit is automatically set when a BRK instruction is decoded and breakpoints are enabled. If the Read Protect option bit is enabled, this bit can only be cleared by resetting the device, it cannot be written to 0.</li> <li>0 = The Z8 Encore! XP<sup>®</sup> F0822 Series device is operating in NORMAL Mode.</li> <li>1 = The Z8 Encore! XP<sup>®</sup> F0822 Series device is in DEBUG Mode.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                  |        |         |       |        |          |     |  |  |

| BRKEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>Breakpoint Enable</li> <li>This bit controls the behavior of the BRK instruction (Op Code 00H). By default, breakpoints are disabled and the BRK instruction behaves like an NOP instruction. If this bit is set to 1 and a BRK instruction is decoded, the OCD takes action dependent upon the BRKLOOP bit.</li> <li>0 = BRK instruction is disabled.</li> <li>1 = BRK instruction is enabled.</li> </ul> |                                                                                                                                                                                                                                                                                  |        |         |       |        |          |     |  |  |

| [5]<br>DBGACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | This bit en<br>an Debug<br>0 = Debug                                                                                                                                                                                                                                                                                                                                                                                | <b>Debug Acknowledge</b><br>This bit enables the debug acknowledge feature. If this bit is set to 1, then the OCD sends<br>an Debug Acknowledge character (FFH) to the host when a Breakpoint occurs.<br>0 = Debug Acknowledge is disabled.<br>1 = Debug Acknowledge is enabled. |        |         |       |        |          |     |  |  |

Table 94. OCD Control Register (OCDCTL)

#### ilog Embedded in Life An IXYS Company 176

# **Electrical Characteristics**

The data in this chapter represents all known data prior to qualification and characterization of the Z8 Encore!  $XP^{\textcircled{B}}$  F0822 Series of products, and is therefore subject to change. Additional electrical characteristics may be found in the individual chapters of this document.

# **Absolute Maximum Ratings**

These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect device reliability. For improved reliability, unused inputs must be tied to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

**Caution:** Stresses greater than those listed in Table 97 can cause permanent damage to the device.

|                                                          |         | -       |       |       |

|----------------------------------------------------------|---------|---------|-------|-------|

| Parameter                                                | Minimum | Maximum | Units | Notes |

| Ambient temperature under bias                           | -40     | +105    | °C    | 1     |

| Storage temperature                                      | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>       | -0.3    | +5.5    | V     | 2     |

| Voltage on AV <sub>SS</sub> pin with respect to $V_{SS}$ | -0.3    | +0.3    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$         | -0.3    | +3.6    | V     |       |

| Voltage on $AV_{DD}$ pin with respect to $V_{DD}$        | -0.3    | +0.3    | V     |       |

| Maximum current on input and/or inactive output pin      | -5      | +5      | μA    |       |

| Maximum output current from active output pin            | -25     | +25     | mA    |       |

| 20-pin SSOP Package Maximum Ratings at -40°C to          | o 70°C  |         |       |       |

| Total power dissipation                                  |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$         |         | 120     | mA    |       |

|                                                          |         |         |       |       |

#### Table 97. Absolute Maximum Ratings

Note: This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, V<sub>REF</sub>, pins that support analog input (Port B), and where otherwise noted.

197

# **UART Timing**

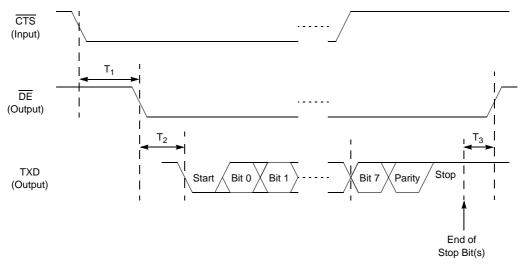

Figure 54 and Table 112 provide timing information for UART pins for the case where the Clear To Send input pin ( $\overline{\text{CTS}}$ ) is used for flow control. In this example, it is assumed that the Driver Enable polarity has been configured to be Active Low and is represented here by  $\overline{\text{DE}}$ . The  $\overline{\text{CTS}}$  to  $\overline{\text{DE}}$  assertion delay (T1) assumes the UART Transmit Data Register has been loaded with data prior to  $\overline{\text{CTS}}$  assertion.

## Figure 54. UART Timing with CTS

## Table 112. UART Timing with CTS

|                |                                                | Delay (ns)                 |                                              |  |  |

|----------------|------------------------------------------------|----------------------------|----------------------------------------------|--|--|

| Parameter      | Abbreviation                                   | Minimum                    | Maximum                                      |  |  |

| T <sub>1</sub> | CTS Fall to DE Assertion Delay                 | 2 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period + 1<br>Bit period |  |  |

| T <sub>2</sub> | DE Assertion to TXD Falling Edge (Start) Delay | 1 Bit period               | 1 Bit period +<br>1 * X <sub>IN</sub> period |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE Deassertion Delay     | 1 * X <sub>IN</sub> period | 2 * X <sub>IN</sub> period                   |  |  |

Figure 55 and Table 113 provide timing information for UART pins for the case where the Clear To Send input signal ( $\overline{\text{CTS}}$ ) is not used for flow control. In this example, it is assumed that the Driver Enable polarity has been configured to be Active Low and is rep-

ilog° Embedded in Life An∎IXYS Company

212

|               |                          |      |             |               |       |   |   |   |   | -     |        |        |

|---------------|--------------------------|------|-------------|---------------|-------|---|---|---|---|-------|--------|--------|

| Assembly      | Symbolic                 |      | ress<br>ode | Op<br>Code(s) | Flags |   |   |   |   | Fetch | Instr. |        |

| Mnemonic      | Operation                | dst  | src         | (Hex)         | С     | Ζ | S | ۷ | D | н     | Cycles | Cycles |

| LD dst, rc    | $dst \gets src$          | r    | IM          | 0C-FC         | -     | - | - | - | - | -     | 2      | 2      |

|               |                          | r    | X(r)        | C7            | -     |   |   |   |   |       | 3      | 3      |

|               |                          | X(r) | r           | D7            | -     |   |   |   |   |       | 3      | 4      |

|               |                          | r    | lr          | E3            | -     |   |   |   |   |       | 2      | 3      |

|               |                          | R    | R           | E4            | -     |   |   |   |   |       | 3      | 2      |

|               |                          | R    | IR          | E5            | -     |   |   |   |   |       | 3      | 4      |

|               |                          | R    | IM          | E6            | -     |   |   |   |   |       | 3      | 2      |

|               |                          | IR   | IM          | E7            | -     |   |   |   |   |       | 3      | 3      |

|               |                          | lr   | r           | F3            | -     |   |   |   |   |       | 2      | 3      |

|               |                          | IR   | R           | F5            | -     |   |   |   |   |       | 3      | 3      |

| LDC dst, src  | $dst \gets src$          | r    | Irr         | C2            | -     | - | - | - | - | -     | 2      | 5      |

|               |                          | lr   | Irr         | C5            | -     |   |   |   |   |       | 2      | 9      |

|               |                          | Irr  | r           | D2            | -     |   |   |   |   |       | 2      | 5      |

| LDCI dst, src | $dst \gets src$          | lr   | Irr         | C3            | -     | - | - | - | - | -     | 2      | 9      |

|               | r ← r + 1<br>rr ← rr + 1 | Irr  | lr          | D3            | -     |   |   |   |   |       | 2      | 9      |

| LDE dst, src  | $dst \gets src$          | r    | Irr         | 82            | -     | - | - | - | - | -     | 2      | 5      |

|               |                          | Irr  | r           | 92            | -     |   |   |   |   |       | 2      | 5      |

| LDEI dst, src | $dst \gets src$          | lr   | Irr         | 83            | -     | - | - | - | - | -     | 2      | 9      |

|               | r ← r + 1<br>rr ← rr + 1 | Irr  | lr          | 93            | -     |   |   |   |   |       | 2      | 9      |

| LDWX dst, src | $dst \gets src$          | ER   | ER          | 1F E8         | -     | - | - | - | - | -     | 5      | 4      |

|               |                          |      |             |               |       |   |   |   |   |       |        |        |

# Table 127. eZ8 CPU Instruction Summary (Continued)

Note: Flags Notation:

\* = Value is a function of the result of the operation.

- = Unaffected.

X = Undefined.

0 = Reset to 0.

1 = Set to 1.

| Z8 Encore! XP® | F0822  | Series  |

|----------------|--------|---------|

| Product        | Specif | ication |

226

# Hex Address: F01

# Table 131. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7 6 5 4 3 2 1 |     |  |       |      |  |  |  |  |  |

|---------|---------------|-----|--|-------|------|--|--|--|--|--|

| Field   | TL            |     |  |       |      |  |  |  |  |  |

| RESET   | 0 1           |     |  |       |      |  |  |  |  |  |

| R/W     |               | R/W |  |       |      |  |  |  |  |  |

| Address |               |     |  | F01H, | F09H |  |  |  |  |  |

# Hex Address: F02

## Table 132. Timer 0–1 Reload High Byte Register (TxRH)

| Bit     | 7 6 5 4 3 2 1 |     |  |       |      |  |  |  |  |  |

|---------|---------------|-----|--|-------|------|--|--|--|--|--|

| Field   |               | TRH |  |       |      |  |  |  |  |  |

| RESET   |               | 1   |  |       |      |  |  |  |  |  |

| R/W     |               | R/W |  |       |      |  |  |  |  |  |

| Address |               |     |  | F02H, | F0AH |  |  |  |  |  |

# Hex Address: F03

# Table 133. Timer 0–1 Reload Low Byte Register (TxRL)

| Bit     | 7 | 6   | 5 | 4     | 3    | 2 | 1 | 0 |  |  |

|---------|---|-----|---|-------|------|---|---|---|--|--|

| Field   |   | TRL |   |       |      |   |   |   |  |  |

| RESET   |   | 1   |   |       |      |   |   |   |  |  |

| R/W     |   | R/W |   |       |      |   |   |   |  |  |

| Address |   |     |   | F03H, | F0BH |   |   |   |  |  |

## Hex Address: F07

#### Table 137. Timer 0–1 Control Registers (TxCTL)

| Bit     | 7   | 6    | 5          | 4     | 3    | 2 1 0 |  |  |  |  |

|---------|-----|------|------------|-------|------|-------|--|--|--|--|

| Field   | TEN | TPOL | PRES TMODE |       |      |       |  |  |  |  |

| RESET   |     | 0    |            |       |      |       |  |  |  |  |

| R/W     |     | R/W  |            |       |      |       |  |  |  |  |

| Address |     |      |            | F07H, | F0FH |       |  |  |  |  |

#### Hex Address: F08

#### Table 138. Timer 0–1 High Byte Register (TxH)

| Bit     | 7 | 6   | 5 | 4     | 3    | 2 | 1 | 0 |  |  |

|---------|---|-----|---|-------|------|---|---|---|--|--|

| Field   |   | TH  |   |       |      |   |   |   |  |  |

| RESET   |   | 0   |   |       |      |   |   |   |  |  |

| R/W     |   | R/W |   |       |      |   |   |   |  |  |

| Address |   |     |   | F00H, | F08H |   |   |   |  |  |

# Hex Address: F09

#### Table 139. Timer 0–1 Low Byte Register (TxL)

| Bit     | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|---------|------------|-----|---|---|---|---|---|---|--|--|--|

| Field   |            | TL  |   |   |   |   |   |   |  |  |  |

| RESET   |            | 0 1 |   |   |   |   |   |   |  |  |  |

| R/W     |            | R/W |   |   |   |   |   |   |  |  |  |

| Address | F01H, F09H |     |   |   |   |   |   |   |  |  |  |

#### Hex Address: F0A

#### Table 140. Timer 0–1 Reload High Byte Register (TxRH)

| Bit     | 7 | 6   | 5 | 4     | 3    | 2          | 1 | 0 |  |  |  |  |  |  |

|---------|---|-----|---|-------|------|------------|---|---|--|--|--|--|--|--|

| Field   |   | TRH |   |       |      |            |   |   |  |  |  |  |  |  |

| RESET   |   | 1   |   |       |      |            |   |   |  |  |  |  |  |  |

| R/W     |   | R/W |   |       |      |            |   |   |  |  |  |  |  |  |

| Address |   |     |   | F02H, | F0AH | F02H, F0AH |   |   |  |  |  |  |  |  |

| Z8 Encore! XP | <sup>®</sup> F0822 Series |

|---------------|---------------------------|

| Produc        | t Specification           |

236

## Hex Address: F63

## Table 165. SPI Mode Register (SPIMODE)

| Bit     | 7    | 6     | 5    | 4                 | 3 | 2 | 1 | 0   |  |

|---------|------|-------|------|-------------------|---|---|---|-----|--|

| Field   | Rese | erved | DIAG | DIAG NUMBITS[2:0] |   |   |   | SSV |  |

| RESET   |      | 0     |      |                   |   |   |   |     |  |

| R/W     | F    | R R/W |      |                   |   |   |   |     |  |

| Address | F63H |       |      |                   |   |   |   |     |  |

## Hex Address: F64

#### Table 166. SPI Diagnostic State Register (SPIDST)

| Bit     | 7     | 6     | 5        | 4 | 3 | 2 | 1 | 0 |  |  |

|---------|-------|-------|----------|---|---|---|---|---|--|--|

| Field   | SCKEN | TCKEN | SPISTATE |   |   |   |   |   |  |  |

| RESET   |       | 0     |          |   |   |   |   |   |  |  |

| R/W     |       | R     |          |   |   |   |   |   |  |  |

| Address |       | F64H  |          |   |   |   |   |   |  |  |

## Hex Address: F65

This address is reserved.

#### Hex Address: F66

## Table 167. SPI Baud Rate High Byte Register (SPIBRH)

| Bit     | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------|---|---|---|---|---|---|---|--|

| Field   | BRH  |   |   |   |   |   |   |   |  |

| RESET   | 1    |   |   |   |   |   |   |   |  |

| R/W     | R/W  |   |   |   |   |   |   |   |  |

| Address | F66H |   |   |   |   |   |   |   |  |

# Hex Address: FD6

## Table 188. Port A–C Input Data Registers (PxIN)

| Bit     | 7    | 6                | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|---------|------|------------------|------|------|------|------|------|------|--|--|

| Field   | PIN7 | PIN6             | PIN5 | PIN4 | PIN3 | PIN2 | PIN1 | PIN0 |  |  |

| RESET   |      | X                |      |      |      |      |      |      |  |  |

| R/W     |      | R                |      |      |      |      |      |      |  |  |

| Address |      | FD2H, FD6H, FDAH |      |      |      |      |      |      |  |  |

# Hex Address: FD7

## Table 189. Port A–C Output Data Register (PxOUT)

| Bit     | 7     | 6                | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|---------|-------|------------------|-------|-------|-------|-------|-------|-------|--|--|

| Field   | POUT7 | POUT6            | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |

| RESET   | 0     |                  |       |       |       |       |       |       |  |  |

| R/W     |       | R/W              |       |       |       |       |       |       |  |  |

| Address |       | FD3H, FD7H, FDBH |       |       |       |       |       |       |  |  |

# Hex Address: FD8

# Table 190. Port A–C GPIO Address Registers (PxADDR)

| Bit     | 7                | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------------------|---|---|---|---|---|---|---|--|

| Field   | PADDR[7:0]       |   |   |   |   |   |   |   |  |

| RESET   | 00H              |   |   |   |   |   |   |   |  |

| R/W     | R/W              |   |   |   |   |   |   |   |  |

| Address | FD0H, FD4H, FD8H |   |   |   |   |   |   |   |  |

# Hex Address: FD9

# Table 191. Port A–C Control Registers (PxCTL)

| Bit     | 7                | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---------|------------------|---|---|---|---|---|---|---|--|

| Field   | PCTL             |   |   |   |   |   |   |   |  |

| RESET   | 00H              |   |   |   |   |   |   |   |  |

| R/W     | R/W              |   |   |   |   |   |   |   |  |

| Address | FD1H, FD5H, FD9H |   |   |   |   |   |   |   |  |