Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT        |

| Number of I/O              | 43                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 32K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.68V ~ 3.6V                                                             |

| Data Converters            | A/D 7x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-TQFP                                                                  |

| Supplier Device Package    | 64-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4lc2ba-au |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

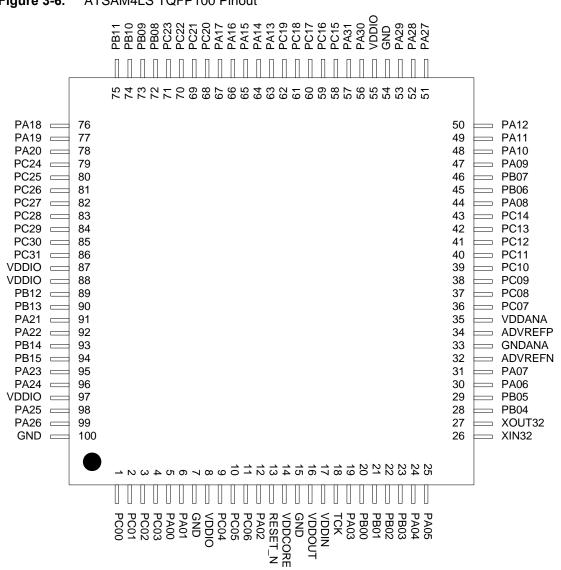

#### 3.1.2 ATSAM4LSx Pinout

Atmel

Figure 3-6. ATSAM4LS TQFP100 Pinout

14

## 3.2 Peripheral Multiplexing on I/O lines

## 3.2.1 Multiplexed Signals

Each GPIO line can be assigned to one of the peripheral functions. The following tables (Section 3-1 "100-pin GPIO Controller Function Multiplexing" on page 19 to Section 3-4 "48-pin GPIO Controller Function Multiplexing" on page 28) describes the peripheral signals multiplexed to the GPIO lines.

Peripheral functions that are not relevant in some parts of the family are grey-shaded.

For description of differents Supply voltage source, refer to the Section 6. "Power and Startup Considerations" on page 46.

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 1 of 4)

| lable | •          |     |            | 0 0011 | 101101 | i unotion | manupion      | ng (Oneer     | 1 01 1)          |                 |                   |                |                 |

|-------|------------|-----|------------|--------|--------|-----------|---------------|---------------|------------------|-----------------|-------------------|----------------|-----------------|

|       | ATSAM4LC   |     | ATSAM4LS   | Pin    | GPIO   | Supply    |               |               | G                | PIO Functio     | ns                |                |                 |

| QFN   | VFBGA      | QFN | VFBGA      |        |        |           | Α             | В             | С                | D               | E                 | F              | G               |

| 5     | B9         | 5   | B9         | PA00   | 0      | VDDIO     |               |               |                  |                 |                   |                |                 |

| 6     | B8         | 6   | B8         | PA01   | 1      | VDDIO     |               |               |                  |                 |                   |                |                 |

| 12    | A7         | 12  | A7         | PA02   | 2      | VDDIN     | SCIF<br>GCLK0 | SPI<br>NPCS0  |                  |                 |                   |                | CATB<br>DIS     |

| 19    | В3         | 19  | В3         | PA03   | 3      | VDDIN     |               | SPI<br>MISO   |                  |                 |                   |                |                 |

| 24    | A2         | 24  | A2         | PA04   | 4      | VDDANA    | ADCIFE<br>AD0 | USART0<br>CLK | EIC<br>EXTINT2   | GLOC<br>IN1     |                   |                | CATB<br>SENSE0  |

| 25    | A1         | 25  | A1         | PA05   | 5      | VDDANA    | ADCIFE<br>AD1 | USART0<br>RXD | EIC<br>EXTINT3   | GLOC<br>IN2     | ADCIFE<br>TRIGGER |                | CATB<br>SENSE1  |

| 30    | C3         | 30  | C3         | PA06   | 6      | VDDANA    | DACC<br>VOUT  | USART0<br>RTS | EIC<br>EXTINT1   | GLOC<br>IN0     | ACIFC<br>ACAN0    |                | CATB<br>SENSE2  |

| 31    | D3         | 31  | D3         | PA07   | 7      | VDDANA    | ADCIFE<br>AD2 | USART0<br>TXD | EIC<br>EXTINT4   | GLOC<br>IN3     | ACIFC<br>ACAP0    |                | CATB<br>SENSE3  |

| 44    | G2         | 44  | G2         | PA08   | 8      | LCDA      | USART0<br>RTS | TC0<br>A0     | PEVC<br>PAD EVT0 | GLOC<br>OUT0    |                   | LCDCA<br>SEG23 | CATB<br>SENSE4  |

| 47    | F5         | 47  | F5         | PA09   | 9      | LCDA      | USART0<br>CTS | ТС0<br>В0     | PEVC<br>PAD EVT1 | PARC<br>PCDATA0 |                   | LCDCA<br>COM3  | CATB<br>SENSE5  |

| 48    | H2         | 48  | H2         | PA10   | 10     | LCDA      | USART0<br>CLK | TC0<br>A1     | PEVC<br>PAD EVT2 | PARC<br>PCDATA1 |                   | LCDCA<br>COM2  | CATB<br>SENSE6  |

| 49    | H3         | 49  | H3         | PA11   | 11     | LCDA      | USART0<br>RXD | TC0<br>B1     | PEVC<br>PAD EVT3 | PARC<br>PCDATA2 |                   | LCDCA<br>COM1  | CATB<br>SENSE7  |

| 50    | J2         | 50  | J2         | PA12   | 12     | LCDA      | USART0<br>TXD | TC0<br>A2     |                  | PARC<br>PCDATA3 |                   | LCDCA<br>COM0  | CATB<br>DIS     |

| 63    | H5         | 63  | H5         | PA13   | 13     | LCDA      | USART1<br>RTS | TC0<br>B2     | SPI<br>NPCS1     | PARC<br>PCDATA4 |                   | LCDCA<br>SEG5  | CATB<br>SENSE8  |

| 64    | <b>K</b> 7 | 64  | <b>K</b> 7 | PA14   | 14     | LCDA      | USART1<br>CLK | TC0<br>CLK0   | SPI<br>NPCS2     | PARC<br>PCDATA5 |                   | LCDCA<br>SEG6  | CATB<br>SENSE9  |

| 65    | G5         | 65  | G5         | PA15   | 15     | LCDA      | USART1<br>RXD | TC0<br>CLK1   | SPI<br>NPCS3     | PARC<br>PCDATA6 |                   | LCDCA<br>SEG7  | CATB<br>SENSE10 |

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 4 of 4)

|     | ATSAM4LC |     | ATSAM4LS   | Pin  | GPIO | Supply |               |                | G                | PIO Functio     | ns               |                |                 |

|-----|----------|-----|------------|------|------|--------|---------------|----------------|------------------|-----------------|------------------|----------------|-----------------|

| QFN | VFBGA    | QFN | VFBGA      |      |      |        | Α             | В              | С                | D               | E                | F              | G               |

| 59  | J6       | 59  | J6         | PC16 | 80   | LCDA   | TC1<br>B0     |                |                  | GLOC<br>IN5     |                  | LCDCA<br>SEG1  | CATB<br>SENSE17 |

| 60  | H4       | 60  | H4         | PC17 | 81   | LCDA   | TC1<br>A1     |                |                  | GLOC<br>IN6     |                  | LCDCA<br>SEG2  | CATB<br>SENSE18 |

| 61  | K6       | 61  | K6         | PC18 | 82   | LCDA   | TC1<br>B1     |                |                  | GLOC<br>IN7     |                  | LCDCA<br>SEG3  | CATB<br>SENSE19 |

| 62  | G4       | 62  | G4         | PC19 | 83   | LCDA   | TC1<br>A2     |                |                  | GLOC<br>OUT1    |                  | LCDCA<br>SEG4  | CATB<br>SENSE20 |

| 68  | H7       | 68  | H7         | PC20 | 84   | LCDA   | TC1<br>B2     |                |                  |                 |                  | LCDCA<br>SEG10 | CATB<br>SENSE21 |

| 69  | К8       | 69  | K8         | PC21 | 85   | LCDA   | TC1<br>CLK0   |                |                  | PARC<br>PCCK    |                  | LCDCA<br>SEG11 | CATB<br>SENSE22 |

| 70  | J8       | 70  | J8         | PC22 | 86   | LCDA   | TC1<br>CLK1   |                |                  | PARC<br>PCEN1   |                  | LCDCA<br>SEG12 | CATB<br>SENSE23 |

| 71  | H8       | 71  | H8         | PC23 | 87   | LCDA   | TC1<br>CLK2   |                |                  | PARC<br>PCEN2   |                  | LCDCA<br>SEG13 | CATB<br>DIS     |

| 79  | J9       | 79  | <b>J</b> 9 | PC24 | 88   | LCDB   | USART1<br>RTS | EIC<br>EXTINT1 | PEVC<br>PAD EVT0 | PARC<br>PCDATA0 |                  | LCDCA<br>SEG24 | CATB<br>SENSE24 |

| 80  | H9       | 80  | H9         | PC25 | 89   | LCDB   | USART1<br>CLK | EIC<br>EXTINT2 | PEVC<br>PAD EVT1 | PARC<br>PCDATA1 |                  | LCDCA<br>SEG25 | CATB<br>SENSE25 |

| 81  | G9       | 81  | G9         | PC26 | 90   | LCDB   | USART1<br>RXD | EIC<br>EXTINT3 | PEVC<br>PAD EVT2 | PARC<br>PCDATA2 | SCIF<br>GCLK0    | LCDCA<br>SEG26 | CATB<br>SENSE26 |

| 82  | F6       | 82  | F6         | PC27 | 91   | LCDB   | USART1<br>TXD | EIC<br>EXTINT4 | PEVC<br>PAD EVT3 | PARC<br>PCDATA3 | SCIF<br>GCLK1    | LCDCA<br>SEG27 | CATB<br>SENSE27 |

| 83  | G10      | 83  | G10        | PC28 | 92   | LCDB   | USART3<br>RXD | SPI<br>MISO    | GLOC<br>IN4      | PARC<br>PCDATA4 | SCIF<br>GCLK2    | LCDCA<br>SEG28 | CATB<br>SENSE28 |

| 84  | F7       | 84  | F7         | PC29 | 93   | LCDB   | USART3<br>TXD | SPI<br>MOSI    | GLOC<br>IN5      | PARC<br>PCDATA5 | SCIF<br>GCLK3    | LCDCA<br>SEG29 | CATB<br>SENSE29 |

| 85  | F8       | 85  | F8         | PC30 | 94   | LCDB   | USART3<br>RTS | SPI<br>SCK     | GLOC<br>IN6      | PARC<br>PCDATA6 | SCIF<br>GCLK IN0 | LCDCA<br>SEG30 | CATB<br>SENSE30 |

| 86  | F9       | 86  | F9         | PC31 | 95   | LCDB   | USART3<br>CLK | SPI<br>NPCS0   | GLOC<br>OUT1     | PARC<br>PCDATA7 | SCIF<br>GCLK IN1 | LCDCA<br>SEG31 | CATB<br>SENSE31 |

Table 3-2.

64-pin GPIO Controller Function Multiplexing (Sheet 1 of 3)

| ATSAM4LC | ATSAM4LS | Pin  | GPIO | Supply |               |              | G | PIO Functio | ns |   |             |

|----------|----------|------|------|--------|---------------|--------------|---|-------------|----|---|-------------|

| QFP      | QFP      |      | •    | S      |               |              |   |             |    |   |             |

| QFN      | QFN      |      |      |        | Α             | В            | С | D           | E  | F | G           |

| 1        | 1        | PA00 | 0    | VDDIO  |               |              |   |             |    |   |             |

| 2        | 2        | PA01 | 1    | VDDIO  |               |              |   |             |    |   |             |

| 3        | 3        | PA02 | 2    | VDDIN  | SCIF<br>GCLK0 | SPI<br>NPCS0 |   |             |    |   | CATB<br>DIS |

| 10       | 10       | PA03 | 3    | VDDIN  |               | SPI<br>MISO  |   |             |    |   |             |

## 3.4.7 ADC Input Pins

These pins are regular I/O pins powered from the VDDANA.

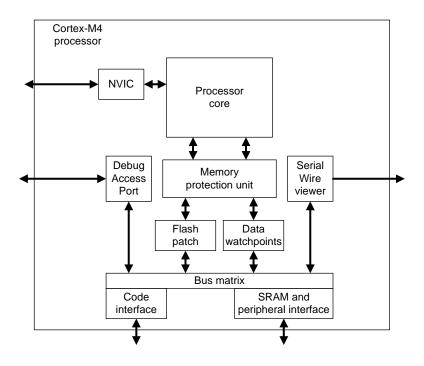

## 4. Cortex-M4 processor and core peripherals

## 4.1 Cortex-M4

The Cortex-M4 processor is a high performance 32-bit processor designed for the microcontroller market. It offers significant benefits to developers, including:

- outstanding processing performance combined with fast interrupt handling

- enhanced system debug with extensive breakpoint and trace capabilities

- efficient processor core, system and memories

- ultra-low power consumption with integrated sleep modes

- platform security robustness, with integrated memory protection unit (MPU).

The Cortex-M4 processor is built on a high-performance processor core, with a 3-stage pipeline Harvard architecture, making it ideal for demanding embedded applications. The processor delivers exceptional power efficiency through an efficient instruction set and extensively optimized design, providing high-end processing hardware including a range of single-cycle and SIMD multiplication and multiply-with-accumulate capabilities, saturating arithmetic and dedicated hardware division.

To facilitate the design of cost-sensitive devices, the Cortex-M4 processor implements tightlycoupled system components that reduce processor area while significantly improving interrupt handling and system debug capabilities. The Cortex-M4 processor implements a version of the Thumb<sup>®</sup> instruction set based on Thumb-2 technology, ensuring high code density and reduced program memory requirements. The Cortex-M4 instruction set provides the exceptional performance expected of a modern 32-bit architecture, with the high code density of 8-bit and 16-bit microcontrollers.

The Cortex-M4 processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC includes a *non-maskable interrupt* (NMI), and provides up to 80 interrupt priority levels. The tight integration of the proces-

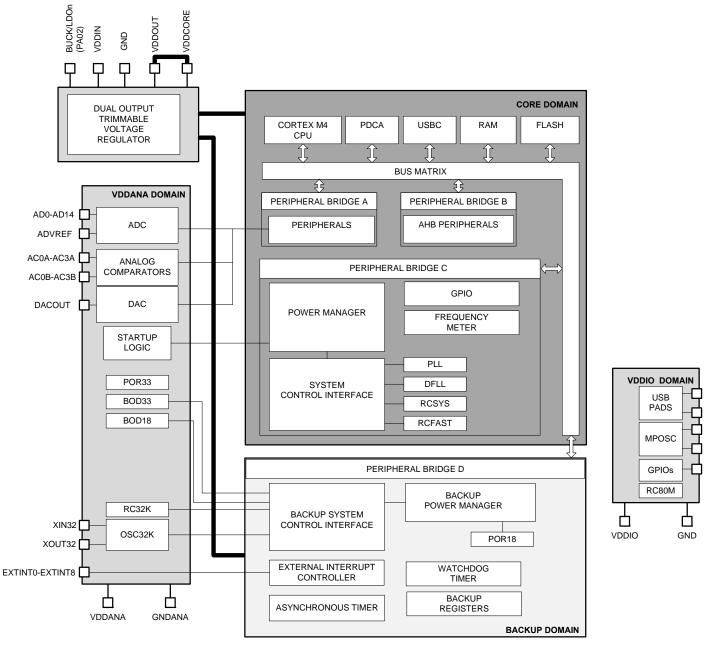

# 6. Power and Startup Considerations

# 6.1 Power Domain Overview

Figure 6-1. ATSAM4LS Power Domain Diagram

## 7. Low Power Techniques

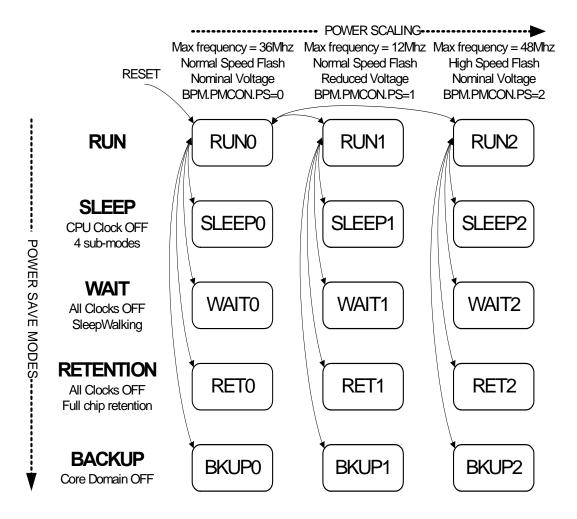

The ATSAM4L8/L4/L2 supports multiple power configurations to allow the user to optimize its power consumption in different use cases. The Backup Power Manager (BPM) implements different solutions to reduce the power consumption:

- The Power Save modes intended to reduce the logic activity and to adapt the power configuration. See "Power Save Modes" on page 55.

- The Power Scaling intended to scale the power configuration (voltage scaling of the regulator). See "Power Scaling" on page 60.

These two techniques can be combined together.

## 7.1 Power Save Modes

Refer to Section 6. "Power and Startup Considerations" on page 46 to get definition of the core and the backup domains.

mechanism can be useful for applications that only require the processor to run when an interrupt occurs.

Before entering the SLEEP mode, the user must configure:

- the SLEEP mode configuration field (BPM.PMCON.SLEEP), Refer to Table 7-1.

- the SCR.SLEEPDEEP bit to 0. (See the Power Management section in the ARM Cortex-M4 Processor chapter).

- the BPM.PMCON.RET bit to 0.

- the BPM.PMCON.BKUP bit to 0.

#### 7.1.1.2 Exiting SLEEP mode

The NVIC wakes the system up when it detects any non-masked interrupt with sufficient priority to cause exception entry. The system goes back to the RUN mode from which the SLEEP mode was entered. The CPU and affected modules are restarted. Note that even if an interrupt is enabled in SLEEP mode, it will not trigger if the source module is not clocked.

#### 7.1.2 WAIT Mode and RETENTION Mode

The WAIT and RETENTION modes allow achieving very low power consumption while maintaining the Core domain powered-on. Internal SRAM and registers contents of the Core domain are preserved.

In these modes, all clocks are stopped except the 32kHz clocks (OSC32K, RC32K) which are kept running if enabled.

In RETENTION mode, the SleepWalking feature is not supported and must not be used.

#### 7.1.2.1 Entering WAIT or RETENTION Mode

The WAIT or RETENTION modes are entered by executing the WFI instruction with the following settings:

- set the SCR.SLEEPDEEP bit to 1. (See the Power Management section in the ARM Cortex-M4 Processor chapter).

- set the BPM.PSAVE.BKUP bit to 0.

- set the BPM.PMCON.RET bit to RETENTION or WAIT mode.

SLEEPONEXIT feature is also available. See "Entering SLEEP mode" on page 56.

#### 7.1.2.2 Exiting WAIT or RETENTION Mode

In WAIT or RETENTION modes, synchronous clocks are stopped preventing interrupt sources from triggering. To wakeup the system, asynchronous wake up sources (AST, EIC, USBC ...) should be enabled in the peripheral (refer to the documentation of the peripheral). The PM.AWEN (Asynchronous Wake Up Enable) register should also be enabled for all peripheral except for EIC and AST.

When the enabled asynchronous wake up event occurs and the system is waken-up, it will generate either:

- an interrupt on the PM WAKE interrupt line if enabled (Refer to Section 9. "Power Manager (PM)" on page 677). In that case, the PM.WCAUSE register indicates the wakeup source.

- or an interrupt directly from the peripheral if enabled (Refer to the section of the peripheral).

When waking up, the system goes back to the RUN mode mode from which the WAIT or RETENTION mode was entered.

# ATSAM4L8/L4/L2

## 8.7 Enhanced Debug Port (EDP)

Rev.: 1.0.0.0

#### 8.7.1 Features

- IEEE1149.1 compliant JTAG debug port

- Serial Wire Debug Port

- Boundary-Scan chain on all digital pins for board-level testing

- Debugger Hot-Plugging

- SMAP core reset request source

#### 8.7.2 Overview

The enhanced debug port embeds a standard ARM debug port plus some specific hardware intended for testability and activation of the debug port features. All the information related to the ARM Debug Interface implementation can be found in the ARM Debug Interface v5.1 Architecture Specification document.

#### It features:

- A single Debug Port (SWJ-DP), that provides the external physical connection to the interface and supports two DP implementations:

- the JTAG Debug Port (JTAG-DP)

- the Serial Wire Debug Port (SW-DP)

- A supplementary JTAG TAP (BSCAN-TAP) connected in parallel with the JTAG-DP that implements the boundary scan instructions detailed in

- A JTAG-FILTER module that monitors TCK and RESET\_N pins to handle specific features like the detection of a debugger hot-plugging and the request of reset of the Cortex-M4 at startup.

The JTAG-FILTER module detects the presence of a debugger. When present, JTAG pins are automatically assigned to the Enhanced Debug Port(EDP). If the SWJ-DP is switched to the SW mode, then TDI and TDO alternate functions are released. The JTAG-FILTER also implements a CPU halt mechanism. When triggered, the Cortex-M4 is maintained under reset after the external reset is released to prevent any system corruption during later programmation operations.

#### 8.11.8 Chip erase typical procedure

The chip erase operation is triggered by writing a one in the CE bit in the Control Register (CR.CE). This clears first all volatile memories in the system and second the whole flash array. Note that the User page is not erased in this process. To ensure that the chip erase operation is completed, check the DONE bit in the Status Register (SR.DONE). Also note that the chip erase operation depends on clocks and power management features that can be altered by the CPU. It is important to ensure that it is stopped. The recommended sequence is shown below:

- 1. At power up, RESET\_N is driven low by a debugger. The on-chip regulator holds the system in a POR state until the input supply is above the POR threshold. The system continues to be held in this static state until the internally regulated supplies have reached a safe operating.

- PM starts, clocks are switched to the slow clock (Core Clock, System Clock, Flash Clock, and any Bus Clocks that do not have clock gate control). Internal resets are maintained due to the external reset.

- The debug port and access ports receives a clock and leave the reset state

- 3. The debugger maintains a low level on TCK and release RESET\_N.

- The SMAP asserts the core\_hold\_reset signal

- 4. The Cortex-M4 core remains in reset state, meanwhile the rest of the system is released.

- 5. The Chip erase operation can be performed by issuing the SMAP Chip Erase command. In this case:

- volatile memories are cleared first

- followed by the clearing of the flash array

- followed by the clearing of the protected state

Atmel

After operation is completed, the chip must be restarted by either controling RESET\_N or switching power off/on. Make sure that the TCK pin is high when releasing RESET\_N not to halt the core.

#### 8.11.9 Setting the protected state

This is done by issuing a specific flash controller command, for more information, refer to the Flash Controller chapter and to section 8.11.7Flash Programming typical procedure97. The protected state is defined by a highly secure Flash builtin mechanism. Note that for this programmation to propagate, it is required to reset the chip.

| Symbol              | Parameter                 | Description                                                          | Мах  | Units |

|---------------------|---------------------------|----------------------------------------------------------------------|------|-------|

| f <sub>CPU</sub>    | CPU clock frequency       |                                                                      | 12   |       |

| f <sub>PBA</sub>    | PBA clock frequency       |                                                                      | 12   |       |

| f <sub>PBB</sub>    | PBB clock frequency       |                                                                      | 12   |       |

| f <sub>PBC</sub>    | PBC clock frequency       |                                                                      | 12   |       |

| f <sub>PBD</sub>    | PBD clock frequency       |                                                                      | 12   |       |

| f <sub>GCLK0</sub>  | GCLK0 clock frequency     | DFLLIF main reference, GCLK0 pin                                     | 16.6 |       |

| f <sub>GCLK1</sub>  | GCLK1 clock frequency     | DFLLIF dithering and SSGreference,<br>GCLK1 pin                      | 16.6 |       |

| f <sub>GCLK2</sub>  | GCLK2 clock frequency     | AST, GCLK2 pin                                                       | 6.6  |       |

| f <sub>GCLK3</sub>  | GCLK3 clock frequency     | CATB, GCLK3 pin                                                      | 17.3 |       |

| f <sub>GCLK4</sub>  | GCLK4 clock frequency     | FLO and AESA                                                         | 16.6 |       |

| f <sub>GCLK5</sub>  | GCLK5 clock frequency     | GLOC, TC0 and RC32KIFB_REF                                           | 26.6 |       |

| f <sub>GCLK6</sub>  | GCLK6 clock frequency     | ABDACB and IISC                                                      | 16.6 | MHz   |

| f <sub>GCLK7</sub>  | GCLK7 clock frequency     | USBC                                                                 | 16.6 |       |

| f <sub>GCLK8</sub>  | GCLK8 clock frequency     | TC1 and PEVC[0]                                                      | 16.6 |       |

| f <sub>GCLK9</sub>  | GCLK9 clock frequency     | PLL0 and PEVC[1]                                                     | 16.6 |       |

| f <sub>GCLK10</sub> | GCLK10 clock<br>frequency | ADCIFE                                                               | 16.6 |       |

| f <sub>GCLK11</sub> | GCLK11 clock<br>frequency | Master generic clock. Can be used as source for other generic clocks | 51.2 |       |

|                     | 0000 1 11                 | Oscillator 0 in crystal mode                                         | 16   |       |

| f <sub>OSC0</sub>   | OSC0 output frequency     | Oscillator 0 in digital clock mode                                   | 16   |       |

| f <sub>PLL</sub>    | PLL output frequency      | Phase Locked Loop                                                    | N/A  |       |

| f <sub>DFLL</sub>   | DFLL output frequency     | Digital Frequency Locked Loop                                        | N/A  |       |

| f <sub>RC80M</sub>  | RC80M output<br>frequency | Internal 80MHz RC Oscillator                                         | N/A  |       |

**Table 9-5.**Maximum Clock Frequencies in Power Scaling Mode 1 and RUN Mode

| Mode      | Conditions                                    | T <sub>A</sub> | Typical<br>Wakeup Time | Тур  | Max <sup>(1)</sup> | Unit |

|-----------|-----------------------------------------------|----------------|------------------------|------|--------------------|------|

|           | Quuitabing mode                               | 25°C           | 9 * Main clock         | 3817 | 4033               |      |

| SLEEP0    | Switching mode                                | 85°C           | cycles                 | 4050 | 4507               |      |

|           | Quitabing mode                                | 25°C           | 9 * Main clock         | 2341 | 2477               |      |

| SLEEP1    | Switching mode                                | 85°C           | cycles + 500ns         | 2525 | 2832               |      |

| SLEEP2    | Quitabing made                                | 25°C           | 9 * Main clock         | 1758 | 1862               |      |

|           | Switching mode                                | 85°C           | cycles + 500ns         | 1925 | 1971               |      |

| SLEEP3    | Linear mode                                   |                |                        | 51   | 60                 |      |

|           | OSC32K and AST running<br>Fast wake-up enable |                | 4.5                    | 6.7  |                    | μΑ   |

| WAIT      | OSC32K and AST stopped<br>Fast wake-up enable |                | 1.5µs                  | 5.5  |                    |      |

| RETENTION | OSC32K running<br>AST running at 1kHz         | 25°C           | 1.5µs                  | 3.9  |                    |      |

|           | AST and OSC32K stopped                        |                |                        | 3.0  |                    |      |

| BACKUP    | OSC32K running<br>AST running at 1 kHz        |                |                        | 1.5  | 3.1                |      |

|           | AST and OSC32K stopped                        |                |                        | 0.9  | 1.7                |      |

Table 9-7.

ATSAM4L8 Current consumption and Wakeup time for power scaling mode 0 and 2

1. These values are based on characterization. These values are not covered by test limits in production.

#### 9.5.2 Power Scaling 1

The values in Table 34-7 are measured values of power consumption under the following conditions, except where noted:

Operating conditions for power scaling mode 1

$-V_{VDDIN} = 3.3V$

- Wake up time from low power modes is measured from the edge of the wakeup signal to the first instruction fetched in flash.

- Oscillators

- OSC0 (crystal oscillator) and OSC32K (32kHz crystal oscillator) stopped

- RCFAST Running at 12MHz

- Clocks

- RCFAST used as main clock source

- CPU, AHB clocks undivided

- APBC and APBD clocks divided by 4

- APBA and APBB bridges off

- The following peripheral clocks running

- PM, SCIF, AST, FLASHCALW, APBC and APBD bridges

#### 9.9.4 Analog- to Digital Converter Characteristics

| Table 9-45. C | perating conditions |

|---------------|---------------------|

|---------------|---------------------|

| Symbol                  | Parameter                                                     | Conditions                                             | Min  | Тур | Max    | Units  |  |  |

|-------------------------|---------------------------------------------------------------|--------------------------------------------------------|------|-----|--------|--------|--|--|

|                         | Temperature range                                             |                                                        | -40  |     | +85    | °C     |  |  |

|                         | Resolution <sup>(1)</sup>                                     | Мах                                                    |      | 12  | 12 (2) | Bit    |  |  |

|                         | Sampling clock <sup>(3)</sup>                                 | Differential modes, Gain=1X                            | 5    |     | 300    |        |  |  |

|                         |                                                               | Unipolar modes, Gain=1X                                | 5    |     | 250    | - kHz  |  |  |

| 4                       | ADC clock frequency <sup>(3)</sup>                            | Differential modes                                     | 0.03 |     | 1.8    |        |  |  |

| f <sub>ADC</sub>        | ADC Clock frequency.                                          | Unipolar modes                                         | 0.03 |     | 1.5    | MHz    |  |  |

| <b>-</b>                | Sampling time <sup>(3)</sup>                                  | Differential modes                                     | 16.5 |     | 277    | μs     |  |  |

| T <sub>SAMPLEHOLD</sub> | Sampling time                                                 | Unipolar modes                                         | 16.5 |     | 333    |        |  |  |

|                         | Conversion rate <sup>(1)</sup>                                | 1X gain, differential                                  |      |     | 300    | kSps   |  |  |

|                         | Internal channel conversion rate <sup>(3)</sup>               | V <sub>VDD</sub> /10, Bandgap and Temperature channels |      |     | 125    | kSps   |  |  |

|                         |                                                               | 1X gain, (resolution/2)+gain <sup>(4)</sup>            |      |     | 6      |        |  |  |

|                         |                                                               | 2X and 4X gain                                         |      |     | 7      | _      |  |  |

|                         | Conversion time (latency)<br>Differential mode (no windowing) | 8X and 16X gain                                        |      |     | 8      | Cycles |  |  |

|                         |                                                               | 32X and 64X gain                                       |      |     | 9      |        |  |  |

|                         |                                                               | 64X gain and unipolar                                  |      |     | 10     | 1      |  |  |

1. These values are based on characterization. These values are not covered by test limits in production

2. Single ended or using divide by two max resolution: 11 bits

3. These values are based on simulation. These values are not covered by test limits in production

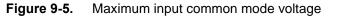

4. See Figure 9-5

# ATSAM4L8/L4/L2

Table 9-46. DC Characteristics

| Symbol              | Parameter                                        | Conditions                                      | Min  | Тур | Мах            | Units  |

|---------------------|--------------------------------------------------|-------------------------------------------------|------|-----|----------------|--------|

| VDDANA              | Supply voltage <sup>(1)</sup>                    |                                                 | 1.6  |     | 3.6            | V      |

|                     |                                                  | Differential mode                               | 1.0  |     | VDDANA<br>-0.6 |        |

|                     | Reference range <sup>(2)</sup>                   | Unipolar and Window modes                       | 1.0  |     | 1.0            | V      |

|                     |                                                  | Using divide by two function (differential)     | 2.0  |     | VDDANA         |        |

|                     | Absolute min, max input voltage <sup>(2)</sup>   |                                                 | -0,1 |     | VDDANA<br>+0.1 | V      |

|                     | Start up time <sup>(2)</sup>                     | ADC with reference already enabled              |      | 12  | 24             | Cycles |

|                     |                                                  | No gain compensation<br>Reference buffer        |      |     | 5              | μs     |

|                     |                                                  | Gain compensation<br>Reference buffer           |      |     | 60             | Cycles |

| R <sub>SAMPLE</sub> | Input channel source resistance <sup>(2)</sup>   |                                                 |      |     | 0.5            | kΩ     |

| C <sub>SAMPLE</sub> | Sampling capacitance <sup>(2)</sup>              |                                                 | 2.9  | 3.6 | 4.3            | pF     |

|                     | Potoronoo input course registence <sup>(2)</sup> | Gain compensation                               |      |     | 2              | kΩ     |

|                     | Reference input source resistance <sup>(2)</sup> | No gain compensation                            |      |     | 1              | MΩ     |

|                     | ADC reference settling time <sup>(2)</sup>       | After changing<br>reference/mode <sup>(3)</sup> |      | 5   | 60             | Cycles |

1. These values are based on characterization. These values are not covered by test limits in production

2. These values are based on simulation. These values are not covered by test limits in production

3. Requires refresh/flush otherwise conversion time (latency) + 1

| Table 9-47. | Differential mode, gair | ∩=1 |

|-------------|-------------------------|-----|

|-------------|-------------------------|-----|

| Symbol | Parameter                                      | Conditions                                                   | Min  | Тур  | Max  | Units |

|--------|------------------------------------------------|--------------------------------------------------------------|------|------|------|-------|

|        | Accuracy without compensation (1)              |                                                              |      | 7    |      | ENOB  |

|        | Accuracy after compensation <sup>(1)</sup>     | (INL, gain and offset)                                       |      |      | 11   | ENOB  |

| INL    | Integral Non Linearity <sup>(2)</sup>          | After calibration,<br>Gain compensation                      |      | 1.2  | 1.7  | LSBs  |

| DNL    | Differential Non Linearity <sup>(2)</sup>      | After calibration                                            |      | 0.7  | 1.0  | LSBs  |

|        |                                                | External reference                                           | -5.0 | -1.0 | 5.0  |       |

|        | Gain error <sup>(2)</sup>                      | VDDANA/1.6                                                   | -40  |      | 40   | mV    |

|        |                                                | VDDANA/2.0                                                   | -40  |      | 40   |       |

|        |                                                | Bandgap After calibration                                    | -30  |      | 30   |       |

|        | Gain error drift vs voltage <sup>(1)</sup>     | External reference                                           | -2   |      | 2    | mV/V  |

|        | Gain error drift vs temperature <sup>(1)</sup> | After calibration + bandgap drift<br>If using onchip bandgap |      |      | 0.08 | mV/°K |

|        |                                                | External reference                                           | -5.0 |      | 5.0  |       |

|        | O#aat array (2)                                | VDDANA/1.6                                                   | -10  |      | 10   |       |

|        | Offset error <sup>(2)</sup>                    | VDDANA/2.0                                                   | -10  |      | 10   | – mV  |

|        |                                                | Bandgap After calibration                                    | -10  |      | 10   | 1     |

|        | Offset error drift vs voltage <sup>(1)</sup>   |                                                              | -4   |      | 4    | mV/V  |

#### Table 9-47. Differential mode, gain=1

| Offset error drift vs temperature <sup>(1)</sup> |                                                      |       |                      | 0.04 | mV/°K |  |

|--------------------------------------------------|------------------------------------------------------|-------|----------------------|------|-------|--|

| Conversion range <sup>(2)</sup>                  | Vin-Vip                                              | -Vref |                      | Vref | V     |  |

| ICMR <sup>(1)</sup>                              |                                                      |       | see<br>Figure<br>9-5 |      |       |  |

| PSRR <sup>(1)</sup>                              | fvdd=1Hz, ext ADVREFP=3.0V<br>V <sub>VDD</sub> =3.6V |       | 100                  |      | dB    |  |

| PORC                                             | fvdd=2MHz, ext<br>ADVREFP=3.0V V <sub>VDD</sub> =3.6 |       | 50                   |      | 0B    |  |

| DC supply surrent <sup>(2)</sup>                 | VDDANA=3.6V,<br>ADVREFP=3.0V                         |       | 1.2                  |      | mA    |  |

| DC supply current <sup>(2)</sup>                 | VDDANA=1.6V,<br>ADVREFP=1.0V                         |       | 0.6                  |      | IIIA  |  |

1. These values are based on simulation only. These values are not covered by test limits in production or characterization

2. These values are based on characterization and not tested in production, and valid for an input voltage between 10% to 90% of reference voltage.

| Table 9-48. | Unipolar mode, gain= | -1 |

|-------------|----------------------|----|

|-------------|----------------------|----|

| Symbol | Parameter                                     | Conditions                                              | Min   | Тур                  | Max  | Units  |  |  |

|--------|-----------------------------------------------|---------------------------------------------------------|-------|----------------------|------|--------|--|--|

|        | Accuracy without compensation (1)             |                                                         |       | 7                    |      | ENOB   |  |  |

|        | Accuracy after compensation <sup>(1)</sup>    |                                                         |       |                      | 11   | ENOB   |  |  |

| INL    | Integral Non Linearity <sup>(2)</sup>         | After calibration Dynamic tests<br>No gain compensation |       |                      | ±3   |        |  |  |

|        |                                               | After calibration Dynamic tests Gain compensation       |       |                      | ±3   | – LSBs |  |  |

| DNL    | Differential Non Linearity <sup>(2)</sup>     | After calibration                                       |       |                      | ±2.8 | LSBs   |  |  |

|        |                                               | External reference                                      | -15   |                      | 15   |        |  |  |

|        | – Gain error <sup>(2)</sup>                   | VDDANA/1.6                                              | -50   |                      | 50   | mV     |  |  |

|        |                                               | VDDANA/2.0                                              | -30   |                      | 30   |        |  |  |

|        | _                                             | Bandgap After calibration                               | -10   |                      | 10   |        |  |  |

|        | Gain error drift vs voltage <sup>(1)</sup>    | External reference                                      | -8    |                      | 8    | mV/V   |  |  |

|        | Gain error drift temperature <sup>(1)</sup>   | + bandgap drift If using bandgap                        |       |                      | 0.08 | mV/°K  |  |  |

|        |                                               | External reference                                      | -15   |                      | 15   | mV     |  |  |

| C      | – Offset error <sup>(2)</sup>                 | VDDANA/1.6                                              | -15   |                      | 15   |        |  |  |

|        |                                               | VDDANA/2.0                                              | -15   |                      | 15   |        |  |  |

|        | _                                             | Bandgap After calibration                               | -10   |                      | 10   |        |  |  |

|        | Offset error drift <sup>(1)</sup>             |                                                         | -4    |                      | 4    | mV/V   |  |  |

|        | Offset error drift temperature <sup>(1)</sup> |                                                         |       | 0                    | 0.04 | mV/°K  |  |  |

|        | Conversion range <sup>(1)</sup>               | Vin-Vip                                                 | -Vref |                      | Vref | V      |  |  |

|        | ICMR <sup>(1)</sup>                           |                                                         |       | see<br>Figure<br>9-5 |      |        |  |  |

Table 9-50. Analog Comparator Characteristics

| Symbol                    | Parameter                                                                      | Conditions                                                                           | Min | Тур | Max  | Units |

|---------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----|-----|------|-------|

|                           |                                                                                | $V_{ACREFN}$ =0.1V to VDDIO-0.1V,<br>hysteresis = 1 <sup>(2)</sup><br>Fast mode      | 10  |     | 55   | mV    |

|                           |                                                                                | $V_{ACREFN}$ =0.1V to VDDIO-0.1V,<br>hysteresis = 1 <sup>(2)</sup><br>Low power mode | 10  |     | 68   | mV    |

| Hysteresis <sup>(1)</sup> | Libertorrois(1)                                                                | $V_{ACREFN} = 0.1V$ to VDDIO-0.1V,<br>hysteresis = $2^{(2)}$<br>Fast mode            | 26  |     | 83   | mV    |

|                           | $V_{ACREFN} = 0.1V$ to VDDIO-0.1V,<br>hysteresis = $2^{(2)}$<br>Low power mode | 19                                                                                   |     | 91  | mV   |       |

|                           | $V_{ACREFN}$ =0.1V to VDDIO-0.1V,<br>hysteresis = $3^{(2)}$<br>Fast mode       | 43                                                                                   |     | 106 | mV   |       |

|                           |                                                                                | $V_{ACREFN} = 0.1V$ to VDDIO-0.1V,<br>hysteresis = $3^{(2)}$<br>Low power mode       | 32  |     | 136  | mV    |

|                           | Dranagation dalou(1)                                                           | Changes for V <sub>ACM</sub> =VDDIO/2<br>100mV Overdrive<br>Fast mode                |     |     | 67   | ns    |

|                           | Propagation delay <sup>(1)</sup>                                               | Changes for V <sub>ACM</sub> =VDDIO/2<br>100mV Overdrive<br>Low power mode           |     |     | 315  | ns    |

|                           | Startup time <sup>(1)</sup>                                                    | Enable to ready delay<br>Fast mode                                                   |     |     | 1.19 | μs    |

| t <sub>STARTUP</sub>      |                                                                                | Enable to ready delay<br>Low power mode                                              |     |     | 3.61 | μs    |

|                           | Channel current                                                                | Low power mode, no hysteresis                                                        |     | 4.9 | 8.7  | μA    |

| I <sub>AC</sub>           | consumption <sup>(3)</sup>                                                     | Fast mode, no hysteresis                                                             |     | 63  | 127  | μΑ    |

1. These values are based on characterization. These values are not covered by test limits in production

2. HYSTAC.CONFn.HYS field, refer to the Analog Comparator Interface chapter

3. These values are based on simulation. These values are not covered by test limits in production or characterization

- Atmel

## Table 9-65.JTAG Timings(1)

| Symbol | Parameter                          | Conditions              | Min  | Max  | Units |  |

|--------|------------------------------------|-------------------------|------|------|-------|--|

| JTAG0  | TCK Low Half-period                |                         | 21.8 |      |       |  |

| JTAG1  | TCK High Half-period               |                         | 8.6  |      |       |  |

| JTAG2  | TCK Period                         |                         | 30.3 |      |       |  |

| JTAG3  | TDI, TMS Setup before TCK High     | V <sub>VDDIO</sub> from | 2.0  |      |       |  |

| JTAG4  | TDI, TMS Hold after TCK High       | 3.0V to 3.6V,           | 2.3  |      |       |  |

| JTAG5  | TDO Hold Time                      | maximum<br>external     | 9.5  |      | ns    |  |

| JTAG6  | TCK Low to TDO Valid               | capacitor =             |      | 21.8 |       |  |

| JTAG7  | Boundary Scan Inputs Setup Time    | 40pF                    | 0.6  |      |       |  |

| JTAG8  | Boundary Scan Inputs Hold Time     |                         | 6.9  |      |       |  |

| JTAG9  | Boundary Scan Outputs Hold Time    |                         | 9.3  |      |       |  |

| JTAG10 | TCK to Boundary Scan Outputs Valid |                         |      | 32.2 |       |  |

Note: 1. These values are based on simulation. These values are not covered by test limits in production.

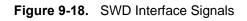

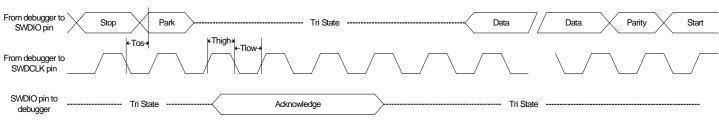

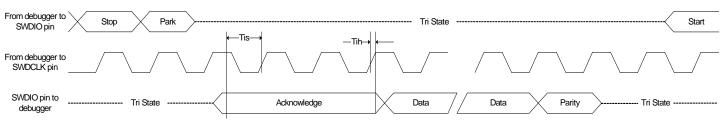

## 9.10.6 SWD Timing

## Read Cycle

## Write Cycle

| Table 11-3. AT SAM4LOZ SUD Selle Oldening Informatio | Table 11-3. | ATSAM4LC2 Sub Serie Ordering Information |

|------------------------------------------------------|-------------|------------------------------------------|

|------------------------------------------------------|-------------|------------------------------------------|

| Ordering Code    | Flash<br>(Kbytes) | RAM<br>(Kbytes) | Package  | Conditioning | Package<br>Type | Temperature Operating<br>Range |

|------------------|-------------------|-----------------|----------|--------------|-----------------|--------------------------------|

| ATSAM4LC2CA-AU   |                   |                 |          | Tray         |                 |                                |

| ATSAM4LC2CA-AUR  |                   | TQFP100         | Reel     |              |                 |                                |

| ATSAM4LC2CA-CFU  | 128               | 128 32          | VFBGA100 | Tray         | Green           |                                |

| ATSAM4LC2CA-CFUR |                   |                 |          | Reel         |                 | Industrial -40°C to 85°C       |

| ATSAM4LC2BA-AU   |                   |                 | TQFP64   | Tray         |                 |                                |

| ATSAM4LC2BA-AUR  |                   |                 |          | Reel         |                 |                                |

| ATSAM4LC2BA-MU   |                   |                 | 2 QFN64  | Tray         |                 |                                |

| ATSAM4LC2BA-MUR  |                   |                 |          | Reel         |                 |                                |

| ATSAM4LC2BA-UUR  |                   |                 | WLCSP64  | Reel         |                 |                                |

| ATSAM4LC2AA-AU   |                   |                 | TQFP48   | Tray         |                 |                                |

| ATSAM4LC2AA-AUR  |                   |                 |          | Reel         |                 |                                |

| ATSAM4LC2AA-MU   |                   |                 | 0.71110  | Tray         |                 |                                |

| ATSAM4LC2AA-MUR  |                   |                 | QFN48    | Reel         |                 |                                |

## Table 11-4. ATSAM4LS8 Sub Serie Ordering Information

| Ordering Code    | Flash<br>(Kbytes) | RAM<br>(Kbytes) | Package  | Conditioning | Package<br>Type | Temperature Operating<br>Range |  |

|------------------|-------------------|-----------------|----------|--------------|-----------------|--------------------------------|--|

| ATSAM4LS8CA-AU   |                   |                 |          | Tray         |                 |                                |  |

| ATSAM4LS8CA-AUR  | 512               | 12 64           | TQFP100  | Reel         |                 |                                |  |

| ATSAM4LS8CA-CFU  |                   |                 | VFBGA100 | Tray         | Green           |                                |  |

| ATSAM4LS8CA-CFUR |                   |                 |          | Reel         |                 |                                |  |

| ATSAM4LS8BA-AU   |                   |                 |          | Tray         |                 | Industrial -40°C to 85°C       |  |

| ATSAM4LS8BA-AUR  |                   |                 |          | Reel         |                 |                                |  |

| ATSAM4LS8BA-MU   |                   |                 |          | Tray         |                 |                                |  |

| ATSAM4LS8BA-MUR  |                   |                 | G        | QFN64        | Reel            |                                |  |

| ATSAM4LS8BA-UUR  |                   |                 | WLCSP64  | Reel         |                 |                                |  |

| ATSAM4LS8AA-MU   |                   |                 |          |              | Tray            |                                |  |

| ATSAM4LS8AA-MUR  |                   |                 | QFN48    | Reel         |                 |                                |  |

#### 12.1.7 FLASHCALW

## Corrupted data in flash may happen after flash page write operations.

After a flash page write operation, reading (data read or code fetch) in flash may fail. This may lead to an expectition or to others errors derived from this corrupted read access. **Fix/Workaround**

## 13.5 Rev. E – 07/13

- 1. Added ATSAM4L8 derivatives and WLCSP packages for ATSAM4L4/2

- 2. Added operating conditions details in Electrical Characteristics Chapter

- 3. Fixed "Supply Rise Rates and Order"

- 4. Added number of USART available in sub-series

- 5. Fixed IO line considerations for USB pins

- 6. Removed useless information about CPU local bus which is not implemented

- 7. Removed useless information about Modem support which is not implemented

- 8. Added information about unsupported features in Power Scaling mode 1

- 9. Fixed SPI timings

## 13.6 Rev. F- 12/13

- 1. Fixed table 3-6 TDI is connected to pin G3 in WLCSP package

- 2. Changed table 42-48 -ADCIFE Electricals in unipolar mode : PSRR & DC supply current typical values

- 3. Fixed SPI timing characteristics

- 4. Fixed BOD33 typical step size value

## 13.7 Rev. G- 03/14

- 1. Added WLCSP64 packages for SAM4LC8 and SAM4LS8 sub-series

- 2. Removed unsupported SWAP feature in LCD module

- 3. Added mnimal value for ADC Reference range

## 13.8 Rev. H- 11/16

1. Fixed AESA configuration in Overview chapter for SAM4LS sub-series