#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT        |

| Number of I/O              | 75                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 32K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.68V ~ 3.6V                                                             |

| Data Converters            | A/D 15x12b; D/A 1x10b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-TQFP                                                                 |

| Supplier Device Package    | 100-TQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4lc2ca-au |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

events, even in sleep modes where the module clock is stopped. Power monitoring is supported by on-chip Power-on Reset (POR18, POR33), Brown-out Detectors (BOD18, BOD33). The device features several oscillators, such as Phase Locked Loop (PLL), Digital Frequency Locked Loop (DFLL), Oscillator 0 (OSC0), Internal RC 4,8,12MHz oscillator (RCFAST), system RC oscillator (RCSYS), Internal RC 80MHz, Internal 32kHz RC and 32kHz Crystal Oscillator. Either of these oscillators can be used as source for the system clock. The DFLL is a programmable internal oscillator from 40 to 150MHz. It can be tuned to a high accuracy if an accurate reference clock is running, e.g. the 32kHz crystal oscillator.

The Watchdog Timer (WDT) will reset the device unless it is periodically serviced by the software. This allows the device to recover from a condition that has caused the system to be unstable.

The Asynchronous Timer (AST) combined with the 32kHz crystal oscillator supports powerful real-time clock capabilities, with a maximum timeout of up to 136 years. The AST can operate in counter or calendar mode.

The Frequency Meter (FREQM) allows accurate measuring of a clock frequency by comparing it to a known reference clock.

The Full-speed USB 2.0 device and embedded host interface (USBC) supports several USB classes at the same time utilizing the rich end-point configuration.

The device includes six identical 16-bit Timer/Counter (TC) channels. Each channel can be independently programmed to perform frequency measurement, event counting, interval measurement, pulse generation, delay timing, and pulse width modulation.

The ATSAM4L8/L4/L2 also features many communication interfaces, like USART, SPI, or TWI, for communication intensive applications. The USART supports different communication modes, like SPI Mode and LIN Mode.

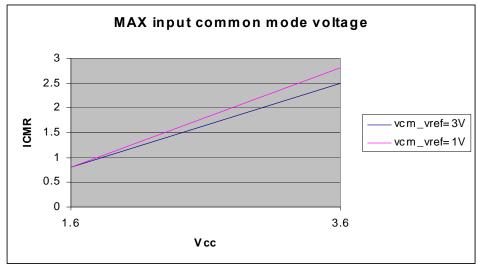

A general purpose 16-channel ADC is provided, as well as four analog comparators (ACIFC). The ADC can operate in 12-bit mode at full speed. The analog comparators can be paired to detect when the sensing voltage is within or outside the defined reference window.

Atmel offers the QTouch Library for embedding capacitive touch buttons, sliders, and wheels functionality. The patented charge-transfer signal acquisition offers robust sensing and includes fully debounced reporting of touch keys as well as Adjacent Key Suppression<sup>®</sup> (AKS<sup>®</sup>) technology for unambiguous detection of key events. The easy-to-use QTouch Suite toolchain allows you to explore, develop, and debug your own touch applications.

The Audio Bitstream DAC (ABDACB) converts a 16-bit sample value to a digital bitstream with an average value proportional to the sample value. Two channels are supported, making the ABDAC particularly suitable for stereo audio.

The Inter-IC Sound Controller (IISC) provides a 5-bit wide, bidirectional, synchronous, digital audio link with external audio devices. The controller is compliant with the Inter-IC Sound (I2S) bus specification.

ATSAM4L8/L4/L2

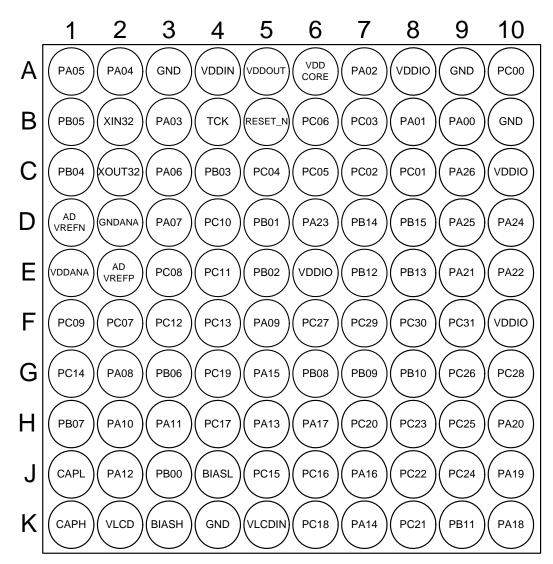

Figure 3-2. ATSAM4LC VFBGA100 Pinout

- Atmel

10

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 4 of 4)

|     | ATSAM4LC |     | ATSAM4LS   | Pin  | GPIO | Supply |               |                | G                | PIO Functio     | ns               |                |                 |

|-----|----------|-----|------------|------|------|--------|---------------|----------------|------------------|-----------------|------------------|----------------|-----------------|

| QFN | VFBGA    | QFN | VFBGA      |      |      |        | Α             | В              | С                | D               | E                | F              | G               |

| 59  | J6       | 59  | J6         | PC16 | 80   | LCDA   | TC1<br>B0     |                |                  | GLOC<br>IN5     |                  | LCDCA<br>SEG1  | CATB<br>SENSE17 |

| 60  | H4       | 60  | H4         | PC17 | 81   | LCDA   | TC1<br>A1     |                |                  | GLOC<br>IN6     |                  | LCDCA<br>SEG2  | CATB<br>SENSE18 |

| 61  | K6       | 61  | K6         | PC18 | 82   | LCDA   | TC1<br>B1     |                |                  | GLOC<br>IN7     |                  | LCDCA<br>SEG3  | CATB<br>SENSE19 |

| 62  | G4       | 62  | G4         | PC19 | 83   | LCDA   | TC1<br>A2     |                |                  | GLOC<br>OUT1    |                  | LCDCA<br>SEG4  | CATB<br>SENSE20 |

| 68  | H7       | 68  | H7         | PC20 | 84   | LCDA   | TC1<br>B2     |                |                  |                 |                  | LCDCA<br>SEG10 | CATB<br>SENSE21 |

| 69  | K8       | 69  | K8         | PC21 | 85   | LCDA   | TC1<br>CLK0   |                |                  | PARC<br>PCCK    |                  | LCDCA<br>SEG11 | CATB<br>SENSE22 |

| 70  | J8       | 70  | J8         | PC22 | 86   | LCDA   | TC1<br>CLK1   |                |                  | PARC<br>PCEN1   |                  | LCDCA<br>SEG12 | CATB<br>SENSE23 |

| 71  | Н8       | 71  | H8         | PC23 | 87   | LCDA   | TC1<br>CLK2   |                |                  | PARC<br>PCEN2   |                  | LCDCA<br>SEG13 | CATB<br>DIS     |

| 79  | J9       | 79  | <b>J</b> 9 | PC24 | 88   | LCDB   | USART1<br>RTS | EIC<br>EXTINT1 | PEVC<br>PAD EVT0 | PARC<br>PCDATA0 |                  | LCDCA<br>SEG24 | CATB<br>SENSE24 |

| 80  | Н9       | 80  | H9         | PC25 | 89   | LCDB   | USART1<br>CLK | EIC<br>EXTINT2 | PEVC<br>PAD EVT1 | PARC<br>PCDATA1 |                  | LCDCA<br>SEG25 | CATB<br>SENSE25 |

| 81  | G9       | 81  | G9         | PC26 | 90   | LCDB   | USART1<br>RXD | EIC<br>EXTINT3 | PEVC<br>PAD EVT2 | PARC<br>PCDATA2 | SCIF<br>GCLK0    | LCDCA<br>SEG26 | CATB<br>SENSE26 |

| 82  | F6       | 82  | F6         | PC27 | 91   | LCDB   | USART1<br>TXD | EIC<br>EXTINT4 | PEVC<br>PAD EVT3 | PARC<br>PCDATA3 | SCIF<br>GCLK1    | LCDCA<br>SEG27 | CATB<br>SENSE27 |

| 83  | G10      | 83  | G10        | PC28 | 92   | LCDB   | USART3<br>RXD | SPI<br>MISO    | GLOC<br>IN4      | PARC<br>PCDATA4 | SCIF<br>GCLK2    | LCDCA<br>SEG28 | CATB<br>SENSE28 |

| 84  | F7       | 84  | F7         | PC29 | 93   | LCDB   | USART3<br>TXD | SPI<br>MOSI    | GLOC<br>IN5      | PARC<br>PCDATA5 | SCIF<br>GCLK3    | LCDCA<br>SEG29 | CATB<br>SENSE29 |

| 85  | F8       | 85  | F8         | PC30 | 94   | LCDB   | USART3<br>RTS | SPI<br>SCK     | GLOC<br>IN6      | PARC<br>PCDATA6 | SCIF<br>GCLK IN0 | LCDCA<br>SEG30 | CATB<br>SENSE30 |

| 86  | F9       | 86  | F9         | PC31 | 95   | LCDB   | USART3<br>CLK | SPI<br>NPCS0   | GLOC<br>OUT1     | PARC<br>PCDATA7 | SCIF<br>GCLK IN1 | LCDCA<br>SEG31 | CATB<br>SENSE31 |

Table 3-2.

64-pin GPIO Controller Function Multiplexing (Sheet 1 of 3)

| ATSAM4LC | ATSAM4LS | Pin  | GPIO | Supply |               |              | G | PIO Functio | ns |   |             |

|----------|----------|------|------|--------|---------------|--------------|---|-------------|----|---|-------------|

| QFP      | QFP      |      | •    | S      |               |              |   |             |    |   |             |

| QFN      | QFN      |      |      |        | Α             | В            | С | D           | E  | F | G           |

| 1        | 1        | PA00 | 0    | VDDIO  |               |              |   |             |    |   |             |

| 2        | 2        | PA01 | 1    | VDDIO  |               |              |   |             |    |   |             |

| 3        | 3        | PA02 | 2    | VDDIN  | SCIF<br>GCLK0 | SPI<br>NPCS0 |   |             |    |   | CATB<br>DIS |

| 10       | 10       | PA03 | 3    | VDDIN  |               | SPI<br>MISO  |   |             |    |   |             |

| ATSAM4LC | ATSAM4LS | Pin  | GPIO | Supply |               |              | GI               | PIO Functio | ns               |                |                |

|----------|----------|------|------|--------|---------------|--------------|------------------|-------------|------------------|----------------|----------------|

| WLCSP    | WLCSP    |      |      |        | Α             | В            | С                | D           | E                | F              | G              |

| E5       | E5       | PB13 | 45   | LCDC   | USART0<br>CLK | SPI<br>NPCS1 | PEVC<br>PAD EVT1 | TC0<br>CLK0 | SCIF<br>GCLK3    | LCDCA<br>SEG33 | CATB<br>SENSE0 |

| F4       | F4       | PB14 | 46   | LCDC   | USART0<br>RXD | SPI<br>MISO  | TWIM3<br>TWD     | TC0<br>CLK1 | SCIF<br>GCLK IN0 | LCDCA<br>SEG36 | CATB<br>SENSE1 |

| H4       | H4       | PB15 | 47   | LCDC   | USART0<br>TXD | SPI<br>MOSI  | TWIM3<br>TWCK    | TC0<br>CLK2 | SCIF<br>GCLK IN1 | LCDCA<br>SEG37 | CATB<br>SENSE2 |

Table 3-3.

64-pin GPIO Controller Function Multiplexing for WLCSP package (Sheet 3 of 3)

# 3.3 Signals Description

The following table gives details on signal names classified by peripheral.

Table 3-8.

Signal Descriptions List (Sheet 1 of 4)

| Signal Name          | Function                                | Туре               | Active<br>Level | Comments |

|----------------------|-----------------------------------------|--------------------|-----------------|----------|

|                      | Audio Bitstream DA                      | C - ABDACB         |                 |          |

| CLK                  | D/A clock output                        | Output             |                 |          |

| DAC1 - DAC0          | D/A bitstream outputs                   | Output             |                 |          |

| DACN1 - DACN0        | D/A inverted bitstream outputs          | Output             |                 |          |

|                      | Analog Comparator Int                   | erface - ACI       | -C              | ·        |

| ACAN1 - ACAN0        | Analog Comparator A negative references | Analog             |                 |          |

| ACAP1 - ACAP0        | Analog Comparator A positive references | Analog             |                 |          |

| ACBN1 - ACBN0        | Analog Comparator B negative references | Analog             |                 |          |

| ACBP1 - ACBP0        | Analog Comparator B positive references | Analog             |                 |          |

|                      | ADC controller interf                   | ace - ADCIFE       |                 |          |

| AD14 - AD0           | Analog inputs                           | Analog             |                 |          |

| ADVREFP              | Positive voltage reference              | Analog             |                 |          |

| TRIGGER              | External trigger                        | Input              |                 |          |

|                      | Backup System Control                   | Interface - B      | SCIF            | 1        |

| XIN32                | 32 kHz Crystal Oscillator Input         | Analog/<br>Digital |                 |          |

| XOUT32               | 32 kHz Crystal Oscillator Output        | Analog             |                 |          |

|                      | Capacitive Touch Mod                    | dule B - CATE      | 3               | 1        |

| DIS                  | Capacitive discharge line               | Output             |                 |          |

| SENSE31 - SENSE0     | Capacitive sense lines                  | I/O                |                 |          |

|                      | DAC Controller                          | - DACC             |                 | 1        |

| DAC external trigger | DAC external trigger                    | Input              |                 |          |

| DAC voltage output   | DAC voltage output                      | Analog             |                 |          |

|                      | Enhanced Debug Port For A               | RM Product         | s - EDP         | 1        |

| TCK/SWCLK            | JTAG / SW Debug Clock                   | Input              |                 |          |

| TDI                  | JTAG Debug Data In                      | Input              |                 |          |

| TDO/TRACESWO         | JTAG Debug Data Out / SW Trace Out      | Output             |                 |          |

| TMS/SWDIO            | JTAG Debug Mode Select / SW Data        | I/O                |                 |          |

|                      | External Interrupt Co                   | ontroller - EIC    | ;               | 1        |

| EXTINT8 - EXTINT0    | External interrupts                     | Input              |                 |          |

|                      | Glue Logic Control                      | ller - GLOC        |                 | 1        |

| IN7 - IN0            | Lookup Tables Inputs                    | Input              |                 |          |

| OUT1 - OUT0          | Lookup Tables Outputs                   | Output             |                 |          |

### 6.2.4 Power-up Sequence

### 6.2.4.1 Maximum Rise Rate

To avoid risk of latch-up, the rise rate of the power supplies must not exceed the values described in Table 9-3 on page 100.

### 6.2.4.2 Minimum Rise Rate

The integrated Power-on Reset (POR33) circuitry monitoring the VDDIN powering supply requires a minimum rise rate for the VDDIN power supply.

See Table 9-3 on page 100 for the minimum rise rate value.

If the application can not ensure that the minimum rise rate condition for the VDDIN power supply is met, the following configuration can be used:

A logic "0" value is applied during power-up on pin RESET\_N until VDDIN rises above 1.6 V.

### 6.3 Startup Considerations

This section summarizes the boot sequence of the ATSAM4L8/L4/L2. The behavior after powerup is controlled by the Power Manager. For specific details, refer to Section 9. "Power Manager (PM)" on page 677.

### 6.3.1 Starting of Clocks

After power-up, the device will be held in a reset state by the power-up circuitry for a short time to allow the power to stabilize throughout the device. After reset, the device will use the System RC Oscillator (RCSYS) as clock source. Refer to Section 9. "Electrical Characteristics" on page 99 for the frequency for this oscillator.

On system start-up, the DFLL and the PLLs are disabled. Only the necessary clocks are active allowing software execution. Refer to Section 3-6 "Maskable Module Clocks in AT32UC3B." on page 24 to know the list of peripheral clock running.. No clocks have a divided frequency; all parts of the system receive a clock with the same frequency as the System RC Oscillator.

### 6.3.2 Fetching of Initial Instructions

After reset has been released, the Cortex M4 CPU starts fetching PC and SP values from the reset address, which is 0x00000000. Refer to the ARM Architecture Reference Manual for more information on CPU startup. This address points to the first address in the internal Flash.

The code read from the internal flash is free to configure the clock system and clock sources.

### 6.4 Power-on-Reset, Brownout and Supply Monitor

The SAM4L embeds four features to monitor, warm, and/or reset the device:

- POR33: Power-on-Reset on VDDANA

- BOD33: Brownout detector on VDDANA

- POR18: Power-on-Reset on VDDCORE

- BOD18: Brownout detector on VDDCORE

Atmel

53

### 7.1.3 BACKUP Mode

The BACKUP mode allows achieving the lowest power consumption possible in a system which is performing periodic wake-ups to perform tasks but not requiring fast startup time.

The Core domain is powered-off. The internal SRAM and register contents of the Core domain are lost. The Backup domain is kept powered-on. The 32kHz clock (RC32K or OSC32K) is kept running if enabled to feed modules that require clocking.

In BACKUP mode, the configuration of the I/O lines is preserved. Refer to Section 9. "Backup Power Manager (BPM)" on page 677 to have more details.

### 7.1.3.1 Entering BACKUP Mode

The Backup mode is entered by using the WFI instruction with the following settings:

- set the SCR.SLEEPDEEP bit to 1. (See the Power Management section in the ARM Cortex-M4 Processor chapter).

- set the BPM.PSAVE.BKUP bit to 1.

### 7.1.3.2 Exiting BACKUP Mode

Exit from BACKUP mode happens if a reset occurs or if an enabled wake up event occurs.

The reset sources are:

- BOD33 reset

- BOD18 reset

- WDT reset

- External reset in RESET\_N pin

The wake up sources are:

- EIC lines (level transition only)

- BOD33 interrupt

- BOD18 interrupt

- AST alarm, periodic, overflow

- WDT interrupt

The RC32K or OSC32K should be used as clock source for modules if required. The PMCON.CK32S is used to select one of these two 32kHz clock sources.

Exiting the BACKUP mode is triggered by:

- a reset source: an internal reset sequence is performed according to the reset source. Once VDDCORE is stable and has the correct value according to RUN0 mode, the internal reset is released and program execution starts. The corresponding reset source is flagged in the Reset Cause register (RCAUSE) of the PM.

- a wake up source: the Backup domain is not reset. An internal reset is generated to the Core domain, and the system switches back to the previous RUN mode. Once VDDCORE is stable and has the correct value, the internal reset in the Core domain is released and program execution starts. The BKUP bit is set in the Reset Cause register (RCAUSE) of the PM. It allows the user to discriminate between the reset cause and a wake up cause from the BACKUP mode. The wake up cause can be found in the Backup Wake up Cause register (BPM.BKUPWCAUSE).

### 7.1.5 Power Save Mode Summary Table

The following table shows a summary of the main Power Save modes:

Table 7-2.

Power Save mode Configuration Summary

| Mode      | Mode Entry                                                                      | Wake up sources                                                                                                                                         | Core<br>domain                                                                                                   | Backup<br>domain                                                                          |

|-----------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| SLEEP     | WFI<br>SCR.SLEEPDEEP bit = 0<br>BPM.PMCON.BKUP bit = 0                          | Any interrupt                                                                                                                                           | CPU clock OFF<br>Other clocks OFF depending<br>on the BPM.PMCON.SLEEP<br>field<br>see "SLEEP mode" on page<br>56 | Clocks OFF depending on<br>the BPM.PMCON.SLEEP<br>field<br>see "SLEEP mode" on page<br>56 |

| WAIT      | WFI<br>SCR.SLEEPDEEP bit = 1<br>BPM.PMCON.RET bit = 0<br>BPM.PMCON.BKUP bit = 0 | PM WAKE interrupt                                                                                                                                       | All clocks are OFF<br>Core domain is retained                                                                    | All clocks are OFF except<br>RC32K or OSC32K if<br>running                                |

| RETENTION | WFI<br>SCR.SLEEPDEEP bit = 1<br>BPM.PMCON.RET bit = 1<br>BPM.PMCON.BKUP bit = 0 | PM WAKE interrupt                                                                                                                                       | All clocks are OFF<br>Core domain is retained                                                                    | All clocks are OFF except<br>RC32K or OSC32K if<br>running                                |

| BACKUP    | WFI<br>+ SCR.SLEEPDEEP bit = 1<br>+ BPM.PMCON.BKUP bit = 1                      | EIC interrupt<br>BOD33, BOD18 interrupt<br>and reset<br>AST alarm, periodic,<br>overflow<br>WDT interrupt and reset<br>external reset on RESET_N<br>pin | OFF (not powered)                                                                                                | All clocks are OFF except<br>RC32K or OSC32K if<br>running                                |

## 7.2 Power Scaling

The Power Scaling technique consists of adjusting the internal regulator output voltage (voltage scaling) to reduce the power consumption. According to the requirements in terms of performance, operating modes, and current consumption, the user can select the Power Scaling configuration that fits the best with its application.

The Power Scaling configuration field (PMCON.PS) is provided in the Backup Power Manager (BPM) module.

In RUN mode, the user can adjust on the fly the Power Scaling configuration

The Figure 7.1 summarizes the different combination of the Power Scaling configuration which can be applied according to the Power Save Mode.

Power scaling from a current power configuration to a new power configuration is done by halting the CPU execution

Power scaling occurs after a WFI instruction. The system is halted until the new power configuration is stabilized. After handling the PM interrupt, the system resumes from WFI.

To scale the power, the following sequence is required:

• Check the BPM.SR.PSOK bit to make sure the current power configuration is stabilized.

### 8.7.5 Product Dependencies

### 8.7.5.1 I/O Lines

The TCK pin is dedicated to the EDP. The other debug port pins default after reset to their GPIO functionality and are automatically reassigned to the JTAG functionalities on detection of a debugger. In serial wire mode, TDI and TDO can be used as GPIO functions. Note that in serial wire mode TDO can be used as a single pin trace output.

### 8.7.5.2 Power Management

When a debugger is present, the connection is kept alive allowing debug operations. As a side effect, the power is never turned off. The hot plugging functionality is always available except when the system is in BACKUP Power Save Mode.

### 8.7.5.3 Clocks

The SWJ-DP uses the external TCK pin as its clock source. This clock must be provided by the external JTAG master device.

Some of the JTAG Instructions are used to access an Access Port (SMAP or AHB-AP). These instructions require the CPU clock to be running.

If the CPU clock is not present because the CPU is in a Power Save Mode where this clock is not provided, the Power Manager(PM) will automatically restore the CPU clock on detection of a debug access.

The RCSYS clock is used as CPU clock when the external reset is applied to ensure correct Access Port operations.

### 8.7.6 Module Initialization

This module is enabled as soon as a TCK falling edge is detected when RESET\_N is not asserted (refer to Section 8.7.7 below). Moreover, the module is synchronously reseted as long as the TAP machine is in the TEST\_LOGIC\_RESET (TLR) state. It is advised asserting TMS at least 5 TCK clock periods after the debugger has been detected to ensure the module is in the TLR state prior to any operation. This module also has the ability to maintain the Cortex-M4 under reset (refer to the Section 8.7.8 "SMAP Core Reset Request Source" on page 70).

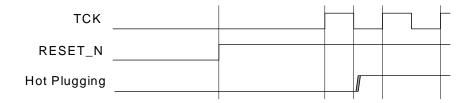

### 8.7.7 Debugger Hot Plugging

The TCK pin is dedicated to the EDP. After reset has been released, the EDP detects that a debugger has been attached when a TCK falling edge arises.

Figure 8-4. Debugger Hot Plugging Detection Timings Diagram

### 8.7.12 JTAG Instructions Summary

The implemented JTAG instructions are shown in the table below.

|                      |                | Implemented JTAG Instructions list                                                        |                                   |                          |

|----------------------|----------------|-------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|

| IR instruction value | Instruction    | Description                                                                               | availability<br>when<br>protected | Component                |

| b0000                | EXTEST         | Select boundary-scan chain as data register for testing circuitry external to the device. | yes                               |                          |

| b0001                | SAMPLE_PRELOAD | Take a snapshot of external pin values without affecting system operation.                | yes                               |                          |

| b0100                | INTEST         | Select boundary-scan chain for internal testing of the device.                            | yes                               |                          |

| b0101                | CLAMP          | Bypass device through Bypass register, while driving outputs from boundary-scan register. | yes                               | BSCAN-TAP                |

| b1000                | ABORT          | ARM JTAG-DP Instruction                                                                   | yes                               |                          |

| b1010                | DPACC          | ARM JTAG-DP Instruction                                                                   | yes                               |                          |

| b1011                | APACC          | ARM JTAG-DP Instruction                                                                   | yes                               |                          |

| b1100                | -              | Reserved                                                                                  | yes                               | SWJ-DP<br>(in JTAG mode) |

| b1101                | -              | Reserved                                                                                  | yes                               |                          |

| b1110                | IDCODE         | ARM JTAG-DP Instruction                                                                   | yes                               |                          |

| b1111                | BYPASS         | Bypass this device through the bypass register.                                           | yes                               |                          |

Table 8-2.

Implemented JTAG instructions list

# ATSAM4L8/L4/L2

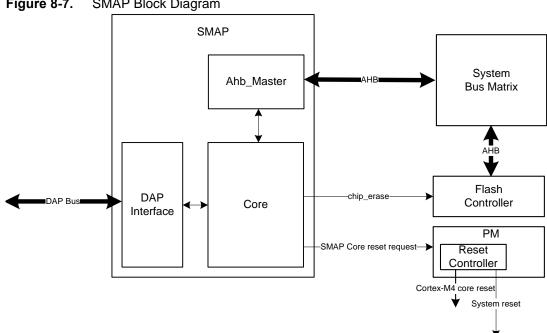

#### 8.9 System Manager Access Port (SMAP)

Rev.: 1.0.0.0

#### 8.9.1 **Features**

- Chip Erase command and status

- Cortex-M4 core reset source

- 32-bit Cyclic Redundancy check of any memory accessible through the bus matrix

- Unlimited Flash User page read access

- Chip identification register

#### 8.9.2 **Overview**

The SMAP provides memory-related services and also Cortex-M4 core reset control to a debugger through the Debug Port. This makes possible to halt the CPU and program the device after reset.

#### 8.9.3 **Block Diagram**

#### SMAP Block Diagram Figure 8-7.

#### 8.9.4 Initializing the Module

The SMAP can be accessed only if the CPU clock is running and the SWJ-DP has been activated by issuing a CDBGPWRUP request. For more details, refer to the ARM Debug Interface v5.1 Architecture Specification.

Then it must be enabled by writing a one to the EN bit of the CR register (CR.EN) before writing or reading other registers. If the SMAP is not enabled it will discard any read or write operation.

#### Stopping the Module 8.9.5

To stop the module, the user must write a one to the DIS bit of the CR register (CR.DIS). All the user interface and internal registers will be cleared and the internal clock will be stopped.

| 8.9.11.1    | Control Register |

|-------------|------------------|

| Name:       | CR               |

| Access Typ  | e: Write-Only    |

| Offset:     | 0x00             |

| Reset Value | e: 0x0000000     |

| 31 | 30 | 29 | 28 | 27   | 26  | 25  | 24 |

|----|----|----|----|------|-----|-----|----|

| -  | -  | -  | -  | -    | -   | -   | -  |

|    |    |    |    |      |     |     |    |

| 23 | 22 | 21 | 20 | 19   | 18  | 17  | 16 |

| -  | -  | -  | -  | -    | -   | -   | -  |

|    |    |    |    |      |     |     |    |

| 15 | 14 | 13 | 12 | 11   | 10  | 9   | 8  |

| -  | -  | -  | -  | -    | -   | -   | -  |

|    |    |    |    |      |     |     |    |

| 7  | 6  | 5  | 4  | 3    | 2   | 1   | 0  |

| -  | -  | -  | CE | FSPR | CRC | DIS | EN |

Writing a zero to a bit in this register has no effect.

### • CE: Chip Erase

Writing a one to this bit triggers the FLASH Erase All (EA) operation which clears all volatile memories, the whole flash array, the general purpose fuses and the protected state. The Status register DONE field indicates the completion of the operation. Reading this bit always returns 0

### • FSPR: Flash User Page Read

Writing a one to this bit triggers a read operation in the User page. The word pointed by the ADDR register in the page is read and written to the DATA register. ADDR is post incremented allowing a burst of reads without modifying ADDR. SR.DONE must be read high prior to reading the DATA register.

Reading this bit always returns 0

### CRC: Cyclic Redundancy Code

Writing a one triggers a CRC calculation over a memory area defined by the ADDR and LENGTH registers. Reading this bit always returns 0

Note: This feature is restricted while in protected state

### DIS: Disable

Writing a one to this bit disables the module. Disabling the module resets the whole module immediately.

Atmel

### • EN: Enable

Writing a one to this bit enables the module.

instruction for the first time. SAMPLE/PRELOAD can also be used for taking a snapshot of the external pins during normal operation of the part.

When using the JTAG interface for Boundary-Scan, the JTAG TCK clock is independent of the internal chip clock, which is not required to run.

**NOTE:** For pins connected to 5V lines care should be taken to not drive the pins to a logic one using boundary scan, as this will create a current flowing from the 3,3V driver to the 5V pullup on the line. Optionally a series resistor can be added between the line and the pin to reduce the current.

### 8.11.7 Flash Programming typical procedure

Flash programming is performed by operating Flash controller commands. The Flash controller is connected to the system bus matrix and is then controllable from the AHP-AP. The AHB-AP cannot write the FLASH page buffer while the core\_hold\_reset is asserted. The AHB-AP cannot be accessed when the device is in protected state. It is important to ensure that the CPU is halted prior to operating any flash programming operation to prevent it from corrupting the system configuration. The recommended sequence is shown below:

- 1. At power up, RESET\_N is driven low by a debugger. The on-chip regulator holds the system in a POR state until the input supply is above the POR threshold. The system continues to be held in this static state until the internally regulated supplies have reached a safe operating.

- 2. PM starts, clocks are switched to the slow clock (Core Clock, System Clock, Flash Clock, and any Bus Clocks that do not have clock gate control). Internal resets are maintained due to the external reset.

- The Debug Port (DP) and Access Ports (AP) receives a clock and leave the reset state,

- 3. The debugger maintains a low level on TCK and release RESET\_N.

- The SMAP asserts the core\_hold\_reset signal

- 4. The Cortex-M4 core remains in reset state, meanwhile the rest of the system is released.

- 5. The debugger then configures the NVIC to catch the Cortex-M4 core reset vector fetch. For more information on how to program the NVIC, refer to the ARMv7-M Architecture Reference Manual.

- 6. The debugger writes a one in the SMAP SCR.HCR to release the Cortex-M4 core reset to make the system bus matrix accessible from the AHB-AP.

- 7. The Cortex-M4 core initializes the SP, then read the exception vector and stalls

- 8. Programming is available through the AHB-AP

Atmel

9. After operation is completed, the chip can be restarted either by asserting RESET\_N or switching power off/on or clearing SCR.HCR. Make sure that the TCK pin is high when releasing RESET\_N not to halt the core.

### 8.11.8 Chip erase typical procedure

The chip erase operation is triggered by writing a one in the CE bit in the Control Register (CR.CE). This clears first all volatile memories in the system and second the whole flash array. Note that the User page is not erased in this process. To ensure that the chip erase operation is completed, check the DONE bit in the Status Register (SR.DONE). Also note that the chip erase operation depends on clocks and power management features that can be altered by the CPU. It is important to ensure that it is stopped. The recommended sequence is shown below:

- 1. At power up, RESET\_N is driven low by a debugger. The on-chip regulator holds the system in a POR state until the input supply is above the POR threshold. The system continues to be held in this static state until the internally regulated supplies have reached a safe operating.

- PM starts, clocks are switched to the slow clock (Core Clock, System Clock, Flash Clock, and any Bus Clocks that do not have clock gate control). Internal resets are maintained due to the external reset.

- The debug port and access ports receives a clock and leave the reset state

- 3. The debugger maintains a low level on TCK and release RESET\_N.

- The SMAP asserts the core\_hold\_reset signal

- 4. The Cortex-M4 core remains in reset state, meanwhile the rest of the system is released.

- 5. The Chip erase operation can be performed by issuing the SMAP Chip Erase command. In this case:

- volatile memories are cleared first

- followed by the clearing of the flash array

- followed by the clearing of the protected state

Atmel

After operation is completed, the chip must be restarted by either controling RESET\_N or switching power off/on. Make sure that the TCK pin is high when releasing RESET\_N not to halt the core.

### 8.11.9 Setting the protected state

This is done by issuing a specific flash controller command, for more information, refer to the Flash Controller chapter and to section 8.11.7Flash Programming typical procedure97. The protected state is defined by a highly secure Flash builtin mechanism. Note that for this programmation to propagate, it is required to reset the chip.

| Peripheral            | Typ Consumption Active | Unit   |

|-----------------------|------------------------|--------|

| IISC                  | 1.0                    |        |

| SPI                   | 1.9                    |        |

| тс                    | 6.3                    |        |

| TWIM                  | 1.5                    |        |

| TWIS                  | 1.2                    |        |

| USART                 | 8.5                    |        |

| ADCIFE <sup>(2)</sup> | 3.1                    |        |

| DACC                  | 1.3                    |        |

| ACIFC <sup>(2)</sup>  | 3.1                    |        |

| GLOC                  | 0.4                    |        |

| ABDACB                | 0.7                    |        |

| TRNG                  | 0.9                    |        |

| PARC                  | 0.7                    |        |

| CATB                  | 3.0                    |        |

| LCDCA                 | 4.4                    | µA/MHz |

| PDCA                  | 1.0                    |        |

| CRCCU                 | 0.3                    |        |

| USBC                  | 1.5                    |        |

| PEVC                  | 5.6                    |        |

| CHIPID                | 0.1                    |        |

| SCIF                  | 6.4                    |        |

| FREQM                 | 0.5                    |        |

| GPIO                  | 7.1                    |        |

| BPM                   | 0.9                    |        |

| BSCIF                 | 4.6                    |        |

| AST                   | 1.5                    |        |

| WDT                   | 1.4                    |        |

| EIC                   | 0.6                    |        |

| PICOUART              | 0.3                    |        |

Table 9-11.

Typical Current Consumption by Peripheral in Power Scaling Mode 0 and 2<sup>(1)</sup>

1. These numbers are valid for the measured condition only and must not be extrapolated to other frequencies

2. Includes the current consumption on VDDANA and ADVREFP.

### 9.5.4 .Peripheral Power Consumption in Power Scaling mode 1

The values in Table 9-13 are measured values of power consumption under the following conditions:

### 9.9.4 Analog- to Digital Converter Characteristics

| Table 9-45. C | perating conditions |

|---------------|---------------------|

|---------------|---------------------|

| Symbol                  | Parameter                                       | Conditions                                             | Min  | Тур | Max    | Units  |  |

|-------------------------|-------------------------------------------------|--------------------------------------------------------|------|-----|--------|--------|--|

|                         | Temperature range                               |                                                        | -40  |     | +85    | °C     |  |

|                         | Resolution <sup>(1)</sup>                       | Мах                                                    |      | 12  | 12 (2) | Bit    |  |

|                         | Sampling clock <sup>(3)</sup>                   | Differential modes, Gain=1X                            | 5    |     | 300    |        |  |

|                         |                                                 | Unipolar modes, Gain=1X                                | 5    |     | 250    | - kHz  |  |

| f <sub>ADC</sub>        | ADC clock frequency <sup>(3)</sup>              | Differential modes                                     | 0.03 |     | 1.8    | - MHz  |  |

|                         | ADC Clock frequency                             | Unipolar modes                                         | 0.03 |     | 1.5    |        |  |

| т                       | Compliant time (3)                              | Differential modes                                     | 16.5 |     | 277    |        |  |

| T <sub>SAMPLEHOLD</sub> | Sampling time <sup>(3)</sup>                    | Unipolar modes                                         | 16.5 |     | 333    | μs     |  |

|                         | Conversion rate <sup>(1)</sup>                  | 1X gain, differential                                  |      |     | 300    | kSps   |  |

|                         | Internal channel conversion rate <sup>(3)</sup> | V <sub>VDD</sub> /10, Bandgap and Temperature channels |      |     | 125    | kSps   |  |

|                         |                                                 | 1X gain, (resolution/2)+gain <sup>(4)</sup>            |      |     | 6      |        |  |

|                         | Conversion time (latency)                       | 2X and 4X gain                                         |      |     | 7      | _      |  |

|                         |                                                 | 8X and 16X gain                                        |      |     | 8      | Cycles |  |

|                         |                                                 | 32X and 64X gain                                       |      |     | 9      | 1      |  |

|                         |                                                 | 64X gain and unipolar                                  |      |     | 10     | 1      |  |

1. These values are based on characterization. These values are not covered by test limits in production

2. Single ended or using divide by two max resolution: 11 bits

3. These values are based on simulation. These values are not covered by test limits in production

4. See Figure 9-5

Table 9-50. Analog Comparator Characteristics

| Symbol               | Parameter                                  | Conditions                                                                           | Min | Тур | Max  | Units |  |

|----------------------|--------------------------------------------|--------------------------------------------------------------------------------------|-----|-----|------|-------|--|

|                      | Hysteresis <sup>(1)</sup>                  | $V_{ACREFN}$ =0.1V to VDDIO-0.1V,<br>hysteresis = 1 <sup>(2)</sup><br>Fast mode      | 10  |     | 55   | mV    |  |

|                      |                                            | $V_{ACREFN}$ =0.1V to VDDIO-0.1V,<br>hysteresis = 1 <sup>(2)</sup><br>Low power mode | 10  |     | 68   | mV    |  |

|                      |                                            | $V_{ACREFN} = 0.1V$ to VDDIO-0.1V,<br>hysteresis = $2^{(2)}$<br>Fast mode            | 26  |     | 83   | mV    |  |

|                      |                                            | $V_{ACREFN} = 0.1V$ to VDDIO-0.1V,<br>hysteresis = $2^{(2)}$<br>Low power mode       | 19  |     | 91   | mV    |  |

|                      |                                            | $V_{ACREFN}$ =0.1V to VDDIO-0.1V,<br>hysteresis = 3 <sup>(2)</sup><br>Fast mode      | 43  |     | 106  | mV    |  |

|                      |                                            | $V_{ACREFN} = 0.1V$ to VDDIO-0.1V,<br>hysteresis = $3^{(2)}$<br>Low power mode       | 32  |     | 136  | mV    |  |

|                      | Propagation delay <sup>(1)</sup>           | Changes for V <sub>ACM</sub> =VDDIO/2<br>100mV Overdrive<br>Fast mode                |     |     | 67   | ns    |  |

|                      | Fropagation delay                          | Changes for V <sub>ACM</sub> =VDDIO/2<br>100mV Overdrive<br>Low power mode           |     |     | 315  | ns    |  |

| t <sub>startup</sub> | Startup time <sup>(1)</sup>                | Enable to ready delay<br>Fast mode                                                   |     |     | 1.19 | μs    |  |

|                      |                                            | Enable to ready delay<br>Low power mode                                              |     |     | 3.61 | μs    |  |

| I <sub>AC</sub>      | Channel current consumption <sup>(3)</sup> | Low power mode, no hysteresis                                                        |     | 4.9 | 8.7  | μΑ    |  |

|                      |                                            | Fast mode, no hysteresis                                                             |     | 63  | 127  |       |  |

1. These values are based on characterization. These values are not covered by test limits in production

2. HYSTAC.CONFn.HYS field, refer to the Analog Comparator Interface chapter

3. These values are based on simulation. These values are not covered by test limits in production or characterization

- Atmel

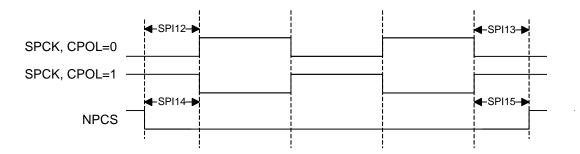

Figure 9-16. SPI Slave Mode, NPCS Timing

Table 9-63. SPI Timing, Slave Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions                                                                              | Min | Max | Units |

|--------|-----------------------------------|-----------------------------------------------------------------------------------------|-----|-----|-------|

| SPI6   | SPCK falling to MISO delay        |                                                                                         | 19  | 47  |       |

| SPI7   | MOSI setup time before SPCK rises | V <sub>VDDIO</sub> from<br>2.85V to 3.6V,<br>maximum<br>external<br>capacitor =<br>40pF | 0   |     |       |

| SPI8   | MOSI hold time after SPCK rises   |                                                                                         | 5.4 |     |       |

| SPI9   | SPCK rising to MISO delay         |                                                                                         | 19  | 46  |       |

| SPI10  | MOSI setup time before SPCK falls |                                                                                         | 0   |     |       |

| SPI11  | MOSI hold time after SPCK falls   |                                                                                         | 5.3 |     | ns    |

| SPI12  | NPCS setup time before SPCK rises |                                                                                         | 4   |     |       |

| SPI13  | NPCS hold time after SPCK falls   |                                                                                         | 2.5 |     |       |

| SPI14  | NPCS setup time before SPCK falls |                                                                                         | 6   |     |       |

| SPI15  | NPCS hold time after SPCK rises   |                                                                                         | 1.1 |     |       |

Note: 1. These values are based on simulation. These values are not covered by test limits in production.

### Maximum SPI Frequency, Slave Input Mode

The maximum SPI slave input frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{CLKSPI}, \frac{1}{SPIn})$$

Where *SPIn* is the MOSI setup and hold time, SPI7 + SPI8 or SPI10 + SPI11 depending on CPOL and NCPHA. $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

### Maximum SPI Frequency, Slave Output Mode

The maximum SPI slave output frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{PINMAX}, \frac{1}{SPIn + t_{SETUP}})$$

# 12. Errata

# 12.1 ATSAM4L4 /2 Rev. B & ATSAM4L8 Rev. A

| 12.1.1 | General |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |         | <ul> <li>PS2 mode is not supported by Engineering Samples</li> <li>PS2 mode support is supported only by parts with calibration version higher than 0.</li> <li>Fix/Workaround</li> <li>The calibration version can be checked by reading a 32-bit word at address 0x0080020C.</li> <li>The calibration version bitfield is 4-bit wide and located from bit 4 to bit 7 in this word. Any value higher than 0 ensures that the part supports the PS2 mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 12.1.2 | SCIF    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |         | <ul> <li>PLLCOUNT value larger than zero can cause PLLEN glitch         Initializing the PLLCOUNT with a value greater than zero creates a glitch on the PLLEN signal during asynchronous wake up.         Fix/Workaround         The lock-masking mechanism for the PLL should not be used.         The PLLCOUNT field of the PLL Control Register should always be written to zero.     </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12.1.3 | WDT     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |         | WDT Control Register does not have synchronization feedback<br>When writing to the Timeout Prescale Select (PSEL), Time Ban Prescale Select (TBAN),<br>Enable (EN), or WDT Mode (MODE) fieldss of the WDT Control Register (CTRL), a synchro-<br>nizer is started to propagate the values to the WDT clook domain. This synchronization<br>takes a finite amount of time, but only the status of the synchronization of the EN bit is<br>reflected back to the user. Writing to the synchronized fields during synchronization can lead<br>to undefined behavior.<br><b>Fix/Workaround</b><br>-When writing to the affected fields, the user must ensure a wait corresponding to 2 clock<br>cycles of both the WDT peripheral bus clock and the selected WDT clock source.<br>-When doing writes that changes the EN bit, the EN bit can be read back until it reflects the<br>written value. |

| 12.1.4 | SPI     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |         | SPI data transfer hangs with CSR0.CSAAT==1 and MR.MODFDIS==0<br>When CSR0.CSAAT==1 and mode fault detection is enabled (MR.MODFDIS==0), the SPI<br>module will not start a data transfer.<br>Fix/Workaround<br>Disable mode fault detection by writing a one to MR.MODFDIS.<br>SPI disable does not work in SLAVE mode<br>SPI disable does not work in SLAVE mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

ATSAM4L8/L4/L2

# 13. Datasheet Revision History

Note that the referring page numbers in this section are referred to this document. The referring revision in this section are referring to the document revision.

# 13.1 Rev. A - 09/12

1. Initial revision.

# 13.2 Rev. B - 10/12

- 1. Fixed ordering code

- 2. Changed BOD18CTRL and BOD33CTRL ACTION field from "Reserved" to 'No action"

# 13.3 Rev. C – 02/13

- 1. Fixed ball pitch for VFBGA100 package

- 2. Added VFBGA100 and WLCSP64 pinouts

- 3. Added Power Scaling Mode 2 for high frequency support

- 4. Minor update on several modules chapters

- 5. Major update on Electrical characteristics

- 6. Updated errata

- 7. Fixed GPIO multiplexing pin numbers

# 13.4 Rev. D - 03/13

- 1. Removed WLCSP package information

- 2. Added errata text for detecting whether a part supports PS2 mode or not

- 3. Removed temperature sensor feature (not supported by production flow)

- 4. Fixed MUX selection on Positive ADC input channel table

- 5. Added information about TWI instances capabilities

- 6. Added some details on errata Corrupted data in flash may happen after flash page write operations.171