# Atmel - ATSAM4LC4AA-AU Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                            |

|----------------------------|-------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                   |

| Core Size                  | 32-Bit Single-Core                                                |

| Speed                      | 48MHz                                                             |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB              |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT |

| Number of I/O              | 27                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                  |

| Program Memory Type        | FLASH                                                             |

| EEPROM Size                | -                                                                 |

| RAM Size                   | 32K x 8                                                           |

| Voltage - Supply (Vcc/Vdd) | 1.68V ~ 3.6V                                                      |

| Data Converters            | A/D 3x12b; D/A 1x10b                                              |

| Oscillator Type            | Internal                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                 |

| Mounting Type              | Surface Mount                                                     |

| Package / Case             | 48-TQFP                                                           |

| Supplier Device Package    | 48-TQFP (7x7)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/atsam4lc4aa-au         |

|                            |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 3-2. 64-pir | GPIO Controller Function Multiplexing (She | et 2 of 3) |

|-------------------|--------------------------------------------|------------|

|-------------------|--------------------------------------------|------------|

|          |          | -    |      |        |                |                 |                  |                 |                   |                |                 |

|----------|----------|------|------|--------|----------------|-----------------|------------------|-----------------|-------------------|----------------|-----------------|

| ATSAM4LC | ATSAM4LS | Pin  | GPIO | Supply | GPIO Functions |                 |                  |                 |                   |                |                 |

| QFP      | QFP      | _    | 0    | ้ร     |                |                 |                  |                 |                   |                |                 |

| QFN      | QFN      |      |      |        | Α              | в               | с                | D               | Е                 | F              | G               |

| 15       | 15       | PA04 | 4    | VDDANA | ADCIFE<br>AD0  | USART0<br>CLK   | EIC<br>EXTINT2   | GLOC<br>IN1     |                   |                | CATB<br>SENSE0  |

| 16       | 16       | PA05 | 5    | VDDANA | ADCIFE<br>AD1  | USART0<br>RXD   | EIC<br>EXTINT3   | GLOC<br>IN2     | ADCIFE<br>TRIGGER |                | CATB<br>SENSE1  |

| 21       | 21       | PA06 | 6    | VDDANA | DACC<br>VOUT   | USART0<br>RTS   | EIC<br>EXTINT1   | GLOC<br>IN0     | ACIFC<br>ACAN0    |                | CATB<br>SENSE2  |

| 22       | 22       | PA07 | 7    | VDDANA | ADCIFE<br>AD2  | USART0<br>TXD   | EIC<br>EXTINT4   | GLOC<br>IN3     | ACIFC<br>ACAP0    |                | CATB<br>SENSE3  |

| 26       | 26       | PA08 | 8    | LCDA   | USART0<br>RTS  | ТС0<br>А0       | PEVC<br>PAD EVT0 | GLOC<br>OUT0    |                   | LCDCA<br>SEG23 | CATB<br>SENSE4  |

| 29       | 29       | PA09 | 9    | LCDA   | USART0<br>CTS  | ТС0<br>В0       | PEVC<br>PAD EVT1 | PARC<br>PCDATA0 |                   | LCDCA<br>COM3  | CATB<br>SENSE5  |

| 30       | 30       | PA10 | 10   | LCDA   | USART0<br>CLK  | TC0<br>A1       | PEVC<br>PAD EVT2 | PARC<br>PCDATA1 |                   | LCDCA<br>COM2  | CATB<br>SENSE6  |

| 31       | 31       | PA11 | 11   | LCDA   | USART0<br>RXD  | TC0<br>B1       | PEVC<br>PAD EVT3 | PARC<br>PCDATA2 |                   | LCDCA<br>COM1  | CATB<br>SENSE7  |

| 32       | 32       | PA12 | 12   | LCDA   | USART0<br>TXD  | TC0<br>A2       |                  | PARC<br>PCDATA3 |                   | LCDCA<br>COM0  | CATB<br>DIS     |

| 40       | 40       | PA13 | 13   | LCDA   | USART1<br>RTS  | TC0<br>B2       | SPI<br>NPCS1     | PARC<br>PCDATA4 |                   | LCDCA<br>SEG5  | CATB<br>SENSE8  |

| 41       | 41       | PA14 | 14   | LCDA   | USART1<br>CLK  | TC0<br>CLK0     | SPI<br>NPCS2     | PARC<br>PCDATA5 |                   | LCDCA<br>SEG6  | CATB<br>SENSE9  |

| 42       | 42       | PA15 | 15   | LCDA   | USART1<br>RXD  | TC0<br>CLK1     | SPI<br>NPCS3     | PARC<br>PCDATA6 |                   | LCDCA<br>SEG7  | CATB<br>SENSE10 |

| 43       | 43       | PA16 | 16   | LCDA   | USART1<br>TXD  | TC0<br>CLK2     | EIC<br>EXTINT1   | PARC<br>PCDATA7 |                   | LCDCA<br>SEG8  | CATB<br>SENSE11 |

| 44       | 44       | PA17 | 17   | LCDA   | USART2<br>RTS  | ABDACB<br>DAC0  | EIC<br>EXTINT2   | PARC<br>PCCK    |                   | LCDCA<br>SEG9  | CATB<br>SENSE12 |

| 49       | 49       | PA18 | 18   | LCDA   | USART2<br>CLK  | ABDACB<br>DACN0 | EIC<br>EXTINT3   | PARC<br>PCEN1   |                   | LCDCA<br>SEG18 | CATB<br>SENSE13 |

| 50       | 50       | PA19 | 19   | LCDA   | USART2<br>RXD  | ABDACB<br>DAC1  | EIC<br>EXTINT4   | PARC<br>PCEN2   | SCIF<br>GCLK0     | LCDCA<br>SEG19 | CATB<br>SENSE14 |

| 51       | 51       | PA20 | 20   | LCDA   | USART2<br>TXD  | ABDACB<br>DACN1 | EIC<br>EXTINT5   | GLOC<br>IN0     | SCIF<br>GCLK1     | LCDCA<br>SEG20 | CATB<br>SENSE15 |

| 55       | 55       | PA21 | 21   | LCDC   | SPI<br>MISO    | USART1<br>CTS   | EIC<br>EXTINT6   | GLOC<br>IN1     | TWIM2<br>TWD      | LCDCA<br>SEG34 | CATB<br>SENSE16 |

| 56       | 56       | PA22 | 22   | LCDC   | SPI<br>MOSI    | USART2<br>CTS   | EIC<br>EXTINT7   | GLOC<br>IN2     | TWIM2<br>TWCK     | LCDCA<br>SEG35 | CATB<br>SENSE17 |

| 59       | 59       | PA23 | 23   | LCDC   | SPI<br>SCK     | TWIMS0<br>TWD   | EIC<br>EXTINT8   | GLOC<br>IN3     | SCIF<br>GCLK IN0  | LCDCA<br>SEG38 | CATB<br>DIS     |

| 60       | 60       | PA24 | 24   | LCDC   | SPI<br>NPCS0   | TWIMS0<br>TWCK  |                  | GLOC<br>OUT0    | SCIF<br>GCLK IN1  | LCDCA<br>SEG39 | CATB<br>SENSE18 |

| 62       | 62       | PA25 | 25   | VDDIO  | USBC<br>DM     | USART2<br>RXD   |                  |                 |                   |                | CATB<br>SENSE19 |

| 63       | 63       | PA26 | 26   | VDDIO  | USBC<br>DP     | USART2<br>TXD   |                  |                 |                   |                | CATB<br>SENSE20 |

#### **Table 3-8.**Signal Descriptions List (Sheet 4 of 4)

| Signal Name | Function                           | Туре | Active<br>Level | Comments |

|-------------|------------------------------------|------|-----------------|----------|

| PA31 - PA00 | Parallel I/O Controller I/O Port A | I/O  |                 |          |

| PB15 - PB00 | Parallel I/O Controller I/O Port B | I/O  |                 |          |

| PC31 - PC00 | Parallel I/O Controller I/O Port C | I/O  |                 |          |

Note: 1. See "Power and Startup Considerations" section.

# 3.4 I/O Line Considerations

#### 3.4.1 SW/JTAG Pins

The JTAG pins switch to the JTAG functions if a rising edge is detected on TCK low after the RESET\_N pin has been released. The TMS, and TDI pins have pull-up resistors when used as JTAG pins. The TCK pin always has pull-up enabled during reset. The JTAG pins can be used as GPIO pins and multiplexed with peripherals when the JTAG is disabled. Refer to Section 3.2.3 "JTAG Port Connections" on page 29 for the JTAG port connections.

For more details, refer to Section 1.1 "Enhanced Debug Port (EDP)" on page 3.

## 3.4.2 RESET\_N Pin

The RESET\_N pin is a schmitt input and integrates a permanent pull-up resistor to VDDIN. As the product integrates a power-on reset detector, the RESET\_N pin can be left unconnected in case no reset from the system needs to be applied to the product.

#### 3.4.3 TWI Pins

When these pins are used for TWI, the pins are open-drain outputs with slew-rate limitation andinputs with inputs with spike-filtering. When used as GPIO-pins or used for other peripherals, the pins have the same characteristics as GPIO pins.

#### 3.4.4 GPIO Pins

All the I/O lines integrate a pull-up/pull-down resistor and slew rate controller. Programming these features is performed independently for each I/O line through the GPIO Controllers. After reset, I/O lines default as inputs with pull-up and pull-down resistors disabled and slew rate enabled.

#### 3.4.5 High-drive Pins

The six pins PA02, PB00, PB01, PC04, PC05 and PC06 have high-drive output capabilities. Refer to Section 9.6.2 "High-drive I/O Pin : PA02, PC04, PC05, PC06" on page 115 for electrical characteristics.

#### 3.4.6 USB Pins

When these pins are used for USB, the pins are behaving according to the USB specification. When used as GPIO pins or used for other peripherals, the pins have the same behavior as other normal I/O pins, but the characteristics are different. Refer to Section 9.6.3 "USB I/O Pin : PA25, PA26" on page 116 for electrical characteristics.

These pins are compliant to USB standard only when VDDIO power supply is 3.3V nominal.

# 4.6 Cortex-M4 implementations options

This table provides the specific configuration options implemented in the SAM4L series

| Option                   | Implementation     |

|--------------------------|--------------------|

| Inclusion of MPU         | yes                |

| Inclusion of FPU         | No                 |

| Number of interrupts     | 80                 |

| Number of priority bits  | 4                  |

| Inclusion of the WIC     | No                 |

| Embedded Trace Macrocell | No                 |

| Sleep mode instruction   | Only WFI supported |

| Endianness               | Little Endian      |

| Bit-banding              | No                 |

| SysTick timer            | Yes                |

| Register reset values    | No                 |

Table 4-1.

Cortex-M4 implementation options

# 4.7 Cortex-M4 Interrupts map

The table below shows how the interrupt request signals are connected to the NVIC.

|      | internape requeet eignal map (encet i ei |         |  |  |  |  |

|------|------------------------------------------|---------|--|--|--|--|

| Line | Module                                   | Signal  |  |  |  |  |

| 0    | Flash Controller                         | HFLASHC |  |  |  |  |

| 1    | Peripheral DMA Controller                | PDCA 0  |  |  |  |  |

| 2    | Peripheral DMA Controller                | PDCA 1  |  |  |  |  |

| 3    | Peripheral DMA Controller                | PDCA 2  |  |  |  |  |

| 4    | Peripheral DMA Controller                | PDCA 3  |  |  |  |  |

| 5    | Peripheral DMA Controller                | PDCA 4  |  |  |  |  |

| 6    | Peripheral DMA Controller                | PDCA 5  |  |  |  |  |

| 7    | Peripheral DMA Controller                | PDCA 6  |  |  |  |  |

| 8    | Peripheral DMA Controller                | PDCA 7  |  |  |  |  |

| 9    | Peripheral DMA Controller                | PDCA 8  |  |  |  |  |

| 10   | Peripheral DMA Controller                | PDCA 9  |  |  |  |  |

| 11   | Peripheral DMA Controller                | PDCA 10 |  |  |  |  |

**Table 4-2.**Interrupt Request Signal Map (Sheet 1 of 3)

| Table 4-2. | Interrupt Request Signal Map (Sheet 3 of 3                 | 3)     |

|------------|------------------------------------------------------------|--------|

| Line       | Module                                                     | Signal |

| 48         | External Interrupt Controller                              | EIC 4  |

| 49         | External Interrupt Controller                              | EIC 5  |

| 50         | External Interrupt Controller                              | EIC 6  |

| 51         | External Interrupt Controller                              | EIC 7  |

| 52         | External Interrupt Controller                              | EIC 8  |

| 53         | Inter-IC Sound (I2S) Controller                            | IISC   |

| 54         | Serial Peripheral Interface                                | SPI    |

| 55         | Timer/Counter                                              | TC00   |

| 56         | Timer/Counter                                              | TC01   |

| 57         | Timer/Counter                                              | TC02   |

| 58         | Timer/Counter                                              | TC10   |

| 59         | Timer/Counter                                              | TC11   |

| 60         | Timer/Counter                                              | TC12   |

| 61         | Two-wire Master Interface                                  | TWIMO  |

| 62         | Two-wire Slave Interface                                   | TWIS0  |

| 63         | Two-wire Master Interface                                  | TWIM1  |

| 64         | Two-wire Slave Interface                                   | TWIS1  |

| 65         | Universal Synchronous Asynchronous<br>Receiver Transmitter | USART0 |

| 66         | Universal Synchronous Asynchronous<br>Receiver Transmitter | USART1 |

| 67         | Universal Synchronous Asynchronous<br>Receiver Transmitter | USART2 |

| 68         | Universal Synchronous Asynchronous<br>Receiver Transmitter | USART3 |

| 69         | ADC controller interface                                   | ADCIFE |

| 70         | DAC Controller                                             | DACC   |

| 71         | Analog Comparator Interface                                | ACIFC  |

| 72         | Audio Bitstream DAC                                        | ABDACB |

| 73         | True Random Number Generator                               | TRNG   |

| 74         | Parallel Capture                                           | PARC   |

| 75         | Capacitive Touch Module B                                  | CATB   |

| 77         | Two-wire Master Interface                                  | TWIM2  |

| 78         | Two-wire Master Interface                                  | TWIM3  |

| 79         | LCD Controller A                                           | LCDCA  |

Table 4-2.

Interrupt Request Signal Map (Sheet 3 of 3)

# ATSAM4L8/L4/L2

# 5.2 Embedded Memories

- Internal high-speed flash

- 512Kbytes (ATSAM4Lx8)

- 256Kbytes (ATSAM4Lx4)

- 128Kbytes (ATSAM4Lx2)

- Pipelined flash architecture, allowing burst reads from sequential flash locations, hiding penalty of 1 wait state access

- Pipelined flash architecture typically reduces the cycle penalty of 1 wait state operation compared to 0 wait state operation

- 100 000 write cycles, 15-year data retention capability

- Sector lock capabilities, bootloader protection, security bit

- 32 fuses, erased during chip erase

- User page for data to be preserved during chip erase

- Internal high-speed SRAM, single-cycle access at full speed

- 64Kbytes (ATSAM4Lx8)

- 32Kbytes (ATSAM4Lx4, ATSAM4Lx2)

# 5.3 Physical Memory Map

The system bus is implemented as a bus matrix. All system bus addresses are fixed, and they are never remapped in any way, not even during boot. The 32-bit physical address space is mapped as follows:

| Mamani              | Start Address | Size      | Size      |

|---------------------|---------------|-----------|-----------|

| Memory              |               | ATSAM4Lx4 | ATSAM4Lx2 |

| Embedded Flash      | 0x0000000     | 256Kbytes | 128Kbytes |

| Embedded SRAM       | 0x20000000    | 32Kbytes  | 32Kbytes  |

| Cache SRAM          | 0x21000000    | 4Kbytes   | 4Kbytes   |

| Peripheral Bridge A | 0x4000000     | 64Kbytes  | 64Kbytes  |

| Peripheral Bridge B | 0x400A0000    | 64Kbytes  | 64Kbytes  |

| AESA                | 0x400B0000    | 256 bytes | 256 bytes |

| Peripheral Bridge C | 0x400E0000    | 64Kbytes  | 64Kbytes  |

| Peripheral Bridge D | 0x400F0000    | 64Kbytes  | 64Kbytes  |

Table 5-1. ATSAM4L8/L4/L2 Physical Memory Map

| Memory              | Start Address | Size      |  |

|---------------------|---------------|-----------|--|

| Memory              |               | ATSAM4Lx8 |  |

| Embedded Flash      | 0x0000000     | 512Kbytes |  |

| Embedded SRAM       | 0x20000000    | 64Kbytes  |  |

| Cache SRAM          | 0x21000000    | 4Kbytes   |  |

| Peripheral Bridge A | 0x4000000     | 64Kbytes  |  |

| Peripheral Bridge B | 0x400A0000    | 64 Kbytes |  |

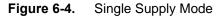

The internal regulator is connected to the VDDIN pin and its output VDDOUT feeds VDDCORE in linear mode or through an inductor in switching mode. Figure 6-4 shows the power schematics to be used. All I/O lines will be powered by the same power ( $V_{VDDIN}=V_{VDDIN}=V_{VDDANA}$ ).

#### 6.2.3 LCD Power Modes

#### 6.2.3.1 Principle

LCD lines is powered using the device internal voltage sources provided by the LCDPWR block. When enabled, the LCDPWR blocks will generate the VLCD, BIASL, BIASH voltages.

LCD pads are splitted into three clusters that can be powered independently namely clusters A, B and C. A cluster can either be in GPIO mode or in LCD mode.

When a cluster is in GPIO mode, its VDDIO pin must be powered externally. None of its GPIO pin can be used as a LCD line

When a cluster is in LCD mode, each clusters VDDIO pin can be either forced externally (1.8-3.6V) or unconnected (nc). GPIOs in a cluster are not available when it is in LCD mode. A cluster is set in LCD mode by the LCDCA controller when it is enabled depending on the number of segments configured. The LCDPWR block is powered by the VLCDIN pin inside cluster A

When LCD feature is not used, VLCDIN must be always powered (1.8-3.6V). VLCD, CAPH, CAPL, BIASH, BIASL can be left unconnected in this case

Atmel

# 7. Low Power Techniques

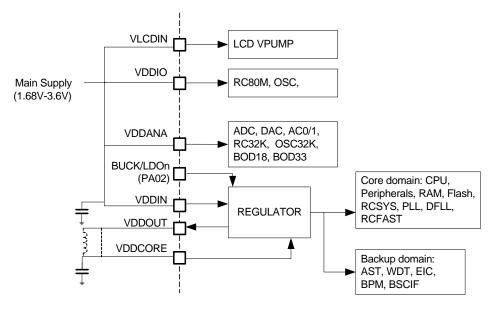

The ATSAM4L8/L4/L2 supports multiple power configurations to allow the user to optimize its power consumption in different use cases. The Backup Power Manager (BPM) implements different solutions to reduce the power consumption:

- The Power Save modes intended to reduce the logic activity and to adapt the power configuration. See "Power Save Modes" on page 55.

- The Power Scaling intended to scale the power configuration (voltage scaling of the regulator). See "Power Scaling" on page 60.

These two techniques can be combined together.

# 7.1 Power Save Modes

Refer to Section 6. "Power and Startup Considerations" on page 46 to get definition of the core and the backup domains.

Atmel

#### 7.1.3 BACKUP Mode

The BACKUP mode allows achieving the lowest power consumption possible in a system which is performing periodic wake-ups to perform tasks but not requiring fast startup time.

The Core domain is powered-off. The internal SRAM and register contents of the Core domain are lost. The Backup domain is kept powered-on. The 32kHz clock (RC32K or OSC32K) is kept running if enabled to feed modules that require clocking.

In BACKUP mode, the configuration of the I/O lines is preserved. Refer to Section 9. "Backup Power Manager (BPM)" on page 677 to have more details.

#### 7.1.3.1 Entering BACKUP Mode

The Backup mode is entered by using the WFI instruction with the following settings:

- set the SCR.SLEEPDEEP bit to 1. (See the Power Management section in the ARM Cortex-M4 Processor chapter).

- set the BPM.PSAVE.BKUP bit to 1.

## 7.1.3.2 Exiting BACKUP Mode

Exit from BACKUP mode happens if a reset occurs or if an enabled wake up event occurs.

The reset sources are:

- BOD33 reset

- BOD18 reset

- WDT reset

- External reset in RESET\_N pin

The wake up sources are:

- EIC lines (level transition only)

- BOD33 interrupt

- BOD18 interrupt

- AST alarm, periodic, overflow

- WDT interrupt

The RC32K or OSC32K should be used as clock source for modules if required. The PMCON.CK32S is used to select one of these two 32kHz clock sources.

Exiting the BACKUP mode is triggered by:

- a reset source: an internal reset sequence is performed according to the reset source. Once VDDCORE is stable and has the correct value according to RUN0 mode, the internal reset is released and program execution starts. The corresponding reset source is flagged in the Reset Cause register (RCAUSE) of the PM.

- a wake up source: the Backup domain is not reset. An internal reset is generated to the Core domain, and the system switches back to the previous RUN mode. Once VDDCORE is stable and has the correct value, the internal reset in the Core domain is released and program execution starts. The BKUP bit is set in the Reset Cause register (RCAUSE) of the PM. It allows the user to discriminate between the reset cause and a wake up cause from the BACKUP mode. The wake up cause can be found in the Backup Wake up Cause register (BPM.BKUPWCAUSE).

#### 8.9.6 Security Considerations

In protected state this module may access sensible information located in the device memories. To avoid any risk of sensible data extraction from the module registers, all operations are non interruptible except by a disable command triggered by writing a one to CR.DIS. Issuing this command clears all the interface and internal registers.

Some registers have some special protection:

- It is not possible to read or write the LENGTH register when the part is protected.

- In addition, when the part is protected and an operation is ongoing, it is not possible to read the ADDR and DATA registers. Once an operation has started, the user has to wait until it has terminated by polling the DONE field in the Status Register (SR.DONE).

#### 8.9.7 Chip Erase

The Chip erase operation consists in:

- 1. clearing all the volatile memories in the system

- 2. clearing the whole flash array

- 3. clearing the protected state

No proprietary or sensitive information is left in volatile memories once the protected state is disabled.

This feature is operated by writing a one to the CE bit of the Control Register (CR.CE). When the operation completes, SR.DONE is asserted.

#### 8.9.8 Cortex-M4 Core Reset Source

The SMAP processes the EDP Core hold reset requests (Refer to Section 1.1.8 "SMAP Core Reset Request Source" on page 6). When requested, it instructs the Power Manager to hold the Cortex-M4 core under reset.

The SMAP can de-assert the core reset request if a one is written to the Hold Core Reset bit in the Status Clear Register (SCR.HCR). This has the effect of releasing the CPU from its reset state. To assert again this signal, a new reset sequence with TCK tied low must be issued.

Note that clearing HCR with this module is only possible when it is enabled, for more information refer to Section 8.9.4 "Initializing the Module" on page 78. Also note that asserting RESET\_N automatically clears HCR.

| 8.9.11.8   | Chip Identification Regist | er |

|------------|----------------------------|----|

| Name:      | CIDR                       |    |

| Access Ty  | e: Read-Only               |    |

| Offset:    | 0xF0                       |    |

| Reset Valu | : -                        |    |

| 31    | 30      | 29     | 28          | 27      | 26      | 25 | 24 |

|-------|---------|--------|-------------|---------|---------|----|----|

| EXT   |         | NVPTYP | NVPTYP ARCH |         |         |    |    |

|       |         |        |             |         |         |    |    |

| 23    | 22      | 21     | 20          | 19      | 18      | 17 | 16 |

|       | ARCH    |        |             |         | SRAMSIZ |    |    |

|       |         |        |             |         |         |    |    |

| 15    | 14      | 13     | 12          | 11      | 10      | 9  | 8  |

|       | NVPSIZ2 |        |             | NVPSIZ  |         |    |    |

|       |         |        |             |         |         |    |    |

| 7     | 6       | 5      | 4           | 3       | 2       | 1  | 0  |

| EPROC |         |        |             | VERSION |         |    |    |

Note: Refer to section CHIPID for more information on this register.

| 8.9.11.9 Chip Identification Extension Register Name: EXID |                        |    |      |    |    |    |    |  |

|------------------------------------------------------------|------------------------|----|------|----|----|----|----|--|

| Access Type:                                               | Access Type: Read-Only |    |      |    |    |    |    |  |

| Offset:                                                    | 0xF4                   |    |      |    |    |    |    |  |

| Reset Value:                                               | -                      |    |      |    |    |    |    |  |

|                                                            |                        |    |      |    |    |    |    |  |

| 31                                                         | 30                     | 29 | 28   | 27 | 26 | 25 | 24 |  |

|                                                            |                        |    | EXID |    |    |    |    |  |

|                                                            |                        |    |      |    |    |    |    |  |

| 23                                                         | 22                     | 21 | 20   | 19 | 18 | 17 | 16 |  |

|                                                            |                        |    | EXID |    |    |    |    |  |

|                                                            |                        |    |      |    |    |    |    |  |

| 15                                                         | 14                     | 13 | 12   | 11 | 10 | 9  | 8  |  |

|                                                            |                        |    | EXID |    |    |    |    |  |

|                                                            |                        |    |      |    |    |    |    |  |

| 7                                                          | 6                      | 5  | 4    | 3  | 2  | 1  | 0  |  |

|                                                            | EXID                   |    |      |    |    |    |    |  |

Note: Refer to section CHIPID for more information on this register.

| Mode      | Conditions                                    | T <sub>A</sub> | Typical<br>Wakeup Time | Тур  | Max <sup>(1)</sup> | Unit |

|-----------|-----------------------------------------------|----------------|------------------------|------|--------------------|------|

| SLEEP0    | Switching mode                                | 25°C           | 9 * Main clock         | 3817 | 4033               |      |

| SLEEPU    | Switching mode                                | 85°C           | cycles                 | 3934 | 4174               |      |

|           |                                               | 25°C           | 9 * Main clock         | 2341 | 2477               |      |

| SLEEP1    | Switching mode                                | 85°C           | cycles + 500ns         | 2437 | 2585               | -    |

|           |                                               | 25°C           | 9 * Main clock         | 1758 | 1862               | -    |

| SLEEP2    | Switching mode                                | 85°C           | cycles + 500ns         | 1847 | 1971               | -    |

| SLEEP3    | Linear mode                                   |                |                        | 51   | 60                 |      |

|           | OSC32K and AST running<br>Fast wake-up enable |                |                        | 5.9  | 8.7                | μA   |

| WAIT      | OSC32K and AST stopped<br>Fast wake-up enable |                | 1.5µs                  | 4.7  | 7.6                | •    |

| RETENTION | OSC32K running<br>AST running at 1kHz         | 25°C           | 1.5µs                  | 3.1  | 5.1                |      |

|           | AST and OSC32K stopped                        |                |                        | 2.2  | 4.2                | -    |

| BACKUP    | OSC32K running<br>AST running at 1 kHz        |                |                        | 1.5  | 3.1                |      |

|           | AST and OSC32K stopped                        |                |                        | 0.9  | 1.7                | Ī    |

Table 9-6.

ATSAM4L4/2 Current consumption and Wakeup time for power scaling mode 0 and 2

1. These values are based on characterization. These values are not covered by test limits in production.

| Table 9-7. | ATSAM4L8 Current consumption and Wakeup time for power scaling mode 0 and 2 |

|------------|-----------------------------------------------------------------------------|

|            |                                                                             |

| Mode | Conditions                                      | T <sub>A</sub> | Typical<br>Wakeup Time | Тур | Max <sup>(1)</sup> | Unit   |

|------|-------------------------------------------------|----------------|------------------------|-----|--------------------|--------|

|      | CPU running a Fibonacci algorithm               | 25°C           | NI/A                   | 319 | 343                |        |

|      | Linear mode                                     | 85°C           | N/A                    | 326 | 350                |        |

|      | CPU running a CoreMark algorithm<br>Linear mode | 25°C           | N/A                    | 343 | 387                |        |

|      |                                                 | 85°C           |                        | 351 | 416                |        |

| RUN  | CPU running a Fibonacci algorithm               | 25°C           | N/A                    | 181 | 198                | µA/MHz |

|      | Switching mode                                  | 85°C           |                        | 186 | 203                |        |

|      | CPU running a CoreMark algorithm                | 25°C           | N/A                    | 192 | 232                |        |

|      | Switching mode                                  | 85°C           |                        | 202 | 239                |        |

- Atmel

#### 9.5.3 Peripheral Power Consumption in Power Scaling mode 0 and 2

The values in Table 9-11 are measured values of power consumption under the following conditions:

- Operating conditions, internal core supply (Figure 9-2)

- $V_{VDDIN} = 3.3 V$

- $-V_{VDDCORE}$  supplied by the internal regulator in switching mode

- TA = 25°C

- Oscillators

- OSC0 (crystal oscillator) stopped

- OSC32K (32KHz crystal oscillator) running with external 32KHz crystal

- DFLL running at 48 MHz with OSC32K as reference clock

Atmel

- Clocks

- DFLL used as main clock source

- CPU, AHB, and PB clocks undivided

- I/Os are inactive with internal pull-up

- Flash enabled in high speed mode

- CPU in SLEEP0 mode

- BOD18 and BOD33 disabled

Consumption active is the added current consumption when the module clock is turned on.

# 9.6.5

**9.6.5 High Drive TWI Pin : PB00, PB01 Table 9-19.** High Drive TWI Pin Characteristics in TWI configuration <sup>(1)</sup>

| Symbol                | Parameter                               | Conditions                                                                              | Min                    | Тур | Max                    | Units |

|-----------------------|-----------------------------------------|-----------------------------------------------------------------------------------------|------------------------|-----|------------------------|-------|

| R <sub>PULLUP</sub>   | Pull-up resistance (2)                  | PB00, PB01                                                                              |                        | 40  |                        | kΩ    |

| R <sub>PULLDOWN</sub> | Pull-down resistance <sup>(2)</sup>     |                                                                                         |                        | 40  |                        | kΩ    |

| V <sub>IL</sub>       | Input low-level voltage                 |                                                                                         | -0.3                   |     | 0.3 * V <sub>VDD</sub> |       |

| V <sub>IH</sub>       | Input high-level voltage                |                                                                                         | 0.7 * V <sub>VDD</sub> |     | V <sub>VDD</sub> + 0.3 |       |

| V <sub>OL</sub>       | Output low-level voltage                |                                                                                         |                        |     | 0.4                    | V     |

| V <sub>OH</sub>       | Output high-level voltage               |                                                                                         | V <sub>VDD</sub> - 0.4 |     |                        |       |

|                       |                                         | DRIVEL=0                                                                                |                        |     | 0.5                    |       |

|                       |                                         | DRIVEL=1                                                                                |                        |     | 1.0                    |       |

|                       |                                         | DRIVEL=2                                                                                |                        |     | 1.6                    |       |

|                       |                                         | DRIVEL=3                                                                                |                        |     | 3.1                    | 1     |

| I <sub>OL</sub>       | Output low-level current <sup>(3)</sup> | DRIVEL=4                                                                                |                        |     | 6.2                    | mA    |

|                       |                                         | DRIVEL=5                                                                                |                        |     | 9.3                    | -     |

|                       |                                         | DRIVEL=6                                                                                |                        |     | 15.5                   |       |

|                       |                                         | DRIVEL=7                                                                                |                        |     | 21.8                   |       |

|                       |                                         | DRIVEH=0                                                                                |                        | 0.5 |                        |       |

|                       | (2)                                     | DRIVEH=1                                                                                |                        | 1   |                        |       |

| I <sub>CS</sub>       | Current Source <sup>(2)</sup>           | DRIVEH=2                                                                                |                        | 1.5 |                        | mA    |

|                       |                                         | DRIVEH=3                                                                                |                        | 3   |                        |       |

| f <sub>MAX</sub>      | Max frequency <sup>(2)</sup>            | HsMode with Current source;<br>DRIVEx=3, SLEW=0<br>Cbus = 400pF, $V_{VDD}$ = 1.68V      | 3.5                    | 6.4 |                        | MHz   |

| t <sub>RISE</sub>     | Rise time <sup>(2)</sup>                | HsMode Mode, DRIVEx=3, SLEW=0<br>Cbus = 400pF, Rp = 440Ohm,<br>$V_{VDD}$ = 1.68V        |                        | 28  | 38                     | ns    |

|                       | Fall time <sup>(2)</sup>                | Standard Mode, DRIVEx=3, SLEW=0<br>Cbus = 400pF, Rp = 440Ohm,<br>$V_{VDD}$ = 1.68V      |                        | 50  | 95                     |       |

| t <sub>FALL</sub>     |                                         | HsMode Mode, DRIVEx=3, SLEW=0<br>Cbus = 400pF, Rp = 440Ohm,<br>V <sub>VDD</sub> = 1.68V |                        | 50  | 95                     | ns    |

1.  $V_{VDD}$  corresponds to either  $V_{VDDIN}$  or  $V_{VDDIO}$ , depending on the supply for the pin. Refer to Section 3-5 on page 13 for details

2. These values are based on simulation. These values are not covered by test limits in production or characterization

3. These values are based on characterization. These values are not covered by test limits in production

# 9.10 Timing Characteristics

## 9.10.1 RESET\_N Timing

Table 9-53. RESET\_N Waveform Parameters (1)

| Symbol             | Parameter                    | Conditions | Min | Max | Units |

|--------------------|------------------------------|------------|-----|-----|-------|

| t <sub>RESET</sub> | RESET_N minimum pulse length |            | 10  |     | ns    |

1. These values are based on simulation. These values are not covered by test limits in production.

#### 9.10.2 USART in SPI Mode Timing

9.10.2.1 Master mode

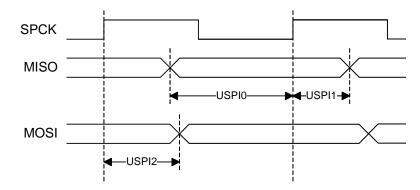

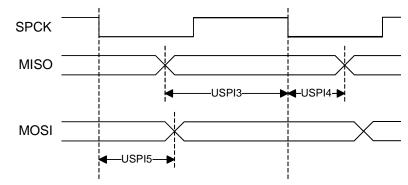

Figure 9-7. USART in SPI Master Mode with (CPOL= CPHA= 0) or (CPOL= CPHA= 1)

**Figure 9-8.** USART in SPI Master Mode with (CPOL= 0 and CPHA= 1) or (CPOL= 1 and CPHA= 0)

# ATSAM4L8/L4/L2

# Table 9-59. USART1 in SPI mode Timing, Slave Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions                           | Min                                                                       | Max    | Units |

|--------|-----------------------------------|--------------------------------------|---------------------------------------------------------------------------|--------|-------|

| USPI6  | SPCK falling to MISO delay        |                                      |                                                                           | 373.58 |       |

| USPI7  | MOSI setup time before SPCK rises |                                      | $4.16 + t_{SAMPLE}^{(2)} + t_{CLK_USART}$                                 |        |       |

| USPI8  | MOSI hold time after SPCK rises   |                                      | 46.69 -( t <sub>SAMPLE</sub> <sup>(2)</sup> +<br>t <sub>CLK_USART )</sub> |        |       |

| USPI9  | SPCK rising to MISO delay         | V <sub>VDDIO</sub> from              |                                                                           | 373.54 |       |

| USPI10 | MOSI setup time before SPCK falls | 3.0V to 3.6V,<br>maximum<br>external | $4.16 + (t_{SAMPLE}^{(2)} + t_{CLK_USART})$                               |        | ns    |

| USPI11 | MOSI hold time after SPCK falls   | capacitor =<br>40pF                  | 46.69 -( t <sub>SAMPLE</sub> <sup>(2)</sup> +<br>t <sub>CLK_USART )</sub> |        |       |

| USPI12 | NSS setup time before SPCK rises  |                                      | 200.43                                                                    |        |       |

| USPI13 | NSS hold time after SPCK falls    |                                      | -16.5                                                                     |        |       |

| USPI14 | NSS setup time before SPCK falls  |                                      | 200.43                                                                    |        |       |

| USPI15 | NSS hold time after SPCK rises    |                                      | -16.5                                                                     |        |       |

Table 9-60.

USART2 in SPI mode Timing, Slave Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions                           | Min                                                                      | Max    | Units |

|--------|-----------------------------------|--------------------------------------|--------------------------------------------------------------------------|--------|-------|

| USPI6  | SPCK falling to MISO delay        |                                      |                                                                          | 770.02 |       |

| USPI7  | MOSI setup time before SPCK rises |                                      | 136.56 + $t_{SAMPLE}^{(2)}$ + $t_{CLK_USART}$                            |        |       |

| USPI8  | MOSI hold time after SPCK rises   |                                      | 47.9 -( t <sub>SAMPLE</sub> <sup>(2)</sup> +<br>t <sub>CLK_USART</sub> ) |        |       |

| USPI9  | SPCK rising to MISO delay         | V <sub>VDDIO</sub> from              |                                                                          | 570.19 |       |

| USPI10 | MOSI setup time before SPCK falls | 3.0V to 3.6V,<br>maximum<br>external | $136.73 + (t_{SAMPLE}^{(2)} + t_{CLK_USART})$                            |        | ns    |

| USPI11 | MOSI hold time after SPCK falls   | capacitor =<br>40pF                  | 47.9 -( t <sub>SAMPLE</sub> <sup>(2)</sup> +<br>t <sub>CLK_USART</sub> ) |        |       |

| USPI12 | NSS setup time before SPCK rises  |                                      | 519.87                                                                   |        |       |

| USPI13 | NSS hold time after SPCK falls    |                                      | -1.83                                                                    |        |       |

| USPI14 | NSS setup time before SPCK falls  |                                      | 519.87                                                                   |        |       |

| USPI15 | NSS hold time after SPCK rises    |                                      | -1.83                                                                    |        |       |

| Symbol | Parameter                         | Conditions                           | Min                                                                       | Мах    | Units |

|--------|-----------------------------------|--------------------------------------|---------------------------------------------------------------------------|--------|-------|

| USPI6  | SPCK falling to MISO delay        |                                      |                                                                           | 593.9  |       |

| USPI7  | MOSI setup time before SPCK rises |                                      | $45.93 + t_{SAMPLE}^{(2)} + t_{CLK_USART}$                                |        |       |

| USPI8  | MOSI hold time after SPCK rises   |                                      | 47.03 -( t <sub>SAMPLE</sub> <sup>(2)</sup> +<br>t <sub>CLK_USART )</sub> |        |       |

| USPI9  | SPCK rising to MISO delay         | V <sub>VDDIO</sub> from              |                                                                           | 593.38 |       |

| USPI10 | MOSI setup time before SPCK falls | 3.0V to 3.6V,<br>maximum<br>external | 45.93 +( $t_{SAMPLE}^{(2)}$ +<br>$t_{CLK_USART}$ )                        |        | ns    |

| USPI11 | MOSI hold time after SPCK falls   | capacitor =<br>40pF                  | 47.03 -( t <sub>SAMPLE</sub> <sup>(2)</sup> +<br>t <sub>CLK_USART</sub> ) |        |       |

| USPI12 | NSS setup time before SPCK rises  |                                      | 237.5                                                                     |        |       |

| USPI13 | NSS hold time after SPCK falls    |                                      | -1.81                                                                     |        |       |

| USPI14 | NSS setup time before SPCK falls  |                                      | 237.5                                                                     |        | 1     |

| USPI15 | NSS hold time after SPCK rises    |                                      | -1.81                                                                     |        |       |

Table 9-61.

USART3 in SPI mode Timing, Slave Mode<sup>(1)</sup>

Notes: 1. These values are based on simulation. These values are not covered by test limits in production.

2. Where:

$$t_{SAMPLE} = t_{SPCK} - \left( \left\lfloor \frac{t_{SPCK}}{2 \times t_{CLKUSART}} \right\rfloor + \frac{1}{2} \right) \times t_{CLKUSART}$$

#### Maximum SPI Frequency, Slave Input Mode

The maximum SPI slave input frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(\frac{f_{CLKSPI} \times 2}{9}, \frac{1}{SPIn})$$

Where *SPIn* is the MOSI setup and hold time, USPI7 + USPI8 or USPI10 + USPI11 depending on CPOL and NCPHA.  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

## Maximum SPI Frequency, Slave Output Mode

The maximum SPI slave output frequency is given by the following formula:

Atmel

$$f_{SPCKMAX} = MIN(\frac{f_{CLKSPI} \times 2}{9}, f_{PINMAX}, \frac{1}{SPIn + t_{SETUP}})$$

Where *SPIn* is the MISO delay, USPI6 or USPI9 depending on CPOL and NCPHA.  $T_{SETUP}$  is the SPI master setup time. refer to the SPI master datasheet for  $T_{SETUP}$ .  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.  $f_{PINMAX}$  is the maximum frequency of the SPI pins. refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

# Table 9-66.SWD Timings(1)

| Symbol | Parameter                                                     | Conditions                               | Min | Мах     | Units |

|--------|---------------------------------------------------------------|------------------------------------------|-----|---------|-------|

| Thigh  | SWDCLK High period                                            |                                          | 10  | 500 000 |       |

| Tlow   | SWDCLK Low period                                             | V <sub>VDDIO</sub> from<br>3.0V to 3.6V, | 10  | 500 000 |       |

| Tos    | SWDIO output skew to falling edge SWDCLK                      | maximum                                  | -5  | 5       | ns    |

| Tis    | Input Setup time required between SWDIO                       | external<br>capacitor =                  | 4   | -       | 10    |

| Tih    | Input Hold time required between SWDIO and rising edge SWDCLK | 40pF                                     | 1   | -       | 1     |

Note: 1. These values are based on simulation. These values are not covered by test limits in production or characterization.

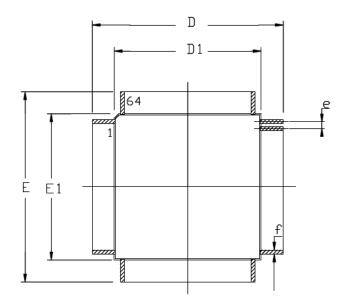

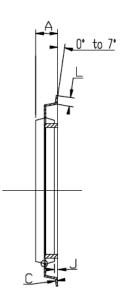

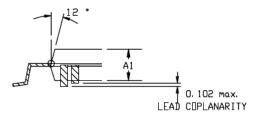

## Figure 10-7. TQFP-64 Package Drawing

#### COMMON DIMENSIONS IN MM

| SYMBOL | Min      | Max   | NDTES |

|--------|----------|-------|-------|

| A      |          | 1. 20 |       |

| A1     | 0, 95    | 1. 05 |       |

| С      | 0. 09    | 0. 20 |       |

| D      | 12.0     | O BSC |       |

| D1     | 10.0     |       |       |

| E      | 12.0     |       |       |

| E1     | 10,0     |       |       |

| J      | 0, 05    | 0.15  |       |

| L      | 0, 45    | 0, 75 |       |

| e      | 0.50 BSC |       |       |

| f      | 0.17     | 0, 27 |       |

# Table 10-20. Device and Package Maximum Weight

| 300 | mg |

|-----|----|

|     |    |

# Table 10-21. Package Characteristics

| bisture Sensitivity Level | MSL3 |

|---------------------------|------|

|---------------------------|------|

# Table 10-22. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

# 11. Ordering Information

| Ordering Code    | Flash<br>(Kbytes) | RAM<br>(Kbytes) | Package | Conditioning | Package<br>Type | Temperature Operating<br>Range |  |

|------------------|-------------------|-----------------|---------|--------------|-----------------|--------------------------------|--|

| ATSAM4LC8CA-AU   |                   |                 | TQFP100 | Tray         |                 |                                |  |

| ATSAM4LC8CA-AUR  |                   |                 | IQFFIUU | Reel         |                 |                                |  |

| ATSAM4LC8CA-CFU  |                   |                 | Tray    |              |                 |                                |  |

| ATSAM4LC8CA-CFUR |                   | VFBGA100        | Reel    |              |                 |                                |  |

| ATSAM4LC8BA-AU   |                   | 64              |         | TOFDCA       | Tray            |                                |  |

| ATSAM4LC8BA-AUR  | 512               |                 | TQFP64  | Reel         | Green           | Industrial -40°C to 85°C       |  |

| ATSAM4LC8BA-MU   |                   |                 |         | Tray         |                 |                                |  |

| ATSAM4LC8BA-MUR  |                   |                 | QFN64   | Reel         |                 |                                |  |

| ATSAM4LC8BA-UUR  |                   | WLCSP64         | Reel    |              |                 |                                |  |

| ATSAM4LC8AA-MU   |                   |                 | Tray    |              |                 |                                |  |

| ATSAM4LC8AA-MUR  |                   |                 | QFN48   | Reel         |                 |                                |  |

Table 11-1.

ATSAM4LC8 Sub Serie Ordering Information

Table 11-2.

ATSAM4LC4 Sub Serie Ordering Information

| Ordering Code     | Flash<br>(Kbytes) | RAM<br>(Kbytes) | Package  | Conditioning | Package<br>Type | Temperature Operating<br>Range |

|-------------------|-------------------|-----------------|----------|--------------|-----------------|--------------------------------|

| ATSAM4LC4CA-AU-ES | 256               | 32              | TQFP100  | ES           | Green           | N/A                            |

| ATSAM4LC4CA-AU    |                   |                 |          | Tray         |                 | Industrial -40°C to 85°C       |

| ATSAM4LC4CA-AUR   |                   |                 |          | Reel         |                 |                                |

| ATSAM4LC4CA-CFU   |                   |                 | VFBGA100 | Tray         |                 |                                |

| ATSAM4LC4CA-CFUR  |                   |                 |          | Reel         |                 | Industrial -40°C to 85°C       |

| ATSAM4LC4BA-AU-ES |                   |                 | TQFP64   | ES           |                 | N/A                            |

| ATSAM4LC4BA-AU    |                   |                 |          | Tray         |                 | Industrial -40°C to 85°C       |

| ATSAM4LC4BA-AUR   |                   |                 |          | Reel         |                 |                                |

| ATSAM4LC4BA-MU-ES |                   |                 | QFN64    | ES           |                 | N/A                            |

| ATSAM4LC4BA-MU    |                   |                 |          | Tray         |                 | Industrial -40°C to 85°C       |

| ATSAM4LC4BA-MUR   |                   |                 |          | Reel         |                 |                                |

| ATSAM4LC4BA-UUR   |                   |                 | WLCSP64  | Reel         |                 | Industrial -40°C to 85°C       |

| ATSAM4LC4AA-AU-ES |                   |                 | TQFP48   | ES           |                 | N/A                            |

| ATSAM4LC4AA-AU    |                   |                 |          | Tray         |                 | Industrial -40°C to 85°C       |

| ATSAM4LC4AA-AUR   |                   |                 |          | Reel         |                 |                                |

| ATSAM4LC4AA-MU-ES |                   |                 | QFN48    | ES           |                 | N/A                            |

| ATSAM4LC4AA-MU    |                   |                 |          | Tray         |                 | Industrial -40°C to 85°C       |

| ATSAM4LC4AA-MUR   |                   |                 |          | Reel         |                 |                                |