Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT         |

| Number of I/O              | 27                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 32K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.68V ~ 3.6V                                                              |

| Data Converters            | A/D 3x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 48-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 48-QFN (7x7)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4lc4aa-mur |

Table 2-2.

ATSAM4LC Configuration Summary

| Feature             | ATSAM4LC8/4/2C                                 | ATSAM4LC8/4/2B         | ATSAM4LC8/4/2A |  |  |  |

|---------------------|------------------------------------------------|------------------------|----------------|--|--|--|

|                     | Digital Frequency Locked Loop 20-150MHz (DFLL) |                        |                |  |  |  |

|                     | Phase Locked Loop 48-240MHz (PLL)              |                        |                |  |  |  |

|                     | Crysta                                         | l Oscillator 0.6-30MHz | (OSC0)         |  |  |  |

| Oscillators         | Cryst                                          | al Oscillator 32kHz (O | SC32K)         |  |  |  |

| Oscillators         | RC                                             | Oscillator 80MHz (RC   | 80M)           |  |  |  |

|                     | RC O                                           | scillator 4,8,12MHz (R | CFAST)         |  |  |  |

|                     | SYS)                                           |                        |                |  |  |  |

|                     | RC Oscillator 32kHz (RC32K)                    |                        |                |  |  |  |

| ADC                 | 15-channel                                     | 7-channel              | 3-channel      |  |  |  |

| DAC                 |                                                | 1-channel              |                |  |  |  |

| Analog Comparators  | 4                                              | 2                      | 1              |  |  |  |

| CATB Sensors        | 32                                             | 32                     | 26             |  |  |  |

| USB                 |                                                | 1                      |                |  |  |  |

| Audio Bitstream DAC |                                                | 1                      |                |  |  |  |

| IIS Controller      |                                                | 1                      |                |  |  |  |

| Packages            | TQFP/VFBGA                                     | TQFP/QFN/<br>WLCSP     | TQFP/QFN       |  |  |  |

Table 2-3.

ATSAM4LS Configuration Summary

| Feature                 | ATSAM4LS8/4/2C | ATSAM4LS8/4/2B | ATSAM4LS8/4/2A                           |  |  |  |

|-------------------------|----------------|----------------|------------------------------------------|--|--|--|

| Number of Pins          | 100            | 64             | 48                                       |  |  |  |

| Max Frequency           | 48MHz          |                |                                          |  |  |  |

| Flash                   |                | 512/256/128KB  |                                          |  |  |  |

| SRAM                    |                | 64/32/32KB     |                                          |  |  |  |

| SEGMENT LCD             |                | NA             |                                          |  |  |  |

| GPIO                    | 80             | 48             | 32                                       |  |  |  |

| High-drive pins         | 6              | 3              | 1                                        |  |  |  |

| External Interrupts     |                | 8 + 1 NMI      |                                          |  |  |  |

| TWI                     | 2 Masters + 2  | Masters/Slaves | 1 Master + 1<br>Master/Slave             |  |  |  |

| USART                   |                | 4              | 3 in LC sub series<br>4 in LS sub series |  |  |  |

| PICOUART                |                | 1              | 0                                        |  |  |  |

| Peripheral DMA Channels |                | 16             |                                          |  |  |  |

| AESA                    |                | NA             |                                          |  |  |  |

| Peripheral Event System | 1              |                |                                          |  |  |  |

| SPI                     | 1              |                |                                          |  |  |  |

| Asynchronous Timers     |                | 1              |                                          |  |  |  |

**Table 3-8.** Signal Descriptions List (Sheet 4 of 4)

| Signal Name | Function                           | Туре | Active<br>Level | Comments |

|-------------|------------------------------------|------|-----------------|----------|

| PA31 - PA00 | Parallel I/O Controller I/O Port A | I/O  |                 |          |

| PB15 - PB00 | Parallel I/O Controller I/O Port B | I/O  |                 |          |

| PC31 - PC00 | Parallel I/O Controller I/O Port C | I/O  |                 |          |

Note: 1. See "Power and Startup Considerations" section.

### 3.4 I/O Line Considerations

### 3.4.1 SW/JTAG Pins

The JTAG pins switch to the JTAG functions if a rising edge is detected on TCK low after the RESET\_N pin has been released. The TMS, and TDI pins have pull-up resistors when used as JTAG pins. The TCK pin always has pull-up enabled during reset. The JTAG pins can be used as GPIO pins and multiplexed with peripherals when the JTAG is disabled. Refer to Section 3.2.3 "JTAG Port Connections" on page 29 for the JTAG port connections.

For more details, refer to Section 1.1 "Enhanced Debug Port (EDP)" on page 3.

# 3.4.2 RESET\_N Pin

The RESET\_N pin is a schmitt input and integrates a permanent pull-up resistor to VDDIN. As the product integrates a power-on reset detector, the RESET\_N pin can be left unconnected in case no reset from the system needs to be applied to the product.

### 3.4.3 TWI Pins

When these pins are used for TWI, the pins are open-drain outputs with slew-rate limitation and-inputs with inputs with spike-filtering. When used as GPIO-pins or used for other peripherals, the pins have the same characteristics as GPIO pins.

### 3.4.4 GPIO Pins

All the I/O lines integrate a pull-up/pull-down resistor and slew rate controller. Programming these features is performed independently for each I/O line through the GPIO Controllers. After reset, I/O lines default as inputs with pull-up and pull-down resistors disabled and slew rate enabled.

### 3.4.5 High-drive Pins

The six pins PA02, PB00, PB01, PC04, PC05 and PC06 have high-drive output capabilities. Refer to Section 9.6.2 "High-drive I/O Pin: PA02, PC04, PC05, PC06" on page 115 for electrical characteristics.

### 3.4.6 **USB Pins**

When these pins are used for USB, the pins are behaving according to the USB specification. When used as GPIO pins or used for other peripherals, the pins have the same behavior as other normal I/O pins, but the characteristics are different. Refer to Section 9.6.3 "USB I/O Pin: PA25, PA26" on page 116 for electrical characteristics.

These pins are compliant to USB standard only when VDDIO power supply is 3.3V nominal.

# 4.4 Cortex-M4 processor features and benefits summary

- tight integration of system peripherals reduces area and development costs

- . Thumb instruction set combines high code density with 32-bit performance

- · code-patch ability for ROM system updates

- · power control optimization of system components

- integrated sleep modes for low power consumption

- · fast code execution permits slower processor clock or increases sleep mode time

- hardware division and fast digital-signal-processing orientated multiply accumulate

- · saturating arithmetic for signal processing

- · deterministic, high-performance interrupt handling for time-critical applications

- memory protection unit (MPU) for safety-critical applications

- · extensive debug and trace capabilities:

- Serial Wire Debug and Serial Wire Trace reduce the number of pins required for debugging, tracing, and code profiling.

# 4.5 Cortex-M4 core peripherals

These are:

Nested Vectored Interrupt Controller

The NVIC is an embedded interrupt controller that supports low latency interrupt processing.

System control block

The *System control block* (SCB) is the programmers model interface to the processor. It provides system implementation information and system control, including configuration, control, and reporting of system exceptions.

System timer

The system timer, SysTick, is a 24-bit count-down timer. Use this as a Real Time Operating System (RTOS) tick timer or as a simple counter.

Memory protection unit

The *Memory protection unit* (MPU) improves system reliability by defining the memory attributes for different memory regions. It provides up to eight different regions, and an optional predefined background region.

The complete Cortex-M4 User Guide can be found on the ARM web site:

http://infocenter.arm.com/help/topic/com.arm.doc.dui0553a/DUI0553A cortex m4 dgug.pdf

### 7.1.3 BACKUP Mode

The BACKUP mode allows achieving the lowest power consumption possible in a system which is performing periodic wake-ups to perform tasks but not requiring fast startup time.

The Core domain is powered-off. The internal SRAM and register contents of the Core domain are lost. The Backup domain is kept powered-on. The 32kHz clock (RC32K or OSC32K) is kept running if enabled to feed modules that require clocking.

In BACKUP mode, the configuration of the I/O lines is preserved. Refer to Section 9. "Backup Power Manager (BPM)" on page 677 to have more details.

### 7.1.3.1 Entering BACKUP Mode

The Backup mode is entered by using the WFI instruction with the following settings:

- set the SCR.SLEEPDEEP bit to 1. (See the Power Management section in the ARM Cortex-M4 Processor chapter).

- set the BPM.PSAVE.BKUP bit to 1.

### 7.1.3.2 Exiting BACKUP Mode

Exit from BACKUP mode happens if a reset occurs or if an enabled wake up event occurs.

The reset sources are:

- BOD33 reset

- BOD18 reset

- WDT reset

- External reset in RESET\_N pin

The wake up sources are:

- EIC lines (level transition only)

- BOD33 interrupt

- BOD18 interrupt

- AST alarm, periodic, overflow

- WDT interrupt

The RC32K or OSC32K should be used as clock source for modules if required. The PMCON.CK32S is used to select one of these two 32kHz clock sources.

Exiting the BACKUP mode is triggered by:

- a reset source: an internal reset sequence is performed according to the reset source. Once VDDCORE is stable and has the correct value according to RUN0 mode, the internal reset is released and program execution starts. The corresponding reset source is flagged in the Reset Cause register (RCAUSE) of the PM.

- a wake up source: the Backup domain is not reset. An internal reset is generated to the Core

domain, and the system switches back to the previous RUN mode. Once VDDCORE is

stable and has the correct value, the internal reset in the Core domain is released and

program execution starts. The BKUP bit is set in the Reset Cause register (RCAUSE) of the

PM. It allows the user to discriminate between the reset cause and a wake up cause from the

BACKUP mode. The wake up cause can be found in the Backup Wake up Cause register

(BPM.BKUPWCAUSE).

### 7.1.4 Wakeup Time

# 7.1.4.1 Wakeup Time From SLEEP Mode

The latency depends on the clock sources wake up time. If the clock sources are not stopped, there is no latency to wake the clocks up.

### 7.1.4.2 Wakeup Time From WAIT or RETENTION Mode

The wake up latency consists of:

- the switching time from the low power configuration to the RUN mode power configuration. By default, the switching time is completed when all the voltage regulation system is ready. To speed-up the startup time, the user can set the Fast Wakeup bit in BPM.PMCON register.

- the wake up time of the RC oscillator used to start the system up. By default, the RCSYS oscillator is used to startup the system. The user can use another clock source (RCFAST for example) to speed up the startup time by configuring the PM.FASTWKUP register. Refer to Section 9. "Power Manager (PM)" on page 677.

- the Flash memory wake up time.

To have the shortest wakeup time, the user should:

- set the BPM.PMCON.FASTWKUP bit.

- configure the PM.FASTSLEEP.FASTRCOSC field to use the RCFAST main clock.

- enter the WAIT or RETENTION mode

Upon a wakeup, this is required to keep the main clock connected to RCFAST until the voltage regulation system is fully ready (when BPM.ISR.PSOK bit is one). During this wakeup period, the FLASHCALW module is automatically configured to operate in "1 wait state mode".

### 7.1.4.3 Wake time from BACKUP mode

It is equal to the Core domain logic reset latency (similar to the reset latency caused by an external reset in RESET\_N pin) added to the time required for the voltage regulation system to be stabilized.

# 8.7.12 JTAG Instructions Summary

The implemented JTAG instructions are shown in the table below.

Table 8-2.

Implemented JTAG instructions list

| IR instruction value | Instruction    | Description                                                                               | availability<br>when<br>protected | Component                |

|----------------------|----------------|-------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|

| b0000                | EXTEST         | Select boundary-scan chain as data register for testing circuitry external to the device. | yes                               |                          |

| b0001                | SAMPLE_PRELOAD | Take a snapshot of external pin values without affecting system operation.                | yes                               |                          |

| b0100                | INTEST         | Select boundary-scan chain for internal testing of the device.                            | yes                               |                          |

| b0101                | CLAMP          | Bypass device through Bypass register, while driving outputs from boundary-scan register. | yes                               | BSCAN-TAP                |

| b1000                | ABORT          | ARM JTAG-DP Instruction                                                                   | yes                               |                          |

| b1010                | DPACC          | ARM JTAG-DP Instruction                                                                   | yes                               |                          |

| b1011                | APACC          | ARM JTAG-DP Instruction                                                                   | yes                               |                          |

| b1100                | -              | Reserved                                                                                  | yes                               | SWJ-DP<br>(in JTAG mode) |

| b1101                | -              | Reserved                                                                                  | yes                               |                          |

| b1110                | IDCODE         | ARM JTAG-DP Instruction                                                                   | yes                               |                          |

| b1111                | BYPASS         | Bypass this device through the bypass register.                                           | yes                               |                          |

8.9.11.1 Control Register

Name: CR

Access Type: Write-Only

Offset: 0x00

**Reset Value:** 0x00000000

| 31 | 30 | 29 | 28 | 27   | 26  | 25  | 24 |

|----|----|----|----|------|-----|-----|----|

| -  | -  | -  | -  | -    | ı   | 1   | -  |

|    |    |    |    |      |     |     |    |

| 23 | 22 | 21 | 20 | 19   | 18  | 17  | 16 |

| -  | -  | -  | -  | -    | ı   | 1   | -  |

|    |    |    |    |      |     |     |    |

| 15 | 14 | 13 | 12 | 11   | 10  | 9   | 8  |

| -  | -  | -  | -  | -    | -   | -   | -  |

|    |    |    |    |      |     |     |    |

| 7  | 6  | 5  | 4  | 3    | 2   | 1   | 0  |

| -  | -  | =  | CE | FSPR | CRC | DIS | EN |

Writing a zero to a bit in this register has no effect.

### CE: Chip Erase

Writing a one to this bit triggers the FLASH Erase All (EA) operation which clears all volatile memories, the whole flash array, the general purpose fuses and the protected state. The Status register DONE field indicates the completion of the operation. Reading this bit always returns 0

### FSPR: Flash User Page Read

Writing a one to this bit triggers a read operation in the User page. The word pointed by the ADDR register in the page is read and written to the DATA register. ADDR is post incremented allowing a burst of reads without modifying ADDR. SR.DONE must be read high prior to reading the DATA register.

Reading this bit always returns 0

# CRC: Cyclic Redundancy Code

Writing a one triggers a CRC calculation over a memory area defined by the ADDR and LENGTH registers. Reading this bit always returns 0

Note: This feature is restricted while in protected state

### DIS: Disable

Writing a one to this bit disables the module. Disabling the module resets the whole module immediately.

### · EN: Enable

Writing a one to this bit enables the module.

- 0: No bus error has been detected sincle last clear of this bit

- HCR: Hold Core reset

- 1: The Cortex-M4 core is held under reset

- 0: The Cortex-M4 core is not held under reset

- DONE: Operation done

- 1: At least one operation has terminated since last clear of this field

- 0: No operation has terminated since last clear of this field

8.9.11.6 Data Register

Name: DATA

Access Type: Read/Write

Offset: 0x14

**Reset Value:** 0x00000000

| 31 | 30   | 29 | 28 | 27 | 26 | 25 | 24 |  |  |  |

|----|------|----|----|----|----|----|----|--|--|--|

|    | DATA |    |    |    |    |    |    |  |  |  |

|    |      |    |    |    |    |    |    |  |  |  |

| 23 | 22   | 21 | 20 | 19 | 18 | 17 | 16 |  |  |  |

|    |      |    | DA | TA |    |    |    |  |  |  |

|    |      |    |    |    |    |    |    |  |  |  |

| 15 | 14   | 13 | 12 | 11 | 10 | 9  | 8  |  |  |  |

|    |      |    | DA | TA |    |    |    |  |  |  |

|    |      |    |    |    |    |    |    |  |  |  |

| 7  | 6    | 5  | 4  | 3  | 2  | 1  | 0  |  |  |  |

|    | DATA |    |    |    |    |    |    |  |  |  |

<sup>•</sup> DATA: Generic data register

8.9.11.7 Module Version

Name: VERSION

Access Type: Read-Only

Offset: 0x28

Reset Value: -

| 31 | 30 | 29 | 28  | 27   | 26  | 25   | 24 |

|----|----|----|-----|------|-----|------|----|

| -  | -  | -  | -   | -    | -   | -    | -  |

|    |    |    |     |      |     |      | _  |

| 23 | 22 | 21 | 20  | 19   | 18  | 17   | 16 |

| -  | -  | -  | -   |      | VAR | ANT  |    |

|    |    |    |     |      |     |      | _  |

| 15 | 14 | 13 | 12  | 11   | 10  | 9    | 8  |

| -  | -  | -  | -   |      | VER | SION |    |

|    |    |    |     |      |     |      |    |

| 7  | 6  | 5  | 4   | 3    | 2   | 1    | 0  |

|    |    |    | VER | SION |     |      |    |

<sup>·</sup> VARIANT: Variant number

Reserved. No functionality associated.

# • VERSION: Version number

Version number of the module. No functionality associated.

3. These values are based on characterization. These values are not covered by test limits in production

# 9.6.2 High-drive I/O Pin: PA02, PC04, PC05, PC06

**Table 9-14.** High-drive I/O Pin Characteristics (1)

| Symbol                | Parameter                                | Conditions    |                                                    | Min                    | Тур  | Max                    | Units |

|-----------------------|------------------------------------------|---------------|----------------------------------------------------|------------------------|------|------------------------|-------|

| R <sub>PULLUP</sub>   | Pull-up resistance (2)                   |               |                                                    |                        | 40   |                        | kΩ    |

| R <sub>PULLDOWN</sub> | Pull-down resistance <sup>(2)</sup>      |               |                                                    |                        | 40   |                        | kΩ    |

| V <sub>IL</sub>       | Input low-level voltage                  |               |                                                    | -0.3                   |      | 0.2 * V <sub>VDD</sub> |       |

| V <sub>IH</sub>       | Input high-level voltage                 |               |                                                    | 0.8 * V <sub>VDD</sub> |      | V <sub>VDD</sub> + 0.3 | .,    |

| V <sub>OL</sub>       | Output low-level voltage                 |               |                                                    |                        |      | 0.4                    | V     |

| V <sub>OH</sub>       | Output high-level voltage                |               |                                                    | V <sub>VDD</sub> - 0.4 |      |                        |       |

|                       |                                          | 00000         | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                        |      | 1.8                    |       |

|                       | 0 1 1 1 1 1 (3)                          | ODCR0=0       | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                        |      | 3.2                    | mA    |

| l <sub>OL</sub>       | Output low-level current (3)             | 00000 4       | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                        |      | 3.2                    |       |

|                       |                                          | ODCR0=1       | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                        |      | 6                      | mA    |

|                       |                                          | 00000         | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                        |      | 1.6                    |       |

|                       | (3)                                      | ODCR0=0       | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                        |      | 3.2                    | mA    |

| I <sub>OH</sub>       | Output high-level current <sup>(3)</sup> |               | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                        |      | 3.2                    | A     |

|                       |                                          | ODCR0=1       | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                        |      | 6                      | mA    |

|                       | Direction (2)                            | OSRR0=0       | ODCR0=0                                            |                        |      | 20                     |       |

|                       |                                          | OSRR0=1       | 1.68V <v<sub>VDD&lt;2.7V,<br/>Cload = 25pF</v<sub> |                        |      | 40                     | ns    |

| t <sub>RISE</sub>     | Rise time <sup>(2)</sup>                 | OSRR0=0       | ODCR0=0                                            |                        |      | 11                     |       |

|                       |                                          | OSRR0=1       | 2.7V <v<sub>VDD&lt;3.6V,<br/>Cload = 25pF</v<sub>  |                        |      | 18                     | ns    |

|                       |                                          | OSRR0=0       | ODCR0=0                                            |                        |      | 20                     |       |

|                       | F-11 (2)                                 | OSRR0=1       | 1.68V <v<sub>VDD&lt;2.7V,<br/>Cload = 25pF</v<sub> |                        |      | 40                     | ns    |

| t <sub>FALL</sub>     | Fall time <sup>(2)</sup>                 | OSRR0=0       | ODCR0=0                                            |                        |      | 11                     |       |

|                       |                                          | OSRR0=1       | $2.7V < V_{VDD} < 3.6V$ , Cload = $25pF$           |                        |      | 18                     | ns    |

|                       |                                          | OSRR0=0       | ODCR0=0, V <sub>VDD</sub> >2.7V                    |                        |      | 22                     | MHz   |

| _                     | (2)                                      | OSRR0=1       | load = 25pF                                        |                        |      | 17                     | MHz   |

| F <sub>PINMAX</sub>   | Output frequency <sup>(2)</sup>          | OSRR0=0       | ODCR0=1, V <sub>VDD</sub> >2.7V                    |                        |      | 35                     | MHz   |

|                       | OSRR0=1                                  | load = 25pF   |                                                    |                        | 26   | MHz                    |       |

| I <sub>LEAK</sub>     | Input leakage current <sup>(3)</sup>     | Pull-up resis | tors disabled                                      |                        | 0.01 | 2                      | μA    |

| C <sub>IN</sub>       | Input capacitance <sup>(2)</sup>         |               |                                                    |                        | 10   |                        | pF    |

<sup>1.</sup>  $V_{VDD}$  corresponds to either  $V_{VDDIN}$  or  $V_{VDDIO}$ , depending on the supply for the pin. Refer to Section 3-5 on page 13 for details

<sup>2.</sup> These values are based on simulation. These values are not covered by test limits in production or characterization

<sup>3.</sup> These values are based on characterization. These values are not covered by test limits in production

# 9.6.5

**High Drive TWI Pin : PB00, PB01**. High Drive TWI Pin Characteristics in TWI configuration (1) Table 9-19.

| Symbol                | Parameter                           | Conditions                                                                                 | Min                    | Тур | Max                    | Units |

|-----------------------|-------------------------------------|--------------------------------------------------------------------------------------------|------------------------|-----|------------------------|-------|

| R <sub>PULLUP</sub>   | Pull-up resistance (2)              | PB00, PB01                                                                                 |                        | 40  |                        | kΩ    |

| R <sub>PULLDOWN</sub> | Pull-down resistance <sup>(2)</sup> |                                                                                            |                        | 40  |                        | kΩ    |

| V <sub>IL</sub>       | Input low-level voltage             |                                                                                            | -0.3                   |     | 0.3 * V <sub>VDD</sub> |       |

| V <sub>IH</sub>       | Input high-level voltage            |                                                                                            | 0.7 * V <sub>VDD</sub> |     | V <sub>VDD</sub> + 0.3 | .,    |

| V <sub>OL</sub>       | Output low-level voltage            |                                                                                            |                        |     | 0.4                    | V     |

| V <sub>OH</sub>       | Output high-level voltage           |                                                                                            | V <sub>VDD</sub> - 0.4 |     |                        |       |

|                       |                                     | DRIVEL=0                                                                                   |                        |     | 0.5                    |       |

|                       |                                     | DRIVEL=1                                                                                   |                        |     | 1.0                    |       |

|                       |                                     | DRIVEL=2                                                                                   |                        |     | 1.6                    |       |

|                       | (3)                                 | DRIVEL=3                                                                                   |                        |     | 3.1                    |       |

| I <sub>OL</sub>       | Output low-level current (3)        | DRIVEL=4                                                                                   |                        |     | 6.2                    | mA    |

|                       |                                     | DRIVEL=5                                                                                   |                        |     | 9.3                    |       |

|                       |                                     | DRIVEL=6                                                                                   |                        |     | 15.5                   |       |

|                       |                                     | DRIVEL=7                                                                                   |                        |     | 21.8                   |       |

|                       |                                     | DRIVEH=0                                                                                   |                        | 0.5 |                        |       |

|                       | (2)                                 | DRIVEH=1                                                                                   |                        | 1   |                        |       |

| I <sub>CS</sub>       | Current Source <sup>(2)</sup>       | DRIVEH=2                                                                                   |                        | 1.5 |                        | mA    |

|                       |                                     | DRIVEH=3                                                                                   |                        | 3   |                        |       |

| f <sub>MAX</sub>      | Max frequency <sup>(2)</sup>        | HsMode with Current source;<br>DRIVEx=3, SLEW=0<br>Cbus = 400pF, V <sub>VDD</sub> = 1.68V  | 3.5                    | 6.4 |                        | MHz   |

| t <sub>RISE</sub>     | Rise time <sup>(2)</sup>            | HsMode Mode, DRIVEx=3, SLEW=0<br>Cbus = 400pF, Rp = 440Ohm,<br>V <sub>VDD</sub> = 1.68 V   |                        | 28  | 38                     | ns    |

|                       | Fall time <sup>(2)</sup>            | Standard Mode, DRIVEx=3, SLEW=0<br>Cbus = 400pF, Rp = 440Ohm,<br>V <sub>VDD</sub> = 1.68 V |                        | 50  | 95                     | 20    |

| t <sub>FALL</sub>     | rail time <sup>v-7</sup>            | HsMode Mode, DRIVEx=3, SLEW=0<br>Cbus = 400pF, Rp = 440Ohm,<br>V <sub>VDD</sub> = 1.68V    |                        | 50  | 95                     | ns    |

$V_{VDD}$  corresponds to either  $V_{VDDIN}$  or  $V_{VDDIO}$ , depending on the supply for the pin. Refer to Section 3-5 on page 13 for details 1.

<sup>2.</sup> These values are based on simulation. These values are not covered by test limits in production or characterization

<sup>3.</sup> These values are based on characterization. These values are not covered by test limits in production

# 9.9.7 Liquid Crystal Display Controler characteristicsTable 9-51. Liquid Crystal Display Controler characteristics

| Symbol              | Parameter                             | Conditions                                                        | Min   | Тур                   | Max | Units |

|---------------------|---------------------------------------|-------------------------------------------------------------------|-------|-----------------------|-----|-------|

| SEG                 | Segment Terminal Pins                 |                                                                   |       |                       | 40  |       |

| СОМ                 | Common Terminal Pins                  |                                                                   |       |                       | 4   |       |

| f <sub>Frame</sub>  | LCD Frame Frequency                   | F <sub>CLKLCD</sub>                                               | 31.25 |                       | 512 | Hz    |

| C <sub>Flying</sub> | Flying Capacitor                      |                                                                   |       | 100                   |     | nF    |

| V <sub>LCD</sub>    | (4)                                   |                                                                   |       | 3                     |     |       |

| BIAS2               | LCD Regulated Voltages (1) CFG.FCST=0 | $C_{Flying} = 100nF$<br>100nF on $V_{LCD}$ , BIAS2 and BIAS1 pins |       | 2*V <sub>LCD</sub> /3 |     | V     |

| BIAS1               | 01 0.1 00 1 = 0                       |                                                                   |       | V <sub>LCD</sub> /3   |     |       |

<sup>1.</sup> These values are based on simulation. These values are not covered by test limits in production or characterization

#### 9.9.7.1 Liquid Crystal Controler supply current

The values in Table 9-52 are measured values of power consumption under the following conditions, except where noted:

- T=25°C, WAIT mode, Low power waveform, Frame Rate = 32Hz from OSC32K

- Configuration: 4COMx40SEG, 1/4 Duty, 1/3 Bias, No animation

- All segments on, Load = 160 x 22pF between each COM and each SEG.

- LCDCA current based on I<sub>LCD</sub> = I<sub>WAIT</sub>(Lcd On) I<sub>WAIT</sub>(Lcd Off)

Table 9-52. Liquid Crystal Display Controler supply current

| Symbol   | Conditions                                            | Conditions          |  |      | Max | Units |

|----------|-------------------------------------------------------|---------------------|--|------|-----|-------|

|          | Internal voltage generation CFG.FCST=0  External bias | $V_{VDDIN} = 3.6V$  |  | 8.85 |     |       |

| <b> </b> |                                                       | $V_{VDDIN} = 1.8V$  |  | 6.16 |     |       |

| ILCD     |                                                       | $V_{VDDIN} = 3.3 V$ |  | 0.98 |     | μA    |

|          | V <sub>LCD</sub> =3.0V                                | $V_{VDDIN} = 1.8V$  |  | 1.17 |     |       |

# 9.10 Timing Characteristics

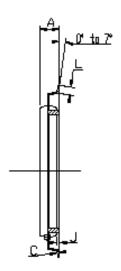

# 9.10.1 RESET\_N Timing

Table 9-53. RESET N Waveform Parameters (1)

| Symbol             | Parameter                    | Conditions | Min | Max | Units |

|--------------------|------------------------------|------------|-----|-----|-------|

| t <sub>RESET</sub> | RESET_N minimum pulse length |            | 10  |     | ns    |

<sup>1.</sup> These values are based on simulation. These values are not covered by test limits in production.

# 9.10.2 USART in SPI Mode Timing

### 9.10.2.1 Master mode

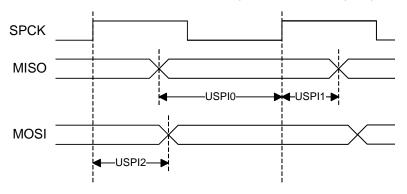

Figure 9-7. USART in SPI Master Mode with (CPOL= CPHA= 0) or (CPOL= CPHA= 1)

**Figure 9-8.** USART in SPI Master Mode with (CPOL= 0 and CPHA= 1) or (CPOL= 1 and CPHA= 0)

MISO

-USPI10--USPI11--

Figure 9-10. USART in SPI Slave Mode with (CPOL= CPHA= 0) or (CPOL= CPHA= 1)

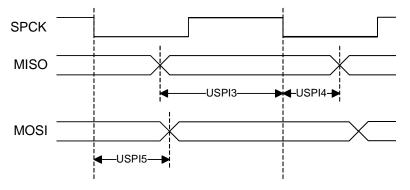

Figure 9-11. USART in SPI Slave Mode, NPCS Timing

Table 9-58. USART0 in SPI mode Timing, Slave Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions                           | Min                                                                    | Max    | Units |

|--------|-----------------------------------|--------------------------------------|------------------------------------------------------------------------|--------|-------|

| USPI6  | SPCK falling to MISO delay        |                                      |                                                                        | 740.67 |       |

| USPI7  | MOSI setup time before SPCK rises |                                      | 56.73 + t <sub>SAMPLE</sub> <sup>(2)</sup> + t <sub>CLK_USART</sub>    |        |       |

| USPI8  | MOSI hold time after SPCK rises   |                                      | 45.18 -( t <sub>SAMPLE</sub> <sup>(2)</sup> + t <sub>CLK_USART</sub> ) |        |       |

| USPI9  | SPCK rising to MISO delay         | V <sub>VDDIO</sub> from              |                                                                        | 670.18 |       |

| USPI10 | MOSI setup time before SPCK falls | 3.0V to 3.6V,<br>maximum<br>external | 56.73 +( t <sub>SAMPLE</sub> <sup>(2)</sup> + t <sub>CLK_USART</sub> ) |        | ns    |

| USPI11 | MOSI hold time after SPCK falls   | capacitor = 40pF                     | 45.18 -( t <sub>SAMPLE</sub> <sup>(2)</sup> + t <sub>CLK_USART</sub> ) |        |       |

| USPI12 | NSS setup time before SPCK rises  |                                      | 688.71                                                                 |        |       |

| USPI13 | NSS hold time after SPCK falls    |                                      | -2.25                                                                  |        |       |

| USPI14 | NSS setup time before SPCK falls  |                                      | 688.71                                                                 |        |       |

| USPI15 | NSS hold time after SPCK rises    |                                      | -2.25                                                                  |        |       |

SPCK, CPOL=0

SPCK, CPOL=1

NPCS

-SPI12SPI13SPI13SPI15NPCS

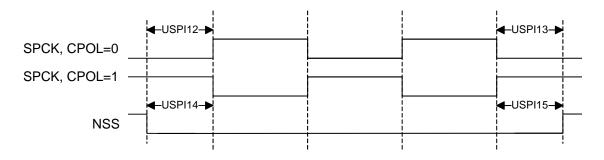

Figure 9-16. SPI Slave Mode, NPCS Timing

**Table 9-63.** SPI Timing, Slave Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions                                           | Min | Max | Units |

|--------|-----------------------------------|------------------------------------------------------|-----|-----|-------|

| SPI6   | SPCK falling to MISO delay        |                                                      | 19  | 47  |       |

| SPI7   | MOSI setup time before SPCK rises |                                                      | 0   |     |       |

| SPI8   | MOSI hold time after SPCK rises   |                                                      | 5.4 |     |       |

| SPI9   | SPCK rising to MISO delay         | V <sub>VDDIO</sub> from<br>2.85V to 3.6V,<br>maximum | 19  | 46  |       |

| SPI10  | MOSI setup time before SPCK falls |                                                      | 0   |     |       |

| SPI11  | MOSI hold time after SPCK falls   | external                                             | 5.3 |     | ns    |

| SPI12  | NPCS setup time before SPCK rises | capacitor = 40pF                                     | 4   |     |       |

| SPI13  | NPCS hold time after SPCK falls   |                                                      | 2.5 |     |       |

| SPI14  | NPCS setup time before SPCK falls |                                                      | 6   |     |       |

| SPI15  | NPCS hold time after SPCK rises   |                                                      | 1.1 |     |       |

Note: 1. These values are based on simulation. These values are not covered by test limits in production.

### Maximum SPI Frequency, Slave Input Mode

The maximum SPI slave input frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{CLKSPI}, \frac{1}{SPIn})$$

Where  $\mathit{SPIn}$  is the MOSI setup and hold time, SPI7 + SPI8 or SPI10 + SPI11 depending on CPOL and NCPHA. $f_{\mathit{CLKSPI}}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

### **Maximum SPI Frequency, Slave Output Mode**

The maximum SPI slave output frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{PINMAX}, \frac{1}{SPIn + t_{SETUP}})$$

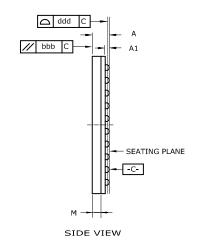

#### 10.2 Package Drawings

Figure 10-1. VFBGA-100 package drawing

### DRAWINGS NOT SCALED

TOP VIEW

## COMMON DIMENSIONS

(UnIt of Measure = mm)

| SYMBOL    | MIN                         | MOM      | MAX   | NOTE    |

|-----------|-----------------------------|----------|-------|---------|

| А         |                             |          | 1.00  |         |

| A1        | 0.160                       |          | 0.260 |         |

| E/D       | 7.                          | 00 / 7.0 | 0     |         |

| E1/D1     | 5.                          | 85 / 5.8 | 5     |         |

| I/J       | 0.575                       |          |       |         |

| eD/eE     | Ball pitch : 0.650          |          | 0     |         |

| b         | 0.270 0.370                 |          |       |         |

| М         | Mold thickness: 0.450 ref   |          |       | 150 ref |

| aaa       | Pack edge tolerance : 0.100 |          |       | : 0.100 |

| bbb       | Mold flatness: 0.100        |          |       | 100     |

| ddd       | Copla: 0.080                |          |       |         |

| ball diam | 0.300                       |          |       |         |

| n         | 100                         |          |       |         |

Notes: 1. No JEDEC Drawing Reference.

- 2. Array as seen from the bottom of the package.

- 3. Dimension A includes stand-off height A1, package body thickness, and lid height, but does not include attached features.

4. Dimension b is measured at the maximum ball diameter, parallel to primary datum C.

Table 10-2. Device and Package Maximum Weight

| 120 | mg |

|-----|----|

|     |    |

#### Table 10-3. Package Characteristics

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

|----------------------------|------|

#### Table 10-4. Package Reference

| JEDEC Drawing Reference | N/A |

|-------------------------|-----|

| JESD97 Classification   | E1  |

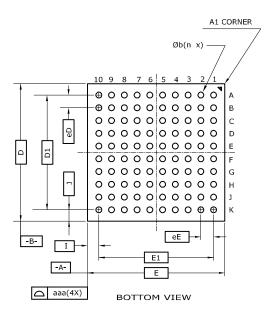

Figure 10-2. TQFP-100 Package Drawing

### COMMON DIMENSIONS IN MM

| SYMBOL | Min               | Max   | NOTES |

|--------|-------------------|-------|-------|

| А      |                   | 1. 20 |       |

| A1     | D. 95             | 1. 05 |       |

| С      | D. D <del>9</del> | 0. 20 |       |

| п      | 16. O             |       |       |

| D1     | 14, 0             |       |       |

| E      | 16. 0             | O BSC |       |

| E1     | 14. 0             | O 85C |       |

| J      | D. D5 O. 15       |       |       |

| L      | D. 45 O. 75       |       |       |

| e      | 0, 5              |       |       |

| f      | 0. 17             | 0, 27 |       |

155

Table 10-5. Device and Package Maximum Weight

| 500 | ma   |

|-----|------|

| 000 | 1119 |

# Table 10-6. Package Characteristics

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

# Table 10-7. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

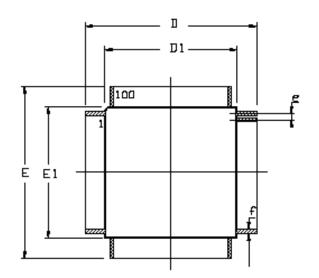

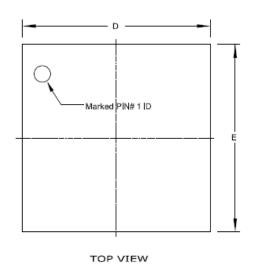

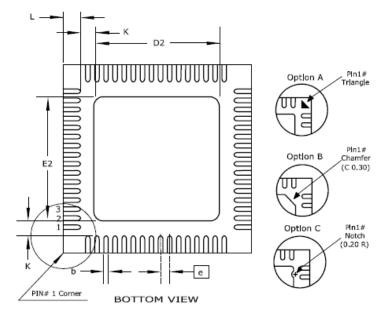

Figure 10-8. QFN-64 Package Drawing

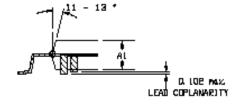

SIDE VIEW

# COMMON DIMENSIONS

(Unit of Measure = mm)

| SYMBOL | MIN      | NOM  | MAX  | NOTE |

|--------|----------|------|------|------|

| Α      | 0,80     | 0,90 | 1,00 |      |

| A1     |          | 0.02 | 0.05 |      |

| А3     | 0.20 REF |      |      |      |

| D/E    | 8,90     | 9.00 | 9.10 |      |

| D2/E2  | 5.90     | 6.00 | 6.10 |      |

| L      | 0,30     | 0,40 | 0,50 |      |

| K      | -        | 1.10 | -    |      |

| b      | 0.18     | 0.25 | 0.30 | 2    |

| e      | 0.50 BSC |      |      |      |

| n      | 64       |      |      |      |

Note: The exposed pad is not connected to anything internally, but should be soldered to ground to increase board level reliability.

Table 10-23. Device and Package Maximum Weight

| 200 mg |

|--------|

|--------|

# Table 10-24. Package Characteristics

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

|----------------------------|------|

# Table 10-25. Package Reference

| JEDEC Drawing Reference | MO-220 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

| able of Contents |                |     |

|------------------|----------------|-----|

| 13.8             | Rev. H– 11/16  | 173 |

| 13.7             | Rev. G- 03/14  | 173 |

| 13.6             | Rev. F- 12/13  | 173 |

| 13.5             | Rev. E – 07/13 | 173 |

| 13.4             | Rev. D – 03/13 | 172 |

### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131 USA

**Tel**: (+1)(408) 441-0311 **Fax**: (+1)(408) 487-2600

www.atmel.com

### Atmel Asia Limited

Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG

**Tel**: (+852) 2245-6100 **Fax**: (+852) 2722-1369

### Atmel Munich GmbH

Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY

**Tel**: (+49) 89-31970-0 **Fax**: (+49) 89-3194621

### Atmel Japan

16F, Shin Osaki Kangyo Bldg. 1-6-4 Osaka Shinagawa-ku Tokyo 104-0032

JAPAN

**Tel**: (+81) 3-6417-0300 **Fax**: (+81) 3-6417-0370

### © 2013 Atmel Corporation. All rights reserved.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, picoPower<sup>®</sup>, Adjacent Key Suppression<sup>®</sup>, AKS<sup>®</sup>, Qtouch<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. ARM<sup>®</sup>, AMBA<sup>®</sup>, Thumb<sup>®</sup>, Cortex<sup>™</sup> are registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.