Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT        |

| Number of I/O              | 43                                                                       |

| Program Memory Size        | 256KB (256K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 32K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.68V ~ 3.6V                                                             |

| Data Converters            | A/D 7x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-TQFP                                                                  |

| Supplier Device Package    | 64-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4lc4ba-au |

events, even in sleep modes where the module clock is stopped. Power monitoring is supported by on-chip Power-on Reset (POR18, POR33), Brown-out Detectors (BOD18, BOD33). The device features several oscillators, such as Phase Locked Loop (PLL), Digital Frequency Locked Loop (DFLL), Oscillator 0 (OSC0), Internal RC 4,8,12MHz oscillator (RCFAST), system RC oscillator (RCSYS), Internal RC 80MHz, Internal 32kHz RC and 32kHz Crystal Oscillator. Either of these oscillators can be used as source for the system clock. The DFLL is a programmable internal oscillator from 40 to 150MHz. It can be tuned to a high accuracy if an accurate reference clock is running, e.g. the 32kHz crystal oscillator.

The Watchdog Timer (WDT) will reset the device unless it is periodically serviced by the software. This allows the device to recover from a condition that has caused the system to be unstable.

The Asynchronous Timer (AST) combined with the 32kHz crystal oscillator supports powerful real-time clock capabilities, with a maximum timeout of up to 136 years. The AST can operate in counter or calendar mode.

The Frequency Meter (FREQM) allows accurate measuring of a clock frequency by comparing it to a known reference clock.

The Full-speed USB 2.0 device and embedded host interface (USBC) supports several USB classes at the same time utilizing the rich end-point configuration.

The device includes six identical 16-bit Timer/Counter (TC) channels. Each channel can be independently programmed to perform frequency measurement, event counting, interval measurement, pulse generation, delay timing, and pulse width modulation.

The ATSAM4L8/L4/L2 also features many communication interfaces, like USART, SPI, or TWI, for communication intensive applications. The USART supports different communication modes, like SPI Mode and LIN Mode.

A general purpose 16-channel ADC is provided, as well as four analog comparators (ACIFC). The ADC can operate in 12-bit mode at full speed. The analog comparators can be paired to detect when the sensing voltage is within or outside the defined reference window.

Atmel offers the QTouch Library for embedding capacitive touch buttons, sliders, and wheels functionality. The patented charge-transfer signal acquisition offers robust sensing and includes fully debounced reporting of touch keys as well as Adjacent Key Suppression® (AKS®) technology for unambiguous detection of key events. The easy-to-use QTouch Suite toolchain allows you to explore, develop, and debug your own touch applications.

The Audio Bitstream DAC (ABDACB) converts a 16-bit sample value to a digital bitstream with an average value proportional to the sample value. Two channels are supported, making the ABDAC particularly suitable for stereo audio.

The Inter-IC Sound Controller (IISC) provides a 5-bit wide, bidirectional, synchronous, digital audio link with external audio devices. The controller is compliant with the Inter-IC Sound (I2S) bus specification.

Figure 3-8. ATSAM4LS WLCSP64 Pinout

|   | 1      | 2      | 3           | 4       | 5    | 6     | 7    | 8     |

|---|--------|--------|-------------|---------|------|-------|------|-------|

| Α | PB04   | GNDANA | AD<br>VREFP | VDDANA  | PA09 | PA28  | PA27 | PA12  |

| В | PB03   | XIN32  | XOUT32      | PA08    | PB06 | PA10  | PA11 | PA29  |

| С | VDDIN  | PB01   | PA05        | PA06    | PA07 | PB07  | PA13 | GND   |

| D | VDDOUT | PB00   | PA04        | PB05    | PB12 | PB08  | PA14 | VDDIO |

| Е | GND    | PA03   | PB02        | RESET_N | PB13 | PB09  | PA15 | PA30  |

| F | VDD    | TCK    | PA02        | PB14    | PA22 | PB10  | PA16 | PA31  |

| G | GND    | PA26   | PA24        | PA00    | PA01 | PA19  | PA18 | PA17  |

| Η | VDDIO  | PA25   | PA23        | PB15    | PA21 | VDDIO | PA20 | PB11  |

Table 3-3.

64-pin GPIO Controller Function Multiplexing for WLCSP package (Sheet 2 of 3)

| ATSAM4LC | ATSAM4LS   | Pin   | GPIO | Supply |               | ·                |                 | PIO Functio  | ns                | ·              |                 |

|----------|------------|-------|------|--------|---------------|------------------|-----------------|--------------|-------------------|----------------|-----------------|

| WLCSP    | ,          |       |      | "      | Α             | В                | С               | D            | E                 | F              | G               |

|          |            |       |      |        | SPI           | TWIMS0           | EIC             | GLOC         | SCIF              | LCDCA          | CATB            |

| Н3       | Н3         | PA23  | 23   | LCDC   | SCK           | TWD              | EXTINT8         | IN3          | GCLK IN0          | SEG38          | DIS             |

| G3       | G3         | PA24  | 24   | LCDC   | SPI<br>NPCS0  | TWIMS0<br>TWCK   |                 | GLOC<br>OUT0 | SCIF<br>GCLK IN1  | LCDCA<br>SEG39 | CATB<br>SENSE18 |

| <u> </u> | GS         | PA24  | 24   | LCDC   | USBC          | USART2           |                 | 0010         | GCLK INT          | 35039          | CATB            |

| H2       | H2         | PA25  | 25   | VDDIO  | DM            | RXD              |                 |              |                   |                | SENSE19         |

|          |            |       |      |        | USBC          | USART2           |                 |              |                   |                | CATB            |

| G2       | G2         | PA26  | 26   | VDDIO  | DP            | TXD              |                 |              |                   |                | SENSE20         |

|          | <b>A</b> 7 | PA27  | 27   | LCDA   | SPI<br>MISO   | IISC<br>ISCK     | ABDACB<br>DAC0  | GLOC<br>IN4  | USART3<br>RTS     |                | CATB<br>SENSE0  |

|          | A6         | PA28  | 28   | LCDA   | SPI<br>Mosi   | IISC<br>ISDI     | ABDACB<br>DACN0 | GLOC<br>IN5  | USART3<br>CTS     |                | CATB<br>SENSE1  |

|          | В8         | PA29  | 29   | LCDA   | SPI<br>SCK    | IISC<br>IWS      | ABDACB<br>DAC1  | GLOC<br>IN6  | USART3<br>CLK     |                | CATB<br>SENSE2  |

|          | E8         | PA30  | 30   | LCDA   | SPI<br>NPCS0  | IISC<br>ISDO     | ABDACB<br>DACN1 | GLOC<br>IN7  | USART3<br>RXD     |                | CATB<br>SENSE3  |

|          | F8         | PA31  | 31   | LCDA   | SPI<br>NPCS1  | IISC<br>IMCK     | ABDACB<br>CLK   | GLOC<br>OUT1 | USART3<br>TXD     |                | CATB<br>DIS     |

| D2       | D2         | PB00  | 32   | VDDIN  | TWIMS1<br>TWD | USART0<br>RXD    |                 |              |                   |                | CATB<br>SENSE21 |

|          | - DE       | 1 500 | -    | VDDIIV | TWIMS1        | USART0           | EIC             |              |                   |                | CATB            |

| C2       | C2         | PB01  | 33   | VDDIN  | TWCK          | TXD              | EXTINT0         |              |                   |                | SENSE22         |

| E3       | E3         | PB02  | 34   | VDDANA | ADCIFE<br>AD3 | USART1<br>RTS    | ABDACB<br>DAC0  | IISC<br>ISCK | ACIFC<br>ACBN0    |                | CATB<br>SENSE23 |

| B1       | B1         | PB03  | 35   | VDDANA | ADCIFE<br>AD4 | USART1<br>CLK    | ABDACB<br>DACN0 | IISC<br>ISDI | ACIFC<br>ACBP0    |                | CATB<br>DIS     |

| A1       | A1         | PB04  | 36   | VDDANA | ADCIFE<br>AD5 | USART1<br>RXD    | ABDACB<br>DAC1  | IISC<br>ISDO | DACC<br>EXT TRIG0 |                | CATB<br>SENSE24 |

| D4       | D4         | PB05  | 37   | VDDANA | ADCIFE<br>AD6 | USART1<br>TXD    | ABDACB<br>DACN1 | IISC         |                   |                | CATB<br>SENSE25 |

|          |            |       |      |        | USART3        |                  | GLOC            | IISC         |                   | LCDCA          | САТВ            |

| B5       | B5         | PB06  | 38   | LCDA   | RTS           |                  | IN4             | IWS          |                   | SEG22          | SENSE26         |

| C6       | C6         | PB07  | 39   | LCDA   | USART3<br>CTS |                  | GLOC<br>IN5     | TC0<br>A0    |                   | LCDCA<br>SEG21 | CATB<br>SENSE27 |

| D6       | D6         | PB08  | 40   | LCDA   | USART3<br>CLK |                  | GLOC<br>IN6     | TC0<br>B0    |                   | LCDCA<br>SEG14 | CATB<br>SENSE28 |

| E6       | E6         | PB09  | 41   | LCDA   | USART3<br>RXD | PEVC<br>PAD EVT2 | GLOC<br>IN7     | TC0<br>A1    |                   | LCDCA<br>SEG15 | CATB<br>SENSE29 |

| F6       | F6         | PB10  | 42   | LCDA   | USART3<br>TXD | PEVC<br>PAD EVT3 | GLOC<br>OUT1    | TC0<br>B1    | SCIF<br>GCLK0     | LCDCA<br>SEG16 | CATB<br>SENSE30 |

| Н8       | Н8         | PB11  | 43   | LCDA   | USART0<br>CTS | SPI<br>NPCS2     |                 | TC0<br>A2    | SCIF<br>GCLK1     | LCDCA<br>SEG17 | CATB<br>SENSE31 |

|          |            |       |      | 2007   | USART0        | SPI              | PEVC            | TC0          | SCIF              | LCDCA          | CATB            |

| D5       | D5         | PB12  | 44   | LCDC   | RTS           | NPCS3            | PAD EVT0        | B2           | GCLK2             | SEG32          | DIS             |

Table 3-3.

64-pin GPIO Controller Function Multiplexing for WLCSP package (Sheet 3 of 3)

| ATSAM4LC | ATSAM4LS | Pin  | GPIO | Supply |               |              | GI               | PIO Functio | ns               |                |                |

|----------|----------|------|------|--------|---------------|--------------|------------------|-------------|------------------|----------------|----------------|

| WLCSP    | WLCSP    |      |      |        | Α             | В            | С                | D           | Е                | F              | G              |

| E5       | E5       | PB13 | 45   | LCDC   | USART0<br>CLK | SPI<br>NPCS1 | PEVC<br>PAD EVT1 | TC0<br>CLK0 | SCIF<br>GCLK3    | LCDCA<br>SEG33 | CATB<br>SENSE0 |

| F4       | F4       | PB14 | 46   | LCDC   | USART0<br>RXD | SPI<br>MISO  | TWIM3<br>TWD     | TC0<br>CLK1 | SCIF<br>GCLK IN0 | LCDCA<br>SEG36 | CATB<br>SENSE1 |

| H4       | H4       | PB15 | 47   | LCDC   | USART0<br>TXD | SPI<br>MOSI  | TWIM3<br>TWCK    | TC0<br>CLK2 | SCIF<br>GCLK IN1 | LCDCA<br>SEG37 | CATB<br>SENSE2 |

37

sor core and NVIC provides fast execution of interrupt service routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to suspend load-multiple and store-multiple operations. Interrupt handlers do not require wrapping in assembler code, removing any code overhead from the ISRs. A tail-chain optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep function enabling the entire device to be rapidly powered down while still retaining program state.

# 4.2 System level interface

The Cortex-M4 processor provides multiple interfaces using AMBA® technology to provide high speed, low latency memory accesses. It supports unaligned data accesses and implements atomic bit manipulation that enables faster peripheral controls, system spinlocks and thread-safe Boolean data handling.

The Cortex-M4 processor has an *memory protection unit* (MPU) that provides fine grain memory control, enabling applications to utilize multiple privilege levels, separating and protecting code, data and stack on a task-by-task basis. Such requirements are becoming critical in many embedded applications such as automotive.

# 4.3 Integrated configurable debug

The Cortex-M4 processor implements a complete hardware debug solution. This provides high system visibility of the processor and memory through either a traditional JTAG port or a 2-pin *Serial Wire Debug* (SWD) port that is ideal for microcontrollers and other small package devices.

For system trace the processor integrates an *Instrumentation Trace Macrocell* (ITM) alongside data watchpoints and a profiling unit. To enable simple and cost-effective profiling of the system events these generate, a *Serial Wire Viewer* (SWV) can export a stream of software-generated messages, data trace, and profiling information through a single pin.

The Flash Patch and Breakpoint Unit (FPB) provides 8 hardware breakpoint comparators that debuggers can use. The comparators in the FPB also provide remap functions of up to 8 words in the program code in the CODE memory region. This enables applications stored on a non-erasable, ROM-based microcontroller to be patched if a small programmable memory, for example flash, is available in the device. During initialization, the application in ROM detects, from the programmable memory, whether a patch is required. If a patch is required, the application programs the FPB to remap a number of addresses. When those addresses are accessed, the accesses are redirected to a remap table specified in the FPB configuration, which means the program in the non-modifiable ROM can be patched.

A specific Peripheral Debug (PDBG) register is implemented in the Private Peripheral Bus address map. This register allows the user to configure the behavior of some modules in debug mode.

mechanism can be useful for applications that only require the processor to run when an interrupt occurs.

Before entering the SLEEP mode, the user must configure:

- the SLEEP mode configuration field (BPM.PMCON.SLEEP), Refer to Table 7-1.

- the SCR.SLEEPDEEP bit to 0. (See the Power Management section in the ARM Cortex-M4 Processor chapter).

- the BPM.PMCON.RET bit to 0.

- the BPM.PMCON.BKUP bit to 0.

### 7.1.1.2 Exiting SLEEP mode

The NVIC wakes the system up when it detects any non-masked interrupt with sufficient priority to cause exception entry. The system goes back to the RUN mode from which the SLEEP mode was entered. The CPU and affected modules are restarted. Note that even if an interrupt is enabled in SLEEP mode, it will not trigger if the source module is not clocked.

#### 7.1.2 WAIT Mode and RETENTION Mode

The WAIT and RETENTION modes allow achieving very low power consumption while maintaining the Core domain powered-on. Internal SRAM and registers contents of the Core domain are preserved.

In these modes, all clocks are stopped except the 32kHz clocks (OSC32K, RC32K) which are kept running if enabled.

In RETENTION mode, the SleepWalking feature is not supported and must not be used.

## 7.1.2.1 Entering WAIT or RETENTION Mode

The WAIT or RETENTION modes are entered by executing the WFI instruction with the following settings:

- set the SCR.SLEEPDEEP bit to 1. (See the Power Management section in the ARM Cortex-M4 Processor chapter).

- set the BPM.PSAVE.BKUP bit to 0.

- set the BPM.PMCON.RET bit to RETENTION or WAIT mode.

SLEEPONEXIT feature is also available. See "Entering SLEEP mode" on page 56.

### 7.1.2.2 Exiting WAIT or RETENTION Mode

In WAIT or RETENTION modes, synchronous clocks are stopped preventing interrupt sources from triggering. To wakeup the system, asynchronous wake up sources (AST, EIC, USBC ...) should be enabled in the peripheral (refer to the documentation of the peripheral). The PM.AWEN (Asynchronous Wake Up Enable) register should also be enabled for all peripheral except for EIC and AST.

When the enabled asynchronous wake up event occurs and the system is waken-up, it will generate either:

- an interrupt on the PM WAKE interrupt line if enabled (Refer to Section 9. "Power Manager (PM)" on page 677). In that case, the PM.WCAUSE register indicates the wakeup source.

- or an interrupt directly from the peripheral if enabled (Refer to the section of the peripheral).

When waking up, the system goes back to the RUN mode mode from which the WAIT or RETENTION mode was entered.

### 8.7.5 Product Dependencies

### 8.7.5.1 I/O Lines

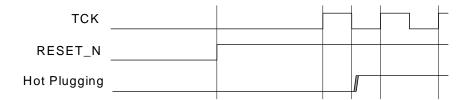

The TCK pin is dedicated to the EDP. The other debug port pins default after reset to their GPIO functionality and are automatically reassigned to the JTAG functionalities on detection of a debugger. In serial wire mode, TDI and TDO can be used as GPIO functions. Note that in serial wire mode TDO can be used as a single pin trace output.

### 8.7.5.2 Power Management

When a debugger is present, the connection is kept alive allowing debug operations. As a side effect, the power is never turned off. The hot plugging functionality is always available except when the system is in BACKUP Power Save Mode.

### 8.7.5.3 Clocks

The SWJ-DP uses the external TCK pin as its clock source. This clock must be provided by the external JTAG master device.

Some of the JTAG Instructions are used to access an Access Port (SMAP or AHB-AP). These instructions require the CPU clock to be running.

If the CPU clock is not present because the CPU is in a Power Save Mode where this clock is not provided, the Power Manager(PM) will automatically restore the CPU clock on detection of a debug access.

The RCSYS clock is used as CPU clock when the external reset is applied to ensure correct Access Port operations.

#### 8.7.6 Module Initialization

This module is enabled as soon as a TCK falling edge is detected when RESET\_N is not asserted (refer to Section 8.7.7 below). Moreover, the module is synchronously reseted as long as the TAP machine is in the TEST\_LOGIC\_RESET (TLR) state. It is advised asserting TMS at least 5 TCK clock periods after the debugger has been detected to ensure the module is in the TLR state prior to any operation. This module also has the ability to maintain the Cortex-M4 under reset (refer to the Section 8.7.8 "SMAP Core Reset Request Source" on page 70).

## 8.7.7 Debugger Hot Plugging

The TCK pin is dedicated to the EDP. After reset has been released, the EDP detects that a debugger has been attached when a TCK falling edge arises.

**Figure 8-4.** Debugger Hot Plugging Detection Timings Diagram

73

## 8.7.13 Security Restrictions

The SAM4L provide a security restrictions mechanism to lock access to the device. The device in the protected state when the Flash Security Bit is set. Refer to section Flash Controller for more details.

When the device is in the protected state the AHB-AP is locked. Full access to the AHB-AP is reenabled when the protected state is released by issuing a Chip Erase command. Note that the protected state will read as programmed only after the system has been reseted.

#### 8.7.13.1 Notation

Table 8-4 on page 73 shows bit patterns to be shifted in a format like "**p01**". Each character corresponds to one bit, and eight bits are grouped together for readability. The least significant bit is always shifted first, and the most significant bit shifted last. The symbols used are shown in Table 8-3.

Table 8-3. Symbol Description

| Symbol | Description                                                                       |

|--------|-----------------------------------------------------------------------------------|

| 0      | Constant low value - always reads as zero.                                        |

| 1      | Constant high value - always reads as one.                                        |

| р      | The chip protected state.                                                         |

| Х      | A don't care bit. Any value can be shifted in, and output data should be ignored. |

| е      | An error bit. Read as one if an error occurred, or zero if not.                   |

| b      | A busy bit. Read as one if the SMAP was busy, or zero if it was not.              |

| S      | Startup done bit. Read as one if the system has started-up correctly.             |

In many cases, it is not required to shift all bits through the data register. Bit patterns are shown using the full width of the shift register, but the suggested or required bits are emphasized using **bold** text. I.e. given the pattern "**01010101** xxxxxxxx xxxxxxxxxxxxx, the shift register is 32 bits, but the test or debug unit may choose to shift only 8 bits "**01010101**".

The following describes how to interpret the fields in the instruction description tables:

Table 8-4. Instruction Description

| Instruction     | Description                                                                                                                                                                                               |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IR input value  | Shows the bit pattern to shift into IR in the Shift-IR state in order to select this instruction. The pattern is show both in binary and in hexadecimal form for convenience.  Example: <b>1000</b> (0x8) |

| IR output value | Shows the bit pattern shifted out of IR in the Shift-IR state when this instruction is active.  Example: p00s                                                                                             |

- 1. Select the IR Scan path.

- 2. In Capture-IR: The IR output value is latched into the shift register.

- 3. In Shift-IR: The instruction register is shifted by the TCK input.

- 4. Return to Run-Test/Idle.

- 5. Select the DR Scan path.

- 6. In Capture-DR: The Data on the external pins are sampled into the boundary-scan chain.

- 7. In Shift-DR: The boundary-scan chain is shifted by the TCK input.

- 8. Return to Run-Test/Idle.

Table 8-6. SAMPLE\_PRELOAD Details

| Instructions    | Details                                          |

|-----------------|--------------------------------------------------|

| IR input value  | <b>0001</b> (0x1)                                |

| IR output value | p00s                                             |

| DR Size         | Depending on boundary-scan chain, see BSDL-file. |

| DR input value  | Depending on boundary-scan chain, see BSDL-file. |

| DR output value | Depending on boundary-scan chain, see BSDL-file. |

#### 8.7.14.3 INTEST

This instruction selects the boundary-scan chain as Data Register for testing internal logic in the device. The logic inputs are determined by the boundary-scan chain, and the logic outputs are captured by the boundary-scan chain. The device output pins are driven from the boundary-scan chain.

Starting in Run-Test/Idle, the INTEST instruction is accessed the following way:

- 1. Select the IR Scan path.

- 2. In Capture-IR: The IR output value is latched into the shift register.

- 3. In Shift-IR: The instruction register is shifted by the TCK input.

- 4. In Update-IR: The data from the boundary-scan chain is applied to the internal logic inputs.

- 5. Return to Run-Test/Idle.

- 6. Select the DR Scan path.

- 7. In Capture-DR: The data on the internal logic is sampled into the boundary-scan chain.

- 8. In Shift-DR: The boundary-scan chain is shifted by the TCK input.

- 9. In Update-DR: The data from the boundary-scan chain is applied to internal logic inputs.

- 10. Return to Run-Test/Idle.

Table 8-7.INTEST Details

| Instructions    | Details                                          |

|-----------------|--------------------------------------------------|

| IR input value  | <b>0100</b> (0x4)                                |

| IR output value | p001                                             |

| DR Size         | Depending on boundary-scan chain, see BSDL-file. |

| DR input value  | Depending on boundary-scan chain, see BSDL-file. |

| DR output value | Depending on boundary-scan chain, see BSDL-file. |

- 0: No bus error has been detected sincle last clear of this bit

- HCR: Hold Core reset

- 1: The Cortex-M4 core is held under reset

- 0: The Cortex-M4 core is not held under reset

- DONE: Operation done

- 1: At least one operation has terminated since last clear of this field

- 0: No operation has terminated since last clear of this field

Table 9-6. ATSAM4L4/2 Current consumption and Wakeup time for power scaling mode 0 and 2

| Mode                                   | Conditions                                 | T <sub>A</sub> | Typical<br>Wakeup Time | Тур  | Max <sup>(1)</sup> | Unit  |

|----------------------------------------|--------------------------------------------|----------------|------------------------|------|--------------------|-------|

| SLEEP0                                 | Switching mode                             | 25°C           | 9 * Main clock         | 3817 | 4033               |       |

| SLEEPU                                 | Switching mode                             | 85°C           | cycles                 | 3934 | 4174               |       |

| OLEED4                                 | Curitahing made                            | 25°C           | 9 * Main clock         | 2341 | 2477               |       |

| SLEEP1                                 | Switching mode                             | 85°C           | cycles + 500ns         | 2437 | 2585               |       |

| CI EEDO                                | Custohing                                  | 25°C           | 9 * Main clock         | 1758 | 1862               |       |

| SLEEP2                                 | Switching mode                             | 85°C           | cycles + 500ns         | 1847 | 1971               | ;<br> |

| SLEEP3                                 | Linear mode                                |                |                        | 51   | 60                 |       |

| \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | OSC32K and AST running Fast wake-up enable | 25°C           | 1.5µs<br>1.5µs         | 5.9  | 8.7                | μΑ    |

| WAIT                                   | OSC32K and AST stopped Fast wake-up enable |                |                        | 4.7  | 7.6                |       |

| RETENTION                              | OSC32K running<br>AST running at 1kHz      |                |                        | 3.1  | 5.1                |       |

|                                        | AST and OSC32K stopped                     |                |                        | 2.2  | 4.2                |       |

| BACKUP                                 | OSC32K running<br>AST running at 1kHz      |                |                        | 1.5  | 3.1                |       |

|                                        | AST and OSC32K stopped                     |                |                        | 0.9  | 1.7                |       |

<sup>1.</sup> These values are based on characterization. These values are not covered by test limits in production.

Table 9-7. ATSAM4L8 Current consumption and Wakeup time for power scaling mode 0 and 2

| Mode | Conditions                        | T <sub>A</sub> | Typical<br>Wakeup Time | Тур | Max <sup>(1)</sup> | Unit       |

|------|-----------------------------------|----------------|------------------------|-----|--------------------|------------|

|      | CPU running a Fibonacci algorithm | 25°C           | N/A                    | 319 | 343                |            |

|      | Linear mode                       | 85°C           | IN/A                   | 326 | 350                |            |

|      | CPU running a CoreMark algorithm  | 25°C           | N/A                    | 343 | 387                |            |

|      | Linear mode                       | 85°C           |                        | 351 | 416                | A /B 41 1— |

| RUN  | CPU running a Fibonacci algorithm | 25°C           | N/A                    | 181 | 198                | µA/MHz     |

|      | Switching mode                    | 85°C           |                        | 186 | 203                |            |

|      | CPU running a CoreMark algorithm  | 25°C           | N/A                    | 192 | 232                |            |

|      | Switching mode                    | 85°C           |                        | 202 | 239                |            |

**Table 9-11.** Typical Current Consumption by Peripheral in Power Scaling Mode 0 and 2 (1)

| Peripheral            | Typ Consumption Active | Unit   |

|-----------------------|------------------------|--------|

| IISC                  | 1.0                    |        |

| SPI                   | 1.9                    |        |

| TC                    | 6.3                    |        |

| TWIM                  | 1.5                    |        |

| TWIS                  | 1.2                    |        |

| USART                 | 8.5                    |        |

| ADCIFE <sup>(2)</sup> | 3.1                    |        |

| DACC                  | 1.3                    |        |

| ACIFC (2)             | 3.1                    |        |

| GLOC                  | 0.4                    |        |

| ABDACB                | 0.7                    |        |

| TRNG                  | 0.9                    |        |

| PARC                  | 0.7                    |        |

| CATB                  | 3.0                    |        |

| LCDCA                 | 4.4                    | μΑ/MHz |

| PDCA                  | 1.0                    |        |

| CRCCU                 | 0.3                    |        |

| USBC                  | 1.5                    |        |

| PEVC                  | 5.6                    |        |

| CHIPID                | 0.1                    |        |

| SCIF                  | 6.4                    |        |

| FREQM                 | 0.5                    |        |

| GPIO                  | 7.1                    |        |

| BPM                   | 0.9                    |        |

| BSCIF                 | 4.6                    |        |

| AST                   | 1.5                    |        |

| WDT                   | 1.4                    |        |

| EIC                   | 0.6                    |        |

| PICOUART              | 0.3                    |        |

These numbers are valid for the measured condition only and must not be extrapolated to other frequencies

# 9.5.4 .Peripheral Power Consumption in Power Scaling mode 1

The values in Table 9-13 are measured values of power consumption under the following conditions:

<sup>2.</sup> Includes the current consumption on VDDANA and ADVREFP.

Table 9-23.

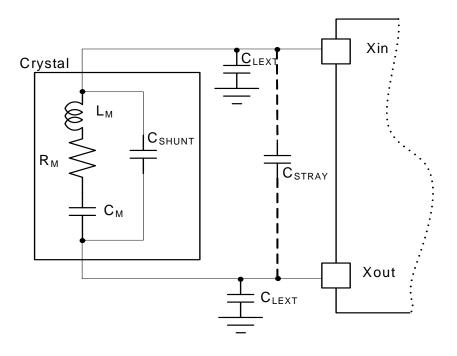

Crystal Oscillator Characteristics

| Symbol               | Parameter                                | Conditions                                        | Min | Тур      | Max | Unit   |

|----------------------|------------------------------------------|---------------------------------------------------|-----|----------|-----|--------|

| C <sub>L</sub>       | Crystal load capacitance <sup>(1)</sup>  |                                                   | 6   |          | 18  |        |

| C <sub>SHUNT</sub>   | Crystal shunt capacitance <sup>(1)</sup> |                                                   |     |          | 7   |        |

| C <sub>XIN</sub>     | Parasitic capacitor load <sup>(2)</sup>  | TQFP100 package                                   |     | 4.91     |     | pF     |

| C <sub>XOUT</sub>    | Parasitic capacitor load <sup>(2)</sup>  | TQFP100 package                                   |     | 3.22     |     |        |

| t <sub>STARTUP</sub> | Startup time <sup>(1)</sup>              | SCIF.OSCCTRL.GAIN = 2                             |     | 30000(3) |     | cycles |

|                      |                                          | Active mode, f = 0.6MHz,<br>SCIF.OSCCTRL.GAIN = 0 |     | 30       |     |        |

|                      |                                          | Active mode, f = 4MHz,<br>SCIF.OSCCTRL.GAIN = 1   |     | 130      |     |        |

| I <sub>OSC</sub>     | Current consumption <sup>(1)</sup>       | Active mode, f = 8MHz,<br>SCIF.OSCCTRL.GAIN = 2   |     | 260      |     | μΑ     |

|                      |                                          | Active mode, f = 16MHz,<br>SCIF.OSCCTRL.GAIN = 3  |     | 590      |     |        |

|                      |                                          | Active mode, f = 30MHz,<br>SCIF.OSCCTRL.GAIN = 4  |     | 960      |     |        |

- 1. These values are based on simulation. These values are not covered by test limits in production or characterization.

- 2. These values are based on characterization. These values are not covered by test limits in production.

- 3. Nominal crystal cycles.

Figure 9-3. Oscillator Connection

# 9.7.3 Phase Locked Loop (PLL) Characteristics

Table 9-26. Phase Locked Loop Characteristics

| Symbol               | Parameter                                      | Conditions                   | Min | Тур | Max | Unit   |

|----------------------|------------------------------------------------|------------------------------|-----|-----|-----|--------|

| f <sub>OUT</sub>     | Output frequency (1)                           | PLL is not availabe in PS1   | 48  |     | 240 | NAL I- |

| f <sub>IN</sub>      | Input frequency <sup>(1)</sup>                 |                              | 4   |     | 16  | MHz    |

|                      | fout=80MHz                                     |                              |     | 200 |     |        |

| I <sub>PLL</sub>     | Current consumption <sup>(1)</sup>             | fout=240MHz                  |     |     | 500 | μΑ     |

|                      | Startup time, from enabling                    | Wide Bandwidth mode disabled |     |     | 8   |        |

| t <sub>STARTUP</sub> | the PLL until the PLL is locked <sup>(1)</sup> | Wide Bandwidth mode enabled  |     |     | 30  | μs     |

<sup>1.</sup> These values are based on simulation. These values are not covered by test limits in production or characterization.

# 9.7.4 Digital Frequency Locked Loop (DFLL) Characteristics

Table 9-27.

Digital Frequency Locked Loop Characteristics

| Symbol            | Parameter                          | Conditions                                                                                     | Min  | Тур  | Max  | Unit |

|-------------------|------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|------|

| f <sub>OUT</sub>  | Output frequency (1)               | DFLL is not availabe in PS1                                                                    | 20   |      | 150  | MHz  |

| f <sub>REF</sub>  | Reference frequency <sup>(1)</sup> |                                                                                                | 8    |      | 150  | kHz  |

|                   |                                    | FINE lock, f <sub>REF</sub> = 32 kHz, SSG disabled <sup>(2)</sup>                              |      | 0.1  | 0.5  |      |

|                   | ,                                  | ACCURATE lock, f <sub>REF</sub> = 32 kHz, dither clk RCSYS/2, SSG disabled <sup>(2)</sup>      |      | 0.06 | 0.5  |      |

|                   | Accuracy <sup>(1)</sup>            | FINE lock, f <sub>REF</sub> = 8-150 kHz, SSG disabled <sup>(2)</sup>                           |      | 0.2  | 1    | %    |

|                   |                                    | ACCURATE lock, f <sub>REF</sub> = 8-150kHz,<br>dither clk RCSYS/2, SSG disabled <sup>(2)</sup> |      | 0.1  | 1    |      |

|                   |                                    | RANGE 0 96 to 220MHz<br>COARSE=0, FINE=0, DIV=0                                                | 430  | 509  | 545  |      |

|                   |                                    | RANGE 0 96 to 220MHz<br>COARSE=31, FINE=255, DIV=0                                             | 1545 | 1858 | 1919 |      |

|                   |                                    | RANGE 1 50 to 110MHz<br>COARSE=0, FINE=0, DIV=0                                                | 218  | 271  | 308  |      |

|                   | 5 (1)                              | RANGE 1 50 to 110MHz<br>COARSE=31, FINE=255, DIV=0                                             | 704  | 827  | 862  | •    |

| I <sub>DFLL</sub> | Power consumption <sup>(1)</sup>   | RANGE 2 25 to 55MHz<br>COARSE=0, FINE=0, DIV=1                                                 | 140  | 187  | 226  | μΑ   |

|                   |                                    | RANGE 2 25 to 55MHz<br>COARSE=31, FINE=255, DIV=1                                              | 365  | 441  | 477  |      |

|                   |                                    | RANGE 3 20 to 30MHz<br>COARSE=0, FINE=0, DIV=1                                                 | 122  | 174  | 219  |      |

|                   |                                    | RANGE 3 20 to 30MHz<br>COARSE=31, FINE=255, DIV=1                                              | 288  | 354  | 391  |      |

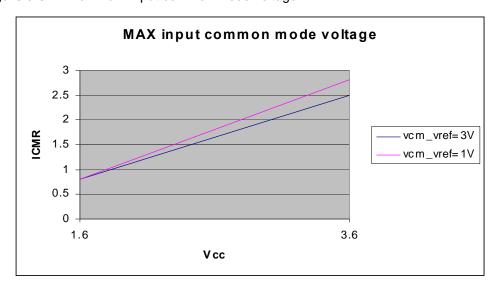

# 9.9.4 Analog- to Digital Converter Characteristics

Table 9-45. Operating conditions

| Symbol                                               | Parameter                                                  | Conditions                                                | Min  | Тур | Max               | Units  |

|------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|------|-----|-------------------|--------|

|                                                      | Temperature range                                          |                                                           | -40  |     | +85               | °C     |

|                                                      | Resolution (1)                                             | Max                                                       |      | 12  | 12 <sup>(2)</sup> | Bit    |

|                                                      | Sampling clock (3)                                         | Differential modes, Gain=1X                               | 5    |     | 300               | kHz    |

|                                                      | Sampling clock (-)                                         | Unipolar modes, Gain=1X                                   | 5    |     | 250               | KIZ    |

| f <sub>ADC</sub> ADC clock frequency <sup>(3)</sup>  | ADC clock fraguency(3)                                     | Differential modes                                        | 0.03 |     | 1.8               | MHz    |

|                                                      | Unipolar modes                                             | 0.03                                                      |      | 1.5 | IVITZ             |        |

| T <sub>SAMPLEHOLD</sub> Sampling time <sup>(3)</sup> | Campling time (3)                                          | Differential modes                                        | 16.5 |     | 277               |        |

|                                                      | Sampling time                                              | Unipolar modes                                            | 16.5 |     | 333               | μs     |

|                                                      | Conversion rate <sup>(1)</sup>                             | 1X gain, differential                                     |      |     | 300               | kSps   |

|                                                      | Internal channel conversion rate <sup>(3)</sup>            | V <sub>VDD</sub> /10, Bandgap and<br>Temperature channels |      |     | 125               | kSps   |

|                                                      |                                                            | 1X gain, (resolution/2)+gain (4)                          |      |     | 6                 |        |

|                                                      | Conversion time (latency) Differential mode (no windowing) | 2X and 4X gain                                            |      |     | 7                 |        |

|                                                      |                                                            | 8X and 16X gain                                           |      |     | 8                 | Cycles |

|                                                      |                                                            | 32X and 64X gain                                          |      |     | 9                 |        |

|                                                      |                                                            | 64X gain and unipolar                                     |      |     | 10                |        |

- 1. These values are based on characterization. These values are not covered by test limits in production

- 2. Single ended or using divide by two max resolution: 11 bits

- 3. These values are based on simulation. These values are not covered by test limits in production

- 4. See Figure 9-5

Figure 9-5. Maximum input common mode voltage

Table 9-48. Unipolar mode, gain=1

| PSRR <sup>(1)</sup>              | fVdd=100kHz, VDDIO=3.6V      | 62 |     | dB |

|----------------------------------|------------------------------|----|-----|----|

| FORK                             | fVdd=1MHz, VDDIO=3.6V        | 49 |     | иБ |

|                                  | VDDANA=3.6V                  | 1  | 2   |    |

| DC supply current <sup>(1)</sup> | VDDANA=1.6V,<br>ADVREFP=1.0V | 1  | 1.3 | mA |

- 1. These values are based on simulation. These values are not covered by test limits in production or characterization.

- These values are based on characterization and not tested in production, and valid for an input voltage between 10% to 90% of reference voltage.

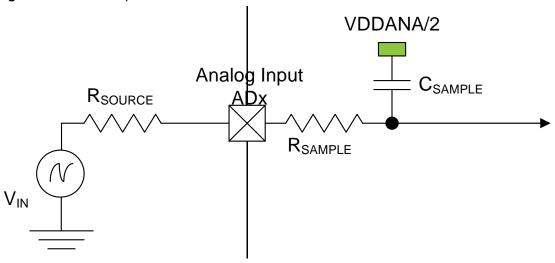

## 9.9.4.1 Inputs and Sample and Hold Acquisition Times

The analog voltage source must be able to charge the sample and hold (S/H) capacitor in the ADC in order to achieve maximum accuracy. Seen externally the ADC input consists of a resistor ( $R_{SAMPLE}$ ) and a capacitor ( $C_{SAMPLE}$ ). In addition, the source resistance ( $R_{SOURCE}$ ) must be taken into account when calculating the required sample and hold time. Figure 9-6 shows the ADC input channel equivalent circuit.

Figure 9-6. ADC Input

To achieve n bits of accuracy, the  $C_{SAMPLE}$  capacitor must be charged at least to a voltage of  $V_{CSAMPLE} \ge V_{IN} \times (1-2^{-(n+1)})$

The minimum sampling time  $t_{SAMPLEHOLD}$  for a given  $R_{SOURCE}$  can be found using this formula:

$$t_{SAMPLEHOLD} \ge (R_{SAMPLE} + R_{SOURCE}) \times (C_{SAMPLE}) \times (n+1) \times \ln(2)$$

for a 12 bits accuracy :  $t_{SAMPLEHOLD} \ge (R_{SAMPLE} + R_{SOURCE}) \times (C_{SAMPLE}) \times 9,02$

where

$$t_{SAMPLEHOLD} = \frac{1}{2 \times fADC}$$

SPCK, CPOL=0

SPCK, CPOL=1

NPCS

-SPI12SPI13SPI13SPI15NPCS

Figure 9-16. SPI Slave Mode, NPCS Timing

**Table 9-63.** SPI Timing, Slave Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions                | Min | Max | Units |

|--------|-----------------------------------|---------------------------|-----|-----|-------|

| SPI6   | SPCK falling to MISO delay        |                           | 19  | 47  |       |

| SPI7   | MOSI setup time before SPCK rises |                           | 0   |     |       |

| SPI8   | MOSI hold time after SPCK rises   |                           | 5.4 |     |       |

| SPI9   | SPCK rising to MISO delay         | V <sub>VDDIO</sub> from   | 19  | 46  |       |

| SPI10  | MOSI setup time before SPCK falls | 2.85V to 3.6V,<br>maximum | 0   |     |       |

| SPI11  | MOSI hold time after SPCK falls   | external                  | 5.3 |     | ns    |

| SPI12  | NPCS setup time before SPCK rises | capacitor = 40pF          | 4   |     |       |

| SPI13  | NPCS hold time after SPCK falls   |                           | 2.5 |     |       |

| SPI14  | NPCS setup time before SPCK falls |                           | 6   |     |       |

| SPI15  | NPCS hold time after SPCK rises   |                           | 1.1 |     |       |

Note: 1. These values are based on simulation. These values are not covered by test limits in production.

## Maximum SPI Frequency, Slave Input Mode

The maximum SPI slave input frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{CLKSPI}, \frac{1}{SPIn})$$

Where  $\mathit{SPIn}$  is the MOSI setup and hold time, SPI7 + SPI8 or SPI10 + SPI11 depending on CPOL and NCPHA. $f_{\mathit{CLKSPI}}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

## **Maximum SPI Frequency, Slave Output Mode**

The maximum SPI slave output frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{PINMAX}, \frac{1}{SPIn + t_{SETUP}})$$

# 10. Mechanical Characteristics

### 10.1 Thermal Considerations

## 10.1.1 Thermal Data

Table 10-1 summarizes the thermal resistance data depending on the package.

Table 10-1. Thermal Resistance Data

| Symbol        | Parameter                              | Condition | Package  | Тур  | Unit     |  |

|---------------|----------------------------------------|-----------|----------|------|----------|--|

| $\theta_{JA}$ | Junction-to-ambient thermal resistance | Still Air | TQFP100  | 48.1 | ·C/W     |  |

| $\theta_{JC}$ | Junction-to-case thermal resistance    |           | TQFP100  | 13.3 | .C/۷۷    |  |

| $\theta_{JA}$ | Junction-to-ambient thermal resistance | Still Air | VFBGA100 | 31.1 | CAM      |  |

| $\theta_{JC}$ | Junction-to-case thermal resistance    |           | VFBGA100 | 6.9  | ·C/W     |  |

| $\theta_{JA}$ | Junction-to-ambient thermal resistance | Still Air | WLCSP64  | 26.9 | 044      |  |

| $\theta_{JC}$ | Junction-to-case thermal resistance    |           | WLCSP64  | 0.2  | 0.2 ·C/W |  |

| $\theta_{JA}$ | Junction-to-ambient thermal resistance | Still Air | TQFP64   | 49.6 | CAM      |  |

| $\theta_{JC}$ | Junction-to-case thermal resistance    |           | TQFP64   | 13.5 | ·C/W     |  |

| $\theta_{JA}$ | Junction-to-ambient thermal resistance | Still Air | QFN64    | 22.0 | CAM      |  |

| $\theta_{JC}$ | Junction-to-case thermal resistance    |           | QFN64    | 1.3  | ·C/W     |  |

| $\theta_{JA}$ | Junction-to-ambient thermal resistance | Still Air | TQFP48   | 51.1 | ·C/W     |  |

| $\theta_{JC}$ | Junction-to-case thermal resistance    |           | TQFP48   |      |          |  |

| $\theta_{JA}$ | Junction-to-ambient thermal resistance | Still Air | QFN48    | 24.9 | CAN      |  |

| $\theta_{JC}$ | Junction-to-case thermal resistance    |           | QFN48    | 1.3  | ·C/W     |  |

### 10.1.2 Junction Temperature

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from the following:

1.

$$T_J = T_A + (P_D \times \theta_{JA})$$

2.

$$T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$$

where:

- θ<sub>JA</sub> = package thermal resistance, Junction-to-ambient (°C/W), provided in Table 10-1.

- θ<sub>JC</sub>= package thermal resistance, Junction-to-case thermal resistance (°C/W), provided in Table 10-1

- θ<sub>HFAT SINK</sub> = cooling device thermal resistance (°C/W), provided in the device datasheet.

- P<sub>D</sub> = device power consumption (W) estimated from data provided in Section 9.5 on page 103.

- T<sub>A</sub> = ambient temperature (°C).

From the first equation, the user can derive the estimated lifetime of the chip and decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature  $T_J$  in °C.

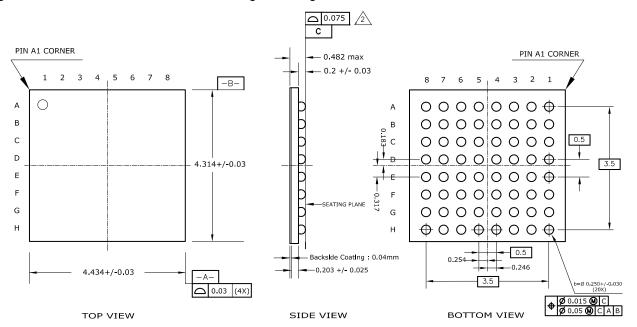

Figure 10-4. WLCSP64 SAM4LS4/2 Package Drawing

#### COMMON DIMENSIONS (Unit of Measure = mm)

| BALL | SIGNAL  | X COORD | Y COORD |

|------|---------|---------|---------|

| A1   | PB04    | 1.746   | 1.683   |

| A2   | GNDANA  | 1.246   | 1.683   |

| A3   | ADVREFP | 0.746   | 1.683   |

| A4   | VDDANA  | 0.246   | 1.683   |

| A5   | PA09    | -0.254  | 1.683   |

| A6   | PA28    | -0.754  | 1.683   |

| A7   | PA27    | -1.254  | 1.683   |

| A8   | PA12    | -1.754  | 1.683   |

| B1   | PB03    | 1.746   | 1.183   |

| B2   | XIN32   | 1.246   | 1.183   |

| В3   | XOUT32  | 0.746   | 1.183   |

| B4   | PA08    | 0.246   | 1.183   |

| B5   | PB06    | -0.254  | 1,183   |

| B6   | PA10    | -0.754  | 1.183   |

| B7   | PA11    | -1.254  | 1.183   |

| B8   | PA29    | -1.754  | 1.183   |

| C1   | VDDIN   | 1.746   | 0.683   |

| C2   | PB01    | 1,246   | 0.683   |

| C3   | PA05    | 0.746   | 0.683   |

| C4   | PA06    | 0,246   | 0,683   |

| C5   | PA07    | -0.254  | 0.683   |

| C6   | PB07    | -0.754  | 0.683   |

| BALL | SIGNAL  | X COORD | Y COORD |

|------|---------|---------|---------|

| C7   | PA13    | -1.254  | 0.683   |

| C8   | GNDI00  | -1.754  | 0.683   |

| D1   | VDDOUT  | 1.746   | 0.183   |

| D2   | PB00    | 1.246   | 0.183   |

| D3   | PA04    | 0.746   | 0.183   |

| D4   | PB05    | 0.246   | 0.183   |

| D5   | PB12    | -0.254  | 0.183   |

| D6   | PB08    | -0.754  | 0.183   |

| D7   | PA14    | -1.254  | 0.183   |

| D8   | VLCDIN  | -1.754  | 0.183   |

| E1   | GNDIN   | 1.746   | -0.317  |

| E2   | PA03    | 1.246   | -0.317  |

| E3   | PB02    | 0.746   | -0.317  |

| E4   | RESET_N | 0.246   | -0.317  |

| E5   | PB13    | -0.254  | -0.317  |

| E6   | PB09    | -0.754  | -0.317  |

| E7   | PA15    | -1.254  | -0.317  |

| E8   | PA30    | -1.754  | -0.317  |

| F1   | VDDCORE | 1.746   | -0.817  |

| F2   | TCK     | 1.246   | -0.817  |

| F3   | PA02    | 0.746   | -0.817  |

| F4   | PB14    | 0.246   | -0.817  |

|      |         |         |         |

| BALL | SIGNAL | X COORD | Y COORD |

|------|--------|---------|---------|

| F5   | PA22   | -0.254  | -0.817  |

| F6   | PB10   | -0.754  | -0.817  |

| F7   | PA16   | -1.254  | -0.817  |

| F8   | PA31   | -1.754  | -0.817  |

| G1   | GNDIO1 | 1.746   | -1.317  |

| G2   | PA26   | 1.246   | -1.317  |

| G3   | PA24   | 0.746   | -1.317  |

| G4   | PA00   | 0.246   | -1.317  |

| G5   | PA01   | -0.254  | -1.317  |

| G6   | PA19   | -0.754  | -1.317  |

| G7   | PA18   | -1.254  | -1.317  |

| G8   | PA17   | -1.754  | -1.317  |

| H1   | VDDIO1 | 1.746   | -1.817  |

| H2   | PA25   | 1.246   | -1.817  |

| H3   | PA23   | 0.746   | -1.817  |

| H4   | PB15   | 0.246   | -1.817  |

| H5   | PA21   | -0.254  | -1.817  |

| H6   | VDDI00 | -0.754  | -1.817  |

| H7   | PA20   | -1.254  | -1.817  |

| Н8   | PB11   | -1.754  | -1.817  |

|      |        |         |         |

|      |        |         |         |

Notes: 1. Dimension "b" is measured at the maximum ball diameter in a plane to the seating plane.

## Table 10-11. Device and Package Maximum Weight

| 14.8 mg |  |

|---------|--|

|---------|--|

# Table 10-12. Package Characteristics

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

|----------------------------|------|

## Table 10-13. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E1     |

<sup>2.</sup> Applied to whole wafer.

Table 11-3.

ATSAM4LC2 Sub Serie Ordering Information

| Ordering Code    | Flash<br>(Kbytes) | RAM<br>(Kbytes) | Package  | Conditioning | Package<br>Type | Temperature Operating Range |

|------------------|-------------------|-----------------|----------|--------------|-----------------|-----------------------------|

| ATSAM4LC2CA-AU   | 128               | 32              | TQFP100  | Tray         | Green           | Industrial -40°C to 85°C    |

| ATSAM4LC2CA-AUR  |                   |                 |          | Reel         |                 |                             |

| ATSAM4LC2CA-CFU  |                   |                 | VFBGA100 | Tray         |                 |                             |

| ATSAM4LC2CA-CFUR |                   |                 |          | Reel         |                 |                             |

| ATSAM4LC2BA-AU   |                   |                 | TQFP64   | Tray         |                 |                             |

| ATSAM4LC2BA-AUR  |                   |                 |          | Reel         |                 |                             |

| ATSAM4LC2BA-MU   |                   |                 | QFN64    | Tray         |                 |                             |

| ATSAM4LC2BA-MUR  |                   |                 |          | Reel         |                 |                             |

| ATSAM4LC2BA-UUR  |                   |                 | WLCSP64  | Reel         |                 |                             |

| ATSAM4LC2AA-AU   |                   |                 | TQFP48   | Tray         |                 |                             |

| ATSAM4LC2AA-AUR  |                   |                 |          | Reel         |                 |                             |

| ATSAM4LC2AA-MU   |                   |                 | QFN48    | Tray         |                 |                             |

| ATSAM4LC2AA-MUR  |                   |                 |          | Reel         |                 |                             |

Table 11-4.

ATSAM4LS8 Sub Serie Ordering Information

| Ordering Code    | Flash<br>(Kbytes) | RAM<br>(Kbytes) | Package  | Conditioning | Package<br>Type | Temperature Operating Range |

|------------------|-------------------|-----------------|----------|--------------|-----------------|-----------------------------|

| ATSAM4LS8CA-AU   |                   | 64              | TQFP100  | Tray         | Green           | Industrial -40°C to 85°C    |

| ATSAM4LS8CA-AUR  |                   |                 |          | Reel         |                 |                             |

| ATSAM4LS8CA-CFU  |                   |                 | VFBGA100 | Tray         |                 |                             |

| ATSAM4LS8CA-CFUR |                   |                 |          | Reel         |                 |                             |

| ATSAM4LS8BA-AU   |                   |                 | TQFP64   | Tray         |                 |                             |

| ATSAM4LS8BA-AUR  | 512               |                 |          | Reel         |                 |                             |

| ATSAM4LS8BA-MU   |                   |                 | QFN64    | Tray         |                 |                             |

| ATSAM4LS8BA-MUR  |                   |                 |          | Reel         |                 |                             |

| ATSAM4LS8BA-UUR  |                   |                 | WLCSP64  | Reel         |                 |                             |

| ATSAM4LS8AA-MU   |                   |                 | QFN48    | Tray         |                 |                             |

| ATSAM4LS8AA-MUR  |                   |                 |          | Reel         |                 |                             |