#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT        |

| Number of I/O              | 27                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.68V ~ 3.6V                                                             |

| Data Converters            | A/D 3x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 48-QFN (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4lc8aa-mu |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Feature                 | ATSAM4LS8/4/2C                                 | ATSAM4LS8/4/2B                                                                                                                                                                                                                                                                                    | ATSAM4LS8/4/2A |  |  |  |  |

|-------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|

| Timer/Counter Channels  | 6                                              | 6 3                                                                                                                                                                                                                                                                                               |                |  |  |  |  |

| Parallel Capture Inputs |                                                | 8                                                                                                                                                                                                                                                                                                 |                |  |  |  |  |

| Frequency Meter         |                                                | 1                                                                                                                                                                                                                                                                                                 |                |  |  |  |  |

| Watchdog Timer          |                                                | 1                                                                                                                                                                                                                                                                                                 |                |  |  |  |  |

| Power Manager           |                                                | 1                                                                                                                                                                                                                                                                                                 |                |  |  |  |  |

| Glue Logic LUT          |                                                | 2                                                                                                                                                                                                                                                                                                 | 1              |  |  |  |  |

| Oscillators             | Phase<br>Crysta<br>Cryst<br>RC<br>RC O<br>RC O | Digital Frequency Locked Loop 20-150MHz (DFLL)<br>Phase Locked Loop 48-240MHz (PLL)<br>Crystal Oscillator 0.6-30MHz (OSC0)<br>Crystal Oscillator 32kHz (OSC32K)<br>RC Oscillator 80MHz (RC80M)<br>RC Oscillator 4,8,12MHz (RCFAST)<br>RC Oscillator 115kHz (RCSYS)<br>RC Oscillator 32kHz (RC32K) |                |  |  |  |  |

| ADC                     | 15-channel                                     | 7-channel                                                                                                                                                                                                                                                                                         | 3-channel      |  |  |  |  |

| DAC                     |                                                | 1-channel                                                                                                                                                                                                                                                                                         |                |  |  |  |  |

| Analog Comparators      | 4                                              | 2                                                                                                                                                                                                                                                                                                 | 1              |  |  |  |  |

| CATB Sensors            | 32                                             | 32                                                                                                                                                                                                                                                                                                | 26             |  |  |  |  |

| USB                     |                                                | 1                                                                                                                                                                                                                                                                                                 |                |  |  |  |  |

| Audio Bitstream DAC     |                                                | 1                                                                                                                                                                                                                                                                                                 |                |  |  |  |  |

| IIS Controller          |                                                | 1                                                                                                                                                                                                                                                                                                 |                |  |  |  |  |

| Packages                | TQFP/VFBGA                                     | TQFP/QFN/<br>WLCSP                                                                                                                                                                                                                                                                                | TQFP/QFN       |  |  |  |  |

#### Table 2-3. ATSAM4LS Configuration Summary

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 3 of 4)

|     | ATSAM4LC |     | ATSAM4LS | Pin  | GPIO | Supply | GPIO Functions |                  |                  |              |                  |                |                 |

|-----|----------|-----|----------|------|------|--------|----------------|------------------|------------------|--------------|------------------|----------------|-----------------|

| QFN | VFBGA    | QFN | VFBGA    |      |      |        | Α              | В                | С                | D            | E                | F              | G               |

| 72  | G6       | 72  | G6       | PB08 | 40   | LCDA   | USART3<br>CLK  |                  | GLOC<br>IN6      | ТС0<br>В0    |                  | LCDCA<br>SEG14 | CATB<br>SENSE28 |

| 73  | G7       | 73  | G7       | PB09 | 41   | LCDA   | USART3<br>RXD  | PEVC<br>PAD EVT2 | GLOC<br>IN7      | ТС0<br>А1    |                  | LCDCA<br>SEG15 | CATB<br>SENSE29 |

| 74  | G8       | 74  | G8       | PB10 | 42   | LCDA   | USART3<br>TXD  | PEVC<br>PAD EVT3 | GLOC<br>OUT1     | TC0<br>B1    | SCIF<br>GCLK0    | LCDCA<br>SEG16 | CATB<br>SENSE30 |

| 75  | К9       | 75  | К9       | PB11 | 43   | LCDA   | USART0<br>CTS  | SPI<br>NPCS2     |                  | TC0<br>A2    | SCIF<br>GCLK1    | LCDCA<br>SEG17 | CATB<br>SENSE31 |

| 89  | E7       | 89  | E7       | PB12 | 44   | LCDC   | USART0<br>RTS  | SPI<br>NPCS3     | PEVC<br>PAD EVT0 | TC0<br>B2    | SCIF<br>GCLK2    | LCDCA<br>SEG32 | CATB<br>DIS     |

| 90  | E8       | 90  | E8       | PB13 | 45   | LCDC   | USART0<br>CLK  | SPI<br>NPCS1     | PEVC<br>PAD EVT1 | TC0<br>CLK0  | SCIF<br>GCLK3    | LCDCA<br>SEG33 | CATB<br>SENSE0  |

| 93  | D7       | 93  | D7       | PB14 | 46   | LCDC   | USART0<br>RXD  | SPI<br>MISO      | TWIM3<br>TWD     | TC0<br>CLK1  | SCIF<br>GCLK IN0 | LCDCA<br>SEG36 | CATB<br>SENSE1  |

| 94  | D8       | 94  | D8       | PB15 | 47   | LCDC   | USART0<br>TXD  | SPI<br>MOSI      | TWIM3<br>TWCK    | TC0<br>CLK2  | SCIF<br>GCLK IN1 | LCDCA<br>SEG37 | CATB<br>SENSE2  |

| 1   | A10      | 1   | A10      | PC00 | 64   | VDDIO  | SPI<br>NPCS2   | USART0<br>CLK    |                  | TC1<br>A0    |                  |                | CATB<br>SENSE3  |

| 2   | C8       | 2   | C8       | PC01 | 65   | VDDIO  | SPI<br>NPCS3   | USART0<br>RTS    |                  | TC1<br>B0    |                  |                | CATB<br>SENSE4  |

| 3   | С7       | 3   | C7       | PC02 | 66   | VDDIO  | SPI<br>NPCS1   | USART0<br>CTS    | USART0<br>RXD    | TC1<br>A1    |                  |                | CATB<br>SENSE5  |

| 4   | B7       | 4   | B7       | PC03 | 67   | VDDIO  | SPI<br>NPCS0   | EIC<br>EXTINT5   | USART0<br>TXD    | TC1<br>B1    |                  |                | CATB<br>SENSE6  |

| 9   | C5       | 9   | C5       | PC04 | 68   | VDDIO  | SPI<br>MISO    | EIC<br>EXTINT6   |                  | TC1<br>A2    |                  |                | CATB<br>SENSE7  |

| 10  | C6       | 10  | C6       | PC05 | 69   | VDDIO  | SPI<br>MOSI    | EIC<br>EXTINT7   |                  | TC1<br>B2    |                  |                | CATB<br>DIS     |

| 11  | В6       | 11  | B6       | PC06 | 70   | VDDIO  | SPI<br>SCK     | EIC<br>EXTINT8   |                  | TC1<br>CLK0  |                  |                | CATB<br>SENSE8  |

| 36  | F2       | 36  | F2       | PC07 | 71   | VDDANA | ADCIFE<br>AD7  | USART2<br>RTS    | PEVC<br>PAD EVT0 | TC1<br>CLK1  |                  |                | CATB<br>SENSE9  |

| 37  | E3       | 37  | E3       | PC08 | 72   | VDDANA | ADCIFE<br>AD8  | USART2<br>CLK    | PEVC<br>PAD EVT1 | TC1<br>CLK2  | USART2<br>CTS    |                | CATB<br>SENSE10 |

| 38  | F1       | 38  | F1       | PC09 | 73   | VDDANA | ADCIFE<br>AD9  | USART3<br>RXD    | ABDACB<br>DAC0   | IISC<br>ISCK | ACIFC<br>ACAN1   |                | CATB<br>SENSE11 |

| 39  | D4       | 39  | D4       | PC10 | 74   | VDDANA | ADCIFE<br>AD10 | USART3<br>TXD    | ABDACB<br>DACN0  | IISC<br>ISDI | ACIFC<br>ACAP1   |                | CATB<br>SENSE12 |

| 40  | E4       | 40  | E4       | PC11 | 75   | VDDANA | ADCIFE<br>AD11 | USART2<br>RXD    | PEVC<br>PAD EVT2 |              |                  |                | CATB<br>SENSE13 |

| 41  | F3       | 41  | F3       | PC12 | 76   | VDDANA | ADCIFE<br>AD12 | USART2<br>TXD    | ABDACB<br>CLK    | IISC<br>IWS  |                  |                | CATB<br>SENSE14 |

| 42  | F4       | 42  | F4       | PC13 | 77   | VDDANA | ADCIFE<br>AD13 | USART3<br>RTS    | ABDACB<br>DAC1   | IISC<br>ISDO | ACIFC<br>ACBN1   |                | CATB<br>SENSE15 |

| 43  | G1       | 43  | G1       | PC14 | 78   | VDDANA | ADCIFE<br>AD14 | USART3<br>CLK    | ABDACB<br>DACN1  | IISC<br>IMCK | ACIFC<br>ACBP1   |                | CATB<br>DIS     |

| 58  | J5       | 58  | J5       | PC15 | 79   | LCDA   | TC1<br>A0      |                  |                  | GLOC<br>IN4  |                  | LCDCA<br>SEG0  | CATB<br>SENSE16 |

| 4LC      | 4LS      |      |      | ×      |              |                | GI              | PIO Functio  | ns               |                |                 |

|----------|----------|------|------|--------|--------------|----------------|-----------------|--------------|------------------|----------------|-----------------|

| ATSAM4LC | ATSAM4LS | Pin  | GPIO | Supply | A            | В              | с               | D            | E                | F              | G               |

| 44       | 44       | PA24 | 24   | LCDC   | SPI<br>NPCS0 | TWIMS0<br>TWCK |                 | GLOC<br>OUT0 | SCIF<br>GCLK IN1 | LCDCA<br>SEG39 | CATB<br>SENSE18 |

| 46       | 46       | PA25 | 25   | VDDIO  | USBC<br>DM   | USART2<br>RXD  |                 |              |                  |                | CATB<br>SENSE19 |

| 47       | 47       | PA26 | 26   | VDDIO  | USBC<br>DP   | USART2<br>TXD  |                 |              |                  |                | CATB<br>SENSE20 |

|          | 25       | PA27 | 27   | LCDA   | SPI<br>MISO  | IISC<br>ISCK   | ABDACB<br>DAC0  | GLOC<br>IN4  | USART3<br>RTS    |                | CATB<br>SENSE0  |

|          | 26       | PA28 | 28   | LCDA   | SPI<br>MOSI  | IISC<br>ISDI   | ABDACB<br>DACN0 | GLOC<br>IN5  | USART3<br>CTS    |                | CATB<br>SENSE1  |

|          | 27       | PA29 | 29   | LCDA   | SPI<br>SCK   | IISC<br>IWS    | ABDACB<br>DAC1  | GLOC<br>IN6  | USART3<br>CLK    |                | CATB<br>SENSE2  |

|          | 30       | PA30 | 30   | LCDA   | SPI<br>NPCS0 | IISC<br>ISDO   | ABDACB<br>DACN1 | GLOC<br>IN7  | USART3<br>RXD    |                | CATB<br>SENSE3  |

|          | 31       | PA31 | 31   | LCDA   | SPI<br>NPCS1 | IISC<br>IMCK   | ABDACB<br>CLK   | GLOC<br>OUT1 | USART3<br>TXD    |                | CATB<br>DIS     |

Table 3-4.

48-pin GPIO Controller Function Multiplexing (Sheet 2 of 2)

## 3.2.2 Peripheral Functions

Each GPIO line can be assigned to one of several peripheral functions. The following table describes how the various peripheral functions are selected. The last listed function has priority in case multiple functions are enabled on the same pin.

| Table 3-5. | Peripheral Functions |

|------------|----------------------|

|------------|----------------------|

| Function                              | Description                               |

|---------------------------------------|-------------------------------------------|

| GPIO Controller Function multiplexing | GPIO and GPIO peripheral selection A to H |

| JTAG port connections                 | JTAG debug port                           |

| Oscillators                           | OSC0                                      |

## 3.2.3 JTAG Port Connections

If the JTAG is enabled, the JTAG will take control over a number of pins, irrespectively of the I/O Controller configuration.

|                    | JIAGEIII          | Jui             |                |                   |             |             |

|--------------------|-------------------|-----------------|----------------|-------------------|-------------|-------------|

| 48-pin<br>Packages | 64-pin<br>QFP/QFN | 64-pin<br>WLSCP | 100-pin<br>QFN | 100-ball<br>VFBGA | Pin<br>Name | JTAG<br>Pin |

| 10                 | 10                | E2              | 19             | B3                | PA03        | TMS         |

| 43                 | 59                | H3              | 95             | D6                | PA23        | TDO         |

| 44                 | 60                | G3              | 96             | D10               | PA24        | TDI         |

| 9                  | 9                 | F2              | 18             | B4                | тск         | тск         |

Table 3-6. JTAG Pinout

# 6. Power and Startup Considerations

# 6.1 Power Domain Overview

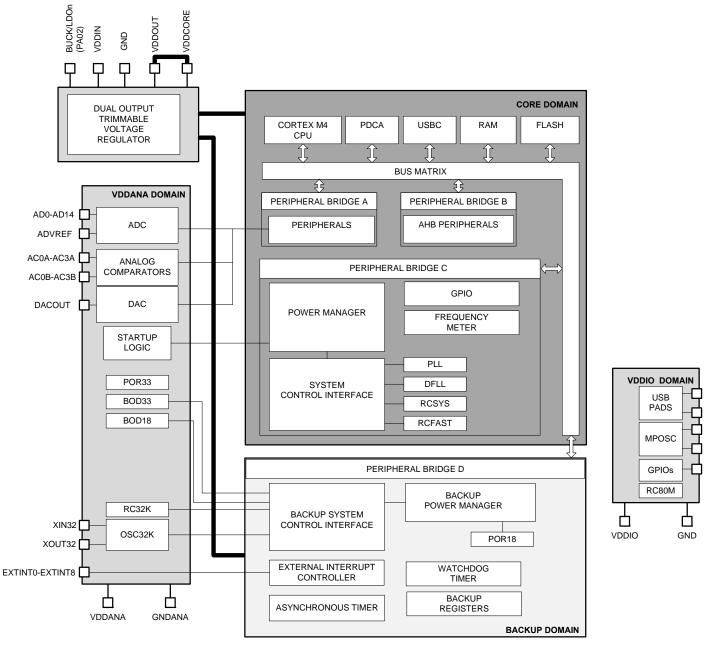

Figure 6-1. ATSAM4LS Power Domain Diagram

## 6.2 Power Supplies

The ATSAM4L8/L4/L2 has several types of power supply pins:

- VDDIO: Powers I/O lines, the general purpose oscillator (OSC), the 80MHz integrated RC oscillator (RC80M). Voltage is 1.68V to 3.6V.

- VLCDIN: (ATSAM4LC only) Powers the LCD voltage pump. Voltage is 1.68V to 3.6V.

- VDDIN: Powers the internal voltage regulator. Voltage is 1.68V to 3.6V.

- VDDANA: Powers the ADC, the DAC, the Analog Comparators, the 32kHz oscillator (OSC32K), the 32kHz integrated RC oscillator (RC32K) and the Brown-out detectors (BOD18 and BOD33). Voltage is 1.68V to 3.6V nominal.

- VDDCORE: Powers the core, memories, peripherals, the PLL, the DFLL, the 4MHz integrated RC oscillator (RCFAST) and the 115kHz integrated RC oscillator (RCSYS).

- VDDOUT is the output voltage of the regulator and must be connected with or without an inductor to VDDCORE.

The ground pins GND are common to VDDCORE, VDDIO, and VDDIN. The ground pin for VDDANA is GNDANA.

For decoupling recommendations for the different power supplies, refer to the schematic document.

## 6.2.1 Voltage Regulator

An embedded voltage regulator supplies all the digital logic in the Core and the Backup power domains.

The regulator has two functionnal mode depending of BUCK/LDOn (PA02) pin value. When this pin is low, the regulator is in linear mode and VDDOUT must be connected to VDDCORE externally. When this pin is high, it behaves as a switching regulator and an inductor must be placed between VDDOUT and VDDCORE. The value of this pin is sampled during the power-up phase when the Power On Reset 33 reaches  $V_{POT+}$  (Section 9.9 "Analog Characteristics" on page 129)

Its output voltages in the Core domain ( $V_{CORE}$ ) and in the Backup domain ( $V_{BKUP}$ ) are always equal except in Backup mode where the Core domain is not powered ( $V_{CORE}$ =0). The Backup domain is always powered. The voltage regulator features three different modes:

- Normal mode: the regulator is configured as linear or switching regulator. It can support all different Run and Sleep modes.

- Low Power (LP) mode: the regulator consumes little static current. It can be used in Wait modes.

- Ultra Low Power (ULP) mode: the regulator consumes very little static current. It is dedicated to Retention and Backup modes. In Backup mode, the regulator only supplies the backup domain.

## 6.2.2 Typical Powering Schematics

The ATSAM4L8/L4/L2 supports the Single supply mode from 1.68V to 3.6V. Depending on the input voltage range and on the final application frequency, it is recommended to use the following table in order to choose the most efficient power strategy

|                                             | VDDIN Voltage      |                                                                 |                             |                                                                                                                                           |       |

|---------------------------------------------|--------------------|-----------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                                             | 1.68V 1.8          | 30V 2.00V                                                       | v 2.                        | 30V                                                                                                                                       | 3.60V |

| Switching Mode<br>(BUCK/LDOn<br>(PA02) =1)  | N,                 |                                                                 | ossible but<br>ot efficient | Optimal power efficiency                                                                                                                  | ,     |

| Linear Mode<br>(BUCK/LDOn<br>(PA02) =0)     | Optin              | nal power effi                                                  | ciency                      | Possible but not efficien                                                                                                                 | t     |

| F <sub>CPUMAX</sub>                         | 12MHz              |                                                                 | U                           | p to 36MHz In PS0<br>p to 12MHz in PS1<br>p to 48MHz in PS2                                                                               |       |

| PowerScaling                                | PS1 <sup>(1)</sup> |                                                                 |                             | ALL                                                                                                                                       |       |

| Typical power<br>consumption in<br>RUN mode |                    | Hz @ F <sub>CPU</sub> =12MHz(<br>Hz @ F <sub>CPU</sub> = 48MHz( |                             | х         100µA/MHz @ F <sub>CPU</sub> =12MHz(PS1) @ V <sub>VD</sub> х         180µA/MHz @ F <sub>CPU</sub> =48MHz(PS2) @ V <sub>VD</sub> |       |

| Typical power<br>consumption in<br>RET mode |                    |                                                                 | 1                           | .5μΑ                                                                                                                                      |       |

Figure 6-3. Efficient power strategy:

Note 1. The SAM4L boots in PS0 on RCSYS(115kHz), then the application must switch to PS1 before running on higher frequency (<12MHz)

- Set the clock frequency to be supported in both power configurations.

- Set the high speed read mode of the FLASH to be supported in both power scaling configurations

- Only relevant when entering or exiting BPM.PMCON.PS=2

- Configure the BPM.PMCON.PS field to the new power configuration.

- Set the BPM.PMCON.PSCREQ bit to one.

- Disable all the interrupts except the PM WCAUSE interrupt and enable only the PSOK asynchronous event in the AWEN register of PM.

- Execute the WFI instruction.

- WAIT for PM interrupt.

The new power configuration is reached when the system is waken up by the PM interrupt thanks to the PSOK event.

By default, all features are available in all Power Scaling modes. However some specific features are not available in PS1 (BPM.PMCON.PS=1) mode :

- USB

- DFLL

- PLL

- Programming/Erasing in Flash

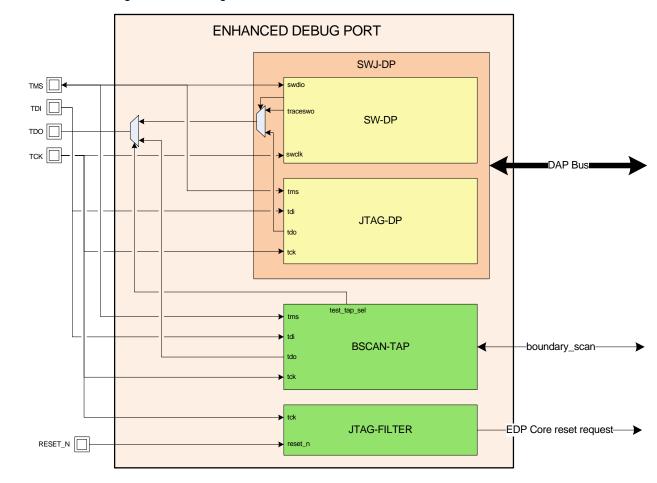

# 8.7.3 Block Diagram

Figure 8-3. Enhanced Debug Port Block Diagram

## 8.7.4 I/O Lines Description

| Table 8-1. | I/O Lines Description |

|------------|-----------------------|

|------------|-----------------------|

| Name         |      | JTAG Debug Port   |      | SWD Debug Port              |

|--------------|------|-------------------|------|-----------------------------|

|              | Туре | Description       | Туре | Description                 |

| TCK/SWCLK    | I    | Debug Clock       | I    | Serial Wire Clock           |

| TDI          | I    | Debug Data in     | -    | NA                          |

| TDO/TRACESWO | 0    | Debug Data Out    | 0    | Trace asynchronous Data Out |

| TMS/SWDIO    | I    | Debug Mode Select | I/O  | Serial Wire Input/Output    |

| RESET_N      | I    | Reset             | I    | Reset                       |

Atmel

## 8.7.5 Product Dependencies

### 8.7.5.1 I/O Lines

The TCK pin is dedicated to the EDP. The other debug port pins default after reset to their GPIO functionality and are automatically reassigned to the JTAG functionalities on detection of a debugger. In serial wire mode, TDI and TDO can be used as GPIO functions. Note that in serial wire mode TDO can be used as a single pin trace output.

### 8.7.5.2 Power Management

When a debugger is present, the connection is kept alive allowing debug operations. As a side effect, the power is never turned off. The hot plugging functionality is always available except when the system is in BACKUP Power Save Mode.

### 8.7.5.3 Clocks

The SWJ-DP uses the external TCK pin as its clock source. This clock must be provided by the external JTAG master device.

Some of the JTAG Instructions are used to access an Access Port (SMAP or AHB-AP). These instructions require the CPU clock to be running.

If the CPU clock is not present because the CPU is in a Power Save Mode where this clock is not provided, the Power Manager(PM) will automatically restore the CPU clock on detection of a debug access.

The RCSYS clock is used as CPU clock when the external reset is applied to ensure correct Access Port operations.

### 8.7.6 Module Initialization

This module is enabled as soon as a TCK falling edge is detected when RESET\_N is not asserted (refer to Section 8.7.7 below). Moreover, the module is synchronously reseted as long as the TAP machine is in the TEST\_LOGIC\_RESET (TLR) state. It is advised asserting TMS at least 5 TCK clock periods after the debugger has been detected to ensure the module is in the TLR state prior to any operation. This module also has the ability to maintain the Cortex-M4 under reset (refer to the Section 8.7.8 "SMAP Core Reset Request Source" on page 70).

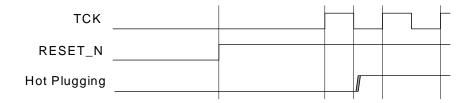

### 8.7.7 Debugger Hot Plugging

The TCK pin is dedicated to the EDP. After reset has been released, the EDP detects that a debugger has been attached when a TCK falling edge arises.

Figure 8-4. Debugger Hot Plugging Detection Timings Diagram

| Instruction     | Description                                                                                                    |

|-----------------|----------------------------------------------------------------------------------------------------------------|

| DR Size         | Shows the number of bits in the data register chain when this instruction is active.<br>Example: 32 bits       |

| DR input value  | Shows which bit pattern to shift into the data register in the Shift-DR state when this instruction is active. |

| DR output value | Shows the bit pattern shifted out of the data register in the Shift-DR state when this instruction is active.  |

Table 8-4.

Instruction Description (Continued)

### 8.7.14 JTAG Instructions

Refer to the ARM Debug Interface v5.1 Architecture Specification for more details on ABORT, DPACC, APACC and IDCODE instructions.

#### 8.7.14.1 EXTEST

This instruction selects the boundary-scan chain as Data Register for testing circuitry external to the chip package. The contents of the latched outputs of the boundary-scan chain is driven out as soon as the JTAG IR-register is loaded with the EXTEST instruction.

Starting in Run-Test/Idle, the EXTEST instruction is accessed the following way:

- 1. Select the IR Scan path.

- 2. In Capture-IR: The IR output value is latched into the shift register.

- 3. In Shift-IR: The instruction register is shifted by the TCK input.

- 4. In Update-IR: The data from the boundary-scan chain is applied to the output pins.

- 5. Return to Run-Test/Idle.

- 6. Select the DR Scan path.

- 7. In Capture-DR: The data on the external pins is sampled into the boundary-scan chain.

- 8. In Shift-DR: The boundary-scan chain is shifted by the TCK input.

- 9. In Update-DR: The data from the scan chain is applied to the output pins.

- 10. Return to Run-Test/Idle.

|  | Table 8 | -5. | EXTE | EST | Details |

|--|---------|-----|------|-----|---------|

|--|---------|-----|------|-----|---------|

| Instructions    | Details                                          |

|-----------------|--------------------------------------------------|

| IR input value  | <b>0000</b> (0x0)                                |

| IR output value | p00s                                             |

| DR Size         | Depending on boundary-scan chain, see BSDL-file. |

| DR input value  | Depending on boundary-scan chain, see BSDL-file. |

| DR output value | Depending on boundary-scan chain, see BSDL-file. |

## 8.7.14.2 SAMPLE\_PRELOAD

This instruction takes a snap-shot of the input/output pins without affecting the system operation, and pre-loading the scan chain without updating the DR-latch. The boundary-scan chain is selected as Data Register.

Starting in Run-Test/Idle, the Device Identification register is accessed in the following way:

| 8.9.11.6 Data F<br>Name: | Register<br>DATA |    |      |    |    |    |

|--------------------------|------------------|----|------|----|----|----|

| Access Type:             | Read/Write       |    |      |    |    |    |

| Offset:                  | 0x14             |    |      |    |    |    |

| Reset Value:             | 0x00000000       |    |      |    |    |    |

|                          |                  |    |      |    |    |    |

| 31                       | 30               | 29 | 28   | 27 | 26 | 25 |

|                          |                  |    | DATA |    |    |    |

|                          |                  |    |      |    |    |    |

| 23                       | 22               | 21 | 20   | 19 | 18 | 17 |

|                          |                  |    | DATA |    |    |    |

|                          |                  |    |      |    |    |    |

| 15                       | 14               | 13 | 12   | 11 | 10 | 9  |

|                          |                  |    | DATA |    |    |    |

|                          |                  |    |      |    |    |    |

| 7                        | 6                | 5  | 4    | 3  | 2  | 1  |

|                          |                  |    | DATA |    |    |    |

• DATA: Generic data register

| 8.9.11.7           | Module Version |

|--------------------|----------------|

| Name:              | VERSION        |

| Access Type        | e: Read-Only   |

| Offset:            | 0x28           |

| <b>Reset Value</b> | -              |

| 31 | 30      | 29 | 28 | 27 | 26  | 25   | 24 |  |  |

|----|---------|----|----|----|-----|------|----|--|--|

| -  | -       | -  | -  | -  | -   | -    | -  |  |  |

|    |         |    |    |    |     |      |    |  |  |

| 23 | 22      | 21 | 20 | 19 | 18  | 17   | 16 |  |  |

| -  | -       | -  | -  |    | VAR | ANT  |    |  |  |

|    |         |    |    |    |     |      |    |  |  |

| 15 | 14      | 13 | 12 | 11 | 10  | 9    | 8  |  |  |

| -  | -       | -  | -  |    | VER | SION |    |  |  |

|    |         |    |    |    |     |      |    |  |  |

| 7  | 6       | 5  | 4  | 3  | 2   | 1    | 0  |  |  |

|    | VERSION |    |    |    |     |      |    |  |  |

#### • VARIANT: Variant number

Reserved. No functionality associated.

## • VERSION: Version number

Version number of the module. No functionality associated.

| RCSYS<br>(MCSEL = 0) | Power scaling mode 1                                         |           | 0.115 | 978 |        |

|----------------------|--------------------------------------------------------------|-----------|-------|-----|--------|

|                      | Dever eesting mode 4                                         |           | 0.5   | 354 |        |

| OSC0                 | Power scaling mode 1                                         |           | 12    | 114 |        |

| (MCSEL = 1)          | Power scaling mode 0                                         |           | 12    | 228 |        |

|                      | Power scaling mode 0                                         |           | 30    | 219 |        |

| OSC0                 | Power scaling mode 1                                         |           | 0.6   | 292 |        |

| (MCSEL = 1)          | Power scaling mode 1                                         |           | 12    | 111 | μΑ/MHz |

| External Clock       | Power scaling mode 0                                         |           | 12    | 193 |        |

| (MODE=0)             | Power scaling mode 2                                         |           | 50    | 194 |        |

| PLL                  | Power scaling mode 2                                         | Switching | 40    | 188 |        |

| (MCSEL = 2)          | Input Freq = 4MHz from OSC0                                  | Mode      | 50    | 185 |        |

| DFLL                 | Power scaling mode 0<br>Input Freq = 32kHz from OSC32K       |           | 20    | 214 |        |

| (MCSEL = 3)          | Power scaling mode 2<br>Input Freq = 32kHz from OSC32K       |           | 50    | 195 |        |

| RC1M<br>(MCSEL = 4)  | C1M<br>MCSEL = 4) Power scaling mode 1                       |           | 1     | 267 |        |

| RCFAST               |                                                              |           | 4     | 153 |        |

| (MCSEL = 5)          | RCFAST frequency is configurable from 4 to 12MHz             |           | 12    | 114 |        |

| RC80M<br>(MCSEL = 6) | Power scaling mode 2<br>f <sub>CPU</sub> = RC80M / 2 = 40MHz |           | 40    | 211 |        |

| Table 9-10. | Typical Power Consumption running CoreMark on CPU clock sources <sup>(1)</sup> |

|-------------|--------------------------------------------------------------------------------|

|             | i jpicari enerie enerie ann piciri ranning e erennant en er e ereen eeu        |

1. These values are based on characterization. These values are not covered by test limits in production.

Table 9-50. Analog Comparator Characteristics

| Symbol               | Parameter                        | Conditions                                                                           | Min | Тур | Max  | Units |

|----------------------|----------------------------------|--------------------------------------------------------------------------------------|-----|-----|------|-------|

|                      |                                  | $V_{ACREFN}$ =0.1V to VDDIO-0.1V,<br>hysteresis = 1 <sup>(2)</sup><br>Fast mode      | 10  |     | 55   | mV    |

|                      | Hysteresis <sup>(1)</sup>        | $V_{ACREFN}$ =0.1V to VDDIO-0.1V,<br>hysteresis = 1 <sup>(2)</sup><br>Low power mode | 10  |     | 68   | mV    |

|                      |                                  | $V_{ACREFN} = 0.1V$ to VDDIO-0.1V,<br>hysteresis = $2^{(2)}$<br>Fast mode            | 26  |     | 83   | mV    |

|                      |                                  | $V_{ACREFN} = 0.1V$ to VDDIO-0.1V,<br>hysteresis = $2^{(2)}$<br>Low power mode       | 19  |     | 91   | mV    |

|                      |                                  | $V_{ACREFN}$ =0.1V to VDDIO-0.1V,<br>hysteresis = $3^{(2)}$<br>Fast mode             | 43  |     | 106  | mV    |

|                      |                                  | $V_{ACREFN} = 0.1V$ to VDDIO-0.1V,<br>hysteresis = $3^{(2)}$<br>Low power mode       | 32  |     | 136  | mV    |

|                      | Dranagation dalay (1)            | Changes for V <sub>ACM</sub> =VDDIO/2<br>100mV Overdrive<br>Fast mode                |     |     | 67   | ns    |

|                      | Propagation delay <sup>(1)</sup> | Changes for V <sub>ACM</sub> =VDDIO/2<br>100mV Overdrive<br>Low power mode           |     |     | 315  | ns    |

|                      | Startup time <sup>(1)</sup>      | Enable to ready delay<br>Fast mode                                                   |     |     | 1.19 | μs    |

| t <sub>startup</sub> |                                  | Enable to ready delay<br>Low power mode                                              |     |     | 3.61 | μs    |

|                      | Channel current                  | Low power mode, no hysteresis                                                        |     | 4.9 | 8.7  | μA    |

| I <sub>AC</sub>      | consumption <sup>(3)</sup>       | Fast mode, no hysteresis                                                             |     | 63  | 127  | μΑ    |

1. These values are based on characterization. These values are not covered by test limits in production

2. HYSTAC.CONFn.HYS field, refer to the Analog Comparator Interface chapter

3. These values are based on simulation. These values are not covered by test limits in production or characterization

- Atmel

# Table 9-54. USART0 in SPI Mode Timing, Master Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions                                    | Min                                         | Мах    | Units |

|--------|-----------------------------------|-----------------------------------------------|---------------------------------------------|--------|-------|

| USPI0  | MISO setup time before SPCK rises |                                               | 123.2 + t <sub>SAMPLE</sub> <sup>(2)</sup>  |        |       |

| USPI1  | MISO hold time after SPCK rises   | V <sub>VDDIO</sub> from                       | 24.74 -t <sub>SAMPLE</sub> <sup>(2)</sup>   |        |       |

| USPI2  | SPCK rising to MOSI delay         | <ul> <li>3.0V to 3.6V,<br/>maximum</li> </ul> |                                             | 513.56 |       |

| USPI3  | MISO setup time before SPCK falls | external                                      | 125.99 + t <sub>SAMPLE</sub> <sup>(2)</sup> |        | ns    |

| USPI4  | MISO hold time after SPCK falls   | capacitor =<br>40pF                           | 24.74 -t <sub>SAMPLE</sub> <sup>(2)</sup>   |        |       |

| USPI5  | SPCK falling to MOSI delay        |                                               |                                             | 516.55 |       |

# Table 9-55. USART1 in SPI Mode Timing, Master Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions                 | Min                                        | Max    | Units |

|--------|-----------------------------------|----------------------------|--------------------------------------------|--------|-------|

| USPI0  | MISO setup time before SPCK rises |                            | 69.28 + t <sub>SAMPLE</sub> <sup>(2)</sup> |        |       |

| USPI1  | MISO hold time after SPCK rises   | V <sub>VDDIO</sub> from    | 25.75 -t <sub>SAMPLE</sub> <sup>(2)</sup>  |        |       |

| USPI2  | SPCK rising to MOSI delay         | 3.0 V to 3.6 V,<br>maximum |                                            | 99.66  |       |

| USPI3  | MISO setup time before SPCK falls | external                   | 73.12 + t <sub>SAMPLE</sub> <sup>(2)</sup> |        | ns    |

| USPI4  | MISO hold time after SPCK falls   | capacitor = 40pF           | 28.10 -t <sub>SAMPLE</sub> <sup>(2)</sup>  |        |       |

| USPI5  | SPCK falling to MOSI delay        |                            |                                            | 102.01 |       |

# Table 9-56. USART2 in SPI Mode Timing, Master Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions               | Min                                        | Max    | Units |

|--------|-----------------------------------|--------------------------|--------------------------------------------|--------|-------|

| USPI0  | MISO setup time before SPCK rises |                          | 69.09 + t <sub>SAMPLE</sub> <sup>(2)</sup> |        |       |

| USPI1  | MISO hold time after SPCK rises   | V <sub>VDDIO</sub> from  | 26.52 -t <sub>SAMPLE</sub> <sup>(2)</sup>  |        |       |

| USPI2  | SPCK rising to MOSI delay         | 3.0V to 3.6V,<br>maximum |                                            | 542.96 |       |

| USPI3  | MISO setup time before SPCK falls | external                 | 72.55 + t <sub>SAMPLE</sub> <sup>(2)</sup> |        | ns    |

| USPI4  | MISO hold time after SPCK falls   | capacitor = 40pF         | 28.37 -t <sub>SAMPLE</sub> <sup>(2)</sup>  |        |       |

| USPI5  | SPCK falling to MOSI delay        |                          |                                            | 544.80 | ]     |

## Table 9-57. USART3 in SPI Mode Timing, Master Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions                               | Min                                         | Мах   | Units |

|--------|-----------------------------------|------------------------------------------|---------------------------------------------|-------|-------|

| USPI0  | MISO setup time before SPCK rises |                                          | 147.24 + t <sub>SAMPLE</sub> <sup>(2)</sup> |       |       |

| USPI1  | MISO hold time after SPCK rises   | V <sub>VDDIO</sub> from                  | 25.80 -t <sub>SAMPLE</sub> <sup>(2)</sup>   |       |       |

| USPI2  | SPCK rising to MOSI delay         | - 3.0V to 3.6V,<br>maximum               |                                             | 88.23 |       |

| USPI3  | MISO setup time before SPCK falls | external                                 | 154.9 + t <sub>SAMPLE</sub> <sup>(2)</sup>  |       | ns    |

| USPI4  | MISO hold time after SPCK falls   | <ul> <li>capacitor =<br/>40pF</li> </ul> | 26.89 -t <sub>SAMPLE</sub> <sup>(2)</sup>   |       |       |

| USPI5  | SPCK falling to MOSI delay        |                                          |                                             | 89.32 |       |

Notes: 1. These values are based on simulation. These values are not covered by test limits in production.

Where:

$$t_{SAMPLE} = t_{SPCK} - \left( \left[ \frac{t_{SPCK}}{2 \times t_{CLKUSART}} \right] \frac{1}{2} \right) \times t_{CLKUSART} \right)$$

2.

Where *SPIn* is the MISO delay, SPI6 or SPI9 depending on CPOL and NCPHA.  $t_{SETUP}$  is the SPI master setup time. refer to the SPI master datasheet for  $t_{SETUP}$ .  $f_{PINMAX}$  is the maximum frequency of the SPI pins. refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

## 9.10.4 TWIM/TWIS Timing

Figure 9-64 shows the TWI-bus timing requirements and the compliance of the device with them. Some of these requirements ( $t_r$  and  $t_f$ ) are met by the device without requiring user intervention. Compliance with the other requirements ( $t_{HD-STA}$ ,  $t_{SU-STA}$ ,  $t_{SU-STO}$ ,  $t_{HD-DAT}$ ,  $t_{SU-DAT-TWI}$ ,  $t_{LOW-TWI}$ ,  $t_{HIGH}$ , and  $f_{TWCK}$ ) requires user intervention through appropriate programming of the relevant TWIM and TWIS user interface registers. refer to the TWIM and TWIS sections for more information.

|                         |                                 |                         | Minim                  | num                 | Maximum            |                                               |      |

|-------------------------|---------------------------------|-------------------------|------------------------|---------------------|--------------------|-----------------------------------------------|------|

| Symbol                  | Parameter                       | Mode                    | Requirement            | Device              | Requirement        | Device                                        | Unit |

|                         |                                 | Standard <sup>(1)</sup> | -                      |                     | 10                 | 00                                            |      |

| t <sub>r</sub>          | TWCK and TWD rise time          | Fast <sup>(1)</sup>     | 20 + 0                 | .1C <sub>b</sub>    | 30                 | 00                                            | ns   |

|                         |                                 | Standard                | -                      |                     | 30                 | 00                                            |      |

| t <sub>f</sub>          | TWCK and TWD fall time          | Fast                    | 20 + 0                 | .1C <sub>b</sub>    | 30                 | 00                                            | ns   |

| +                       | (Dependented) STADT hold time   | Standard                | 4                      |                     |                    |                                               |      |

| t <sub>HD-STA</sub>     | (Repeated) START hold time      | Fast                    | 0.6                    | t <sub>clkpb</sub>  | -                  |                                               | μs   |

| +                       | (Dependented) STADT act up time | Standard                | 4.7                    |                     |                    |                                               |      |

| t <sub>SU-STA</sub>     | (Repeated) START set-up time    | Fast                    | 0.6                    | t <sub>clkpb</sub>  | -                  |                                               | μs   |

| +                       | STOD oot up time                | Standard                | 4.0                    | 4+                  | -                  |                                               |      |

| t <sub>SU-STO</sub>     | STOP set-up time                | Fast                    | 0.6                    | 4t <sub>clkpb</sub> |                    |                                               | μs   |

| +                       | Dete held time                  | Standard                | - 0.3 <sup>(2)</sup> 2 | 2t <sub>clkpb</sub> | 3.45 <sup>()</sup> | 15+ +                                         |      |

| t <sub>HD-DAT</sub>     | Data hold time                  | Fast                    |                        |                     | 0.9()              | 15t <sub>prescaled</sub> + t <sub>clkpb</sub> | μs   |

| +                       | Data set-up time                | Standard                | 250                    | Q+                  |                    |                                               |      |

| t <sub>SU-DAT-TWI</sub> | Data set-up time                | Fast                    | 100                    | 2t <sub>clkpb</sub> | -                  |                                               | ns   |

| t <sub>SU-DAT</sub>     |                                 | -                       | -                      | t <sub>clkpb</sub>  | -                  |                                               | -    |

| +                       | TWCK LOW period                 | Standard                | 4.7                    | <i>/</i> +          |                    |                                               |      |

| t <sub>LOW-TWI</sub>    | TWOR LOW period                 | Fast                    | 1.3                    | 4t <sub>clkpb</sub> | -                  |                                               | μs   |

| t <sub>LOW</sub>        |                                 | -                       | -                      | t <sub>clkpb</sub>  | -                  |                                               | -    |

| +                       | TWCK HIGH period                | Standard                | 4.0                    | Q+                  |                    |                                               |      |

| t <sub>HIGH</sub>       |                                 | Fast                    | 0.6                    | 8t <sub>clkpb</sub> | -                  |                                               | μs   |

| f                       | TWCK frequency                  | Standard                |                        |                     | 100                | 1                                             | kHz  |

| f <sub>TWCK</sub>       |                                 | Fast                    | -                      |                     | 400                | <sup>12t</sup> clkpb                          | KIIZ |

**Table 9-64.**TWI-Bus Timing Requirements

Notes: 1. Standard mode:  $f_{TWCK} \le 100 \text{ kHz}$ ; fast mode:  $f_{TWCK} > 100 \text{ kHz}$ .

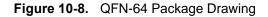

# **10. Mechanical Characteristics**

# 10.1 Thermal Considerations

# 10.1.1 Thermal Data

Table 10-1 summarizes the thermal resistance data depending on the package.

| Symbol               | Parameter                              | Condition | Package  | Тур  | Unit  |

|----------------------|----------------------------------------|-----------|----------|------|-------|

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | TQFP100  | 48.1 | ·C/W  |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | TQFP100  | 13.3 | ·C/vv |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | VFBGA100 | 31.1 | CAN   |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | VFBGA100 | 6.9  | ·C/W  |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | WLCSP64  | 26.9 | 0.00  |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | WLCSP64  | 0.2  | ·C/W  |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | TQFP64   | 49.6 | C 144 |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | TQFP64   | 13.5 | ·C/W  |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | QFN64    | 22.0 | C 144 |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | QFN64    | 1.3  | ·C/W  |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | TQFP48   | 51.1 | 0.000 |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | TQFP48   | 13.7 | ·C/W  |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | QFN48    | 24.9 | CAN   |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | QFN48    | 1.3  | ·C/W  |

Table 10-1. Thermal Resistance Data

## 10.1.2 Junction Temperature

The average chip-junction temperature,  $T_J$ , in °C can be obtained from the following:

1.

$$T_J = T_A + (P_D \times \theta_{JA})$$

2.  $T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$ where:

- $\theta_{JA}$  = package thermal resistance, Junction-to-ambient (°C/W), provided in Table 10-1.

- $\theta_{JC}$  = package thermal resistance, Junction-to-case thermal resistance (°C/W), provided in Table 10-1.

- $\theta_{HEAT SINK}$  = cooling device thermal resistance (°C/W), provided in the device datasheet.

Atmel

- $P_D$  = device power consumption (W) estimated from data provided in Section 9.5 on page 103.

- $T_A$  = ambient temperature (°C).

From the first equation, the user can derive the estimated lifetime of the chip and decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature  $T_J$  in °C.

Note: The exposed pad is not connected to anything internally, but should be soldered to ground to increase board level reliability.

| Table 10-23. | Device and Package Max | kimum Weight |

|--------------|------------------------|--------------|

|--------------|------------------------|--------------|

| 200 | mg |

|-----|----|

|     |    |

# Table 10-24. Package Characteristics

| Moisture Sensitivity Level MSL3 | Moisture Sensitivity Level | MSL3 |

|---------------------------------|----------------------------|------|

|---------------------------------|----------------------------|------|

## Table 10-25. Package Reference

| JEDEC Drawing Reference | MO-220 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

| Table 11-5. | ATSAM4LS4 Sub Serie Ordering Information |

|-------------|------------------------------------------|

|             | ATOAM4LO4 Oub Oche Ordening Information  |

| Ordering Code     | Flash<br>(Kbytes) | RAM<br>(Kbytes) | Package  | Conditioning | Package<br>Type | Temperature Operating<br>Range |

|-------------------|-------------------|-----------------|----------|--------------|-----------------|--------------------------------|

| ATSAM4LS4CA-AU-ES |                   | 5 32            | TQFP100  | ES           | Green           | N/A                            |

| ATSAM4LS4CA-AU    |                   |                 |          | Tray         |                 | Industrial -40°C to 85°C       |

| ATSAM4LS4CA-AUR   |                   |                 |          | Reel         |                 |                                |

| ATSAM4LS4CA-CFU   |                   |                 | VFBGA100 | Tray         |                 |                                |

| ATSAM4LS4CA-CFUR  |                   |                 |          | Reel         |                 | Industrial -40°C to 85°C       |

| ATSAM4LS4BA-AU-ES | 256               |                 | TQFP64   | ES           |                 | N/A                            |

| ATSAM4LS4BA-AU    |                   |                 |          | Tray         |                 | Industrial -40°C to 85°C       |

| ATSAM4LS4BA-AUR   |                   |                 |          | Reel         |                 |                                |

| ATSAM4LS4BA-MU-ES |                   |                 | QFN64    | ES           |                 | N/A                            |

| ATSAM4LS4BA-MU    |                   |                 |          | Tray         |                 | Industrial -40°C to 85°C       |

| ATSAM4LS4BA-MUR   |                   |                 |          | Reel         |                 |                                |

| ATSAM4LS4BA-UUR   |                   |                 | WLCSP64  | Reel         |                 | Industrial -40°C to 85°C       |

| ATSAM4LS4AA-AU-ES |                   |                 | TQFP48   | ES           |                 | N/A                            |

| ATSAM4LS4AA-AU    |                   |                 |          | Tray         |                 | Industrial -40°C to 85°C       |

| ATSAM4LS4AA-AUR   |                   |                 |          | Reel         |                 |                                |

| ATSAM4LS4AA-MU-ES |                   |                 | QFN48    | ES           |                 | N/A                            |

| ATSAM4LS4AA-MU    |                   |                 |          | Tray         |                 |                                |

| ATSAM4LS4AA-MUR   |                   |                 |          | Reel         |                 | Industrial -40°C to 85°C       |

# Table 11-6. ATSAM4LS2 Sub Serie Ordering Information

| Ordering Code    | Flash<br>(Kbytes) | RAM<br>(Kbytes) | Package  | Conditioning | Package<br>Type | Temperature Operating<br>Range |                          |

|------------------|-------------------|-----------------|----------|--------------|-----------------|--------------------------------|--------------------------|

| ATSAM4LS2CA-AU   |                   |                 |          | Tray         |                 |                                |                          |

| ATSAM4LS2CA-AUR  | 128               |                 | TQFP100  | Reel         |                 |                                |                          |

| ATSAM4LS2CA-CFU  |                   |                 | VFBGA100 | Tray         |                 |                                |                          |

| ATSAM4LS2CA-CFUR |                   |                 |          | Reel         |                 |                                |                          |

| ATSAM4LS2BA-AU   |                   |                 |          | TOFRA        | Tray            | l I                            |                          |

| ATSAM4LS2BA-AUR  |                   |                 | TQFP64   | Reel         |                 |                                |                          |

| ATSAM4LS2BA-MU   |                   | 128 32          | 32       |              | Tray            | Green                          | Industrial -40°C to 85°C |

| ATSAM4LS2BA-MUR  |                   |                 | QFN64    | Reel         |                 |                                |                          |

| ATSAM4LS2BA-UUR  |                   |                 | WLCSP64  | Reel         |                 |                                |                          |

| ATSAM4LS2AA-AU   |                   |                 | TQFP48   | Tray         |                 |                                |                          |

| ATSAM4LS2AA-AUR  |                   |                 |          | Reel         |                 |                                |                          |

| ATSAM4LS2AA-MU   |                   |                 | QFN48    | Tray         |                 |                                |                          |

| ATSAM4LS2AA-MUR  |                   |                 |          | Reel         |                 |                                |                          |

# 13. Datasheet Revision History

Note that the referring page numbers in this section are referred to this document. The referring revision in this section are referring to the document revision.

# 13.1 Rev. A - 09/12

1. Initial revision.

# 13.2 Rev. B - 10/12

- 1. Fixed ordering code

- 2. Changed BOD18CTRL and BOD33CTRL ACTION field from "Reserved" to 'No action"

# 13.3 Rev. C – 02/13

- 1. Fixed ball pitch for VFBGA100 package

- 2. Added VFBGA100 and WLCSP64 pinouts

- 3. Added Power Scaling Mode 2 for high frequency support

- 4. Minor update on several modules chapters

- 5. Major update on Electrical characteristics

- 6. Updated errata

- 7. Fixed GPIO multiplexing pin numbers

# 13.4 Rev. D - 03/13

- 1. Removed WLCSP package information

- 2. Added errata text for detecting whether a part supports PS2 mode or not

- 3. Removed temperature sensor feature (not supported by production flow)

- 4. Fixed MUX selection on Positive ADC input channel table

- 5. Added information about TWI instances capabilities

- 6. Added some details on errata Corrupted data in flash may happen after flash page write operations.171