Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

|                            |                                                                          |

| Product Status             | Active                                                                   |

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                          |

| Number of I/O              | 80                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 32K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.68V ~ 3.6V                                                             |

| Data Converters            | A/D 15x12b; D/A 1x10b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-TQFP                                                                 |

| Supplier Device Package    | 100-TQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4ls2ca-au |

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 2 of 4)

| Table |          |     |            | O COIII | IOIICI | i unction | Multiplexi     | ng (Sneet       | 2 01 4)         |                 |                   |                |                 |

|-------|----------|-----|------------|---------|--------|-----------|----------------|-----------------|-----------------|-----------------|-------------------|----------------|-----------------|

|       | ATSAM4LC |     | ATSAM4LS   | Pin     | GPIO   | Supply    | GPIO Functions |                 |                 |                 |                   |                |                 |

| QFN   | VFBGA    | QFN | VFBGA      |         |        |           | Α              | В               | С               | D               | E                 | F              | G               |

| 66    | J7       | 66  | J7         | PA16    | 16     | LCDA      | USART1<br>TXD  | TC0<br>CLK2     | EIC<br>EXTINT1  | PARC<br>PCDATA7 |                   | LCDCA<br>SEG8  | CATB<br>SENSE11 |

| 67    | Н6       | 67  | Н6         | PA17    | 17     | LCDA      | USART2<br>RTS  | ABDACB<br>DAC0  | EIC<br>EXTINT2  | PARC<br>PCCK    |                   | LCDCA<br>SEG9  | CATB<br>SENSE12 |

| 76    | K10      | 76  | K10        | PA18    | 18     | LCDA      | USART2<br>CLK  | ABDACB<br>DACN0 | EIC<br>EXTINT3  | PARC<br>PCEN1   |                   | LCDCA<br>SEG18 | CATB<br>SENSE13 |

| 77    | J10      | 77  | J10        | PA19    | 19     | LCDA      | USART2<br>RXD  | ABDACB<br>DAC1  | EIC<br>EXTINT4  | PARC<br>PCEN2   | SCIF<br>GCLK0     | LCDCA<br>SEG19 | CATB<br>SENSE14 |

| 78    | H10      | 78  | H10        | PA20    | 20     | LCDA      | USART2<br>TXD  | ABDACB<br>DACN1 | EIC<br>EXTINT5  | GLOC<br>IN0     | SCIF<br>GCLK1     | LCDCA<br>SEG20 | CATB<br>SENSE15 |

| 91    | E9       | 91  | <b>E</b> 9 | PA21    | 21     | LCDC      | SPI<br>MISO    | USART1<br>CTS   | EIC<br>EXTINT6  | GLOC<br>IN1     | TWIM2<br>TWD      | LCDCA<br>SEG34 | CATB<br>SENSE16 |

| 92    | E10      | 92  | E10        | PA22    | 22     | LCDC      | SPI<br>Mosi    | USART2<br>CTS   | EIC<br>EXTINT7  | GLOC<br>IN2     | TWIM2<br>TWCK     | LCDCA<br>SEG35 | CATB<br>SENSE17 |

| 95    | D6       | 95  | D6         | PA23    | 23     | LCDC      | SPI<br>SCK     | TWIMS0<br>TWD   | EIC<br>EXTINT8  | GLOC<br>IN3     | SCIF<br>GCLK IN0  | LCDCA<br>SEG38 | CATB<br>DIS     |

| 96    | D10      | 96  | D10        | PA24    | 24     | LCDC      | SPI<br>NPCS0   | TWIMS0<br>TWCK  |                 | GLOC<br>OUT0    | SCIF<br>GCLK IN1  | LCDCA<br>SEG39 | CATB<br>SENSE18 |

| 98    | D9       | 98  | D9         | PA25    | 25     | VDDIO     | USBC<br>DM     | USART2<br>RXD   |                 |                 |                   |                | CATB<br>SENSE19 |

| 99    | C9       | 99  | C9         | PA26    | 26     | VDDIO     | USBC<br>DP     | USART2<br>TXD   |                 |                 |                   |                | CATB<br>SENSE20 |

|       |          | 51  | K1         | PA27    | 27     | LCDA      | SPI<br>MISO    | IISC<br>ISCK    | ABDACB<br>DAC0  | GLOC<br>IN4     | USART3<br>RTS     |                | CATB<br>SENSE0  |

|       |          | 52  | J1         | PA28    | 28     | LCDA      | SPI<br>MOSI    | IISC<br>ISDI    | ABDACB<br>DACN0 | GLOC<br>IN5     | USART3<br>CTS     |                | CATB<br>SENSE1  |

|       |          | 53  | K2         | PA29    | 29     | LCDA      | SPI<br>SCK     | IISC<br>IWS     | ABDACB<br>DAC1  | GLOC<br>IN6     | USART3<br>CLK     |                | CATB<br>SENSE2  |

|       |          | 56  | K4         | PA30    | 30     | LCDA      | SPI<br>NPCS0   | IISC<br>ISDO    | ABDACB<br>DACN1 | GLOC<br>IN7     | USART3<br>RXD     |                | CATB<br>SENSE3  |

|       |          | 57  | K5         | PA31    | 31     | LCDA      | SPI<br>NPCS1   | IISC<br>IMCK    | ABDACB<br>CLK   | GLOC<br>OUT1    | USART3<br>TXD     |                | CATB<br>DIS     |

| 20    | J3       | 20  | J3         | PB00    | 32     | VDDIN     | TWIMS1<br>TWD  | USART0<br>RXD   |                 |                 |                   |                | CATB<br>SENSE21 |

| 21    | D5       | 21  | D5         | PB01    | 33     | VDDIN     | TWIMS1<br>TWCK | USART0<br>TXD   | EIC<br>EXTINT0  |                 |                   |                | CATB<br>SENSE22 |

| 22    | E5       | 22  | E5         | PB02    | 34     | VDDANA    | ADCIFE<br>AD3  | USART1<br>RTS   | ABDACB<br>DAC0  | IISC<br>ISCK    | ACIFC<br>ACBN0    |                | CATB<br>SENSE23 |

| 23    | C4       | 23  | C4         | PB03    | 35     | VDDANA    | ADCIFE<br>AD4  | USART1<br>CLK   | ABDACB<br>DACN0 | IISC<br>ISDI    | ACIFC<br>ACBP0    |                | CATB<br>DIS     |

| 28    | C1       | 28  | C1         | PB04    | 36     | VDDANA    | ADCIFE<br>AD5  | USART1<br>RXD   | ABDACB<br>DAC1  | IISC<br>ISDO    | DACC<br>EXT TRIG0 |                | CATB<br>SENSE24 |

| 29    | B1       | 29  | B1         | PB05    | 37     | VDDANA    | ADCIFE<br>AD6  | USART1<br>TXD   | ABDACB<br>DACN1 | IISC<br>IMCK    |                   |                | CATB<br>SENSE25 |

| 45    | G3       | 45  | G3         | PB06    | 38     | LCDA      | USART3<br>RTS  |                 | GLOC<br>IN4     | IISC<br>IWS     |                   | LCDCA<br>SEG22 | CATB<br>SENSE26 |

| 46    | H1       | 46  | H1         | PB07    | 39     | LCDA      | USART3<br>CTS  |                 | GLOC<br>IN5     | TC0<br>A0       |                   | LCDCA<br>SEG21 | CATB<br>SENSE27 |

# 3.3 Signals Description

The following table gives details on signal names classified by peripheral.

Table 3-8.

Signal Descriptions List (Sheet 1 of 4)

| Signal Name                         | Function                                | Туре               | Active<br>Level | Comments |  |  |  |  |  |

|-------------------------------------|-----------------------------------------|--------------------|-----------------|----------|--|--|--|--|--|

|                                     | Audio Bitstream DA                      | C - ABDACB         |                 |          |  |  |  |  |  |

| CLK                                 | D/A clock output                        | Output             |                 |          |  |  |  |  |  |

| DAC1 - DAC0                         | D/A bitstream outputs                   | Output             |                 |          |  |  |  |  |  |

| DACN1 - DACN0                       | D/A inverted bitstream outputs          | Output             |                 |          |  |  |  |  |  |

| Analog Comparator Interface - ACIFC |                                         |                    |                 |          |  |  |  |  |  |

| ACAN1 - ACAN0                       | Analog Comparator A negative references | Analog             |                 |          |  |  |  |  |  |

| ACAP1 - ACAP0                       | Analog Comparator A positive references | Analog             |                 |          |  |  |  |  |  |

| ACBN1 - ACBN0                       | Analog Comparator B negative references | Analog             |                 |          |  |  |  |  |  |

| ACBP1 - ACBP0                       | Analog Comparator B positive references | Analog             |                 |          |  |  |  |  |  |

|                                     | ADC controller interf                   | ace - ADCIFE       |                 |          |  |  |  |  |  |

| AD14 - AD0                          | Analog inputs                           | Analog             |                 |          |  |  |  |  |  |

| ADVREFP                             | Positive voltage reference              | Analog             |                 |          |  |  |  |  |  |

| TRIGGER                             | External trigger                        | Input              |                 |          |  |  |  |  |  |

|                                     | Backup System Control                   | Interface - BS     | SCIF            |          |  |  |  |  |  |

| XIN32                               | 32 kHz Crystal Oscillator Input         | Analog/<br>Digital |                 |          |  |  |  |  |  |

| XOUT32                              | 32 kHz Crystal Oscillator Output        | Analog             |                 |          |  |  |  |  |  |

|                                     | Capacitive Touch Mod                    | dule B - CATI      | 3               |          |  |  |  |  |  |

| DIS                                 | Capacitive discharge line               | Output             |                 |          |  |  |  |  |  |

| SENSE31 - SENSE0                    | Capacitive sense lines                  | I/O                |                 |          |  |  |  |  |  |

|                                     | DAC Controller                          | - DACC             |                 |          |  |  |  |  |  |

| DAC external trigger                | DAC external trigger                    | Input              |                 |          |  |  |  |  |  |

| DAC voltage output                  | DAC voltage output                      | Analog             |                 |          |  |  |  |  |  |

|                                     | Enhanced Debug Port For A               | RM Product         | s - EDP         |          |  |  |  |  |  |

| TCK/SWCLK                           | JTAG / SW Debug Clock                   | Input              |                 |          |  |  |  |  |  |

| TDI                                 | JTAG Debug Data In                      | Input              |                 |          |  |  |  |  |  |

| TDO/TRACESWO                        | JTAG Debug Data Out / SW Trace Out      | Output             |                 |          |  |  |  |  |  |

| TMS/SWDIO                           | JTAG Debug Mode Select / SW Data        | I/O                |                 |          |  |  |  |  |  |

|                                     | External Interrupt Co                   | ntroller - EIC     | <b>;</b>        |          |  |  |  |  |  |

| EXTINT8 - EXTINT0                   | External interrupts                     | Input              |                 |          |  |  |  |  |  |

|                                     | Glue Logic Control                      | ller - GLOC        |                 |          |  |  |  |  |  |

| IN7 - IN0                           | Lookup Tables Inputs                    | Input              |                 |          |  |  |  |  |  |

| OUT1 - OUT0                         | Lookup Tables Outputs                   | Output             |                 |          |  |  |  |  |  |

|                                     |                                         |                    |                 |          |  |  |  |  |  |

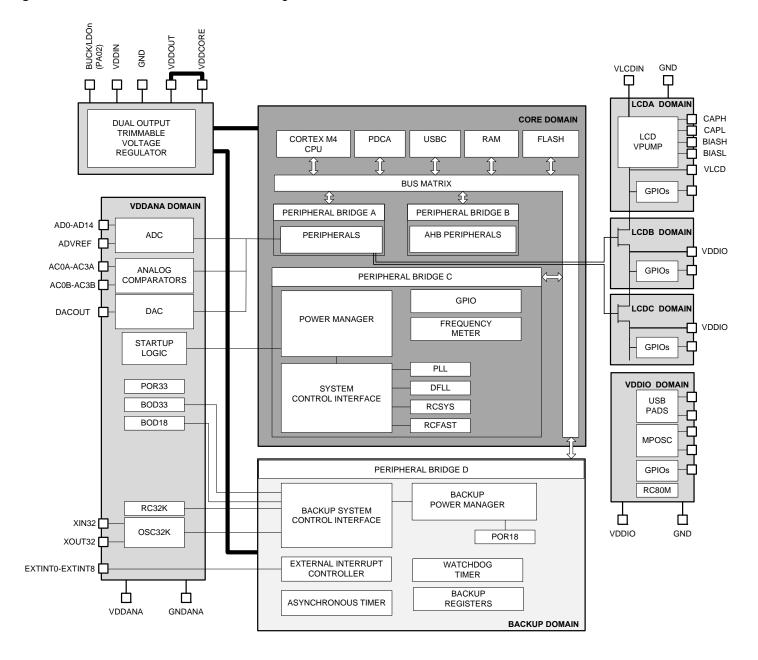

Figure 6-2. ATSAM4LC Power Domain Diagram

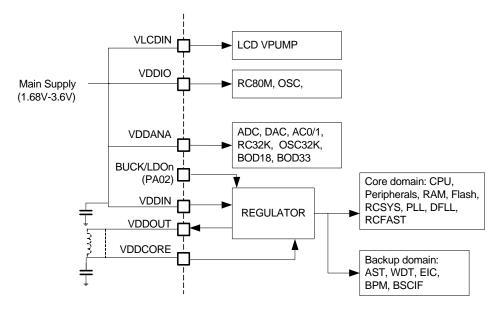

The internal regulator is connected to the VDDIN pin and its output VDDOUT feeds VDDCORE in linear mode or through an inductor in switching mode. Figure 6-4 shows the power schematics to be used. All I/O lines will be powered by the same power (V<sub>VDDIN</sub>=V<sub>VDDIO</sub>=V<sub>VDDANA</sub>).

Figure 6-4. Single Supply Mode

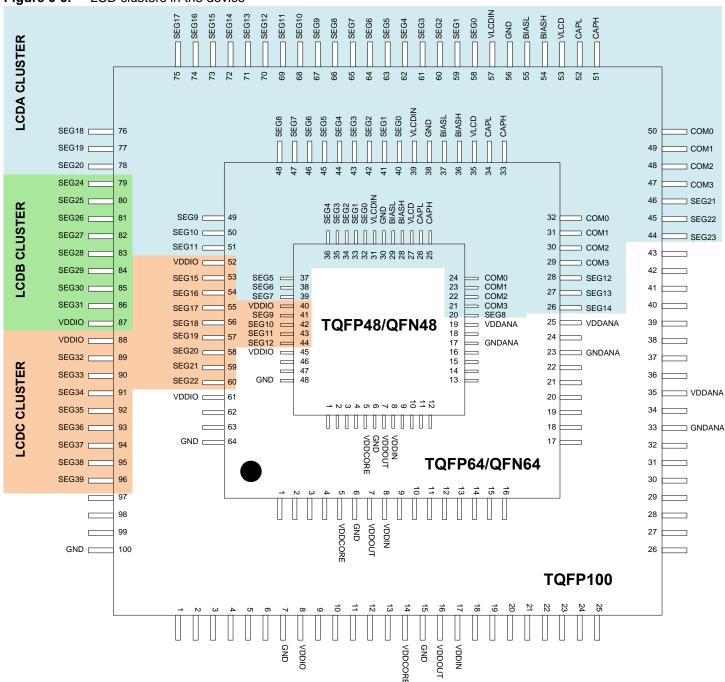

#### 6.2.3 LCD Power Modes

#### 6.2.3.1 Principle

LCD lines is powered using the device internal voltage sources provided by the LCDPWR block. When enabled, the LCDPWR blocks will generate the VLCD, BIASL, BIASH voltages.

LCD pads are splitted into three clusters that can be powered independently namely clusters A, B and C. A cluster can either be in GPIO mode or in LCD mode.

When a cluster is in GPIO mode, its VDDIO pin must be powered externally. None of its GPIO pin can be used as a LCD line

When a cluster is in LCD mode, each clusters VDDIO pin can be either forced externally (1.8-3.6V) or unconnected (nc). GPIOs in a cluster are not available when it is in LCD mode. A cluster is set in LCD mode by the LCDCA controller when it is enabled depending on the number of segments configured. The LCDPWR block is powered by the VLCDIN pin inside cluster A

When LCD feature is not used, VLCDIN must be always powered (1.8-3.6V). VLCD, CAPH, CAPL, BIASH, BIASL can be left unconnected in this case

Figure 6-5. LCD clusters in the device

# 6.2.3.2 Internal LCD Voltage

In this mode the LCD voltages are internally generated. Depending of the number of segments required by the application, LCDB and LDCC clusters VDDIO pin must be unconnected (nc) or

### 6.2.4 Power-up Sequence

### 6.2.4.1 Maximum Rise Rate

To avoid risk of latch-up, the rise rate of the power supplies must not exceed the values described in Table 9-3 on page 100.

#### 6.2.4.2 Minimum Rise Rate

The integrated Power-on Reset (POR33) circuitry monitoring the VDDIN powering supply requires a minimum rise rate for the VDDIN power supply.

See Table 9-3 on page 100 for the minimum rise rate value.

If the application can not ensure that the minimum rise rate condition for the VDDIN power supply is met, the following configuration can be used:

• A logic "0" value is applied during power-up on pin RESET\_N until VDDIN rises above 1.6 V.

# 6.3 Startup Considerations

This section summarizes the boot sequence of the ATSAM4L8/L4/L2. The behavior after power-up is controlled by the Power Manager. For specific details, refer to Section 9. "Power Manager (PM)" on page 677.

#### 6.3.1 Starting of Clocks

After power-up, the device will be held in a reset state by the power-up circuitry for a short time to allow the power to stabilize throughout the device. After reset, the device will use the System RC Oscillator (RCSYS) as clock source. Refer to Section 9. "Electrical Characteristics" on page 99 for the frequency for this oscillator.

On system start-up, the DFLL and the PLLs are disabled. Only the necessary clocks are active allowing software execution. Refer to Section 3-6 "Maskable Module Clocks in AT32UC3B." on page 24 to know the list of peripheral clock running. No clocks have a divided frequency; all parts of the system receive a clock with the same frequency as the System RC Oscillator.

#### 6.3.2 Fetching of Initial Instructions

After reset has been released, the Cortex M4 CPU starts fetching PC and SP values from the reset address, which is 0x00000000. Refer to the ARM Architecture Reference Manual for more information on CPU startup. This address points to the first address in the internal Flash.

The code read from the internal flash is free to configure the clock system and clock sources.

# 6.4 Power-on-Reset, Brownout and Supply Monitor

The SAM4L embeds four features to monitor, warm, and/or reset the device:

- POR33: Power-on-Reset on VDDANA

- BOD33: Brownout detector on VDDANA

- POR18: Power-on-Reset on VDDCORE

- BOD18: Brownout detector on VDDCORE

# 7. Low Power Techniques

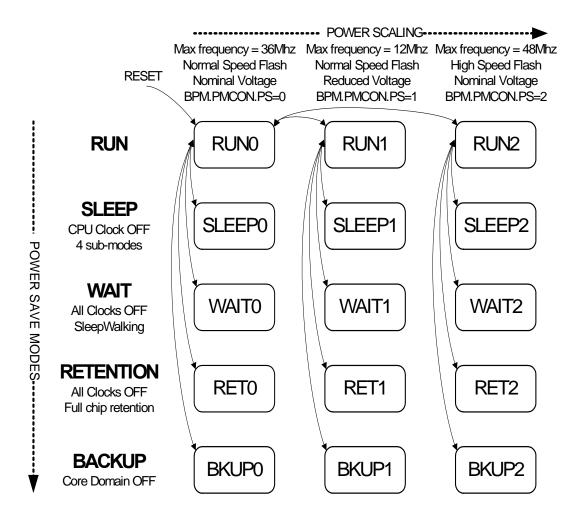

The ATSAM4L8/L4/L2 supports multiple power configurations to allow the user to optimize its power consumption in different use cases. The Backup Power Manager (BPM) implements different solutions to reduce the power consumption:

- The Power Save modes intended to reduce the logic activity and to adapt the power configuration. See "Power Save Modes" on page 55.

- The Power Scaling intended to scale the power configuration (voltage scaling of the regulator). See "Power Scaling" on page 60.

These two techniques can be combined together.

Figure 7-1. Power Scaling and Power Save Mode Overview

# 7.1 Power Save Modes

Refer to Section 6. "Power and Startup Considerations" on page 46 to get definition of the core and the backup domains.

At power-up or after a reset, the ATSAM4L8/L4/L2 is in the RUN0 mode. Only the necessary clocks are enabled allowing software execution. The Power Manager (PM) can be used to adjust the clock frequencies and to enable and disable the peripheral clocks.

When the CPU is entering a Power Save Mode, the CPU stops executing code. The user can choose between four Power Save Modes to optimize power consumption:

- SLEEP mode: the Cortex-M4 core is stopped, optionally some clocks are stopped, peripherals are kept running if enabled by the user.

- WAIT mode: all clock sources are stopped, the core and all the peripherals are stopped except the modules running with the 32kHz clock if enabled. This is the lowest power configuration where SleepWalking is supported.

- RETENTION mode: similar to the WAIT mode in terms of clock activity. This is the lowest power configuration where the logic is retained.

- BACKUP mode: the Core domain is powered off, the Backup domain is kept powered.

A wake up source exits the system to the RUN mode from which the Power Save Mode was entered.

A reset source always exits the system from the Power Save Mode to the RUN0 mode.

The configuration of the I/O lines are maintained in all Power Save Modes. Refer to Section 9. "Backup Power Manager (BPM)" on page 677.

#### 7.1.1 **SLEEP** mode

The SLEEP mode allows power optimization with the fastest wake up time.

The CPU is stopped. To further reduce power consumption, the user can switch off modulesclocks and synchronous clock sources through the BPM.PMCON.SLEEP field (See Table 7-1). The required modules will be halted regardless of the bit settings of the mask registers in the Power Manager (PM.AHBMASK, PM.APBxMASK).

**Table 7-1. SLEEP mode Configuration**

| BPM.PSAVE.SLEEP | CPU<br>clock | AHB<br>clocks | APB clocks<br>GCLK | Clock sources:<br>OSC, RCFAST,<br>RC80M, PLL,<br>DFLL | RCSYS | OSC32K<br>RC32K <sup>(2)</sup> | Wake up Sources              |

|-----------------|--------------|---------------|--------------------|-------------------------------------------------------|-------|--------------------------------|------------------------------|

| 0               | Stop         | Run           | Run                | Run                                                   | Run   | Run                            | Any interrupt                |

| 1               | Stop         | Stop          | Run                | Run                                                   | Run   | Run                            | Any interrupt <sup>(1)</sup> |

| 2               | Stop         | Stop          | Stop               | Run                                                   | Run   | Run                            | Any interrupt <sup>(1)</sup> |

| 3               | Stop         | Stop          | Stop               | Stop                                                  | Run   | Run                            | Any interrupt <sup>(1)</sup> |

- Notes: 1. from modules with clock running.

- 2. OSC32K and RC32K will only remain operational if pre-enabled.

#### 7.1.1.1 Entering SLEEP mode

The SLEEP mode is entered by executing the WFI instruction.

Additionally, if the SLEEPONEXIT bit in the Cortex-M4 System Control Register (SCR) is set, the SLEEP mode will also be entered when the Cortex-M4 exits the lowest priority ISR. This

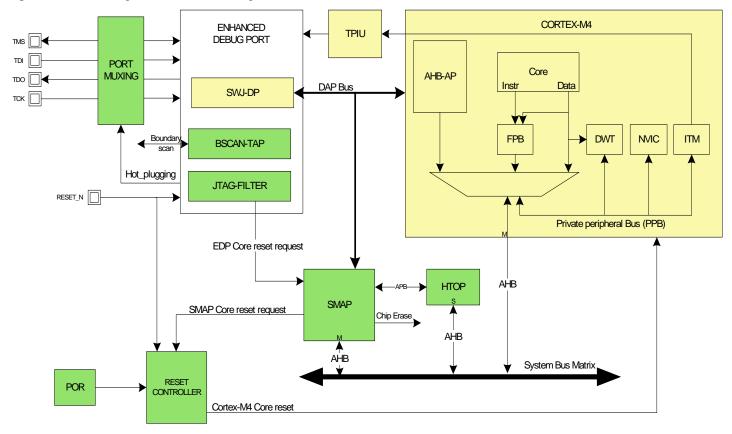

# 8.3 Block diagram

Figure 8-1. Debug and Test Block Diagram

note: Boxes with a plain corner are SAM4L specific.

# 8.4 I/O Lines Description

Refer to Section 1.1.4 "I/O Lines Description" on page 4.

74

Table 8-4.

Instruction Description (Continued)

| Instruction     | Description                                                                                                    |

|-----------------|----------------------------------------------------------------------------------------------------------------|

| DR Size         | Shows the number of bits in the data register chain when this instruction is active.  Example: 32 bits         |

| DR input value  | Shows which bit pattern to shift into the data register in the Shift-DR state when this instruction is active. |

| DR output value | Shows the bit pattern shifted out of the data register in the Shift-DR state when this instruction is active.  |

#### 8.7.14 JTAG Instructions

Refer to the ARM Debug Interface v5.1 Architecture Specification for more details on ABORT, DPACC, APACC and IDCODE instructions.

#### 8.7.14.1 EXTEST

This instruction selects the boundary-scan chain as Data Register for testing circuitry external to the chip package. The contents of the latched outputs of the boundary-scan chain is driven out as soon as the JTAG IR-register is loaded with the EXTEST instruction.

Starting in Run-Test/Idle, the EXTEST instruction is accessed the following way:

- 1. Select the IR Scan path.

- 2. In Capture-IR: The IR output value is latched into the shift register.

- 3. In Shift-IR: The instruction register is shifted by the TCK input.

- 4. In Update-IR: The data from the boundary-scan chain is applied to the output pins.

- 5. Return to Run-Test/Idle.

- 6. Select the DR Scan path.

- 7. In Capture-DR: The data on the external pins is sampled into the boundary-scan chain.

- 8. In Shift-DR: The boundary-scan chain is shifted by the TCK input.

- 9. In Update-DR: The data from the scan chain is applied to the output pins.

- 10. Return to Run-Test/Idle.

Table 8-5. EXTEST Details

| Instructions    | Details                                          |

|-----------------|--------------------------------------------------|

| IR input value  | <b>0000</b> (0x0)                                |

| IR output value | p00s                                             |

| DR Size         | Depending on boundary-scan chain, see BSDL-file. |

| DR input value  | Depending on boundary-scan chain, see BSDL-file. |

| DR output value | Depending on boundary-scan chain, see BSDL-file. |

#### 8.7.14.2 SAMPLE PRELOAD

This instruction takes a snap-shot of the input/output pins without affecting the system operation, and pre-loading the scan chain without updating the DR-latch. The boundary-scan chain is selected as Data Register.

Starting in Run-Test/Idle, the Device Identification register is accessed in the following way:

#### 8.9.9 Unlimited Flash User Page Read Access

The SMAP can access the User page even if the protected state is set. Prior to operate such an access, the user should check that the module is not busy by checking that SR.STATE is equal to zerp. Once the offset of the word to access inside the page is written in ADDR.ADDR, the read operation can be initiated by writing a one in CR.FSPR. The SR.STATE field will indicate the FSPR state. Addresses written to ADDR.ADDR must be world aligned. Failing to do so will result in unpredictable behavior. The result can be read in the DATA register as soon as SR.DONE rises. The ADDR field is used as an offset in the page, bits outside a page boundary will be silently discarded. The ADDR register is automatically incremented at the end of the read operation making possible to dump consecutive words without writing the next offset into ADDR.ADDR.

# 8.9.10 32-bit Cyclic Redundancy Check (CRC)

The SMAP unit provides support for calculating a Cyclic Redundancy Check (CRC) value for a memory area. The algorithm used is the industry standard CRC32 algorithm using the generator polynomial 0xEDB88320.

# 8.9.10.1 Starting CRC Calculation

To calculate CRC for a memory range, the start address must be written into the ADDR register, and the size of the memory range into the LENGTH register. Both the start address and the length must be word aligned.

The initial value used for the CRC calculation must be written to the DATA register. This value will usually be 0xFFFFFFF, but can be e.g. the result of a previous CRC calculation if generating a common CRC of separate memory blocks.

Once completed, the calculated CRC value can be read out of the DATA register. The read value must be inverted to match standard CRC32 implementations, or kept non-inverted if used as starting point for subsequent CRC calculations.

If the device is in protected state, it is only possible to calculate the CRC of the whole flash array. In most cases this area will be the entire onboard nonvolatile memory. The ADDR, LENGTH, and DATA registers will be forced to predefined values once the CRC operation is started, and user-written values are ignored. This allows the user to verify the contents of a protected device.

The actual test is started by writing a one in CR.CRC. A running CRC operation can be cancelled by disabling the module (write a one in CR.DIS). This has the effect of resetting the module. The module has to be restarted by issuing an enable command (write a one in CR.EN).

#### 8.9.10.2 Interpreting the Results

The user should monitor the SR register (Refer to Section 8.9.11.2 "Status Register" on page 83). When the operation is completed SR.DONE is set. Then the SR.BERR and SR.FAIL must be read to ensure that no bus error nor functional error occured.

# 8.9.11 SMAP User Interface

Table 8-9. SMAP Register Memory Map

| Offset | Register                   | Register Name | Access (unprotected) | Access (protected)                  | Reset      |

|--------|----------------------------|---------------|----------------------|-------------------------------------|------------|

| 0x0000 | Control Register           | CR            | Write-Only           | Write-Only (partial)(2)             | 0x00000000 |

| 0x0004 | Status Register            | SR            | Read-Only            | Read-Only                           | 0x00000000 |

| 0x0008 | Status Clear Register      | SCR           | Write-Only           | Write-Only (partial) <sup>(3)</sup> | 0x00000000 |

| 0x000C | Address Register           | ADDR          | Read/Write           | Read/Write (partial) <sup>(4)</sup> | 0x00000000 |

| 0x0010 | Length Register            | LENGTH        | Read/Write           | denied                              | 0x00000000 |

| 0x0014 | Data Register              | DATA          | Read/Write           | Read/Write (partial) <sup>(4)</sup> | 0x00000000 |

| 0x0028 | VERSION Register           | VERSION       | Read-Only            | Read-Only                           | _(1)       |

| 0x00F0 | Chip ID Register           | CIDR          | Read-Only            | Read-Only                           | _(1)       |

| 0x00F4 | Chip ID Extension Register | EXID          | Read-Only            | Read-Only                           | _(1)       |

| 0x00FC | AP Identification register | IDR           | Read-Only            | Read-Only                           | 0x003E0000 |

Note:

- 1. The reset value for this register is device specific. Refer to the Module Configuration section at the end of this chapter.

- 2. CR.MBIST is ignored

- 3. SCR.HCR is ignored

- 4. Access is not allowed when an operation is ongoing

8.9.11.1 Control Register

Name: CR

Access Type: Write-Only

Offset: 0x00

**Reset Value:** 0x00000000

| 31 | 30 | 29 | 28 | 27   | 26  | 25  | 24 |

|----|----|----|----|------|-----|-----|----|

| -  | -  | -  | -  | -    | ı   | 1   | -  |

|    |    |    |    |      |     |     |    |

| 23 | 22 | 21 | 20 | 19   | 18  | 17  | 16 |

| -  | -  | -  | -  | -    | ı   | 1   | -  |

|    |    |    |    |      |     |     |    |

| 15 | 14 | 13 | 12 | 11   | 10  | 9   | 8  |

| -  | -  | -  | -  | -    | -   | -   | -  |

|    |    |    |    |      |     |     |    |

| 7  | 6  | 5  | 4  | 3    | 2   | 1   | 0  |

| -  | -  | =  | CE | FSPR | CRC | DIS | EN |

Writing a zero to a bit in this register has no effect.

#### CE: Chip Erase

Writing a one to this bit triggers the FLASH Erase All (EA) operation which clears all volatile memories, the whole flash array, the general purpose fuses and the protected state. The Status register DONE field indicates the completion of the operation. Reading this bit always returns 0

#### FSPR: Flash User Page Read

Writing a one to this bit triggers a read operation in the User page. The word pointed by the ADDR register in the page is read and written to the DATA register. ADDR is post incremented allowing a burst of reads without modifying ADDR. SR.DONE must be read high prior to reading the DATA register.

Reading this bit always returns 0

# CRC: Cyclic Redundancy Code

Writing a one triggers a CRC calculation over a memory area defined by the ADDR and LENGTH registers. Reading this bit always returns 0

Note: This feature is restricted while in protected state

#### DIS: Disable

Writing a one to this bit disables the module. Disabling the module resets the whole module immediately.

#### · EN: Enable

Writing a one to this bit enables the module.

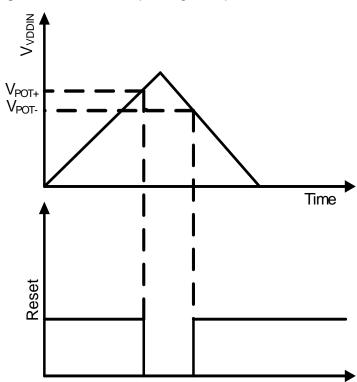

# 9.9.2 Power-on Reset 33 Characteristics

Table 9-41. POR33 Characteristics (1)

| Symbol            | Parameter                                       | Conditions | Min  | Тур | Max  | Units |

|-------------------|-------------------------------------------------|------------|------|-----|------|-------|

| V <sub>POT+</sub> | Voltage threshold on V <sub>VDDIN</sub> rising  |            | 1.25 |     | 1.55 | V     |

| V <sub>POT-</sub> | Voltage threshold on V <sub>VDDIN</sub> falling |            | 0.95 |     | 1.30 | V     |

<sup>1.</sup> These values are based on characterization. These values are not covered by test limits in production.

Figure 9-4. POR33 Operating Principle

# 9.9.3 Brown Out Detectors Characteristics

**Table 9-42.** BOD18 Characteristics (1)

| Symbol               | Parameter                                                             | Conditions                                                                        | Min | Тур  | Max | Units |

|----------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|------|-----|-------|

|                      | Step size, between adjacent values in BSCIF.BOD18LEVEL <sup>(1)</sup> |                                                                                   |     | 10.1 |     | mV    |

| V <sub>HYST</sub>    | BOD hysteresis <sup>(1)</sup>                                         | T = 25°C                                                                          | 3   |      | 40  |       |

| t <sub>DET</sub>     | Detection time <sup>(1)</sup>                                         | Time with V <sub>VDDCORE</sub> < BOD18.LEVEL necessary to generate a reset signal | 1.2 |      |     | μs    |

| 1                    | Command approximation (1)                                             | on VDDIN                                                                          |     | 7.4  | 14  |       |

| I <sub>BOD</sub>     | Current consumption <sup>(1)</sup>                                    | on VDDCORE                                                                        | 7   |      | μΑ  |       |

| t <sub>STARTUP</sub> | Startup time <sup>(1)</sup>                                           |                                                                                   |     |      | 4.5 | μs    |

Table 9-46. DC Characteristics

| Symbol              | Parameter                                        | Conditions                                  | Min  | Тур | Max            | Units  |

|---------------------|--------------------------------------------------|---------------------------------------------|------|-----|----------------|--------|

| VDDANA              | Supply voltage (1)                               |                                             | 1.6  |     | 3.6            | V      |

|                     |                                                  | Differential mode                           | 1.0  |     | VDDANA<br>-0.6 |        |

|                     | Reference range (2)                              | Unipolar and Window modes                   | 1.0  |     | 1.0            | V      |

|                     |                                                  | Using divide by two function (differential) | 2.0  |     | VDDANA         |        |

|                     | Absolute min, max input voltage <sup>(2)</sup>   |                                             | -0,1 |     | VDDANA<br>+0.1 | V      |

|                     |                                                  | ADC with reference already enabled          |      | 12  | 24             | Cycles |

|                     | Start up time <sup>(2)</sup>                     | No gain compensation<br>Reference buffer    |      |     | 5              | μs     |

|                     |                                                  | Gain compensation Reference buffer          |      |     | 60             | Cycles |

| R <sub>SAMPLE</sub> | Input channel source resistance <sup>(2)</sup>   |                                             |      |     | 0.5            | kΩ     |

| C <sub>SAMPLE</sub> | Sampling capacitance <sup>(2)</sup>              |                                             | 2.9  | 3.6 | 4.3            | pF     |

|                     | Deference input source registeres(2)             | Gain compensation                           |      |     | 2              | kΩ     |

|                     | Reference input source resistance <sup>(2)</sup> | No gain compensation                        |      |     | 1              | МΩ     |

|                     | ADC reference settling time <sup>(2)</sup>       | After changing reference/mode (3)           |      | 5   | 60             | Cycles |

- 1. These values are based on characterization. These values are not covered by test limits in production

- 2. These values are based on simulation. These values are not covered by test limits in production

- 3. Requires refresh/flush otherwise conversion time (latency) + 1

**Table 9-47.** Differential mode, gain=1

| Symbol | Parameter                                      | Conditions                                                | Min  | Тур  | Max  | Units |  |

|--------|------------------------------------------------|-----------------------------------------------------------|------|------|------|-------|--|

|        | Accuracy without compensation (1)              |                                                           |      | 7    |      | ENOB  |  |

|        | Accuracy after compensation <sup>(1)</sup>     | (INL, gain and offset)                                    |      |      | 11   | ENOB  |  |

| INL    | Integral Non Linearity (2)                     | After calibration, Gain compensation                      |      | 1.2  | 1.7  | LSBs  |  |

| DNL    | Differential Non Linearity <sup>(2)</sup>      | After calibration                                         |      | 0.7  | 1.0  | LSBs  |  |

|        |                                                | External reference                                        | -5.0 | -1.0 | 5.0  |       |  |

|        | Gain error <sup>(2)</sup>                      | VDDANA/1.6                                                | -40  |      | 40   | mV    |  |

|        |                                                | VDDANA/2.0                                                | -40  |      | 40   | IIIV  |  |

|        |                                                | Bandgap After calibration                                 | -30  |      | 30   |       |  |

|        | Gain error drift vs voltage <sup>(1)</sup>     | External reference                                        | -2   |      | 2    | mV/V  |  |

|        | Gain error drift vs temperature <sup>(1)</sup> | After calibration + bandgap drift If using onchip bandgap |      |      | 0.08 | mV/°K |  |

|        |                                                | External reference                                        | -5.0 |      | 5.0  |       |  |

|        | Offset error (2)                               | VDDANA/1.6                                                | -10  |      | 10   | mV    |  |

|        |                                                | VDDANA/2.0                                                | -10  |      | 10   | IIIV  |  |

|        |                                                | Bandgap After calibration                                 | -10  |      | 10   |       |  |

|        | Offset error drift vs voltage <sup>(1)</sup>   |                                                           | -4   |      | 4    | mV/V  |  |

Where  $\mathit{SPIn}$  is the MISO delay, SPI6 or SPI9 depending on CPOL and NCPHA.  $t_{\mathit{SETUP}}$  is the SPI master setup time. refer to the SPI master datasheet for  $t_{\mathit{SETUP}}$   $.f_{\mathit{PINMAX}}$  is the maximum frequency of the SPI pins. refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

# 9.10.4 TWIM/TWIS Timing

Figure 9-64 shows the TWI-bus timing requirements and the compliance of the device with them. Some of these requirements ( $t_r$  and  $t_f$ ) are met by the device without requiring user intervention. Compliance with the other requirements ( $t_{HD-STA}$ ,  $t_{SU-STA}$ ,  $t_{SU-STO}$ ,  $t_{HD-DAT}$ ,  $t_{SU-DAT-TWI}$ ,  $t_{LOW-TWI}$ ,  $t_{HIGH}$ , and  $t_{TWCK}$ ) requires user intervention through appropriate programming of the relevant TWIM and TWIS user interface registers. refer to the TWIM and TWIS sections for more information.

**Table 9-64.** TWI-Bus Timing Requirements

|                                    |                                        | Minimum                 |                                       | Maximum               |             |                                              |      |

|------------------------------------|----------------------------------------|-------------------------|---------------------------------------|-----------------------|-------------|----------------------------------------------|------|

| Symbol                             | Parameter                              | Mode                    | Requirement                           | Device                | Requirement | Device                                       | Unit |

|                                    | TMOK and TMD via a time                | Standard <sup>(1)</sup> | -                                     | I                     | 10          | 000                                          |      |

| t <sub>r</sub>                     | TWCK and TWD rise time                 | Fast <sup>(1)</sup>     | 20 + 0.1C <sub>b</sub>                |                       | 300         |                                              | ns   |

|                                    | TMOK - a d TMD fell fire -             | Standard                | -                                     |                       | 30          | 00                                           |      |

| t <sub>f</sub>                     | TWCK and TWD fall time                 | Fast                    | 20 + 0.1C <sub>b</sub>                |                       | 300         |                                              | ns   |

| 1                                  | (Demosted) CTART hold times            | Standard                | 4                                     |                       |             |                                              |      |

| t <sub>HD-STA</sub>                | (Repeated) START hold time             | Fast                    | 0.6                                   | t <sub>clkpb</sub>    |             | -                                            | μs   |

|                                    | (Danis and all) OTA DT and are discus- | Standard                | 4.7                                   | 4                     |             |                                              | μs   |

| t <sub>SU-STA</sub>                | (Repeated) START set-up time           | Fast                    | 0.6                                   |                       |             | -                                            |      |

|                                    | OTOD and are time.                     | Standard                | 4.0                                   | 4t <sub>clkpb</sub>   | -           |                                              | μs   |

| t <sub>su-sto</sub>                | STOP set-up time                       | Fast                    | 0.6                                   |                       |             |                                              |      |

| t <sub>HD-DAT</sub> Data hold time | Data hald time                         | Standard                | 0.3 <sup>(2)</sup> 2t <sub>ckpb</sub> | 3.45()                | 454         |                                              |      |

| t <sub>HD-DAT</sub>                | Data noid time                         | Fast                    | 0.3(-/                                | 2t <sub>clkpb</sub>   | 0.9()       | 15t <sub>prescaled</sub> + t <sub>clkp</sub> | μs   |

| 1                                  | Data act up time                       | Standard                | 250                                   | 24                    |             |                                              |      |

| t <sub>SU-DAT-TWI</sub>            | Data set-up time                       | Fast                    | 100                                   | 2t <sub>clkpb</sub>   | -           |                                              | ns   |

| t <sub>SU-DAT</sub>                |                                        | -                       | -                                     | t <sub>clkpb</sub>    |             | -                                            | -    |

| +                                  | TWCK LOW period                        | Standard                | 4.7                                   | 4+                    |             |                                              |      |

| t <sub>LOW-TWI</sub>               | TWOK LOW period                        | Fast                    | 1.3                                   | 4t <sub>clkpb</sub>   | -           |                                              | μs   |

| t <sub>LOW</sub>                   |                                        | -                       | -                                     | t <sub>clkpb</sub>    |             | -                                            | -    |

| +                                  | TWCK HIGH poriod                       | Standard                | 4.0                                   | 0+                    |             |                                              |      |

| t <sub>HIGH</sub>                  | TWCK HIGH period                       | Fast                    | 0.6                                   | - 8t <sub>clkpb</sub> |             | -                                            | μs   |

| f                                  | TWCK frequency                         | Standard                |                                       | 1                     | 100         | 1                                            | kHz  |

| f <sub>TWCK</sub>                  | TWCK frequency                         | Fast                    | -                                     |                       | 400         | 12t <sub>clkpb</sub>                         | KΠZ  |

Notes: 1. Standard mode:  $f_{TWCK} \le 100 \text{ kHz}$ ; fast mode:  $f_{TWCK} > 100 \text{ kHz}$ .

Table 9-66. SWD Timings<sup>(1)</sup>

| Symbol | Parameter                                                     | Conditions                              | Min | Max     | Units |

|--------|---------------------------------------------------------------|-----------------------------------------|-----|---------|-------|

| Thigh  | SWDCLK High period                                            |                                         | 10  | 500 000 |       |

| Tlow   | SWDCLK Low period                                             | V <sub>VDDIO</sub> from 3.0 V to 3.6 V, | 10  | 500 000 |       |

| Tos    | SWDIO output skew to falling edge SWDCLK                      | maximum                                 | -5  | 5       | ns    |

| Tis    | Input Setup time required between SWDIO                       | external capacitor =                    | 4   | -       |       |

| Tih    | Input Hold time required between SWDIO and rising edge SWDCLK | 40pF                                    | 1   | -       |       |

Note: 1. These values are based on simulation. These values are not covered by test limits in production or characterization.

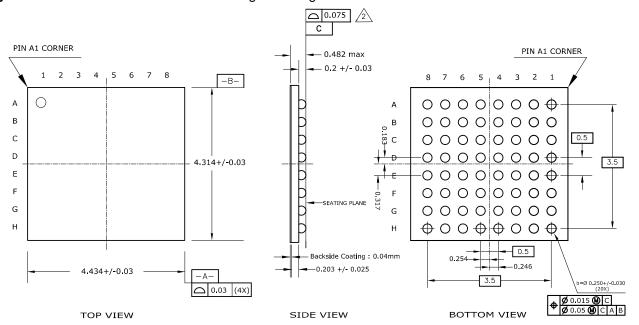

Figure 10-3. WLCSP64 SAM4LC4/2 Package Drawing

# COMMON DIMENSIONS

(Unit of Measure = mm)

| BALL | SIGNAL  | X COORD | Y COORD |

|------|---------|---------|---------|

| A1   | PB04    | 1.746   | 1.683   |

| A2   | GNDANA  | 1.246   | 1.683   |

| А3   | ADVREFP | 0.746   | 1.683   |

| A4   | VDDANA  | 0.246   | 1.683   |

| A5   | PA09    | -0.254  | 1.683   |

| A6   | CAPL    | -0.754  | 1.683   |

| Α7   | CAPH    | -1.254  | 1.683   |

| A8   | PA12    | -1.754  | 1.683   |

| B1   | PB03    | 1.746   | 1.183   |

| B2   | XIN32   | 1.246   | 1,183   |

| В3   | XOUT32  | 0.746   | 1.183   |

| B4   | PA08    | 0.246   | 1,183   |

| B5   | PB06    | -0.254  | 1.183   |

| В6   | PA10    | -0.754  | 1.183   |

| В7   | PA11    | -1.254  | 1.183   |

| В8   | VLCD    | -1.754  | 1.183   |

| C1   | VDDIN   | 1.746   | 0.683   |

| C2   | PB01    | 1.246   | 0.683   |

| C3   | PA05    | 0.746   | 0.683   |

| C4   | PA06    | 0.246   | 0.683   |

| C5   | PA07    | -0.254  | 0.683   |

| C6   | PB07    | -0.754  | 0.683   |

| BALL         SIGNAL         X COORD         Y COORD           C7         PA13         -1.254         0.683           C8         BIAS1         -1.754         0.683           D1         VDDOUT         1.746         0.183           D2         PB00         1.246         0.183           D3         PA04         0.746         0.183           D4         PB05         0.246         0.183           D5         PB12         -0.254         0.183           D6         PB08         -0.754         0.183           D7         PA14         -1.254         0.183           D8         BIAS2         -1.754         0.183           E1         GNDIN         1.746         -0.317           E2         PA03         1.246         -0.317           E3         PB02         0.746         -0.317           E5         PB13         -0.254         -0.317           E6         PB09         -0.754         -0.317           E7         PA15         -1.254         -0.317           E8         GND100         -1.754         -0.317           E8         GND100         -1.754         < |      |         |         |         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|---------|---------|

| C8 BIAS1 -1,754 0.683 D1 VDDOUT 1,746 0.183 D2 PB00 1,246 0.183 D3 PA04 0,746 0.183 D4 PB05 0.246 0.183 D5 PB12 -0.254 0.183 D6 PB08 -0.754 0.183 D7 PA14 -1.254 0.183 D8 BIAS2 -1,754 0.183 E1 GNDIN 1,746 -0.317 E2 PA03 1,246 -0.317 E3 PB02 0,746 -0.317 E4 RESET_N 0,246 -0.317 E5 PB13 -0.254 -0.317 E6 PB09 -0.754 -0.317 E7 PA15 -1.254 -0.317 E8 GNDIO -1,754 -0.317 E7 PA15 -1,254 -0.317 E7 PA15 -1,254 -0.317 E7 PA15 -1,254 -0.317 E7 PA15 -1,254 -0.317 E7 TCK 1,246 -0.817 E7 TCK 1,746 -0.817 E7 TCK 1,246 -0.817 E7 TCK 1,246 -0.817 E7 TCK 1,246 -0.817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | BALL | SIGNAL  | X COORD | Y COORD |

| D1         VDDOUT         1,746         0.183           D2         PB00         1,246         0.183           D3         PA04         0,746         0.183           D4         PB05         0,246         0.183           D5         PB12         -0,254         0.183           D6         PB08         -0,754         0.183           D7         PA14         -1,254         0.183           B8         BIAS2         -1,754         0.183           E1         GNDIN         1,746         -0,317           E2         PA03         1,246         -0,317           E4         RESET_N         0,246         -0,317           E5         PB13         -0,254         -0,317           E6         PB09         -0,754         -0,317           E7         PA15         -1,254         -0,317           E8         GNDIO0         -1,754         -0,317           E8         GNDIO0         -1,754         -0,317           E1         VDDCORE         1,746         -0,817           F1         VDDCORE         1,746         -0,817           F3         PA02         0,746          | C7   | PA13    | -1.254  | 0.683   |

| D2         PB00         1.246         0.183           D3         PA04         0.746         0.183           D4         PB05         0.246         0.183           D5         PB12         -0.254         0.183           D6         PB08         -0.754         0.183           D7         PA14         -1.254         0.183           D8         BIAS2         -1.754         0.183           E1         GNDIN         1.746         -0.317           E2         PA03         1.246         -0.317           E3         PB02         0.746         -0.317           E4         RESET_N         0.246         -0.317           E6         PB09         -0.754         -0.317           E6         PB09         -0.754         -0.317           E7         PA15         -1.254         -0.317           E8         GNDI00         -1.754         -0.317           E8         GNDI00         -1.754         -0.317           F1         VDDCORE         1.746         -0.817           F2         TCK         1.246         -0.817           F3         PA02         0.746         -     | C8   | BIAS1   | -1.754  | 0.683   |

| D3         PA04         0.746         0.183           D4         PB05         0.246         0.183           D5         PB12         -0.254         0.183           D6         PB08         -0.754         0.183           D7         PA14         -1.254         0.183           D8         BIAS2         -1.754         0.183           E1         GNDIN         1.746         -0.317           E2         PA03         1.246         -0.317           E3         PB02         0.746         -0.317           E4         RESET_N         0.246         -0.317           E5         PB13         -0.254         -0.317           E6         PB09         -0.754         -0.317           E7         PA15         -1.254         -0.317           E8         GND100         -1.754         -0.317           E8         GND100         -1.754         -0.317           F1         VDDCORE         1.746         -0.817           F2         TCK         1.246         -0.817           F3         PA02         0.746         -0.817                                                      | D1   | VDDOUT  | 1.746   | 0.183   |

| D4 PB05 0.246 0.183 D5 PB12 -0.254 0.183 D6 PB08 -0.754 0.183 D7 PA14 -1.254 0.183 D8 BIAS2 -1.754 0.183 E1 GNDIN 1.746 -0.317 E2 PA03 1.246 -0.317 E4 RESET_N 0.246 -0.317 E5 PB13 -0.254 -0.317 E6 PB09 -0.754 -0.317 E7 PA15 -1.254 -0.317 E7 TCK 1.246 -0.817 F3 PA02 0.746 -0.817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | D2   | PB00    | 1.246   | 0.183   |

| D5         PB12         -0.254         0.183           D6         PB08         -0.754         0.183           D7         PA14         -1.254         0.183           D8         BIAS2         -1.754         0.183           E1         GNDIN         1.746         -0.317           E2         PA03         1.246         -0.317           E3         PB02         0.746         -0.317           E4         RESET_N         0.246         -0.317           E5         PB13         -0.254         -0.317           E6         PB09         -0.754         -0.317           E7         PA15         -1.254         -0.317           E8         GND100         -1.754         -0.317           F1         VDDCORE         1.746         -0.817           F2         TCK         1.246         -0.817           F3         PA02         0.746         -0.817                                                                                                                                                                                                                            | D3   | PA04    | 0.746   | 0.183   |

| D6         PB08         -0.754         0.183           D7         PA14         -1.254         0.183           D8         BIAS2         -1.754         0.183           E1         GNDIN         1.746         -0.317           E2         PA03         1.246         -0.317           E3         PB02         0.746         -0.317           E4         RESET_N         0.246         -0.317           E5         PB13         -0.254         -0.317           E6         PB09         -0.754         -0.317           E7         PA15         -1.254         -0.317           E8         GND100         -1.754         -0.317           F1         VDDCORE         1.746         -0.817           F2         TCK         1.246         -0.817           F3         PA02         0.746         -0.817                                                                                                                                                                                                                                                                                   | D4   | PB05    | 0.246   | 0.183   |

| D7         PA14         -1.254         0.183           D8         BIAS2         -1.754         0.183           E1         GNDIN         1.746         -0.317           E2         PA03         1.246         -0.317           E3         PB02         0.746         -0.317           E4         RESET N         0.246         -0.317           E5         PB13         -0.254         -0.317           E6         PB09         -0.754         -0.317           E7         PA15         -1.254         -0.317           E8         GND100         -1.754         -0.317           F1         VDDCORE         1.746         -0.817           F2         TCK         1.246         -0.817           F3         PA02         0.746         -0.817                                                                                                                                                                                                                                                                                                                                          | D5   | PB12    | -0.254  | 0.183   |

| D8 BIAS2 -1,754 0.183 E1 GNDIN 1.746 -0.317 E2 PA03 1.246 -0.317 E3 PB02 0.746 -0.317 E4 RESET_N 0.246 -0.317 E5 PB13 -0.254 -0.317 E6 PB09 -0.754 -0.317 E7 PA15 -1.254 -0.317 E8 GNDIO0 -1,754 -0.317 F1 VDDCORE 1,746 -0.817 F2 TCK 1.246 -0.817 F3 PA02 0.746 -0.817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | D6   | PB08    | -0.754  | 0.183   |

| E1 GNDIN 1.746 -0.317 E2 PA03 1.246 -0.317 E3 PB02 0,746 -0.317 E4 RESET_N 0.246 -0.317 E5 PB13 -0.254 -0.317 E6 PB09 -0.754 -0.317 E7 PA15 -1.254 -0.317 E8 GNDIO0 -1.754 -0.317 F1 VDDCORE 1.746 -0.817 F2 TCK 1.246 -0.817 F3 PA02 0,746 -0.817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D7   | PA14    | -1.254  | 0.183   |

| E2         PA03         1.246         -0.317           E3         PB02         0.746         -0.317           E4         RESET_N         0.246         -0.317           E5         PB13         -0.254         -0.317           E6         PB09         -0.754         -0.317           E7         PA15         -1.254         -0.317           E8         GNDIO0         -1.754         -0.317           F1         VDDCORE         1.746         -0.817           F2         TCK         1.246         -0.817           F3         PA02         0.746         -0.817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D8   | BIAS2   | -1.754  | 0.183   |

| E3 PB02 0,746 -0.317 E4 RESET_N 0,246 -0.317 E5 PB13 -0.254 -0.317 E6 PB09 -0.754 -0.317 E7 PA15 -1.254 -0.317 E8 GND100 -1.754 -0.317 F1 VDDCORE 1,746 -0.817 F2 TCK 1,246 -0.817 F3 PA02 0,746 -0.817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | E1   | GNDIN   | 1.746   | -0.317  |

| E4         RESET_N         0.246         -0.317           E5         PB13         -0.254         -0.317           E6         PB09         -0.754         -0.317           E7         PA15         -1.254         -0.317           E8         GNDIO0         -1.754         -0.317           F1         VDDCORE         1.746         -0.817           F2         TCK         1.246         -0.817           F3         PA02         0.746         -0.817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | E2   | PA03    | 1.246   | -0.317  |

| E5 PB13 -0.254 -0.317<br>E6 PB09 -0.754 -0.317<br>E7 PA15 -1.254 -0.317<br>E8 GNDIO0 -1.754 -0.317<br>F1 VDDCORE 1.746 -0.817<br>F2 TCK 1.246 -0.817<br>F3 PA02 0.746 -0.817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | E3   |         | 0.746   | -0.317  |

| E6         PB09         -0.754         -0.317           E7         PA15         -1.254         -0.317           E8         GND100         -1.754         -0.317           F1         VDDCORE         1.746         -0.817           F2         TCK         1.246         -0.817           F3         PA02         0.746         -0.817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | E4   | RESET_N | 0.246   | -0.317  |

| E7         PA15         -1.254         -0.317           E8         GNDIO0         -1.754         -0.317           F1         VDDCORE         1.746         -0.817           F2         TCK         1.246         -0.817           F3         PA02         0.746         -0.817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | E5   | PB13    | -0.254  | -0.317  |

| E8 GNDI00 -1,754 -0,317<br>F1 VDDCORE 1,746 -0,817<br>F2 TCK 1,246 -0,817<br>F3 PA02 0,746 -0,817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | E6   | PB09    | -0.754  | -0.317  |

| F1 VDDCORE 1.746 -0.817<br>F2 TCK 1.246 -0.817<br>F3 PA02 0.746 -0.817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | E7   | PA15    | -1.254  | -0.317  |

| F2 TCK 1.246 -0.817<br>F3 PA02 0.746 -0.817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | E8   | GNDI00  | -1.754  | -0.317  |

| F3 PA02 0.746 -0.817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | F1   | VDDCORE | 1.746   | -0.817  |

| 77.02 317.10 31627                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | F2   | TCK     | 1.246   | -0.817  |

| E4 DD14 0.246 0.017                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | F3   | PA02    | 0.746   | -0.817  |

| F4   PB14   0.246   -0.817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | F4   | PB14    | 0.246   | -0.817  |

| DALL | CTCNIAL | V COODD | V COODD |

|------|---------|---------|---------|

| BALL | SIGNAL  | X COORD | Y COORD |

| F5   | PA22    | -0.254  | -0.817  |

| F6   | PB10    | -0.754  | -0.817  |

| F7   | PA16    | -1.254  | -0.817  |

| F8   | VLCDIN  | -1.754  | -0.817  |

| G1   | GNDIO1  | 1.746   | -1.317  |

| G2   | PA26    | 1.246   | -1.317  |

| G3   | PA24    | 0.746   | -1.317  |

| G4   | PA00    | 0.246   | -1.317  |

| G5   | PA01    | -0.254  | -1.317  |

| G6   | PA19    | -0.754  | -1.317  |

| G7   | PA18    | -1.254  | -1.317  |

| G8   | PA17    | -1.754  | -1.317  |

| H1   | VDDIO1  | 1.746   | 1.817   |

| H2   | PA25    | 1.246   | -1.817  |

| H3   | PA23    | 0.746   | -1.817  |

| H4   | PB15    | 0.246   | -1.817  |

| H5   | PA21    | -0.254  | -1.817  |

| H6   | VDDI00  | -0.754  | -1.817  |

| H7   | PA20    | -1.254  | -1.817  |

| H8   | PB11    | -1.754  | -1.817  |

|      |         |         |         |

Notes: 1. Dimension "b" is measured at the maximum ball diameter in a plane to the seating plane.

Table 10-8. Device and Package Maximum Weight

|                            |                         | 5    |

|----------------------------|-------------------------|------|

| Table 10-9.                | Package Characteristics |      |

| Moisture Sensitivity Level |                         | MSL3 |

mg

### Table 10-10. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E1     |

14.8

<sup>2.</sup> Applied to whole wafer.

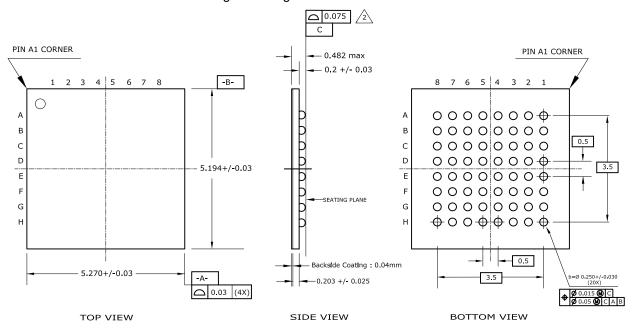

Figure 10-6. WLCSP64 SAM4LS8 Package Drawing

#### COMMON DIMENSIONS (Unit of Measure = mm)

| DALL | CTCNIAL | V 600DD | V 6000D |

|------|---------|---------|---------|

| BALL | SIGNAL  | X COORD | Y COORD |

| A1   | PB04    | 1.75    | 1.75    |

| A2   | GNDANA  | 1.75    | 1.25    |

| А3   | ADVREFP | 1.75    | 0.75    |

| A4   | VDDANA  | 1.75    | 0.25    |

| A5   | PA09    | 1.75    | -0.25   |

| A6   | PA28    | 1.75    | -0.75   |

| Α7   | PA27    | 1.75    | -1.25   |