Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M4                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 80                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.68V ~ 3.6V                                                               |

| Data Converters            | A/D 15x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-VFBGA                                                                  |

| Supplier Device Package    | 100-VFBGA (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4ls2ca-cfur |

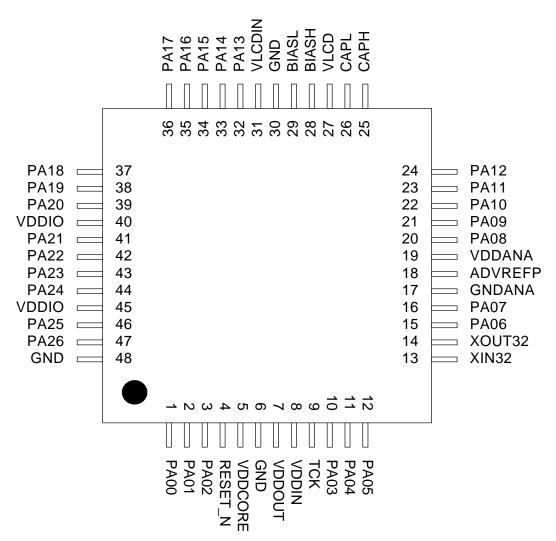

Figure 3-5. ATSAM4LC TQFP48/QFN48 Pinout

Figure 3-7. ATSAM4LS VFBGA100 Pinout

|   | 1           | 2           | 3    | 4     | 5       | 6           | 7    | 8     | 9    | 10    |

|---|-------------|-------------|------|-------|---------|-------------|------|-------|------|-------|

| Α | PA05        | PA04        | GND  | VDDIN | VDDOUT  | VDD<br>CORE | PA02 | VDDIO | GND  | PC00  |

| В | PB05        | XIN32       | PA03 | TCK   | RESET_N | PC06        | PC03 | PA01  | PA00 | GND   |

| С | PB04        | XOUT32      | PA06 | PB03  | PC04    | PC05        | PC02 | PC01  | PA26 | VDDIO |

| D | AD<br>VREFN | GNDANA      | PA07 | PC10  | PB01    | PA23        | PB14 | PB15  | PA25 | PA24  |

| Е | (VDDANA)    | AD<br>VREFP | PC08 | PC11  | PB02    | (VDDIO)     | PB12 | PB13  | PA21 | PA22  |

| F | PC09        | PC07        | PC12 | PC13  | PA09    | PC27        | PC29 | PC30  | PC31 | VDDIO |

| G | PC14        | PA08        | PB06 | PC19  | PA15    | PB08        | PB09 | PB10  | PC26 | PC28  |

| Н | PB07        | PA10        | PA11 | PC17  | PA13    | PA17        | PC20 | PC23  | PC25 | PA20  |

| J | PA28        | PA12        | PB00 | VDDIO | PC15    | PC16        | PA16 | PC22  | PC24 | PA19  |

| K | PA27        | PA29        | GND  | PA30  | PA31    | PC18        | PA14 | PC21  | PB11 | PA18  |

## 3.2 Peripheral Multiplexing on I/O lines

## 3.2.1 Multiplexed Signals

Each GPIO line can be assigned to one of the peripheral functions. The following tables (Section 3-1 "100-pin GPIO Controller Function Multiplexing" on page 19 to Section 3-4 "48-pin GPIO Controller Function Multiplexing" on page 28) describes the peripheral signals multiplexed to the GPIO lines.

Peripheral functions that are not relevant in some parts of the family are grey-shaded.

For description of differents Supply voltage source, refer to the Section 6. "Power and Startup Considerations" on page 46.

Table 3-1. 100-pin GPIO Controller Function Multiplexing (Sheet 1 of 4)

|     | ATSAM4LC   |     | ATSAM4LS   | Pin  | GPIO | Supply | GPIO Functions |               |                  |                 |                   |                |                 |

|-----|------------|-----|------------|------|------|--------|----------------|---------------|------------------|-----------------|-------------------|----------------|-----------------|

| QFN | VFBGA      | QFN | VFBGA      |      |      |        | Α              | В             | С                | D               | E                 | F              | G               |

| 5   | В9         | 5   | В9         | PA00 | 0    | VDDIO  |                |               |                  |                 |                   |                |                 |

| 6   | B8         | 6   | B8         | PA01 | 1    | VDDIO  |                |               |                  |                 |                   |                |                 |

| 12  | A7         | 12  | A7         | PA02 | 2    | VDDIN  | SCIF<br>GCLK0  | SPI<br>NPCS0  |                  |                 |                   |                | CATB<br>DIS     |

| 19  | В3         | 19  | В3         | PA03 | 3    | VDDIN  |                | SPI<br>MISO   |                  |                 |                   |                |                 |

| 24  | A2         | 24  | A2         | PA04 | 4    | VDDANA | ADCIFE<br>AD0  | USART0<br>CLK | EIC<br>EXTINT2   | GLOC<br>IN1     |                   |                | CATB<br>SENSE0  |

| 25  | A1         | 25  | <b>A</b> 1 | PA05 | 5    | VDDANA | ADCIFE<br>AD1  | USART0<br>RXD | EIC<br>EXTINT3   | GLOC<br>IN2     | ADCIFE<br>TRIGGER |                | CATB<br>SENSE1  |

| 30  | С3         | 30  | C3         | PA06 | 6    | VDDANA | DACC<br>VOUT   | USART0<br>RTS | EIC<br>EXTINT1   | GLOC<br>IN0     | ACIFC<br>ACAN0    |                | CATB<br>SENSE2  |

| 31  | D3         | 31  | D3         | PA07 | 7    | VDDANA | ADCIFE<br>AD2  | USART0<br>TXD | EIC<br>EXTINT4   | GLOC<br>IN3     | ACIFC<br>ACAP0    |                | CATB<br>SENSE3  |

| 44  | G2         | 44  | G2         | PA08 | 8    | LCDA   | USART0<br>RTS  | TC0<br>A0     | PEVC<br>PAD EVT0 | GLOC<br>OUT0    |                   | LCDCA<br>SEG23 | CATB<br>SENSE4  |

| 47  | F5         | 47  | F5         | PA09 | 9    | LCDA   | USART0<br>CTS  | TC0<br>B0     | PEVC<br>PAD EVT1 | PARC<br>PCDATA0 |                   | LCDCA<br>COM3  | CATB<br>SENSE5  |

| 48  | H2         | 48  | H2         | PA10 | 10   | LCDA   | USART0<br>CLK  | TC0<br>A1     | PEVC<br>PAD EVT2 | PARC<br>PCDATA1 |                   | LCDCA<br>COM2  | CATB<br>SENSE6  |

| 49  | Н3         | 49  | Н3         | PA11 | 11   | LCDA   | USART0<br>RXD  | TC0<br>B1     | PEVC<br>PAD EVT3 | PARC<br>PCDATA2 |                   | LCDCA<br>COM1  | CATB<br>SENSE7  |

| 50  | J2         | 50  | J2         | PA12 | 12   | LCDA   | USART0<br>TXD  | TC0<br>A2     |                  | PARC<br>PCDATA3 |                   | LCDCA<br>COM0  | CATB<br>DIS     |

| 63  | H5         | 63  | Н5         | PA13 | 13   | LCDA   | USART1<br>RTS  | TC0<br>B2     | SPI<br>NPCS1     | PARC<br>PCDATA4 |                   | LCDCA<br>SEG5  | CATB<br>SENSE8  |

| 64  | <b>K</b> 7 | 64  | <b>K</b> 7 | PA14 | 14   | LCDA   | USART1<br>CLK  | TC0<br>CLK0   | SPI<br>NPCS2     | PARC<br>PCDATA5 |                   | LCDCA<br>SEG6  | CATB<br>SENSE9  |

| 65  | G5         | 65  | G5         | PA15 | 15   | LCDA   | USART1<br>RXD  | TC0<br>CLK1   | SPI<br>NPCS3     | PARC<br>PCDATA6 |                   | LCDCA<br>SEG7  | CATB<br>SENSE10 |

Table 4-2.

Interrupt Request Signal Map (Sheet 3 of 3)

| Line | Module                                                     | Signal |

|------|------------------------------------------------------------|--------|

| 48   | External Interrupt Controller                              | EIC 4  |

| 49   | External Interrupt Controller                              | EIC 5  |

| 50   | External Interrupt Controller                              | EIC 6  |

| 51   | External Interrupt Controller                              | EIC 7  |

| 52   | External Interrupt Controller                              | EIC 8  |

| 53   | Inter-IC Sound (I2S) Controller                            | IISC   |

| 54   | Serial Peripheral Interface                                | SPI    |

| 55   | Timer/Counter                                              | TC00   |

| 56   | Timer/Counter                                              | TC01   |

| 57   | Timer/Counter                                              | TC02   |

| 58   | Timer/Counter                                              | TC10   |

| 59   | Timer/Counter                                              | TC11   |

| 60   | Timer/Counter                                              | TC12   |

| 61   | Two-wire Master Interface                                  | TWIM0  |

| 62   | Two-wire Slave Interface                                   | TWIS0  |

| 63   | Two-wire Master Interface                                  | TWIM1  |

| 64   | Two-wire Slave Interface                                   | TWIS1  |

| 65   | Universal Synchronous Asynchronous<br>Receiver Transmitter | USART0 |

| 66   | Universal Synchronous Asynchronous<br>Receiver Transmitter | USART1 |

| 67   | Universal Synchronous Asynchronous<br>Receiver Transmitter | USART2 |

| 68   | Universal Synchronous Asynchronous<br>Receiver Transmitter | USART3 |

| 69   | ADC controller interface                                   | ADCIFE |

| 70   | DAC Controller                                             | DACC   |

| 71   | Analog Comparator Interface                                | ACIFC  |

| 72   | Audio Bitstream DAC                                        | ABDACB |

| 73   | True Random Number Generator                               | TRNG   |

| 74   | Parallel Capture                                           | PARC   |

| 75   | Capacitive Touch Module B                                  | CATB   |

| 77   | Two-wire Master Interface                                  | TWIM2  |

| 78   | Two-wire Master Interface                                  | TWIM3  |

| 79   | LCD Controller A                                           | LCDCA  |

| Mamani              | Start Address | Size      |

|---------------------|---------------|-----------|

| Memory              |               | ATSAM4Lx8 |

| AESA                | 0x400B0000    | 256 bytes |

| Peripheral Bridge C | 0x400E0000    | 64Kbytes  |

| Peripheral Bridge D | 0x400F0000    | 64Kbytes  |

Table 5-2.

Flash Memory Parameters

| Device    | Flash Size (FLASH_PW) | Number of Pages (FLASH_P) | Page Size (FLASH_W) |

|-----------|-----------------------|---------------------------|---------------------|

| ATSAM4Lx8 | 512Kbytes             | 1024                      | 512 bytes           |

| ATSAM4Lx4 | 256Kbytes             | 512                       | 512 bytes           |

| ATSAM4Lx2 | 128Kbytes             | 256                       | 512 bytes           |

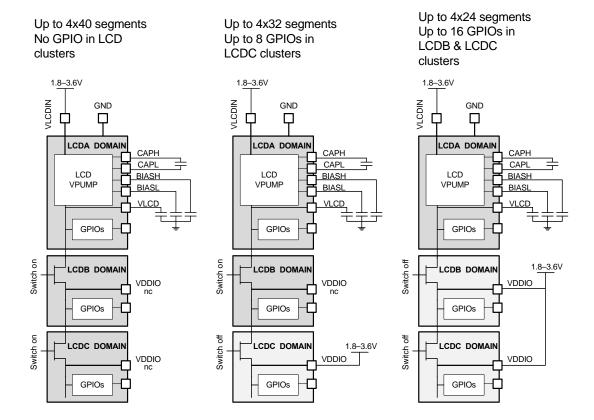

connected to an external voltage source (1.8-3.6V). LCDB cluster is not available in 64 and 48 pin packages

**Table 6-1.** LCD powering when using the internal voltage pump

| Package          | Segments in use | VDDIO<br>LCDB | VDDIO<br>LCDC |

|------------------|-----------------|---------------|---------------|

|                  | [1,24]          | 1.8-3.6V      | 1.8-3.6V      |

| 100-pin packages | [1, 32]         | nc            | 1.8-3.6V      |

|                  | [1, 40]         | nc            | nc            |

| 64-pin packages  | [1,15]          | -             | 1.8-3.6V      |

| 04-ріп раскаўся  | [1, 23]         | -             | nc            |

| 48-pin packages  | [1,9]           | -             | 1.8-3.6V      |

| To pin packages  | [1,13]          | -             | nc            |

52

#### 7.1.3 BACKUP Mode

The BACKUP mode allows achieving the lowest power consumption possible in a system which is performing periodic wake-ups to perform tasks but not requiring fast startup time.

The Core domain is powered-off. The internal SRAM and register contents of the Core domain are lost. The Backup domain is kept powered-on. The 32kHz clock (RC32K or OSC32K) is kept running if enabled to feed modules that require clocking.

In BACKUP mode, the configuration of the I/O lines is preserved. Refer to Section 9. "Backup Power Manager (BPM)" on page 677 to have more details.

## 7.1.3.1 Entering BACKUP Mode

The Backup mode is entered by using the WFI instruction with the following settings:

- set the SCR.SLEEPDEEP bit to 1. (See the Power Management section in the ARM Cortex-M4 Processor chapter).

- set the BPM.PSAVE.BKUP bit to 1.

#### 7.1.3.2 Exiting BACKUP Mode

Exit from BACKUP mode happens if a reset occurs or if an enabled wake up event occurs.

The reset sources are:

- BOD33 reset

- BOD18 reset

- WDT reset

- External reset in RESET\_N pin

The wake up sources are:

- EIC lines (level transition only)

- BOD33 interrupt

- BOD18 interrupt

- AST alarm, periodic, overflow

- WDT interrupt

The RC32K or OSC32K should be used as clock source for modules if required. The PMCON.CK32S is used to select one of these two 32kHz clock sources.

Exiting the BACKUP mode is triggered by:

- a reset source: an internal reset sequence is performed according to the reset source. Once VDDCORE is stable and has the correct value according to RUN0 mode, the internal reset is released and program execution starts. The corresponding reset source is flagged in the Reset Cause register (RCAUSE) of the PM.

- a wake up source: the Backup domain is not reset. An internal reset is generated to the Core

domain, and the system switches back to the previous RUN mode. Once VDDCORE is

stable and has the correct value, the internal reset in the Core domain is released and

program execution starts. The BKUP bit is set in the Reset Cause register (RCAUSE) of the

PM. It allows the user to discriminate between the reset cause and a wake up cause from the

BACKUP mode. The wake up cause can be found in the Backup Wake up Cause register

(BPM.BKUPWCAUSE).

## 8.5 Product dependencies

#### 8.5.1 I/O Lines

Refer to Section 1.1.5.1 "I/O Lines" on page 5.

#### 8.5.2 Power management

Refer to Section 1.1.5.2 "Power Management" on page 5.

#### 8.5.3 Clocks

Refer to Section 1.1.5.3 "Clocks" on page 5.

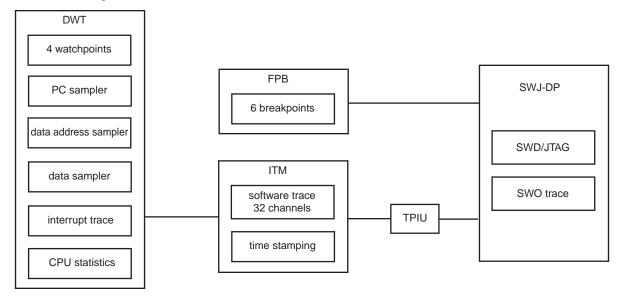

## 8.6 Core debug

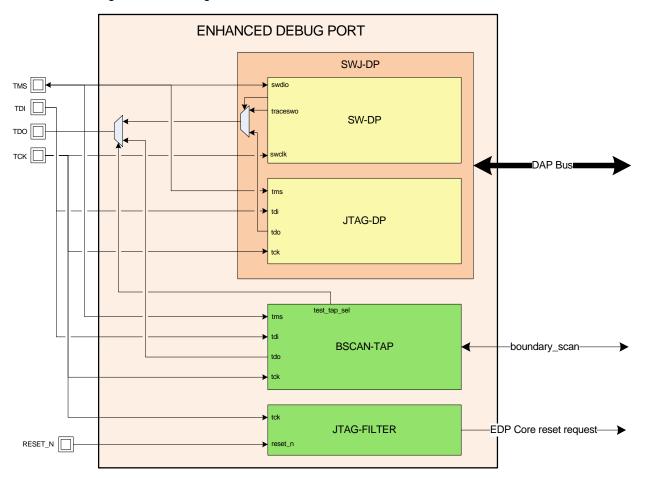

Figure 8-2 shows the Debug Architecture used in the SAM4L. The Cortex-M4 embeds four functional units for debug:

- FPB (Flash Patch Breakpoint)

- DWT (Data Watchpoint and Trace)

- ITM (Instrumentation Trace Macrocell)

- TPIU (Trace Port Interface Unit)

The debug architecture information that follows is mainly dedicated to developers of SWJ-DP Emulators/Probes and debugging tool vendors for Cortex-M4 based microcontrollers. For further details on SWJ-DP see the Cortex-M4 technical reference manual.

Figure 8-2. Debug Architecture

#### 8.6.1 FPB (Flash Patch Breakpoint)

The FPB:

- · Implements hardware breakpoints

- Patches (on the fly) code and data being fetched by the Cortex-M4 core from code space with data in the system space. Definition of code and system spaces can be found in the System Address Map section of the ARMv7-M Architecture Reference Manual.

## 8.7.3 Block Diagram

Figure 8-3. Enhanced Debug Port Block Diagram

## 8.7.4 I/O Lines Description

Table 8-1. I/O Lines Description

| Name         |      | JTAG Debug Port   | SWD Debug Port |                             |  |

|--------------|------|-------------------|----------------|-----------------------------|--|

|              | Туре | Description       | Туре           | Description                 |  |

| TCK/SWCLK    | I    | Debug Clock       | I              | Serial Wire Clock           |  |

| TDI          | I    | Debug Data in     | -              | NA                          |  |

| TDO/TRACESWO | 0    | Debug Data Out    | 0              | Trace asynchronous Data Out |  |

| TMS/SWDIO    | I    | Debug Mode Select | I/O            | Serial Wire Input/Output    |  |

| RESET_N      | I    | Reset             | I              | Reset                       |  |

70

The Debug Port pins assignation is then forced to the EDP function even if they were already assigned to another module. This allows to connect a debugger at any time without reseting the device. The connection is non-intrusive meaning that the chip will continue its execution without being disturbed. The CPU can of course be halted later on by issuing Cortex-M4 OCD features.

### 8.7.8 SMAP Core Reset Request Source

The EDP has the ability to send a request to the SMAP for a Cortex-M4 Core reset. The procedure to do so is to hold TCK low until RESET\_N is released. This mechanism aims at halting the CPU to prevent it from changing the system configuration while the SMAP is operating.

Figure 8-5. SMAP Core Reset Request Timings Diagram

The SMAP can de-assert the core reset request for this operation, refer to Section 2.8.8 "Cortex-M4 Core Reset Source" on page 57.

#### 8.7.9 SWJ-DP

The Cortex-M4 embeds a SWJ-DP Debug port which is the standard CoreSight<sup>™</sup> debug port. It combines Serial Wire Debug Port (SW-DP), from 2 to 3 pins and JTAG debug Port(JTAG-DP), 5 pins.

By default, the JTAG Debug Port is active. If the host debugger wants to switch to the Serial Wire Debug Port, it must provide a dedicated JTAG sequence on TMS/SWDIO and TCK/SWCLK which disables JTAG-DP and enables SW-DP.

When the EDP has been switched to Serial Wire mode, TDO/TRACESWO can be used for trace (for more information refer to the section below). The asynchronous TRACE output (TRACESWO) is multiplexed with TDO. So the asynchronous trace can only be used with SW-DP, not JTAG-DP.

The SWJ-DP provides access to the AHB-AP and SMAP access ports which have the following APSEL value:

Figure 8-6. Access Ports APSEL

| Acces Port (AP) | APSEL |

|-----------------|-------|

| AHB-AP          | 0     |

| SMAP            | 1     |

Refer to the ARM Debug Interface v5.1 Architecture Specification for more details on SWJ-DP.

8.9.11.7 Module Version

Name: VERSION

Access Type: Read-Only

Offset: 0x28

Reset Value: -

| 31 | 30 | 29 | 28  | 27      | 26  | 25   | 24 |  |

|----|----|----|-----|---------|-----|------|----|--|

| -  | -  | -  | -   | -       | -   | -    | -  |  |

|    |    |    |     |         |     |      | _  |  |

| 23 | 22 | 21 | 20  | 19      | 18  | 17   | 16 |  |

| -  | -  | -  | -   | VARIANT |     |      |    |  |

|    |    |    |     |         |     |      | _  |  |

| 15 | 14 | 13 | 12  | 11      | 10  | 9    | 8  |  |

| -  | -  | -  | -   |         | VER | SION |    |  |

|    |    |    |     |         |     |      |    |  |

| 7  | 6  | 5  | 4   | 3       | 2   | 1    | 0  |  |

|    |    |    | VER | SION    |     |      |    |  |

VARIANT: Variant number

Reserved. No functionality associated.

## • VERSION: Version number

Version number of the module. No functionality associated.

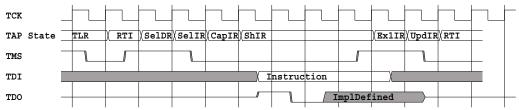

Apply the TMS sequence 1, 1, 0 to re-enter the Run-Test/Idle state. The instruction is latched onto the parallel output from the shift register path in the Update-IR state. The Exit-IR, Pause-IR, and Exit2-IR states are only used for navigating the state machine.

Figure 8-10. Scanning in JTAG instruction

#### 8.11.5.2 Scanning in/out data

At the TMS input, apply the sequence 1, 0, 0 at the rising edges of TCK to enter the Shift Data Register - Shift-DR state. While in this state, upload the selected Data Register (selected by the present JTAG instruction in the JTAG Instruction Register) from the TDI input at the rising edge of TCK. In order to remain in the Shift-DR state, the TMS input must be held low. While the Data Register is shifted in from the TDI pin, the parallel inputs to the Data Register captured in the Capture-DR state is shifted out on the TDO pin.

Apply the TMS sequence 1, 1, 0 to re-enter the Run-Test/Idle state. If the selected Data Register has a latched parallel-output, the latching takes place in the Update-DR state. The Exit-DR, Pause-DR, and Exit2-DR states are only used for navigating the state machine.

As shown in the state diagram, the Run-Test/Idle state need not be entered between selecting JTAG instruction and using Data Registers.

#### 8.11.6 Boundary-Scan

The Boundary-Scan chain has the capability of driving and observing the logic levels on the digital I/O pins, as well as the boundary between digital and analog logic for analog circuitry having off-chip connections. At system level, all ICs having JTAG capabilities are connected serially by the TDI/TDO signals to form a long shift register. An external controller sets up the devices to drive values at their output pins, and observe the input values received from other devices. The controller compares the received data with the expected result. In this way, Boundary-Scan provides a mechanism for testing interconnections and integrity of components on Printed Circuits Boards by using the 4 TAP signals only.

The four IEEE 1149.1 defined mandatory JTAG instructions IDCODE, BYPASS, SAMPLE/PRE-LOAD, and EXTEST can be used for testing the Printed Circuit Board. Initial scanning of the data register path will show the ID-code of the device, since IDCODE is the default JTAG instruction. It may be desirable to have the device in reset during test mode. If not reset, inputs to the device may be determined by the scan operations, and the internal software may be in an undetermined state when exiting the test mode. Entering reset, the outputs of any Port Pin will instantly enter the high impedance state, making the HIGHZ instruction redundant. If needed, the BYPASS instruction can be issued to make the shortest possible scan chain through the device. The device can be set in the reset state by pulling the external RESET\_N pin low.

The EXTEST instruction is used for sampling external pins and loading output pins with data. The data from the output latch will be driven out on the pins as soon as the EXTEST instruction is loaded into the JTAG IR-register. Therefore, the SAMPLE/PRELOAD should also be used for setting initial values to the scan ring, to avoid damaging the board when issuing the EXTEST

**Table 9-12.** Typical Current Consumption by Peripheral in Power Scaling Mode 1 (1)

| Peripheral            | Typ Consumption Active | Unit   |

|-----------------------|------------------------|--------|

| IISC                  | 0.5                    |        |

| SPI                   | 1.1                    |        |

| TC                    | 3.1                    |        |

| TWIM                  | 0.8                    |        |

| TWIS                  | 0.7                    |        |

| USART                 | 4.4                    |        |

| ADCIFE <sup>(2)</sup> | 1.6                    |        |

| DACC                  | 0.6                    |        |

| ACIFC (2)             | 1.6                    |        |

| GLOC                  | 0.1                    |        |

| ABDACB                | 0.3                    |        |

| TRNG                  | 0.3                    |        |

| PARC                  | 0.3                    |        |

| CATB                  | 1.5                    |        |

| LCDCA                 | 2.2                    | μΑ/MHz |

| PDCA                  | 0.4                    |        |

| CRCCU                 | 0.3                    |        |

| USBC                  | 0.9                    |        |

| PEVC                  | 2.8                    |        |

| CHIPID                | 0.1                    |        |

| SCIF                  | 3.1                    |        |

| FREQM                 | 0.2                    |        |

| GPIO                  | 3.4                    |        |

| BPM                   | 0.4                    |        |

| BSCIF                 | 2.3                    |        |

| AST                   | 0.8                    |        |

| WDT                   | 0.8                    |        |

| EIC                   | 0.3                    |        |

| PICOUART              | 0.2                    |        |

<sup>1.</sup> These numbers are valid for the measured condition only and must not be extrapolated to other frequencies

<sup>2.</sup> Includes the current consumption on VDDANA and ADVREFP.

## 9.6.3 USB I/O Pin: PA25, PA26

**Table 9-15.** USB I/O Pin Characteristics in GPIO configuration (1)

| Symbol                | Parameter                                | Conditions                 |                                  | Min                    | Тур  | Max                    | Units |

|-----------------------|------------------------------------------|----------------------------|----------------------------------|------------------------|------|------------------------|-------|

| R <sub>PULLUP</sub>   | Pull-up resistance (2)                   |                            |                                  |                        | 40   |                        | kΩ    |

| R <sub>PULLDOWN</sub> | Pull-down resistance <sup>(2)</sup>      |                            |                                  |                        | 40   |                        | kΩ    |

| V <sub>IL</sub>       | Input low-level voltage                  |                            |                                  | -0.3                   |      | 0.2 * V <sub>VDD</sub> |       |

| V <sub>IH</sub>       | Input high-level voltage                 |                            |                                  | 0.8 * V <sub>VDD</sub> |      | V <sub>VDD</sub> + 0.3 | .,    |

| V <sub>OL</sub>       | Output low-level voltage                 |                            |                                  |                        |      | 0.4                    | V     |

| V <sub>OH</sub>       | Output high-level voltage                |                            |                                  | V <sub>VDD</sub> - 0.4 |      |                        |       |

|                       | 0 (3)                                    | 00000                      | 1.68V <v<sub>VDD&lt;2.7V</v<sub> |                        | 20   |                        |       |

| I <sub>OL</sub>       | Output low-level current (3)             | ODCR0=0                    | 2.7V <v<sub>VDD&lt;3.6V</v<sub>  |                        | 30   |                        | mA mA |

|                       | (2)                                      | 00000                      | 1.68V <v<sub>VDD&lt;2.7V</v<sub> |                        | 20   |                        |       |

| I <sub>OH</sub>       | Output high-level current <sup>(3)</sup> | ODCR0=0                    | 2.7V <v<sub>VDD&lt;3.6V</v<sub>  |                        | 30   |                        | mA    |

| F <sub>PINMAX</sub>   | Maximum frequency <sup>(2)</sup>         | ODCR0=0<br>OSRR0=0         | load = 25pF                      |                        |      | 20                     | MHz   |

| I <sub>LEAK</sub>     | Input leakage current <sup>(3)</sup>     | Pull-up resistors disabled |                                  |                        | 0.01 | 1                      | μA    |

| C <sub>IN</sub>       | Input capacitance <sup>(2)</sup>         |                            |                                  |                        | 5    |                        | pF    |

- 1.  $V_{VDD}$  corresponds to either  $V_{VDDIN}$  or  $V_{VDDIO}$ , depending on the supply for the pin. Refer to Section 3-5 on page 13 for details

- 2. These values are based on simulation. These values are not covered by test limits in production or characterization

- 3. These values are based on characterization. These values are not covered by test limits in production

# 9.6.4 TWI Pin: PA21, PA22, PA23, PA24, PB14, PB15 Table 9-16. TWI Pin Characteristics in TWI configuration (1)

| Symbol                | Parameter                           | Conditions | Min                    | Тур | Max                    | Units |

|-----------------------|-------------------------------------|------------|------------------------|-----|------------------------|-------|

| R <sub>PULLUP</sub>   | Pull-up resistance (2)              |            |                        | 40  |                        | kΩ    |

| R <sub>PULLDOWN</sub> | Pull-down resistance <sup>(2)</sup> |            |                        | 40  |                        | kΩ    |

| V <sub>IL</sub>       | Input low-level voltage             |            | -0.3                   |     | 0.3 * V <sub>VDD</sub> | V     |

| V <sub>IH</sub>       | Input high-level voltage            |            | 0.7 * V <sub>VDD</sub> |     | V <sub>VDD</sub> + 0.3 | V     |

| V <sub>OL</sub>       | Output low-level voltage            |            |                        |     | 0.4                    | V     |

|                       |                                     | DRIVEL=0   |                        |     | 0.5                    |       |

|                       |                                     | DRIVEL=1   |                        |     | 1.0                    |       |

|                       |                                     | DRIVEL=2   |                        |     | 1.6                    |       |

|                       | 0                                   | DRIVEL=3   |                        |     | 3.1                    |       |

| I <sub>OL</sub>       | Output low-level current (3)        | DRIVEL=4   |                        |     | 6.2                    | mA    |

|                       |                                     | DRIVEL=5   |                        |     | 9.3                    |       |

|                       |                                     | DRIVEL=6   |                        |     | 15.5                   |       |

|                       |                                     | DRIVEL=7   |                        |     | 21.8                   |       |

Table 9-20. High Drive TWI Pin Characteristics in GPIO configuration (1)

| Symbol                | Parameter                                | Conditions |                                                    | Min                    | Тур | Max                    | Units |  |

|-----------------------|------------------------------------------|------------|----------------------------------------------------|------------------------|-----|------------------------|-------|--|

| R <sub>PULLUP</sub>   | Pull-up resistance (2)                   |            |                                                    |                        | 40  |                        | kΩ    |  |

| R <sub>PULLDOWN</sub> | Pull-up resistance <sup>(2)</sup>        |            |                                                    |                        | 40  |                        | kΩ    |  |

| V <sub>IL</sub>       | Input low-level voltage                  |            |                                                    | -0.3                   |     | 0.2 * V <sub>VDD</sub> |       |  |

| V <sub>IH</sub>       | Input high-level voltage                 |            |                                                    | 0.8 * V <sub>VDD</sub> |     | V <sub>VDD</sub> + 0.3 | .,    |  |

| V <sub>OL</sub>       | Output low-level voltage                 |            |                                                    |                        |     | 0.4                    | V     |  |

| $V_{OH}$              | Output high-level voltage                |            |                                                    | V <sub>VDD</sub> - 0.4 |     |                        |       |  |

|                       |                                          | ODCR0=0    | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                        |     | 3.4                    | A     |  |

|                       | Output low-level current (3)             | ODCR0=0    | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                        |     | 6                      | mA    |  |

| l <sub>OL</sub>       | Output low-level current                 | ODCD0 4    | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                        |     | 5.2                    | A     |  |

|                       |                                          | ODCR0=1    | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                        |     | 8                      | mA    |  |

|                       |                                          | ODCR0=0    | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                        |     | 3.4                    | A     |  |

|                       | Output high-level current <sup>(3)</sup> | ODCK0=0    | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                        |     | 6                      | mA    |  |

| I <sub>OH</sub>       | Output nign-level current                | ODCD0 4    | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                        |     | 5.2                    | A     |  |

|                       |                                          | ODCR0=1    | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                        |     | 8                      | mA    |  |

|                       |                                          | OSRR0=0    | ODCR0=0                                            |                        | 18  |                        |       |  |

|                       | Dia - (in (2)                            | OSRR0=1    | 1.68V <v<sub>VDD&lt;2.7V,<br/>Cload = 25pF</v<sub> |                        | 110 |                        | ns    |  |

| t <sub>RISE</sub>     | Rise time <sup>(2)</sup>                 | OSRR0=0    | ODCR0=0                                            |                        | 10  |                        |       |  |

|                       |                                          | OSRR0=1    | $2.7V < V_{VDD} < 3.6V$ , Cload = $25pF$           |                        | 50  |                        | ns    |  |

|                       |                                          | OSRR0=0    | ODCR0=0                                            |                        | 19  |                        |       |  |

|                       | Fall time <sup>(2)</sup>                 | OSRR0=1    | 1.68V <v<sub>VDD&lt;2.7V,<br/>Cload = 25pF</v<sub> |                        | 140 |                        | ns    |  |

| t <sub>FALL</sub>     | rail liiile                              | OSRR0=0    | ODCR0=0                                            |                        | 12  |                        |       |  |

|                       |                                          | OSRR0=1    | $2.7V < V_{VDD} < 3.6V$ , Cload = $25pF$           |                        | 63  |                        | ns    |  |

<sup>1.</sup> V<sub>VDD</sub> corresponds to either V<sub>VDDIN</sub> or V<sub>VDDIO</sub>, depending on the supply for the pin. Refer to Section 3-5 on page 13 for details

Table 9-21.

Common High Drive TWI Pin Characteristics

| Symbol            | Parameter                        | Conditions                 | Min | Тур  | Max | Units |

|-------------------|----------------------------------|----------------------------|-----|------|-----|-------|

| I <sub>LEAK</sub> | Input leakage current (1)        | Pull-up resistors disabled |     | 0.01 | 2   | μA    |

| C <sub>IN</sub>   | Input capacitance <sup>(1)</sup> |                            |     | 10   |     | pF    |

<sup>1.</sup> These values are based on simulation. These values are not covered by test limits in production or characterization

<sup>2.</sup> These values are based on simulation. These values are not covered by test limits in production or characterization

<sup>3.</sup> These values are based on characterization. These values are not covered by test limits in production

125

Table 9-27. Digital Frequency Locked Loop Characteristics

| Symbol               | Parameter                   | Conditions                                                                                       |  | Тур  | Max | Unit |

|----------------------|-----------------------------|--------------------------------------------------------------------------------------------------|--|------|-----|------|

| t <sub>STARTUP</sub> | Startup time <sup>(1)</sup> | Within 90% of final values                                                                       |  |      | 100 | μs   |

|                      |                             | f <sub>REF</sub> = 32 kHz, FINE lock, SSG disabled <sup>(2)</sup>                                |  | 600  |     |      |

| t <sub>LOCK</sub>    | Lock time <sup>(1)</sup>    | f <sub>REF</sub> = 32 kHz, ACCURATE lock, dithering clock = RCSYS/2, SSG disabled <sup>(2)</sup> |  | 1100 |     |      |

- 1. These values are based on simulation. These values are not covered by test limits in production or characterization.

- 2. Spread Spectrum Generator (SSG) is disabled by writing a zero to the EN bit in the SCIF.DFLL0SSG register.

## 9.7.5 32kHz RC Oscillator (RC32K) Characteristics

Table 9-28. 32kHz RC Oscillator Characteristics

| Symbol                                                | Parameter                   | Conditions                                                                 | Min | Тур    | Max | Unit  |

|-------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------|-----|--------|-----|-------|

| f <sub>OUT</sub>                                      | Output frequency (1)        | Calibrated against a 32.768kHz reference Temperature compensation disabled | 20  | 32.768 | 44  | kHz   |

|                                                       | Current concumption (2)     | Without temperature compensation                                           |     | 0.5    |     | μΑ    |

| I <sub>RC32K</sub> Current consumption <sup>(2)</sup> |                             | Temperature compensation enabled                                           |     | 2      |     | μA    |

| t <sub>STARTUP</sub>                                  | Startup time <sup>(1)</sup> |                                                                            |     | 1      |     | cycle |

- 1. These values are based on characterization. These values are not covered by test limits in production.

- 2. These values are based on simulation. These values are not covered by test limits in production or characterization.

#### 9.7.6 System RC Oscillator (RCSYS) Characteristics

Table 9-29.

System RC Oscillator Characteristics

| Symbol               | Parameter                   | Conditions         | Min  | Тур   | Max  | Unit |

|----------------------|-----------------------------|--------------------|------|-------|------|------|

| f <sub>OUT</sub>     | Output frequency (1)        | Calibrated at 85°C | 110  | 113.6 | 116  | kHz  |

| I <sub>RCSYS</sub>   | Current consumption (2)     |                    |      |       | 12   | μΑ   |

| t <sub>STARTUP</sub> | Startup time <sup>(1)</sup> |                    | 25   | 38    | 63   | μs   |

| Duty                 | Duty cycle <sup>(1)</sup>   |                    | 49.6 | 50    | 50.3 | %    |

- 1. These values are based on characterization. These values are not covered by test limits in production.

- 2. These values are based on simulation. These values are not covered by test limits in production or characterization.

Table 9-39. VREG Electrical Characteristics in Switching mode

| Symbol           | Parameter                                                          | Conditions                                                           | Min  | Тур  | Max | Units |

|------------------|--------------------------------------------------------------------|----------------------------------------------------------------------|------|------|-----|-------|

| I <sub>OUT</sub> | DC output current <sup>(1)</sup>                                   | V <sub>VDDCORE</sub> > 1.65V                                         |      |      | 55  | mA    |

|                  | Output DC load regulation <sup>(1)</sup> Transient load regulation | $I_{OUT} = 0$ to 50 mA,<br>$V_{VDDIN} = 3 V$                         | -136 | -101 | -82 | mV    |

|                  | Output DC regulation <sup>(1)</sup>                                | $I_{OUT} = 50 \text{ mA},$ $V_{VDDIN} = 2 \text{V to } 3.6 \text{V}$ | -20  | 38   | 99  | mV    |

|                  | Quescient current <sup>(1)</sup>                                   | V <sub>VDDIN</sub> = 2V, I <sub>OUT</sub> = 0 mA                     | 97   | 186  | 546 |       |

| IQ               | Quescient current                                                  | $V_{VDDIN} > 2.2V$ , $I_{OUT} = 0$ mA                                | 97   | 111  | 147 | μΑ    |

| P <sub>EFF</sub> | Power efficiency <sup>(1)</sup>                                    | I <sub>OUT</sub> = 5mA, 50mA<br>Reference power not included         |      | 88.3 | 95  | %     |

<sup>1.</sup> These values are based on characterization. These values are not covered by test limits in production.

Table 9-40.

Decoupling Requirements in Switching Mode

| Symbol               | Parameter                              | Technology                    | Тур | Units |

|----------------------|----------------------------------------|-------------------------------|-----|-------|

| C <sub>IN1</sub>     | Input regulator capacitor 1            |                               | 33  | nF    |

| C <sub>IN2</sub>     | Input regulator capacitor 2            |                               | 100 | nr nr |

| C <sub>IN3</sub>     | Input regulator capacitor 3            |                               | 10  | μF    |

| C <sub>OUT1</sub>    | Output regulator capacitor 1           | X7R MLCC                      | 100 | nF    |

| C <sub>OUT2</sub>    | Output regulator capacitor 2           | X7R MLCC (ex : GRM31CR71A475) | 4.7 | μF    |

| L <sub>EXT</sub>     | External inductance                    | (ex: Murata LQH3NPN220MJ0)    | 22  | μH    |

| R <sub>DCLEXT</sub>  | Serial resistance of L <sub>EXT</sub>  |                               | 0.7 | Ω     |

| ISAT <sub>LEXT</sub> | Saturation current of L <sub>EXT</sub> |                               | 300 | mA    |

Note: 1. Refer to Section 6. on page 46.

Where  $\mathit{SPIn}$  is the MISO delay, SPI6 or SPI9 depending on CPOL and NCPHA.  $t_{\mathit{SETUP}}$  is the SPI master setup time. refer to the SPI master datasheet for  $t_{\mathit{SETUP}}$   $.f_{\mathit{PINMAX}}$  is the maximum frequency of the SPI pins. refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

## 9.10.4 TWIM/TWIS Timing

Figure 9-64 shows the TWI-bus timing requirements and the compliance of the device with them. Some of these requirements ( $t_r$  and  $t_f$ ) are met by the device without requiring user intervention. Compliance with the other requirements ( $t_{HD-STA}$ ,  $t_{SU-STA}$ ,  $t_{SU-STO}$ ,  $t_{HD-DAT}$ ,  $t_{SU-DAT-TWI}$ ,  $t_{LOW-TWI}$ ,  $t_{HIGH}$ , and  $t_{TWCK}$ ) requires user intervention through appropriate programming of the relevant TWIM and TWIS user interface registers. refer to the TWIM and TWIS sections for more information.

**Table 9-64.** TWI-Bus Timing Requirements

|                         |                                        |                         | Minin              | num                   | Maxi        |                                               |      |

|-------------------------|----------------------------------------|-------------------------|--------------------|-----------------------|-------------|-----------------------------------------------|------|

| Symbol                  | Parameter                              | Mode                    | Requirement        | Device                | Requirement | Device                                        | Unit |

|                         | TMOK and TMD via a time                | Standard <sup>(1)</sup> | -                  | I                     | 10          | 000                                           |      |

| t <sub>r</sub>          | TWCK and TWD rise time                 | Fast <sup>(1)</sup>     | 20 + 0             | .1C <sub>b</sub>      | 3           | 00                                            | ns   |

|                         | TMOK - a d TMD fell fire -             | Standard                | -                  |                       | 30          | 00                                            |      |

| t <sub>f</sub>          | TWCK and TWD fall time                 | Fast                    | 20 + 0             | .1C <sub>b</sub>      | 30          | 00                                            | ns   |

| 1                       | (Demosted) CTADT hold times            | Standard                | 4                  |                       |             |                                               |      |

| t <sub>HD-STA</sub>     | (Repeated) START hold time             | Fast                    | 0.6                | t <sub>clkpb</sub>    |             | -                                             | μs   |

|                         | (Danis and all) OTA DT and are discus- | Standard                | 4.7                | 4                     |             |                                               | _    |

| t <sub>SU-STA</sub>     | (Repeated) START set-up time           | Fast                    | 0.6                | t <sub>clkpb</sub>    | -           |                                               | μs   |

|                         | OTOD and are time.                     | Standard                | 4.0                | 44                    | -           |                                               | _    |

| t <sub>su-sto</sub>     | STOP set-up time                       | Fast                    | 0.6                | 4t <sub>clkpb</sub>   |             |                                               | μs   |

| 1                       | Data hald time                         | Standard                | 0.3 <sup>(2)</sup> | 24                    | 3.45()      | 454                                           |      |

| t <sub>HD-DAT</sub>     | Data hold time                         | Fast                    | 0.3(-/             | 2t <sub>clkpb</sub>   | 0.9()       | 15t <sub>prescaled</sub> + t <sub>clkpb</sub> | μs   |

| 1                       | Data act up time                       | Standard                | 250                | 24                    |             |                                               |      |

| t <sub>SU-DAT-TWI</sub> | Data set-up time                       | Fast                    | 100                | 2t <sub>clkpb</sub> - |             | -                                             | ns   |

| t <sub>SU-DAT</sub>     |                                        | -                       | -                  | t <sub>clkpb</sub>    |             | -                                             | -    |

| +                       | TWCK LOW period                        | Standard                | 4.7                | 4+                    |             |                                               |      |

| t <sub>LOW-TWI</sub>    | TWOK LOW period                        | Fast                    | 1.3                | - 4t <sub>clkpb</sub> |             | -                                             | μs   |

| t <sub>LOW</sub>        |                                        | -                       | -                  | t <sub>clkpb</sub>    | -           |                                               | -    |

| +                       | TWCK HIGH poriod                       | Standard                | 4.0                | 0+                    |             |                                               |      |

| t <sub>HIGH</sub>       | TWCK HIGH period                       | Fast                    | 0.6                | - 8t <sub>clkpb</sub> |             | -                                             | μs   |

| f                       | TWCK frequency                         | Standard                |                    | 1                     | 100         | 1                                             | kHz  |

| f <sub>TWCK</sub>       | I WON ITEQUENCY                        | Fast                    | -                  |                       | 400         | 12t <sub>clkpb</sub>                          | KIZ  |

Notes: 1. Standard mode:  $f_{TWCK} \le 100 \text{ kHz}$ ; fast mode:  $f_{TWCK} > 100 \text{ kHz}$ .

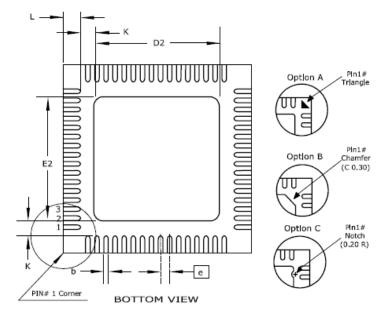

Figure 10-8. QFN-64 Package Drawing

SIDE VIEW

## COMMON DIMENSIONS

(Unit of Measure = mm)

| SYMBOL | MIN      | NOM  | MAX  | NOTE |

|--------|----------|------|------|------|

| Α      | 0,80     | 0,90 | 1,00 |      |

| A1     |          | 0.02 | 0.05 |      |

| А3     | 0.20 REF |      |      |      |

| D/E    | 8,90     | 9.00 | 9.10 |      |

| D2/E2  | 5.90     | 6.00 | 6.10 |      |

| L      | 0,30     | 0,40 | 0,50 |      |

| K      | -        | 1.10 | -    |      |

| b      | 0.18     | 0.25 | 0.30 | 2    |

| e      | 0.50 BSC |      |      |      |

| n      |          | 64   |      |      |

Note: The exposed pad is not connected to anything internally, but should be soldered to ground to increase board level reliability.

Table 10-23. Device and Package Maximum Weight

| 200 mg |

|--------|

|--------|

## Table 10-24. Package Characteristics

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

|----------------------------|------|

## Table 10-25. Package Reference

| JEDEC Drawing Reference | MO-220 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

| 8  | Debug    | and Test                              | 62  |

|----|----------|---------------------------------------|-----|

|    | 8.1      | Features                              | 62  |

|    | 8.2      | Overview                              | 62  |

|    | 8.3      | Block diagram                         | 63  |

|    | 8.4      | I/O Lines Description                 | 63  |

|    | 8.5      | Product dependencies                  | 64  |

|    | 8.6      | Core debug                            | 64  |

|    | 8.7      | Enhanced Debug Port (EDP)             | 67  |

|    | 8.8      | AHB-AP Access Port                    | 77  |

|    | 8.9      | System Manager Access Port (SMAP)     | 78  |

|    | 8.10     | Available Features in Protected State | 93  |

|    | 8.11     | Functional Description                | 94  |

| 9  | Electric | cal Characteristics                   | 99  |

|    | 9.1      | Absolute Maximum Ratings*             | 99  |

|    | 9.2      | Operating Conditions                  | 99  |

|    | 9.3      | Supply Characteristics                | 99  |

|    | 9.4      | Maximum Clock Frequencies             | 101 |

|    | 9.5      | Power Consumption                     | 103 |

|    | 9.6      | I/O Pin Characteristics               | 114 |

|    | 9.7      | Oscillator Characteristics            | 121 |

|    | 9.8      | Flash Characteristics                 | 127 |

|    | 9.9      | Analog Characteristics                | 129 |

|    | 9.10     | Timing Characteristics                | 140 |

| 10 | Mecha    | nical Characteristics                 | 153 |

|    | 10.1     | Thermal Considerations                | 153 |

|    | 10.2     | Package Drawings                      | 154 |

|    | 10.3     | Soldering Profile                     | 165 |

| 11 | Orderii  | ng Information                        | 166 |

| 12 | Errata   |                                       | 169 |

|    | 12.1     | ATSAM4L4 /2 Rev. B & ATSAM4L8 Rev. A  |     |

| 13 | Datash   | neet Revision History                 | 172 |

| -  | 13.1     | Rev. A – 09/12                        |     |

|    | 13.2     | Rev. B – 10/12                        |     |

|    | 13.3     | Rev. C – 02/13                        |     |