Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 48                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.68V ~ 3.6V                                                             |

| Data Converters            | A/D 7x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-TQFP                                                                  |

| Supplier Device Package    | 64-TQFP (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4ls8ba-au |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Atmel

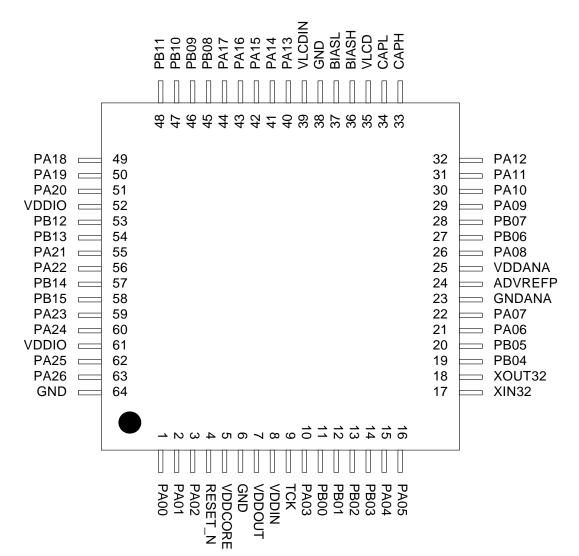

Figure 3-4. ATSAM4LC TQFP64/QFN64 Pinout

12

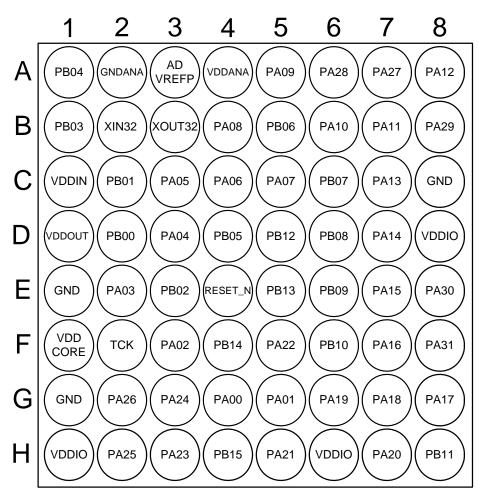

Figure 3-8. ATSA

B. ATSAM4LS WLCSP64 Pinout

- Atmel

| Table 3-2. 64-pir | GPIO Controller Function Multiplexing (She | et 2 of 3) |

|-------------------|--------------------------------------------|------------|

|-------------------|--------------------------------------------|------------|

|          |          | P.   |      |        |               |                 |                  |                 |                   |                |                 |

|----------|----------|------|------|--------|---------------|-----------------|------------------|-----------------|-------------------|----------------|-----------------|

| ATSAM4LC | ATSAM4LS | Pin  | GPIO | Supply |               |                 | G                | PIO Functio     | ns                |                |                 |

| QFP      | QFP      | _    | 0    | ้ร     |               |                 |                  |                 |                   |                |                 |

| QFN      | QFN      |      |      |        | Α             | в               | с                | D               | Е                 | F              | G               |

| 15       | 15       | PA04 | 4    | VDDANA | ADCIFE<br>AD0 | USART0<br>CLK   | EIC<br>EXTINT2   | GLOC<br>IN1     |                   |                | CATB<br>SENSE0  |

| 16       | 16       | PA05 | 5    | VDDANA | ADCIFE<br>AD1 | USART0<br>RXD   | EIC<br>EXTINT3   | GLOC<br>IN2     | ADCIFE<br>TRIGGER |                | CATB<br>SENSE1  |

| 21       | 21       | PA06 | 6    | VDDANA | DACC<br>VOUT  | USART0<br>RTS   | EIC<br>EXTINT1   | GLOC<br>IN0     | ACIFC<br>ACAN0    |                | CATB<br>SENSE2  |

| 22       | 22       | PA07 | 7    | VDDANA | ADCIFE<br>AD2 | USART0<br>TXD   | EIC<br>EXTINT4   | GLOC<br>IN3     | ACIFC<br>ACAP0    |                | CATB<br>SENSE3  |

| 26       | 26       | PA08 | 8    | LCDA   | USART0<br>RTS | ТС0<br>А0       | PEVC<br>PAD EVT0 | GLOC<br>OUT0    |                   | LCDCA<br>SEG23 | CATB<br>SENSE4  |

| 29       | 29       | PA09 | 9    | LCDA   | USART0<br>CTS | ТС0<br>В0       | PEVC<br>PAD EVT1 | PARC<br>PCDATA0 |                   | LCDCA<br>COM3  | CATB<br>SENSE5  |

| 30       | 30       | PA10 | 10   | LCDA   | USART0<br>CLK | TC0<br>A1       | PEVC<br>PAD EVT2 | PARC<br>PCDATA1 |                   | LCDCA<br>COM2  | CATB<br>SENSE6  |

| 31       | 31       | PA11 | 11   | LCDA   | USART0<br>RXD | TC0<br>B1       | PEVC<br>PAD EVT3 | PARC<br>PCDATA2 |                   | LCDCA<br>COM1  | CATB<br>SENSE7  |

| 32       | 32       | PA12 | 12   | LCDA   | USART0<br>TXD | TC0<br>A2       |                  | PARC<br>PCDATA3 |                   | LCDCA<br>COM0  | CATB<br>DIS     |

| 40       | 40       | PA13 | 13   | LCDA   | USART1<br>RTS | TC0<br>B2       | SPI<br>NPCS1     | PARC<br>PCDATA4 |                   | LCDCA<br>SEG5  | CATB<br>SENSE8  |

| 41       | 41       | PA14 | 14   | LCDA   | USART1<br>CLK | TC0<br>CLK0     | SPI<br>NPCS2     | PARC<br>PCDATA5 |                   | LCDCA<br>SEG6  | CATB<br>SENSE9  |

| 42       | 42       | PA15 | 15   | LCDA   | USART1<br>RXD | TC0<br>CLK1     | SPI<br>NPCS3     | PARC<br>PCDATA6 |                   | LCDCA<br>SEG7  | CATB<br>SENSE10 |

| 43       | 43       | PA16 | 16   | LCDA   | USART1<br>TXD | TC0<br>CLK2     | EIC<br>EXTINT1   | PARC<br>PCDATA7 |                   | LCDCA<br>SEG8  | CATB<br>SENSE11 |

| 44       | 44       | PA17 | 17   | LCDA   | USART2<br>RTS | ABDACB<br>DAC0  | EIC<br>EXTINT2   | PARC<br>PCCK    |                   | LCDCA<br>SEG9  | CATB<br>SENSE12 |

| 49       | 49       | PA18 | 18   | LCDA   | USART2<br>CLK | ABDACB<br>DACN0 | EIC<br>EXTINT3   | PARC<br>PCEN1   |                   | LCDCA<br>SEG18 | CATB<br>SENSE13 |

| 50       | 50       | PA19 | 19   | LCDA   | USART2<br>RXD | ABDACB<br>DAC1  | EIC<br>EXTINT4   | PARC<br>PCEN2   | SCIF<br>GCLK0     | LCDCA<br>SEG19 | CATB<br>SENSE14 |

| 51       | 51       | PA20 | 20   | LCDA   | USART2<br>TXD | ABDACB<br>DACN1 | EIC<br>EXTINT5   | GLOC<br>IN0     | SCIF<br>GCLK1     | LCDCA<br>SEG20 | CATB<br>SENSE15 |

| 55       | 55       | PA21 | 21   | LCDC   | SPI<br>MISO   | USART1<br>CTS   | EIC<br>EXTINT6   | GLOC<br>IN1     | TWIM2<br>TWD      | LCDCA<br>SEG34 | CATB<br>SENSE16 |

| 56       | 56       | PA22 | 22   | LCDC   | SPI<br>MOSI   | USART2<br>CTS   | EIC<br>EXTINT7   | GLOC<br>IN2     | TWIM2<br>TWCK     | LCDCA<br>SEG35 | CATB<br>SENSE17 |

| 59       | 59       | PA23 | 23   | LCDC   | SPI<br>SCK    | TWIMS0<br>TWD   | EIC<br>EXTINT8   | GLOC<br>IN3     | SCIF<br>GCLK IN0  | LCDCA<br>SEG38 | CATB<br>DIS     |

| 60       | 60       | PA24 | 24   | LCDC   | SPI<br>NPCS0  | TWIMS0<br>TWCK  |                  | GLOC<br>OUT0    | SCIF<br>GCLK IN1  | LCDCA<br>SEG39 | CATB<br>SENSE18 |

| 62       | 62       | PA25 | 25   | VDDIO  | USBC<br>DM    | USART2<br>RXD   |                  |                 |                   |                | CATB<br>SENSE19 |

| 63       | 63       | PA26 | 26   | VDDIO  | USBC<br>DP    | USART2<br>TXD   |                  |                 |                   |                | CATB<br>SENSE20 |

| Table 4-2.         Interrupt Request Signal Map (Sheet 3 of 3) |                                                            |        |  |  |  |  |

|----------------------------------------------------------------|------------------------------------------------------------|--------|--|--|--|--|

| Line                                                           | Module                                                     | Signal |  |  |  |  |

| 48                                                             | External Interrupt Controller                              | EIC 4  |  |  |  |  |

| 49                                                             | External Interrupt Controller                              | EIC 5  |  |  |  |  |

| 50                                                             | External Interrupt Controller                              | EIC 6  |  |  |  |  |

| 51                                                             | External Interrupt Controller                              | EIC 7  |  |  |  |  |

| 52                                                             | External Interrupt Controller                              | EIC 8  |  |  |  |  |

| 53                                                             | Inter-IC Sound (I2S) Controller                            | IISC   |  |  |  |  |

| 54                                                             | Serial Peripheral Interface                                | SPI    |  |  |  |  |

| 55                                                             | Timer/Counter                                              | TC00   |  |  |  |  |

| 56                                                             | Timer/Counter                                              | TC01   |  |  |  |  |

| 57                                                             | Timer/Counter                                              | TC02   |  |  |  |  |

| 58                                                             | Timer/Counter                                              | TC10   |  |  |  |  |

| 59                                                             | Timer/Counter                                              | TC11   |  |  |  |  |

| 60                                                             | Timer/Counter                                              | TC12   |  |  |  |  |

| 61                                                             | Two-wire Master Interface                                  | TWIMO  |  |  |  |  |

| 62                                                             | Two-wire Slave Interface                                   | TWIS0  |  |  |  |  |

| 63                                                             | Two-wire Master Interface                                  | TWIM1  |  |  |  |  |

| 64                                                             | Two-wire Slave Interface                                   | TWIS1  |  |  |  |  |

| 65                                                             | Universal Synchronous Asynchronous<br>Receiver Transmitter | USART0 |  |  |  |  |

| 66                                                             | Universal Synchronous Asynchronous<br>Receiver Transmitter | USART1 |  |  |  |  |

| 67                                                             | Universal Synchronous Asynchronous<br>Receiver Transmitter | USART2 |  |  |  |  |

| 68                                                             | Universal Synchronous Asynchronous<br>Receiver Transmitter | USART3 |  |  |  |  |

| 69                                                             | ADC controller interface                                   | ADCIFE |  |  |  |  |

| 70                                                             | DAC Controller                                             | DACC   |  |  |  |  |

| 71                                                             | Analog Comparator Interface                                | ACIFC  |  |  |  |  |

| 72                                                             | Audio Bitstream DAC                                        | ABDACB |  |  |  |  |

| 73                                                             | True Random Number Generator                               | TRNG   |  |  |  |  |

| 74                                                             | Parallel Capture                                           | PARC   |  |  |  |  |

| 75                                                             | Capacitive Touch Module B                                  | CATB   |  |  |  |  |

| 77                                                             | Two-wire Master Interface                                  | TWIM2  |  |  |  |  |

| 78                                                             | Two-wire Master Interface                                  | TWIM3  |  |  |  |  |

| 79                                                             | LCD Controller A                                           | LCDCA  |  |  |  |  |

Table 4-2.

Interrupt Request Signal Map (Sheet 3 of 3)

# 6.2 Power Supplies

The ATSAM4L8/L4/L2 has several types of power supply pins:

- VDDIO: Powers I/O lines, the general purpose oscillator (OSC), the 80MHz integrated RC oscillator (RC80M). Voltage is 1.68V to 3.6V.

- VLCDIN: (ATSAM4LC only) Powers the LCD voltage pump. Voltage is 1.68V to 3.6V.

- VDDIN: Powers the internal voltage regulator. Voltage is 1.68V to 3.6V.

- VDDANA: Powers the ADC, the DAC, the Analog Comparators, the 32kHz oscillator (OSC32K), the 32kHz integrated RC oscillator (RC32K) and the Brown-out detectors (BOD18 and BOD33). Voltage is 1.68V to 3.6V nominal.

- VDDCORE: Powers the core, memories, peripherals, the PLL, the DFLL, the 4MHz integrated RC oscillator (RCFAST) and the 115kHz integrated RC oscillator (RCSYS).

- VDDOUT is the output voltage of the regulator and must be connected with or without an inductor to VDDCORE.

The ground pins GND are common to VDDCORE, VDDIO, and VDDIN. The ground pin for VDDANA is GNDANA.

For decoupling recommendations for the different power supplies, refer to the schematic document.

#### 6.2.1 Voltage Regulator

An embedded voltage regulator supplies all the digital logic in the Core and the Backup power domains.

The regulator has two functionnal mode depending of BUCK/LDOn (PA02) pin value. When this pin is low, the regulator is in linear mode and VDDOUT must be connected to VDDCORE externally. When this pin is high, it behaves as a switching regulator and an inductor must be placed between VDDOUT and VDDCORE. The value of this pin is sampled during the power-up phase when the Power On Reset 33 reaches  $V_{POT+}$  (Section 9.9 "Analog Characteristics" on page 129)

Its output voltages in the Core domain ( $V_{CORE}$ ) and in the Backup domain ( $V_{BKUP}$ ) are always equal except in Backup mode where the Core domain is not powered ( $V_{CORE}$ =0). The Backup domain is always powered. The voltage regulator features three different modes:

- Normal mode: the regulator is configured as linear or switching regulator. It can support all different Run and Sleep modes.

- Low Power (LP) mode: the regulator consumes little static current. It can be used in Wait modes.

- Ultra Low Power (ULP) mode: the regulator consumes very little static current. It is dedicated to Retention and Backup modes. In Backup mode, the regulator only supplies the backup domain.

Atmel

At power-up or after a reset, the ATSAM4L8/L4/L2 is in the RUN0 mode. Only the necessary clocks are enabled allowing software execution. The Power Manager (PM) can be used to adjust the clock frequencies and to enable and disable the peripheral clocks.

When the CPU is entering a Power Save Mode, the CPU stops executing code. The user can choose between four Power Save Modes to optimize power consumption:

- SLEEP mode: the Cortex-M4 core is stopped, optionally some clocks are stopped, peripherals are kept running if enabled by the user.

- WAIT mode: all clock sources are stopped, the core and all the peripherals are stopped except the modules running with the 32kHz clock if enabled. This is the lowest power configuration where SleepWalking is supported.

- RETENTION mode: similar to the WAIT mode in terms of clock activity. This is the lowest power configuration where the logic is retained.

- BACKUP mode: the Core domain is powered off, the Backup domain is kept powered.

A wake up source exits the system to the RUN mode from which the Power Save Mode was entered.

A reset source always exits the system from the Power Save Mode to the RUN0 mode.

The configuration of the I/O lines are maintained in all Power Save Modes. Refer to Section 9. "Backup Power Manager (BPM)" on page 677.

#### 7.1.1 SLEEP mode

The SLEEP mode allows power optimization with the fastest wake up time.

The CPU is stopped. To further reduce power consumption, the user can switch off modulesclocks and synchronous clock sources through the BPM.PMCON.SLEEP field (See Table 7-1). The required modules will be halted regardless of the bit settings of the mask registers in the Power Manager (PM.AHBMASK, PM.APBxMASK).

| BPM.PSAVE.SLEEP | CPU<br>clock | AHB<br>clocks | APB clocks<br>GCLK | Clock sources:<br>OSC, RCFAST,<br>RC80M, PLL,<br>DFLL | RCSYS | OSC32K<br>RC32K <sup>(2)</sup> | Wake up Sources              |

|-----------------|--------------|---------------|--------------------|-------------------------------------------------------|-------|--------------------------------|------------------------------|

| 0               | Stop         | Run           | Run                | Run                                                   | Run   | Run                            | Any interrupt                |

| 1               | Stop         | Stop          | Run                | Run                                                   | Run   | Run                            | Any interrupt <sup>(1)</sup> |

| 2               | Stop         | Stop          | Stop               | Run                                                   | Run   | Run                            | Any interrupt <sup>(1)</sup> |

| 3               | Stop         | Stop          | Stop               | Stop                                                  | Run   | Run                            | Any interrupt <sup>(1)</sup> |

Table 7-1.

SLEEP mode Configuration

Notes: 1. from modules with clock running.

2. OSC32K and RC32K will only remain operational if pre-enabled.

#### 7.1.1.1 Entering SLEEP mode

The SLEEP mode is entered by executing the WFI instruction.

Atmel

Additionally, if the SLEEPONEXIT bit in the Cortex-M4 System Control Register (SCR) is set, the SLEEP mode will also be entered when the Cortex-M4 exits the lowest priority ISR. This

#### 7.1.5 Power Save Mode Summary Table

The following table shows a summary of the main Power Save modes:

Table 7-2.

Power Save mode Configuration Summary

| Mode      | Mode Entry                                                                      | Wake up sources                                                                                                                                         | Core<br>domain                                                                                                   | Backup<br>domain                                                                          |

|-----------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| SLEEP     | WFI<br>SCR.SLEEPDEEP bit = 0<br>BPM.PMCON.BKUP bit = 0                          | Any interrupt                                                                                                                                           | CPU clock OFF<br>Other clocks OFF depending<br>on the BPM.PMCON.SLEEP<br>field<br>see "SLEEP mode" on page<br>56 | Clocks OFF depending on<br>the BPM.PMCON.SLEEP<br>field<br>see "SLEEP mode" on page<br>56 |

| WAIT      | WFI<br>SCR.SLEEPDEEP bit = 1<br>BPM.PMCON.RET bit = 0<br>BPM.PMCON.BKUP bit = 0 | PM WAKE interrupt                                                                                                                                       | All clocks are OFF<br>Core domain is retained                                                                    | All clocks are OFF except<br>RC32K or OSC32K if<br>running                                |

| RETENTION | WFI<br>SCR.SLEEPDEEP bit = 1<br>BPM.PMCON.RET bit = 1<br>BPM.PMCON.BKUP bit = 0 | PM WAKE interrupt                                                                                                                                       | All clocks are OFF<br>Core domain is retained                                                                    | All clocks are OFF except<br>RC32K or OSC32K if<br>running                                |

| BACKUP    | WFI<br>+ SCR.SLEEPDEEP bit = 1<br>+ BPM.PMCON.BKUP bit = 1                      | EIC interrupt<br>BOD33, BOD18 interrupt<br>and reset<br>AST alarm, periodic,<br>overflow<br>WDT interrupt and reset<br>external reset on RESET_N<br>pin | OFF (not powered)                                                                                                | All clocks are OFF except<br>RC32K or OSC32K if<br>running                                |

# 7.2 Power Scaling

The Power Scaling technique consists of adjusting the internal regulator output voltage (voltage scaling) to reduce the power consumption. According to the requirements in terms of performance, operating modes, and current consumption, the user can select the Power Scaling configuration that fits the best with its application.

The Power Scaling configuration field (PMCON.PS) is provided in the Backup Power Manager (BPM) module.

In RUN mode, the user can adjust on the fly the Power Scaling configuration

The Figure 7.1 summarizes the different combination of the Power Scaling configuration which can be applied according to the Power Save Mode.

Power scaling from a current power configuration to a new power configuration is done by halting the CPU execution

Power scaling occurs after a WFI instruction. The system is halted until the new power configuration is stabilized. After handling the PM interrupt, the system resumes from WFI.

To scale the power, the following sequence is required:

• Check the BPM.SR.PSOK bit to make sure the current power configuration is stabilized.

The FPB unit contains:

- Two literal comparators for matching against literal loads from Code space, and remapping to a corresponding area in System space.

- Six instruction comparators for matching against instruction fetches from Code space and remapping to a corresponding area in System space.

- Alternatively, comparators can also be configured to generate a Breakpoint instruction to the processor core on a match.

#### 8.6.2 DWT (Data Watchpoint and Trace)

The DWT contains four comparators which can be configured to generate the following:

- · PC sampling packets at set intervals

- PC or Data watchpoint packets

- Watchpoint event to halt core

The DWT contains counters for the items that follow:

- Clock cycle (CYCCNT)

- Folded instructions

- Load Store Unit (LSU) operations

- Sleep Cycles

- CPI (all instruction cycles except for the first cycle)

- Interrupt overhead

#### 8.6.3 ITM (Instrumentation Trace Macrocell)

The ITM is an application driven trace source that supports printf style debugging to trace Operating System (OS) and application events, and emits diagnostic system information. The ITM emits trace information as packets which can be generated by three different sources with several priority levels:

- **Software trace**: This can be done thanks to the printf style debugging. For more information, refer to Section "How to Configure the ITM:".

- Hardware trace: The ITM emits packets generated by the DWT.

- **Time stamping**: Timestamps are emitted relative to packets. The ITM contains a 21-bit counter to generate the timestamp.

#### How to Configure the ITM:

The following example describes how to output trace data in asynchronous trace mode.

- Configure the TPIU for asynchronous trace mode (refer to Section "5.4.3. How to Configure the TPIU")

- Enable the write accesses into the ITM registers by writing "0xC5ACCE55" into the Lock Access Register (Address: 0xE0000FB0)

- Write 0x00010015 into the Trace Control Register:

- Enable ITM

- Enable Synchronization packets

- Enable SWO behavior

#### 8.7.5 Product Dependencies

#### 8.7.5.1 I/O Lines

The TCK pin is dedicated to the EDP. The other debug port pins default after reset to their GPIO functionality and are automatically reassigned to the JTAG functionalities on detection of a debugger. In serial wire mode, TDI and TDO can be used as GPIO functions. Note that in serial wire mode TDO can be used as a single pin trace output.

#### 8.7.5.2 Power Management

When a debugger is present, the connection is kept alive allowing debug operations. As a side effect, the power is never turned off. The hot plugging functionality is always available except when the system is in BACKUP Power Save Mode.

#### 8.7.5.3 Clocks

The SWJ-DP uses the external TCK pin as its clock source. This clock must be provided by the external JTAG master device.

Some of the JTAG Instructions are used to access an Access Port (SMAP or AHB-AP). These instructions require the CPU clock to be running.

If the CPU clock is not present because the CPU is in a Power Save Mode where this clock is not provided, the Power Manager(PM) will automatically restore the CPU clock on detection of a debug access.

The RCSYS clock is used as CPU clock when the external reset is applied to ensure correct Access Port operations.

#### 8.7.6 Module Initialization

This module is enabled as soon as a TCK falling edge is detected when RESET\_N is not asserted (refer to Section 8.7.7 below). Moreover, the module is synchronously reseted as long as the TAP machine is in the TEST\_LOGIC\_RESET (TLR) state. It is advised asserting TMS at least 5 TCK clock periods after the debugger has been detected to ensure the module is in the TLR state prior to any operation. This module also has the ability to maintain the Cortex-M4 under reset (refer to the Section 8.7.8 "SMAP Core Reset Request Source" on page 70).

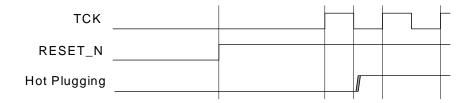

#### 8.7.7 Debugger Hot Plugging

The TCK pin is dedicated to the EDP. After reset has been released, the EDP detects that a debugger has been attached when a TCK falling edge arises.

Figure 8-4. Debugger Hot Plugging Detection Timings Diagram

Atmel

#### 8.7.10 SW-DP and JTAG-DP Selection Mechanism

After reset, the SWJ-DP is in JTAG mode but it can be switched to the Serial Wire mode. Debug port selection mechanism is done by sending specific **SWDIOTMS** sequence. The JTAG-DP is selected by default after reset.

- Switch from JTAG-DP to SW-DP. The sequence is:

- Send more than 50 **SWCLKTCK** cycles with **SWDIOTMS** = 1

- Send the 16-bit sequence on SWDIOTMS = 0111100111100111 (0x79E7 MSB first)

- Send more than 50 SWCLKTCK cycles with SWDIOTMS = 1

- Switch from SWD to JTAG. The sequence is:

- Send more than 50 SWCLKTCK cycles with SWDIOTMS = 1

- Send the 16-bit sequence on **SWDIOTMS** = 0011110011100111 (0x3CE7 MSB first)

Send more than 50 SWCLKTCK cycles with SWDIOTMS = 1

Atmel

Note that the BSCAN-TAP is not available when the debug port is switched to Serial Mode. Boundary scan instructions are not available.

# 8.7.11 JTAG-DP and BSCAN-TAP Selection Mechanism

After the DP has been enabled, the BSCAN-TAP and the JTAG-DP run simultaneously has long as the SWJ-DP remains in JTAG mode. Each TAP captures simultaneously the JTAG instructions that are shifted. If an instruction is recognized by the BSCAN-TAP, then the BSCAN-TAP TDO is selected instead of the SWJ-DP TDO. TDO selection changes dynamically depending on the current instruction held in the BSCAN-TAP instruction register.

### 8.7.14.4 CLAMP

This instruction selects the Bypass register as Data Register. The device output pins are driven from the boundary-scan chain.

Starting in Run-Test/Idle, the CLAMP instruction is accessed the following way:

- 1. Select the IR Scan path.

- 2. In Capture-IR: The IR output value is latched into the shift register.

- 3. In Shift-IR: The instruction register is shifted by the TCK input.

- 4. In Update-IR: The data from the boundary-scan chain is applied to the output pins.

- 5. Return to Run-Test/Idle.

- 6. Select the DR Scan path.

- 7. In Capture-DR: A logic '0' is loaded into the Bypass Register.

Atmel

- 8. In Shift-DR: Data is scanned from TDI to TDO through the Bypass register.

- 9. Return to Run-Test/Idle.

#### Table 8-8. CLAMP Details

| Instructions    | Details           |

|-----------------|-------------------|

| IR input value  | <b>0101</b> (0x5) |

| IR output value | p00s              |

| DR Size         | 1                 |

| DR input value  | x                 |

| DR output value | x                 |

| 8.9.11.6 Data F<br>Name: | Register<br>DATA |    |      |    |    |    |

|--------------------------|------------------|----|------|----|----|----|

| Access Type:             | Read/Write       |    |      |    |    |    |

| Offset:                  | 0x14             |    |      |    |    |    |

| Reset Value:             | 0x00000000       |    |      |    |    |    |

|                          |                  |    |      |    |    |    |

| 31                       | 30               | 29 | 28   | 27 | 26 | 25 |

|                          |                  |    | DATA |    |    |    |

|                          |                  |    |      |    |    |    |

| 23                       | 22               | 21 | 20   | 19 | 18 | 17 |

|                          |                  |    | DATA |    |    |    |

|                          |                  |    |      |    |    |    |

| 15                       | 14               | 13 | 12   | 11 | 10 | 9  |

|                          |                  |    | DATA |    |    |    |

|                          |                  |    |      |    |    |    |

| 7                        | 6                | 5  | 4    | 3  | 2  | 1  |

|                          |                  |    | DATA |    |    |    |

• DATA: Generic data register

#### 8.11.8 Chip erase typical procedure

The chip erase operation is triggered by writing a one in the CE bit in the Control Register (CR.CE). This clears first all volatile memories in the system and second the whole flash array. Note that the User page is not erased in this process. To ensure that the chip erase operation is completed, check the DONE bit in the Status Register (SR.DONE). Also note that the chip erase operation depends on clocks and power management features that can be altered by the CPU. It is important to ensure that it is stopped. The recommended sequence is shown below:

- 1. At power up, RESET\_N is driven low by a debugger. The on-chip regulator holds the system in a POR state until the input supply is above the POR threshold. The system continues to be held in this static state until the internally regulated supplies have reached a safe operating.

- PM starts, clocks are switched to the slow clock (Core Clock, System Clock, Flash Clock, and any Bus Clocks that do not have clock gate control). Internal resets are maintained due to the external reset.

- The debug port and access ports receives a clock and leave the reset state

- 3. The debugger maintains a low level on TCK and release RESET\_N.

- The SMAP asserts the core\_hold\_reset signal

- 4. The Cortex-M4 core remains in reset state, meanwhile the rest of the system is released.

- 5. The Chip erase operation can be performed by issuing the SMAP Chip Erase command. In this case:

- volatile memories are cleared first

- followed by the clearing of the flash array

- followed by the clearing of the protected state

Atmel

After operation is completed, the chip must be restarted by either controling RESET\_N or switching power off/on. Make sure that the TCK pin is high when releasing RESET\_N not to halt the core.

## 8.11.9 Setting the protected state

This is done by issuing a specific flash controller command, for more information, refer to the Flash Controller chapter and to section 8.11.7Flash Programming typical procedure97. The protected state is defined by a highly secure Flash builtin mechanism. Note that for this programmation to propagate, it is required to reset the chip.

| Symbol                | Parameter                                | Conditions |                                                    | Min                             | Тур | Мах                    | Units |

|-----------------------|------------------------------------------|------------|----------------------------------------------------|---------------------------------|-----|------------------------|-------|

| R <sub>PULLUP</sub>   | Pull-up resistance (2)                   |            |                                                    |                                 | 40  |                        | kΩ    |

| R <sub>PULLDOWN</sub> | Pull-up resistance <sup>(2)</sup>        |            |                                                    |                                 | 40  |                        | kΩ    |

| V <sub>IL</sub>       | Input low-level voltage                  |            |                                                    | -0.3                            |     | 0.2 * V <sub>VDD</sub> |       |

| V <sub>IH</sub>       | Input high-level voltage                 |            |                                                    | 0.8 * V <sub>VDD</sub>          |     | V <sub>VDD</sub> + 0.3 | V     |

| V <sub>OL</sub>       | Output low-level voltage                 |            |                                                    |                                 |     | 0.4                    | V     |

| V <sub>OH</sub>       | Output high-level voltage                |            |                                                    | V <sub>VDD</sub> - 0.4          |     |                        |       |

|                       |                                          | ODCR0=0    | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                                 |     | 3.4                    | ~ ^   |

|                       | Output low lovel surrent (3)             | ODCR0=0    | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                                 |     | 6                      | mA    |

| I <sub>OL</sub>       | Output low-level current <sup>(3)</sup>  | ODCR0=1    | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                                 |     | 5.2                    | ~^^   |

|                       |                                          |            | ODCR0=1                                            | 2.7V <v<sub>VDD&lt;3.6V</v<sub> |     |                        | 8     |

| I <sub>ОН</sub>       | Output high-level current <sup>(3)</sup> | ODCR0=0    | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                                 |     | 3.4                    | mA    |

|                       |                                          |            | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                                 |     | 6                      |       |

|                       |                                          | ODCR0=1    | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                                 |     | 5.2                    | mA    |

|                       |                                          | ODCR0=1    | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                                 |     | 8                      | ШA    |

|                       |                                          | OSRR0=0    | ODCR0=0                                            |                                 | 18  |                        |       |

|                       | (2)                                      | OSRR0=1    | 1.68V <v<sub>VDD&lt;2.7V,<br/>Cload = 25pF</v<sub> |                                 | 110 |                        | ns    |

| t <sub>RISE</sub>     | Rise time <sup>(2)</sup>                 | OSRR0=0    | ODCR0=0                                            |                                 | 10  |                        |       |

|                       |                                          | OSRR0=1    | 2.7V <v<sub>VDD&lt;3.6V,<br/>Cload = 25pF</v<sub>  |                                 | 50  |                        | ns    |

|                       |                                          | OSRR0=0    | ODCR0=0                                            |                                 | 19  |                        |       |

|                       | Fall time <sup>(2)</sup>                 | OSRR0=1    | 1.68V <v<sub>VDD&lt;2.7V,<br/>Cload = 25pF</v<sub> |                                 | 140 |                        | ns    |

| t <sub>FALL</sub>     |                                          | OSRR0=0    | ODCR0=0                                            |                                 | 12  |                        |       |

|                       |                                          | OSRR0=1    | 2.7V <v<sub>VDD&lt;3.6V,<br/>Cload = 25pF</v<sub>  |                                 | 63  |                        | ns    |

# Table 9-20. High Drive TWI Pin Characteristics in GPIO configuration <sup>(1)</sup>

1.  $V_{VDD}$  corresponds to either  $V_{VDDIN}$  or  $V_{VDDIO}$ , depending on the supply for the pin. Refer to Section 3-5 on page 13 for details

2. These values are based on simulation. These values are not covered by test limits in production or characterization

3. These values are based on characterization. These values are not covered by test limits in production

| Table 9-21. | Common High Drive TWI Pin Characteristics |

|-------------|-------------------------------------------|

|-------------|-------------------------------------------|

| Symbol            | Parameter                        | Conditions                 | Min | Тур  | Max | Units |

|-------------------|----------------------------------|----------------------------|-----|------|-----|-------|

| I <sub>LEAK</sub> | Input leakage current (1)        | Pull-up resistors disabled |     | 0.01 | 2   | μA    |

| C <sub>IN</sub>   | Input capacitance <sup>(1)</sup> |                            |     | 10   |     | pF    |

1. These values are based on simulation. These values are not covered by test limits in production or characterization

- Atmel

# 9.7.2 32kHz Crystal Oscillator (OSC32K) Characteristics

Figure 9-3 and the equation above also applies to the 32kHz oscillator connection. The user must choose a crystal oscillator where the crystal load capacitance  $C_L$  is within the range given in the table. The exact value of  $C_L$  can then be found in the crystal datasheet.

Table 9-24.

Digital Clock Characteristics

| Symbol               | Parameter                             | Conditions | Min | Тур | Max | Units  |

|----------------------|---------------------------------------|------------|-----|-----|-----|--------|

| f <sub>CPXIN32</sub> | XIN32 clock frequency <sup>(1)</sup>  |            |     |     | 6   | MHz    |

|                      | XIN32 clock duty cycle <sup>(1)</sup> |            | 40  |     | 60  | %      |

| t <sub>STARTUP</sub> | Startup time                          |            |     | N/A |     | cycles |

1. These values are based on simulation. These values are not covered by test limits in production or characterization.

Table 9-25. 32 kHz Crystal Oscillator Characteristics

| Symbol               | Parameter                                                                                 | Conditions                                   |                        | Min | Тур                  | Мах   | Unit   |

|----------------------|-------------------------------------------------------------------------------------------|----------------------------------------------|------------------------|-----|----------------------|-------|--------|

| f <sub>OUT</sub>     | Crystal oscillator frequency                                                              |                                              |                        |     | 32 768               |       | Hz     |

| t <sub>STARTUP</sub> | Startup time (1)                                                                          | $R_{\rm m}$ = 100kΩ, C <sub>L</sub> = 12.5pF |                        |     | 30000 <sup>(2)</sup> |       | cycles |

| CL                   | Crystal load capacitance <sup>(1)</sup>                                                   |                                              |                        | 6   |                      | 12.5  |        |

| C <sub>SHUNT</sub>   | Crystal shunt capacitance <sup>(1)</sup>                                                  |                                              |                        | 0.8 |                      | 1.7   |        |

| C <sub>XIN</sub>     | Parasitic capacitor load (3)                                                              | TQFP100 package                              |                        |     | 3.4                  |       | pF     |

| C <sub>XOUT</sub>    | Parasitic capacitor load <sup>(3)</sup>                                                   |                                              |                        |     | 2.72                 |       |        |

| I <sub>OSC32K</sub>  | Current consumption <sup>(1)</sup>                                                        |                                              |                        |     | 350                  |       | nA     |

| re<br>f=<br>O        | Crystal equivalent series<br>resistance <sup>(1)</sup><br>f=32.768kHz<br>OSCCTRL32.MODE=1 | OSCCTRL32.SELCURR=0                          |                        |     |                      | 28    | kΩ     |

|                      |                                                                                           | OSCCTRL32.SELCURR=4                          | 0.0-5                  |     |                      | 72    |        |

|                      |                                                                                           | OSCCTRL32.SELCURR=8                          | C <sub>L</sub> =6pF    |     |                      | 114   |        |

|                      |                                                                                           | OSCCTRL32.SELCURR=15                         |                        |     |                      | 313   |        |

|                      |                                                                                           | OSCCTRL32.SELCURR=0                          |                        |     |                      | 14    | - kΩ   |

|                      | Safety Factor = 3                                                                         | OSCCTRL32.SELCURR=4                          | 0.0-5                  |     |                      | 36    |        |

| ESR <sub>XTAL</sub>  |                                                                                           | OSCCTRL32.SELCURR=8                          | C <sub>L</sub> =9pF    |     |                      | 100   |        |

|                      |                                                                                           | OSCCTRL32.SELCURR=15                         |                        |     |                      | 170   |        |

|                      |                                                                                           | OSCCTRL32.SELCURR=4                          |                        |     |                      | 15.2  |        |

|                      | Crystal equivalent series resistance <sup>(3)</sup>                                       | OSCCTRL32.SELCURR=6                          |                        |     |                      | 61.8  | kΩ     |

|                      | f=32.768kHz                                                                               | OSCCTRL32.SELCURR=8                          | C <sub>L</sub> =12.5pF |     |                      | 101.8 |        |

|                      | OSCCTRL32.MODE=1                                                                          | OSCCTRL32.SELCURR=10                         |                        |     |                      | 138.5 |        |

|                      | Safety Factor = 3                                                                         | OSCCTRL32.SELCURR=15                         |                        |     |                      | 228.5 |        |

1. These values are based on simulation. These values are not covered by test limits in production or characterization.

2. Nominal crystal cycles.

3. These values are based on characterization. These values are not covered by test limits in production.

1. These values are based on simulation. These values are not covered by test limits in production or characterization.

The values in Table 9-43 describe the values of the BOD33.LEVEL in the flash User Page fuses.

| BOD33.LEVEL Value | Min | Тур  | Мах | Units |

|-------------------|-----|------|-----|-------|

| 16                |     | 2.08 |     |       |

| 20                |     | 2.18 |     |       |

| 24                |     | 2.33 |     |       |

| 28                |     | 2.48 |     |       |

| 32                |     | 2.62 |     | V     |

| 36                |     | 2.77 |     |       |

| 40                |     | 2.92 |     |       |

| 44                |     | 3.06 |     | Ţ     |

| 48                |     | 3.21 |     | Ţ     |

## Table 9-44. BOD33 Characteristics <sup>(1)</sup>

| Symbol               | Parameter                                                             | Conditions                                                             | Min | Тур  | Max | Units |

|----------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------|-----|------|-----|-------|

|                      | Step size, between adjacent values in BSCIF.BOD33LEVEL <sup>(1)</sup> |                                                                        |     | 34.4 |     | mV    |

| V <sub>HYST</sub>    | Hysteresis <sup>(1)</sup>                                             |                                                                        | 45  |      | 170 |       |

| t <sub>DET</sub>     | Detection time <sup>(1)</sup>                                         | Time with VDDIN < V <sub>TH</sub> necessary to generate a reset signal |     |      |     | μs    |

| I <sub>BOD33</sub>   | Current consumption <sup>(1)</sup>                                    | Normal mode                                                            |     |      | 36  | μA    |

| t <sub>STARTUP</sub> | Startup time <sup>(1)</sup>                                           | Normal mode                                                            |     |      | 6   | μs    |

1. These values are based on simulation. These values are not covered by test limits in production or characterization.

#### Maximum SPI Frequency, Master Output

The maximum SPI master output frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{PINMAX}, \frac{1}{SPIn}, \frac{f_{CLKSPI} \times 2}{9})$$

Where *SPIn* is the MOSI delay, USPI2 or USPI5 depending on CPOL and NCPHA.  $f_{PINMAX}$  is the maximum frequency of the SPI pins. refer to the I/O Pin Characteristics section for the maximum frequency of the pins.  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

#### Maximum SPI Frequency, Master Input

The maximum SPI master input frequency is given by the following formula:

USPI6-

MOSI

$$f_{SPCKMAX} = MIN(\frac{1}{SPIn + t_{VALID}}, \frac{f_{CLKSPI} \times 2}{9})$$

Where *SPIn* is the MISO setup and hold time, USPI0 + USPI1 or USPI3 + USPI4 depending on CPOL and NCPHA.  $T_{VALID}$  is the SPI slave response time. refer to the SPI slave datasheet for  $T_{VALID}$ .  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

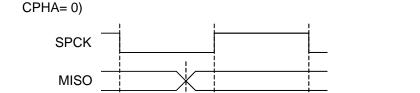

#### 9.10.2.2 Slave mode

Figure 9-9.

**9-9.** USART in SPI Slave Mode with (CPOL= 0 and CPHA= 1) or (CPOL= 1 and CPHA= 0)

| Symbol | Parameter                         | Conditions                           | Min                                                                       | Мах    | Units |

|--------|-----------------------------------|--------------------------------------|---------------------------------------------------------------------------|--------|-------|

| USPI6  | SPCK falling to MISO delay        |                                      |                                                                           | 593.9  |       |

| USPI7  | MOSI setup time before SPCK rises |                                      | $45.93 + t_{SAMPLE}^{(2)} + t_{CLK\_USART}$                               |        |       |

| USPI8  | MOSI hold time after SPCK rises   |                                      | 47.03 -( t <sub>SAMPLE</sub> <sup>(2)</sup> +<br>t <sub>CLK_USART )</sub> |        |       |

| USPI9  | SPCK rising to MISO delay         | V <sub>VDDIO</sub> from              |                                                                           | 593.38 |       |

| USPI10 | MOSI setup time before SPCK falls | 3.0V to 3.6V,<br>maximum<br>external | 45.93 +( $t_{SAMPLE}^{(2)}$ +<br>$t_{CLK_USART}$ )                        |        | ns    |

| USPI11 | MOSI hold time after SPCK falls   | capacitor =<br>40pF                  | 47.03 -( t <sub>SAMPLE</sub> <sup>(2)</sup> +<br>t <sub>CLK_USART</sub> ) |        |       |

| USPI12 | NSS setup time before SPCK rises  |                                      | 237.5                                                                     |        |       |

| USPI13 | NSS hold time after SPCK falls    |                                      | -1.81                                                                     |        |       |

| USPI14 | NSS setup time before SPCK falls  |                                      | 237.5                                                                     |        |       |

| USPI15 | NSS hold time after SPCK rises    |                                      | -1.81                                                                     |        |       |

Table 9-61.

USART3 in SPI mode Timing, Slave Mode<sup>(1)</sup>

Notes: 1. These values are based on simulation. These values are not covered by test limits in production.

2. Where:

$$t_{SAMPLE} = t_{SPCK} - \left( \left\lfloor \frac{t_{SPCK}}{2 \times t_{CLKUSART}} \right\rfloor + \frac{1}{2} \right) \times t_{CLKUSART}$$

#### Maximum SPI Frequency, Slave Input Mode

The maximum SPI slave input frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(\frac{f_{CLKSPI} \times 2}{9}, \frac{1}{SPIn})$$

Where *SPIn* is the MOSI setup and hold time, USPI7 + USPI8 or USPI10 + USPI11 depending on CPOL and NCPHA.  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

## Maximum SPI Frequency, Slave Output Mode

The maximum SPI slave output frequency is given by the following formula:

Atmel

$$f_{SPCKMAX} = MIN(\frac{f_{CLKSPI} \times 2}{9}, f_{PINMAX}, \frac{1}{SPIn + t_{SETUP}})$$

Where *SPIn* is the MISO delay, USPI6 or USPI9 depending on CPOL and NCPHA.  $T_{SETUP}$  is the SPI master setup time. refer to the SPI master datasheet for  $T_{SETUP}$ .  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.  $f_{PINMAX}$  is the maximum frequency of the SPI pins. refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

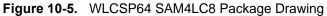

#### COMMON DIMENSIONS (Unit of Measure = mm)

BALL SIGNAL X COORD Y COORD

| BALL | SIGNAL  | X COORD | Y COORD |

|------|---------|---------|---------|

| A1   | PB04    | 1.75    | 1.75    |

| A2   | GNDANA  | 1.75    | 1.25    |

| A3   | ADVREFP | 1.75    | 0.75    |

| A4   | VDDANA  | 1.75    | 0.25    |

| A5   | PA09    | 1.75    | -0.25   |

| A6   | CAPL    | 1.75    | -0.75   |

| A7   | CAPH    | 1.75    | -1.25   |

| A8   | PA12    | 1.75    | -1.75   |

| B1   | PB03    | 1.25    | 1.75    |

| B2   | XIN32   | 1.25    | 1.25    |

| B3   | XOUT32  | 1,25    | 0.75    |

| B4   | PA08    | 1.25    | 0.25    |

| B5   | PB06    | 1.25    | -0.25   |

| B6   | PA10    | 1,25    | -0.75   |

| B7   | PA11    | 1.25    | -1.25   |

| B8   | VLCD    | 1.25    | -1.75   |

| C1   | VDDIN   | 0.75    | 1.75    |

| C2   | PB01    | 0.75    | 1,25    |

| C3   | PA05    | 0.75    | 0.75    |

| C4   | PA06    | 0.75    | 0.25    |

| C5   | PA07    | 0.75    | -0.25   |

| C6   | PB07    | 0.75    | -0.75   |

| C7 | PA13    | 0.75  | -1.25 |  |

|----|---------|-------|-------|--|

| C8 | BIAS1   | 0.75  | -1.75 |  |

| D1 | VDDOUT  | 0.25  | 1.75  |  |

| D2 | PB00    | 0.25  | 1.25  |  |

| D3 | PA04    | 0.25  | 0.75  |  |

| D4 | PB05    | 0.25  | 0.25  |  |

| D5 | PB12    | 0.25  | -0.25 |  |

| D6 | PB08    | 0.25  | -0.75 |  |

| D7 | PA14    | 0.25  | -1.25 |  |

| D8 | BIAS2   | 0.25  | -1.75 |  |

| E1 | GNDIN   | -0.25 | 1.75  |  |

| E2 | PA03    | -0.25 | 1.25  |  |

| E3 | PB02    | -0.25 | 0.75  |  |

| E4 | RESET_N | -0.25 | 0.25  |  |

| E5 | PB13    | -0.25 | -0.25 |  |

| E6 | PB09    | -0.25 | -0.75 |  |

| E7 | PA15    | -0.25 | -1.25 |  |

| E8 | GNDIO0  | -0.25 | -1.75 |  |

| F1 | VDDCORE | -0.75 | 1.75  |  |

| F2 | TCK     | -0.75 | 1.25  |  |

| F3 | PA02    | -0.75 | 0.75  |  |

| F4 | PB14    | -0.75 | 0.25  |  |

| BALL | SIGNAL | X COORD | Y COORD |

|------|--------|---------|---------|

| F5   | PA22   | -0.75   | -0.25   |

| F6   | PB10   | -0.75   | -0.75   |

| F7   | PA16   | -0.75   | -1.25   |

| F8   | VLCDIN | -0.75   | -1.75   |

| G1   | GNDIO1 | -1.25   | 1.75    |

| G2   | PA26   | -1.25   | 1.25    |

| G3   | PA24   | -1.25   | 0.75    |

| G4   | PA00   | -1.25   | 0.25    |

| G5   | PA01   | -1.25   | -0.25   |

| G6   | PA19   | -1.25   | -0.75   |

| G7   | PA18   | -1.25   | -1.25   |

| G8   | PA17   | -1.25   | -1.75   |

| H1   | VDDIO1 | -1.75   | 1.75    |

| H2   | PA25   | -1.75   | 1,25    |

| H3   | PA23   | -1.75   | 0.75    |

| H4   | PB15   | -1.75   | 0.25    |

| H5   | PA21   | -1.75   | -0.25   |

| H6   | VDDIO0 | -1.75   | -0.75   |

| H7   | PA20   | -1.75   | -1.25   |

| H8   | PB11   | -1.75   | -1.75   |

|      |        |         |         |

|      |        |         |         |

Notes: 1. Dimension "b" is measured at the maximum ball diameter in a plane to the seating plane.

2. Applied to whole wafer.

#### Table 10-14. Device and Package Maximum Weight

| 14.8                                         | mg   |

|----------------------------------------------|------|

| Table 10-15.         Package Characteristics |      |

| Moisture Sensitivity Level                   | MSL3 |

#### Table 10-16. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E1     |

Atmel

| Table 11-3. AT SAM4LOZ SUD Selle Oldening Informatio | Table 11-3. | ATSAM4LC2 Sub Serie Ordering Information |

|------------------------------------------------------|-------------|------------------------------------------|

|------------------------------------------------------|-------------|------------------------------------------|

| Ordering Code    | Flash<br>(Kbytes) | RAM<br>(Kbytes)  | Package  | Conditioning | Package<br>Type | Temperature Operating<br>Range |

|------------------|-------------------|------------------|----------|--------------|-----------------|--------------------------------|

| ATSAM4LC2CA-AU   |                   |                  |          | Tray         |                 |                                |

| ATSAM4LC2CA-AUR  |                   |                  | TQFP100  | Reel         |                 |                                |

| ATSAM4LC2CA-CFU  |                   |                  |          | Tray         |                 |                                |

| ATSAM4LC2CA-CFUR | 128               |                  | VFBGA100 | Reel         |                 |                                |

| ATSAM4LC2BA-AU   |                   |                  |          | Tray         |                 |                                |

| ATSAM4LC2BA-AUR  |                   |                  | TQFP64   | Reel         |                 |                                |

| ATSAM4LC2BA-MU   |                   | 128 3            | 32       |              | Tray            | Green                          |

| ATSAM4LC2BA-MUR  |                   | QFN64<br>WLCSP64 | Reel     |              |                 |                                |

| ATSAM4LC2BA-UUR  |                   |                  | WLCSP64  | Reel         |                 |                                |

| ATSAM4LC2AA-AU   |                   |                  |          | Tray         |                 |                                |

| ATSAM4LC2AA-AUR  |                   |                  | TQFP48   | Reel         |                 |                                |

| ATSAM4LC2AA-MU   |                   |                  |          | Tray         |                 |                                |

| ATSAM4LC2AA-MUR  |                   |                  | QFN48    | Reel         |                 |                                |

# Table 11-4. ATSAM4LS8 Sub Serie Ordering Information

| Ordering Code    | Flash<br>(Kbytes) | RAM<br>(Kbytes) | Package  | Conditioning | Package<br>Type | Temperature Operating<br>Range |

|------------------|-------------------|-----------------|----------|--------------|-----------------|--------------------------------|

| ATSAM4LS8CA-AU   | 512               | 64              | TQFP100  | Tray         | Green           | Industrial -40°C to 85°C       |

| ATSAM4LS8CA-AUR  |                   |                 |          | Reel         |                 |                                |

| ATSAM4LS8CA-CFU  |                   |                 | VFBGA100 | Tray         |                 |                                |

| ATSAM4LS8CA-CFUR |                   |                 |          | Reel         |                 |                                |

| ATSAM4LS8BA-AU   |                   |                 | TQFP64   | Tray         |                 |                                |

| ATSAM4LS8BA-AUR  |                   |                 |          | Reel         |                 |                                |

| ATSAM4LS8BA-MU   |                   |                 | QFN64    | Tray         |                 |                                |

| ATSAM4LS8BA-MUR  |                   |                 |          | Reel         |                 |                                |

| ATSAM4LS8BA-UUR  |                   |                 | WLCSP64  | Reel         |                 |                                |

| ATSAM4LS8AA-MU   |                   |                 | QFN48    | Tray         |                 |                                |

| ATSAM4LS8AA-MUR  |                   |                 |          | Reel         |                 |                                |