Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 48MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                      |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 48                                                                        |

| Program Memory Size        | 512KB (512K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | · ·                                                                       |

| RAM Size                   | 64K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.68V ~ 3.6V                                                              |

| Data Converters            | A/D 7x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4ls8ba-aur |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

events, even in sleep modes where the module clock is stopped. Power monitoring is supported by on-chip Power-on Reset (POR18, POR33), Brown-out Detectors (BOD18, BOD33). The device features several oscillators, such as Phase Locked Loop (PLL), Digital Frequency Locked Loop (DFLL), Oscillator 0 (OSC0), Internal RC 4,8,12MHz oscillator (RCFAST), system RC oscillator (RCSYS), Internal RC 80MHz, Internal 32kHz RC and 32kHz Crystal Oscillator. Either of these oscillators can be used as source for the system clock. The DFLL is a programmable internal oscillator from 40 to 150MHz. It can be tuned to a high accuracy if an accurate reference clock is running, e.g. the 32kHz crystal oscillator.

The Watchdog Timer (WDT) will reset the device unless it is periodically serviced by the software. This allows the device to recover from a condition that has caused the system to be unstable.

The Asynchronous Timer (AST) combined with the 32kHz crystal oscillator supports powerful real-time clock capabilities, with a maximum timeout of up to 136 years. The AST can operate in counter or calendar mode.

The Frequency Meter (FREQM) allows accurate measuring of a clock frequency by comparing it to a known reference clock.

The Full-speed USB 2.0 device and embedded host interface (USBC) supports several USB classes at the same time utilizing the rich end-point configuration.

The device includes six identical 16-bit Timer/Counter (TC) channels. Each channel can be independently programmed to perform frequency measurement, event counting, interval measurement, pulse generation, delay timing, and pulse width modulation.

The ATSAM4L8/L4/L2 also features many communication interfaces, like USART, SPI, or TWI, for communication intensive applications. The USART supports different communication modes, like SPI Mode and LIN Mode.

A general purpose 16-channel ADC is provided, as well as four analog comparators (ACIFC). The ADC can operate in 12-bit mode at full speed. The analog comparators can be paired to detect when the sensing voltage is within or outside the defined reference window.

Atmel offers the QTouch Library for embedding capacitive touch buttons, sliders, and wheels functionality. The patented charge-transfer signal acquisition offers robust sensing and includes fully debounced reporting of touch keys as well as Adjacent Key Suppression<sup>®</sup> (AKS<sup>®</sup>) technology for unambiguous detection of key events. The easy-to-use QTouch Suite toolchain allows you to explore, develop, and debug your own touch applications.

The Audio Bitstream DAC (ABDACB) converts a 16-bit sample value to a digital bitstream with an average value proportional to the sample value. Two channels are supported, making the ABDAC particularly suitable for stereo audio.

The Inter-IC Sound Controller (IISC) provides a 5-bit wide, bidirectional, synchronous, digital audio link with external audio devices. The controller is compliant with the Inter-IC Sound (I2S) bus specification.

Atmel

## 3. Package and Pinout

## 3.1 Package

The device pins are multiplexed with peripheral functions as described in Section 3.2 "Peripheral Multiplexing on I/O lines" on page 19.

## 3.1.1 ATSAM4LCx Pinout

Atmel

## Figure 3-1. ATSAM4LC TQFP100 Pinout

ATSAM4L8/L4/L2

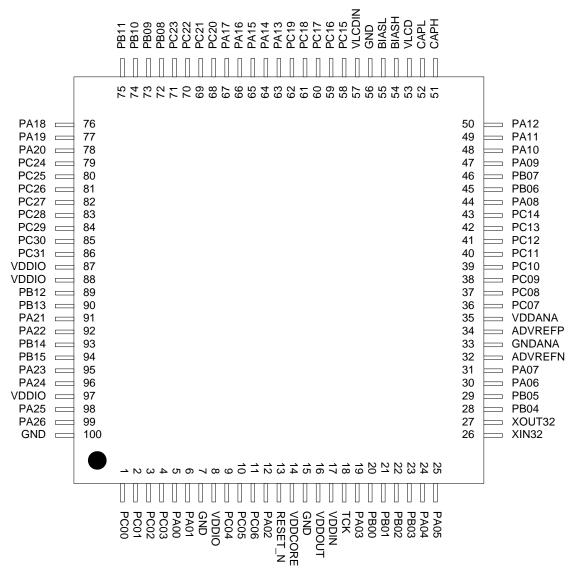

Figure 3-9. ATSAM4LS TQFP64/QFN64 Pinout

## 3.2 Peripheral Multiplexing on I/O lines

## 3.2.1 Multiplexed Signals

Each GPIO line can be assigned to one of the peripheral functions. The following tables (Section 3-1 "100-pin GPIO Controller Function Multiplexing" on page 19 to Section 3-4 "48-pin GPIO Controller Function Multiplexing" on page 28) describes the peripheral signals multiplexed to the GPIO lines.

Peripheral functions that are not relevant in some parts of the family are grey-shaded.

For description of differents Supply voltage source, refer to the Section 6. "Power and Startup Considerations" on page 46.

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 1 of 4)

| lable | •          |     |            | 0 0011 | 101101 | i unotion | manupion       | ng (Oneer     | 1 01 1)          |                 |                   |                |                 |

|-------|------------|-----|------------|--------|--------|-----------|----------------|---------------|------------------|-----------------|-------------------|----------------|-----------------|

|       | ATSAM4LC   |     | ATSAM4LS   | Pin    | GPIO   | Supply    | GPIO Functions |               |                  |                 |                   |                |                 |

| QFN   | VFBGA      | QFN | VFBGA      |        |        |           | Α              | В             | С                | D               | E                 | F              | G               |

| 5     | B9         | 5   | B9         | PA00   | 0      | VDDIO     |                |               |                  |                 |                   |                |                 |

| 6     | B8         | 6   | B8         | PA01   | 1      | VDDIO     |                |               |                  |                 |                   |                |                 |

| 12    | A7         | 12  | A7         | PA02   | 2      | VDDIN     | SCIF<br>GCLK0  | SPI<br>NPCS0  |                  |                 |                   |                | CATB<br>DIS     |

| 19    | В3         | 19  | В3         | PA03   | 3      | VDDIN     |                | SPI<br>MISO   |                  |                 |                   |                |                 |

| 24    | A2         | 24  | A2         | PA04   | 4      | VDDANA    | ADCIFE<br>AD0  | USART0<br>CLK | EIC<br>EXTINT2   | GLOC<br>IN1     |                   |                | CATB<br>SENSE0  |

| 25    | A1         | 25  | A1         | PA05   | 5      | VDDANA    | ADCIFE<br>AD1  | USART0<br>RXD | EIC<br>EXTINT3   | GLOC<br>IN2     | ADCIFE<br>TRIGGER |                | CATB<br>SENSE1  |

| 30    | C3         | 30  | C3         | PA06   | 6      | VDDANA    | DACC<br>VOUT   | USART0<br>RTS | EIC<br>EXTINT1   | GLOC<br>IN0     | ACIFC<br>ACAN0    |                | CATB<br>SENSE2  |

| 31    | D3         | 31  | D3         | PA07   | 7      | VDDANA    | ADCIFE<br>AD2  | USART0<br>TXD | EIC<br>EXTINT4   | GLOC<br>IN3     | ACIFC<br>ACAP0    |                | CATB<br>SENSE3  |

| 44    | G2         | 44  | G2         | PA08   | 8      | LCDA      | USART0<br>RTS  | TC0<br>A0     | PEVC<br>PAD EVT0 | GLOC<br>OUT0    |                   | LCDCA<br>SEG23 | CATB<br>SENSE4  |

| 47    | F5         | 47  | F5         | PA09   | 9      | LCDA      | USART0<br>CTS  | TC0<br>B0     | PEVC<br>PAD EVT1 | PARC<br>PCDATA0 |                   | LCDCA<br>COM3  | CATB<br>SENSE5  |

| 48    | H2         | 48  | H2         | PA10   | 10     | LCDA      | USART0<br>CLK  | TC0<br>A1     | PEVC<br>PAD EVT2 | PARC<br>PCDATA1 |                   | LCDCA<br>COM2  | CATB<br>SENSE6  |

| 49    | H3         | 49  | H3         | PA11   | 11     | LCDA      | USART0<br>RXD  | TC0<br>B1     | PEVC<br>PAD EVT3 | PARC<br>PCDATA2 |                   | LCDCA<br>COM1  | CATB<br>SENSE7  |

| 50    | J2         | 50  | J2         | PA12   | 12     | LCDA      | USART0<br>TXD  | TC0<br>A2     |                  | PARC<br>PCDATA3 |                   | LCDCA<br>COM0  | CATB<br>DIS     |

| 63    | H5         | 63  | H5         | PA13   | 13     | LCDA      | USART1<br>RTS  | TC0<br>B2     | SPI<br>NPCS1     | PARC<br>PCDATA4 |                   | LCDCA<br>SEG5  | CATB<br>SENSE8  |

| 64    | <b>K</b> 7 | 64  | <b>K</b> 7 | PA14   | 14     | LCDA      | USART1<br>CLK  | TC0<br>CLK0   | SPI<br>NPCS2     | PARC<br>PCDATA5 |                   | LCDCA<br>SEG6  | CATB<br>SENSE9  |

| 65    | G5         | 65  | G5         | PA15   | 15     | LCDA      | USART1<br>RXD  | TC0<br>CLK1   | SPI<br>NPCS3     | PARC<br>PCDATA6 |                   | LCDCA<br>SEG7  | CATB<br>SENSE10 |

| Table 3-2. | 64-pin GPIO Controller Function Multiplexing (Sheet 3 of 3) |

|------------|-------------------------------------------------------------|

|            |                                                             |

| ATSAM4LC   | ATSAM4LS   | Pin  | GPIO | Supply |                |                  |                  |              |                   |                |                 |

|------------|------------|------|------|--------|----------------|------------------|------------------|--------------|-------------------|----------------|-----------------|

|            |            | ā    | GP   | np     |                | GPIO Functions   |                  |              |                   |                |                 |

| QFP<br>QFN | QFP<br>QFN |      |      |        | Α              | В                | с                | D            | E                 | F              | G               |

|            | 33         | PA27 | 27   | LCDA   | SPI<br>MISO    | IISC<br>ISCK     | ABDACB<br>DAC0   | GLOC<br>IN4  | USART3<br>RTS     |                | CATB<br>SENSE0  |

|            | 34         | PA28 | 28   | LCDA   | SPI<br>MOSI    | IISC<br>ISDI     | ABDACB<br>DACN0  | GLOC<br>IN5  | USART3<br>CTS     |                | CATB<br>SENSE1  |

|            | 35         | PA29 | 29   | LCDA   | SPI<br>SCK     | IISC<br>IWS      | ABDACB<br>DAC1   | GLOC<br>IN6  | USART3<br>CLK     |                | CATB<br>SENSE2  |

|            | 38         | PA30 | 30   | LCDA   | SPI<br>NPCS0   | IISC<br>ISDO     | ABDACB<br>DACN1  | GLOC<br>IN7  | USART3<br>RXD     |                | CATB<br>SENSE3  |

|            | 39         | PA31 | 31   | LCDA   | SPI<br>NPCS1   | IISC<br>IMCK     | ABDACB<br>CLK    | GLOC<br>OUT1 | USART3<br>TXD     |                | CATB<br>DIS     |

| 11         | 11         | PB00 | 32   | VDDIN  | TWIMS1<br>TWD  | USART0<br>RXD    |                  |              |                   |                | CATB<br>SENSE21 |

| 12         | 12         | PB01 | 33   | VDDIN  | TWIMS1<br>TWCK | USART0<br>TXD    | EIC<br>EXTINT0   |              |                   |                | CATB<br>SENSE22 |

| 13         | 13         | PB02 | 34   | VDDANA | ADCIFE<br>AD3  | USART1<br>RTS    | ABDACB<br>DAC0   | IISC<br>ISCK | ACIFC<br>ACBN0    |                | CATB<br>SENSE23 |

| 14         | 14         | PB03 | 35   | VDDANA | ADCIFE<br>AD4  | USART1<br>CLK    | ABDACB<br>DACN0  | IISC<br>ISDI | ACIFC<br>ACBP0    |                | CATB<br>DIS     |

| 19         | 19         | PB04 | 36   | VDDANA | ADCIFE<br>AD5  | USART1<br>RXD    | ABDACB<br>DAC1   | IISC<br>ISDO | DACC<br>EXT TRIG0 |                | CATB<br>SENSE24 |

| 20         | 20         | PB05 | 37   | VDDANA | ADCIFE<br>AD6  | USART1<br>TXD    | ABDACB<br>DACN1  | IISC<br>IMCK |                   |                | CATB<br>SENSE25 |

| 27         | 27         | PB06 | 38   | LCDA   | USART3<br>RTS  |                  | GLOC<br>IN4      | IISC<br>IWS  |                   | LCDCA<br>SEG22 | CATB<br>SENSE26 |

| 28         | 28         | PB07 | 39   | LCDA   | USART3<br>CTS  |                  | GLOC<br>IN5      | TC0<br>A0    |                   | LCDCA<br>SEG21 | CATB<br>SENSE27 |

| 45         | 45         | PB08 | 40   | LCDA   | USART3<br>CLK  |                  | GLOC<br>IN6      | ТС0<br>В0    |                   | LCDCA<br>SEG14 | CATB<br>SENSE28 |

| 46         | 46         | PB09 | 41   | LCDA   | USART3<br>RXD  | PEVC<br>PAD EVT2 | GLOC<br>IN7      | TC0<br>A1    |                   | LCDCA<br>SEG15 | CATB<br>SENSE29 |

| 47         | 47         | PB10 | 42   | LCDA   | USART3<br>TXD  | PEVC<br>PAD EVT3 | GLOC<br>OUT1     | TC0<br>B1    | SCIF<br>GCLK0     | LCDCA<br>SEG16 | CATB<br>SENSE30 |

| 48         | 48         | PB11 | 43   | LCDA   | USART0<br>CTS  | SPI<br>NPCS2     |                  | TC0<br>A2    | SCIF<br>GCLK1     | LCDCA<br>SEG17 | CATB<br>SENSE31 |

| 53         | 53         | PB12 | 44   | LCDC   | USART0<br>RTS  | SPI<br>NPCS3     | PEVC<br>PAD EVT0 | TC0<br>B2    | SCIF<br>GCLK2     | LCDCA<br>SEG32 | CATB<br>DIS     |

| 54         | 54         | PB13 | 45   | LCDC   | USART0<br>CLK  | SPI<br>NPCS1     | PEVC<br>PAD EVT1 | TC0<br>CLK0  | SCIF<br>GCLK3     | LCDCA<br>SEG33 | CATB<br>SENSE0  |

| 57         | 57         | PB14 | 46   | LCDC   | USART0<br>RXD  | SPI<br>MISO      | TWIM3<br>TWD     | TC0<br>CLK1  | SCIF<br>GCLK IN0  | LCDCA<br>SEG36 | CATB<br>SENSE1  |

| 58         | 58         | PB15 | 47   | LCDC   | USART0<br>TXD  | SPI<br>MOSI      | TWIM3<br>TWCK    | TC0<br>CLK2  | SCIF<br>GCLK IN1  | LCDCA<br>SEG37 | CATB<br>SENSE2  |

|          |          |      |      | Contione |                | планиріслі       |                  |              | age (Sneet        | 2010)          |                 |

|----------|----------|------|------|----------|----------------|------------------|------------------|--------------|-------------------|----------------|-----------------|

| ATSAM4LC | ATSAM4LS | Pin  | GPIO | Supply   | GPIO Functions |                  |                  |              |                   |                |                 |

| WLCSP    | WLCSP    |      |      |          | Α              | В                | С                | D            | Е                 | F              | G               |

| НЗ       | H3       | PA23 | 23   | LCDC     | SPI<br>SCK     | TWIMS0<br>TWD    | EIC<br>EXTINT8   | GLOC<br>IN3  | SCIF<br>GCLK IN0  | LCDCA<br>SEG38 | CATB<br>DIS     |

| G3       | G3       | PA24 | 24   | LCDC     | SPI<br>NPCS0   | TWIMS0<br>TWCK   |                  | GLOC<br>OUT0 | SCIF<br>GCLK IN1  | LCDCA<br>SEG39 | CATB<br>SENSE18 |

| H2       | H2       | PA25 | 25   | VDDIO    | USBC<br>DM     | USART2<br>RXD    |                  |              |                   |                | CATB<br>SENSE19 |

| G2       | G2       | PA26 | 26   | VDDIO    | USBC<br>DP     | USART2<br>TXD    |                  |              |                   |                | CATB<br>SENSE20 |

|          | A7       | PA27 | 27   | LCDA     | SPI<br>MISO    | IISC<br>ISCK     | ABDACB<br>DAC0   | GLOC<br>IN4  | USART3<br>RTS     |                | CATB<br>SENSE0  |

|          | A6       | PA28 | 28   | LCDA     | SPI<br>MOSI    | IISC<br>ISDI     | ABDACB<br>DACN0  | GLOC<br>IN5  | USART3<br>CTS     |                | CATB<br>SENSE1  |

|          | B8       | PA29 | 29   | LCDA     | SPI<br>SCK     | IISC             | ABDACB<br>DAC1   | GLOC<br>IN6  | USART3<br>CLK     |                | CATB<br>SENSE2  |

|          | E8       | PA30 | 30   | LCDA     | SPI<br>NPCS0   | IISC<br>ISDO     | ABDACB<br>DACN1  | GLOC<br>IN7  | USART3<br>RXD     |                | CATB<br>SENSE3  |

|          | F8       | PA31 | 31   | LCDA     | SPI<br>NPCS1   | IISC<br>IMCK     | ABDACB<br>CLK    | GLOC<br>OUT1 | USART3<br>TXD     |                | CATB<br>DIS     |

| D2       | D2       | PB00 | 32   | VDDIN    | TWIMS1<br>TWD  | USART0<br>RXD    |                  |              |                   |                | CATB<br>SENSE21 |

| C2       | C2       | PB01 | 33   | VDDIN    | TWIMS1<br>TWCK | USART0<br>TXD    | EIC<br>EXTINT0   |              |                   |                | CATB<br>SENSE22 |

| E3       | E3       | PB02 | 34   | VDDANA   | ADCIFE<br>AD3  | USART1<br>RTS    | ABDACB<br>DAC0   | IISC<br>ISCK | ACIFC<br>ACBN0    |                | CATB<br>SENSE23 |

| B1       | B1       | PB03 | 35   | VDDANA   | ADCIFE<br>AD4  | USART1<br>CLK    | ABDACB<br>DACN0  | IISC<br>ISDI | ACIFC<br>ACBP0    |                | CATB<br>DIS     |

| A1       | A1       | PB04 | 36   | VDDANA   | ADCIFE<br>AD5  | USART1<br>RXD    | ABDACB<br>DAC1   | IISC<br>ISDO | DACC<br>EXT TRIG0 |                | CATB<br>SENSE24 |

| D4       | D4       | PB05 | 37   | VDDANA   | ADCIFE<br>AD6  | USART1<br>TXD    | ABDACB<br>DACN1  | IISC<br>IMCK |                   |                | CATB<br>SENSE25 |

| В5       | В5       | PB06 | 38   | LCDA     | USART3<br>RTS  |                  | GLOC<br>IN4      | IISC<br>IWS  |                   | LCDCA<br>SEG22 | CATB<br>SENSE26 |

| C6       | C6       | PB07 | 39   | LCDA     | USART3<br>CTS  |                  | GLOC<br>IN5      | TC0<br>A0    |                   | LCDCA<br>SEG21 | CATB<br>SENSE27 |

| D6       | D6       | PB08 | 40   | LCDA     | USART3<br>CLK  |                  | GLOC<br>IN6      | ТС0<br>В0    |                   | LCDCA<br>SEG14 | CATB<br>SENSE28 |

| E6       | E6       | PB09 | 41   | LCDA     | USART3<br>RXD  | PEVC<br>PAD EVT2 | GLOC<br>IN7      | TC0<br>A1    |                   | LCDCA<br>SEG15 | CATB<br>SENSE29 |

| F6       | F6       | PB10 | 42   | LCDA     | USART3<br>TXD  | PEVC<br>PAD EVT3 | GLOC<br>OUT1     | TC0<br>B1    | SCIF<br>GCLK0     | LCDCA<br>SEG16 | CATB<br>SENSE30 |

| H8       | H8       | PB11 | 43   | LCDA     | USART0<br>CTS  | SPI<br>NPCS2     |                  | TC0<br>A2    | SCIF<br>GCLK1     | LCDCA<br>SEG17 | CATB<br>SENSE31 |

| D5       | D5       | PB12 | 44   | LCDC     | USART0<br>RTS  | SPI<br>NPCS3     | PEVC<br>PAD EVT0 | TC0<br>B2    | SCIF<br>GCLK2     | LCDCA<br>SEG32 | CATB<br>DIS     |

Table 3-3.

64-pin GPIO Controller Function Multiplexing for WLCSP package (Sheet 2 of 3)

# ATSAM4L8/L4/L2

| Signal Name            | Function                             | Туре               | Active<br>Level | Comments |

|------------------------|--------------------------------------|--------------------|-----------------|----------|

|                        | Inter-IC Sound (I2S)                 | Controller - IIS   | С               |          |

| IMCK                   | I2S Master Clock                     | Output             |                 |          |

| ISCK                   | I2S Serial Clock                     | I/O                |                 |          |

| ISDI                   | I2S Serial Data In                   | Input              |                 |          |

| ISDO                   | I2S Serial Data Out                  | Output             |                 |          |

| IWS                    | I2S Word Select                      | I/O                |                 |          |

|                        | LCD Controll                         | er - LCDCA         |                 |          |

| BIASL                  | Bias voltage (1/3 VLCD)              | Analog             |                 |          |

| BIASH                  | Bias voltage (2/3 VLCD)              | Analog             |                 |          |

| CAPH                   | High voltage end of flying capacitor | Analog             |                 |          |

| CAPL                   | Low voltage end of flying capacitor  | Analog             |                 |          |

| COM3 - COM0            | Common terminals                     | Analog             |                 |          |

| SEG39 - SEG0           | Segment terminals                    | Analog             |                 |          |

| VLCD                   | Bias voltage                         | Analog             |                 |          |

|                        | Parallel Capt                        | ure - PARC         |                 |          |

| PCCK                   | Clock                                | Input              |                 |          |

| PCDATA7 - PCDATA0      | Data lines                           | Input              |                 |          |

| PCEN1                  | Data enable 1                        | Input              |                 |          |

| PCEN2                  | Data enable 2                        | Input              |                 |          |

|                        | Peripheral Event C                   | ontroller - PEVC   | ;               |          |

| PAD_EVT3 -<br>PAD_EVT0 | Event Inputs                         | Input              |                 |          |

|                        | Power Mana                           | ager - PM          |                 |          |

| RESET_N                | Reset                                | Input              | Low             |          |

|                        | System Control I                     | nterface - SCIF    |                 |          |

| GCLK3 - GCLK0          | Generic Clock Outputs                | Output             |                 |          |

| GCLK_IN1 - GCLK_IN0    | Generic Clock Inputs                 | Input              |                 |          |

| XIN0                   | Crystal 0 Input                      | Analog/<br>Digital |                 |          |

| XOUT0                  | Crystal 0 Output                     | Analog             |                 |          |

|                        | Serial Peripheral                    | Interface - SPI    |                 | •        |

| MISO                   | Master In Slave Out                  | I/O                |                 |          |

| MOSI                   | Master Out Slave In                  | I/O                |                 |          |

|                        |                                      | I/O                | Low             |          |

| NPCS3 - NPCS0          |                                      |                    |                 |          |

## Table 3-8. Signal Descriptions List (Sheet 2 of 4)

## **Table 3-8.**Signal Descriptions List (Sheet 4 of 4)

| Signal Name | Function                           | Туре | Active<br>Level | Comments |

|-------------|------------------------------------|------|-----------------|----------|

| PA31 - PA00 | Parallel I/O Controller I/O Port A | I/O  |                 |          |

| PB15 - PB00 | Parallel I/O Controller I/O Port B | I/O  |                 |          |

| PC31 - PC00 | Parallel I/O Controller I/O Port C | I/O  |                 |          |

Note: 1. See "Power and Startup Considerations" section.

## 3.4 I/O Line Considerations

## 3.4.1 SW/JTAG Pins

The JTAG pins switch to the JTAG functions if a rising edge is detected on TCK low after the RESET\_N pin has been released. The TMS, and TDI pins have pull-up resistors when used as JTAG pins. The TCK pin always has pull-up enabled during reset. The JTAG pins can be used as GPIO pins and multiplexed with peripherals when the JTAG is disabled. Refer to Section 3.2.3 "JTAG Port Connections" on page 29 for the JTAG port connections.

For more details, refer to Section 1.1 "Enhanced Debug Port (EDP)" on page 3.

## 3.4.2 RESET\_N Pin

The RESET\_N pin is a schmitt input and integrates a permanent pull-up resistor to VDDIN. As the product integrates a power-on reset detector, the RESET\_N pin can be left unconnected in case no reset from the system needs to be applied to the product.

#### 3.4.3 TWI Pins

When these pins are used for TWI, the pins are open-drain outputs with slew-rate limitation andinputs with inputs with spike-filtering. When used as GPIO-pins or used for other peripherals, the pins have the same characteristics as GPIO pins.

#### 3.4.4 GPIO Pins

All the I/O lines integrate a pull-up/pull-down resistor and slew rate controller. Programming these features is performed independently for each I/O line through the GPIO Controllers. After reset, I/O lines default as inputs with pull-up and pull-down resistors disabled and slew rate enabled.

#### 3.4.5 High-drive Pins

The six pins PA02, PB00, PB01, PC04, PC05 and PC06 have high-drive output capabilities. Refer to Section 9.6.2 "High-drive I/O Pin : PA02, PC04, PC05, PC06" on page 115 for electrical characteristics.

#### 3.4.6 USB Pins

When these pins are used for USB, the pins are behaving according to the USB specification. When used as GPIO pins or used for other peripherals, the pins have the same behavior as other normal I/O pins, but the characteristics are different. Refer to Section 9.6.3 "USB I/O Pin : PA25, PA26" on page 116 for electrical characteristics.

These pins are compliant to USB standard only when VDDIO power supply is 3.3V nominal.

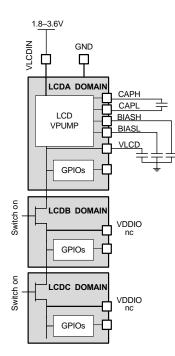

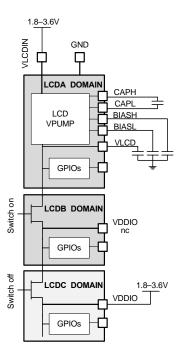

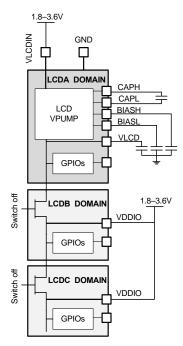

connected to an external voltage source (1.8-3.6V). LCDB cluster is not available in 64 and 48 pin packages

| Package          | Segments<br>in use | VDDIO<br>LCDB | VDDIO<br>LCDC |

|------------------|--------------------|---------------|---------------|

|                  | [1,24]             | 1.8-3.6V      | 1.8-3.6V      |

| 100-pin packages | [1, 32]            | nc            | 1.8-3.6V      |

|                  | [1, 40]            | nc            | nc            |

| 64-pin packages  | [1,15]             | -             | 1.8-3.6V      |

| 04-pin packages  | [1, 23]            | -             | nc            |

| 48-pin packages  | [1,9]              | -             | 1.8-3.6V      |

|                  | [1,13]             | -             | nc            |

| Table 6-1. | LCD powering when using the internal voltage pump |

|------------|---------------------------------------------------|

|------------|---------------------------------------------------|

Up to 4x40 segments No GPIO in LCD clusters Up to 4x32 segments Up to 8 GPIOs in LCDC clusters

Up to 4x24 segments Up to 16 GPIOs in LCDB & LCDC clusters

## 8.7.14.4 CLAMP

This instruction selects the Bypass register as Data Register. The device output pins are driven from the boundary-scan chain.

Starting in Run-Test/Idle, the CLAMP instruction is accessed the following way:

- 1. Select the IR Scan path.

- 2. In Capture-IR: The IR output value is latched into the shift register.

- 3. In Shift-IR: The instruction register is shifted by the TCK input.

- 4. In Update-IR: The data from the boundary-scan chain is applied to the output pins.

- 5. Return to Run-Test/Idle.

- 6. Select the DR Scan path.

- 7. In Capture-DR: A logic '0' is loaded into the Bypass Register.

Atmel

- 8. In Shift-DR: Data is scanned from TDI to TDO through the Bypass register.

- 9. Return to Run-Test/Idle.

### Table 8-8. CLAMP Details

| Instructions    | Details           |

|-----------------|-------------------|

| IR input value  | <b>0101</b> (0x5) |

| IR output value | p00s              |

| DR Size         | 1                 |

| DR input value  | x                 |

| DR output value | x                 |

| 8.9.11.8   | Chip Identification Regist | er |

|------------|----------------------------|----|

| Name:      | CIDR                       |    |

| Access Ty  | e: Read-Only               |    |

| Offset:    | 0xF0                       |    |

| Reset Valu | : -                        |    |

| 31  | 30    | 29     | 28 | 27     | 26      | 25 | 24 |  |

|-----|-------|--------|----|--------|---------|----|----|--|

| EXT |       | NVPTYP |    |        | AR      | СН |    |  |

|     |       |        |    |        |         |    |    |  |

| 23  | 22    | 21     | 20 | 19     | 18      | 17 | 16 |  |

|     | ARCH  |        |    |        | SRAMSIZ |    |    |  |

|     |       |        |    |        |         |    |    |  |

| 15  | 14    | 13     | 12 | 11     | 10      | 9  | 8  |  |

|     | NVF   | SIZ2   |    | NVPSIZ |         |    |    |  |

|     |       |        |    |        |         |    |    |  |

| 7   | 6     | 5      | 4  | 3      | 2       | 1  | 0  |  |

|     | EPROC |        |    |        | VERSION |    |    |  |

Note: Refer to section CHIPID for more information on this register.

instruction for the first time. SAMPLE/PRELOAD can also be used for taking a snapshot of the external pins during normal operation of the part.

When using the JTAG interface for Boundary-Scan, the JTAG TCK clock is independent of the internal chip clock, which is not required to run.

**NOTE:** For pins connected to 5V lines care should be taken to not drive the pins to a logic one using boundary scan, as this will create a current flowing from the 3,3V driver to the 5V pullup on the line. Optionally a series resistor can be added between the line and the pin to reduce the current.

## 8.11.7 Flash Programming typical procedure

Flash programming is performed by operating Flash controller commands. The Flash controller is connected to the system bus matrix and is then controllable from the AHP-AP. The AHB-AP cannot write the FLASH page buffer while the core\_hold\_reset is asserted. The AHB-AP cannot be accessed when the device is in protected state. It is important to ensure that the CPU is halted prior to operating any flash programming operation to prevent it from corrupting the system configuration. The recommended sequence is shown below:

- 1. At power up, RESET\_N is driven low by a debugger. The on-chip regulator holds the system in a POR state until the input supply is above the POR threshold. The system continues to be held in this static state until the internally regulated supplies have reached a safe operating.

- 2. PM starts, clocks are switched to the slow clock (Core Clock, System Clock, Flash Clock, and any Bus Clocks that do not have clock gate control). Internal resets are maintained due to the external reset.

- The Debug Port (DP) and Access Ports (AP) receives a clock and leave the reset state,

- 3. The debugger maintains a low level on TCK and release RESET\_N.

- The SMAP asserts the core\_hold\_reset signal

- 4. The Cortex-M4 core remains in reset state, meanwhile the rest of the system is released.

- 5. The debugger then configures the NVIC to catch the Cortex-M4 core reset vector fetch. For more information on how to program the NVIC, refer to the ARMv7-M Architecture Reference Manual.

- 6. The debugger writes a one in the SMAP SCR.HCR to release the Cortex-M4 core reset to make the system bus matrix accessible from the AHB-AP.

- 7. The Cortex-M4 core initializes the SP, then read the exception vector and stalls

- 8. Programming is available through the AHB-AP

Atmel

9. After operation is completed, the chip can be restarted either by asserting RESET\_N or switching power off/on or clearing SCR.HCR. Make sure that the TCK pin is high when releasing RESET\_N not to halt the core.

## ATSAM4L8/L4/L2

3. These values are based on characterization. These values are not covered by test limits in production

## 9.6.2 High-drive I/O Pin : PA02, PC04, PC05, PC06

Table 9-14.

High-drive I/O Pin Characteristics <sup>(1)</sup>

| Symbol                | Parameter                                | Conditions    |                                                    | Min                    | Тур  | Max                    | Units |

|-----------------------|------------------------------------------|---------------|----------------------------------------------------|------------------------|------|------------------------|-------|

| R <sub>PULLUP</sub>   | Pull-up resistance (2)                   |               |                                                    |                        | 40   |                        | kΩ    |

| R <sub>PULLDOWN</sub> | Pull-down resistance <sup>(2)</sup>      |               |                                                    |                        | 40   |                        | kΩ    |

| V <sub>IL</sub>       | Input low-level voltage                  |               |                                                    | -0.3                   |      | 0.2 * V <sub>VDD</sub> |       |

| V <sub>IH</sub>       | Input high-level voltage                 |               |                                                    | 0.8 * V <sub>VDD</sub> |      | V <sub>VDD</sub> + 0.3 |       |

| V <sub>OL</sub>       | Output low-level voltage                 |               |                                                    |                        | 0.4  | 0.4                    | V     |

| V <sub>OH</sub>       | Output high-level voltage                |               |                                                    | V <sub>VDD</sub> - 0.4 |      |                        |       |

|                       |                                          |               | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                        |      | 1.8                    |       |

|                       | Output low lovel surrest (3)             | ODCR0=0       | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                        |      | 3.2                    | mA    |

| I <sub>OL</sub>       | Output low-level current <sup>(3)</sup>  |               | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                        |      | 3.2                    |       |

|                       |                                          | ODCR0=1       | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                        |      | 6                      | mA    |

|                       |                                          |               | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                        |      | 1.6                    |       |

|                       | Outrast bisk laurel surray (3)           | ODCR0=0       | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                        |      | 3.2                    | mA    |

| I <sub>OH</sub>       | Output high-level current <sup>(3)</sup> | 00000 4       | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                   |                        |      | 3.2                    | mA    |

|                       |                                          | ODCR0=1       | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                    |                        |      | 6                      |       |

| (2)                   |                                          | OSRR0=0       | ODCR0=0                                            |                        |      | 20                     | ns    |

|                       |                                          | OSRR0=1       | 1.68V <v<sub>VDD&lt;2.7V,<br/>Cload = 25pF</v<sub> |                        |      | 40                     |       |

| t <sub>RISE</sub>     | Rise time <sup>(2)</sup>                 | OSRR0=0       | ODCR0=0                                            |                        |      | 11                     |       |

|                       |                                          | OSRR0=1       | $2.7V < V_{VDD} < 3.6V$ ,<br>Cload = 25pF          |                        |      | 18                     | ns    |

|                       |                                          | OSRR0=0       | ODCR0=0                                            |                        |      | 20                     |       |

|                       | Fall time <sup>(2)</sup>                 | OSRR0=1       | 1.68V <v<sub>VDD&lt;2.7V,<br/>Cload = 25pF</v<sub> |                        |      | 40                     | ns    |

| t <sub>FALL</sub>     |                                          | OSRR0=0       | ODCR0=0                                            |                        |      | 11                     |       |

|                       |                                          | OSRR0=1       | $2.7V < V_{VDD} < 3.6V,$<br>Cload = 25pF           |                        |      | 18                     | ns    |

| F                     |                                          | OSRR0=0       | ODCR0=0, V <sub>VDD</sub> >2.7V                    |                        |      | 22                     | MHz   |

|                       | Output frequency <sup>(2)</sup>          | OSRR0=1       | load = 25pF                                        |                        |      | 17                     | MHz   |

| F <sub>PINMAX</sub>   |                                          | OSRR0=0       | ODCR0=1, V <sub>VDD</sub> >2.7V                    |                        |      | 35                     | MHz   |

|                       |                                          | OSRR0=1       | load = 25pF                                        |                        |      | 26                     | MHz   |

| I <sub>LEAK</sub>     | Input leakage current <sup>(3)</sup>     | Pull-up resis | tors disabled                                      |                        | 0.01 | 2                      | μA    |

| C <sub>IN</sub>       | Input capacitance <sup>(2)</sup>         |               |                                                    |                        | 10   |                        | pF    |

1.  $V_{VDD}$  corresponds to either  $V_{VDDIN}$  or  $V_{VDDIO}$ , depending on the supply for the pin. Refer to Section 3-5 on page 13 for details

2. These values are based on simulation. These values are not covered by test limits in production or characterization

3. These values are based on characterization. These values are not covered by test limits in production

1. These values are based on simulation. These values are not covered by test limits in production or characterization.

| Symbol              | Parameter                                   | Conditions                   | Min  | Тур | Max | Unit   |

|---------------------|---------------------------------------------|------------------------------|------|-----|-----|--------|

| N <sub>FARRAY</sub> | Array endurance (write/page)                | f <sub>CLK_AHB</sub> > 10MHz | 100k |     |     | avalaa |

| N <sub>FFUSE</sub>  | General Purpose fuses endurance (write/bit) | f <sub>CLK_AHB</sub> > 10MHz | 10k  |     |     | cycles |

| t <sub>RET</sub>    | Data retention                              |                              | 15   |     |     | years  |

Table 9-35.

Flash Endurance and Data Retention<sup>(1)</sup>

1. These values are based on simulation. These values are not covered by test limits in production or characterization.

Units V bits kHz pF kΩ LSBs LSBs mV mV dB

μs

μs V

V

V

nA

μΑ

## 9.9.5 Digital to Analog Converter Characteristics

| Symbol | Parameter                                | Conditions                                      | Min  | Тур | Max     |  |

|--------|------------------------------------------|-------------------------------------------------|------|-----|---------|--|

|        | Analog Supply Voltage (1)                | on VDDANA                                       | 2.4  | 3   | 3.6     |  |

|        | Digital Supply Voltage <sup>(1)</sup>    | on VDDCORE                                      | 1.62 | 1.8 | 1.98    |  |

|        | Resolution <sup>(2)</sup>                |                                                 |      | 10  |         |  |

|        | Clock frequency <sup>(1)</sup>           | Cload = 50pF ; Rload = $5k\Omega$               |      |     | 500     |  |

|        | L                                        | CLoad                                           |      |     | 50      |  |

|        | Load <sup>(1)</sup>                      | RLoad                                           | 5    |     |         |  |

| INL    | Integral Non Linearity (1)               | Best fit-line method                            |      |     | ±2      |  |

| DNL    | Differential Non Linearity (1)           | Best fit-line method                            | -0.9 |     | +1      |  |

|        | Zero Error (offset) <sup>(1)</sup>       | CDR[9:0] = 0                                    |      | 1   | 5       |  |

|        | Gain Error <sup>(1)</sup>                | CDR[9:0] = 1023                                 |      | 5   | 10      |  |

|        | Total Harmonic Distortion <sup>(1)</sup> | 80% of VDDANA @ fin =<br>70kHz                  | -56  |     | 7       |  |

|        | Delay to vout <sup>(1)</sup>             | CDR[9:0] = 512/ Cload = 50 pF<br>/ Rload = 5 kΩ | 2    |     |         |  |

|        | Startup time <sup>(1)</sup>              | CDR[9:0] = 512                                  | 5    |     | 9       |  |

|        | Output Voltage Range                     | (ADVREFP < VDDANA –<br>100mV) is mandatory      | 0    |     | ADVREFP |  |

|        | ADVREFP Voltage Range <sup>(1)</sup>     | (ADVREFP < VDDANA –<br>100mV) is mandatory      | 2.3  |     | 3.5     |  |

|        | ADVREFN Voltage Range <sup>(1)</sup>     | ADVREFP = GND                                   |      | 0   |         |  |

|        |                                          | On VDDANA                                       |      |     | 500     |  |

|        | Standby Current <sup>(1)</sup>           | On VDDCORE                                      |      |     | 100     |  |

|        |                                          | On VDDANA (no Rload)                            |      | 485 | 660     |  |

|        | DC Current consumption <sup>(1)</sup>    | On ADVREFP                                      |      | 250 | 295     |  |

#### Table 9-49. Operating conditions

1. These values are based on simulation. These values are not covered by test limits in production or characterization

(CDR[9:0] = 512)

2. These values are based on characterization. These values are not covered by test limits in production

#### 9.9.6 Analog Comparator Characteristics Table 9-50. Analog Comparator Characteristics

| Symbol | Parameter                    | Conditions                                                                       | Min | Тур | Мах       | Units |

|--------|------------------------------|----------------------------------------------------------------------------------|-----|-----|-----------|-------|

|        | Positive input voltage range |                                                                                  | 0.1 |     | VDDIO-0.1 | N     |

|        | Negative input voltage range |                                                                                  | 0.1 |     | VDDIO-0.1 | V     |

|        | Offset <sup>(1)</sup>        | $V_{ACREFN} = 0.1V$ to VDDIO-0.1V,<br>hysteresis = 0 <sup>(2)</sup><br>Fast mode | -12 |     | 13        | mV    |

|        | Unserv                       | $V_{ACREFN} = 0.1V$ to VDDIO-0.1V,<br>hysteresis = $0^{(2)}$<br>Low power mode   | -11 |     | 12        | mV    |

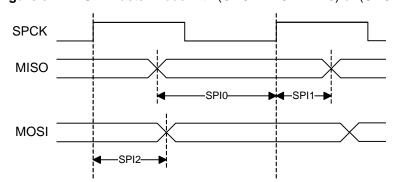

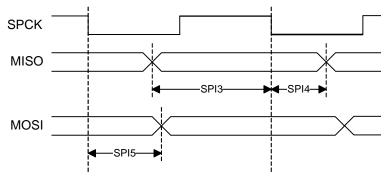

#### Maximum SPI Frequency, Master Output

The maximum SPI master output frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{PINMAX}, \frac{1}{SPIn}, \frac{f_{CLKSPI} \times 2}{9})$$

Where *SPIn* is the MOSI delay, USPI2 or USPI5 depending on CPOL and NCPHA.  $f_{PINMAX}$  is the maximum frequency of the SPI pins. refer to the I/O Pin Characteristics section for the maximum frequency of the pins.  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

#### Maximum SPI Frequency, Master Input

The maximum SPI master input frequency is given by the following formula:

USPI6-

MOSI

$$f_{SPCKMAX} = MIN(\frac{1}{SPIn + t_{VALID}}, \frac{f_{CLKSPI} \times 2}{9})$$

Where *SPIn* is the MISO setup and hold time, USPI0 + USPI1 or USPI3 + USPI4 depending on CPOL and NCPHA.  $T_{VALID}$  is the SPI slave response time. refer to the SPI slave datasheet for  $T_{VALID}$ .  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

#### 9.10.2.2 Slave mode

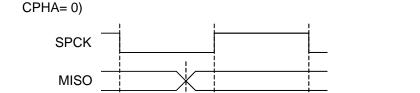

Figure 9-9.

**9-9.** USART in SPI Slave Mode with (CPOL= 0 and CPHA= 1) or (CPOL= 1 and CPHA= 0)

## 9.10.3 SPI Timing

9.10.3.1 Master mode

Figure 9-12. SPI Master Mode with (CPOL= NCPHA= 0) or (CPOL= NCPHA= 1)

| Table 9-62. | SPI Timing, Master Mode <sup>(1)</sup> |

|-------------|----------------------------------------|

|-------------|----------------------------------------|

| Symbol | Parameter                         | Conditions                  | Min | Мах | Units |

|--------|-----------------------------------|-----------------------------|-----|-----|-------|

| SPI0   | MISO setup time before SPCK rises |                             | 9   |     |       |

| SPI1   | MISO hold time after SPCK rises   | V <sub>VDDIO</sub> from     | 0   |     |       |

| SPI2   | SPCK rising to MOSI delay         | 2.85 V to 3.6 V,<br>maximum | 9   | 21  |       |

| SPI3   | MISO setup time before SPCK falls | external                    | 7.3 |     | ns    |

| SPI4   | MISO hold time after SPCK falls   | capacitor =<br>40pF         | 0   |     |       |

| SPI5   | SPCK falling to MOSI delay        |                             | 9   | 22  | 1     |

Atmel

Note: 1. These values are based on simulation. These values are not covered by test limits in production.

Maximum SPI Frequency, Master Output

## Table 9-65.JTAG Timings(1)

| Symbol | Parameter                          | Conditions              | Min  | Max  | Units |

|--------|------------------------------------|-------------------------|------|------|-------|

| JTAG0  | TCK Low Half-period                |                         | 21.8 |      |       |

| JTAG1  | TCK High Half-period               |                         | 8.6  |      |       |

| JTAG2  | TCK Period                         |                         | 30.3 |      |       |

| JTAG3  | TDI, TMS Setup before TCK High     | V <sub>VDDIO</sub> from | 2.0  |      |       |

| JTAG4  | TDI, TMS Hold after TCK High       | 3.0V to 3.6V,           | 2.3  |      |       |

| JTAG5  | TDO Hold Time                      | maximum<br>external     | 9.5  |      | ns    |

| JTAG6  | TCK Low to TDO Valid               | capacitor =             |      | 21.8 |       |

| JTAG7  | Boundary Scan Inputs Setup Time    | 40pF                    | 0.6  |      |       |

| JTAG8  | Boundary Scan Inputs Hold Time     |                         | 6.9  |      |       |

| JTAG9  | Boundary Scan Outputs Hold Time    |                         | 9.3  |      |       |

| JTAG10 | TCK to Boundary Scan Outputs Valid |                         |      | 32.2 |       |

Note: 1. These values are based on simulation. These values are not covered by test limits in production.

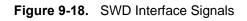

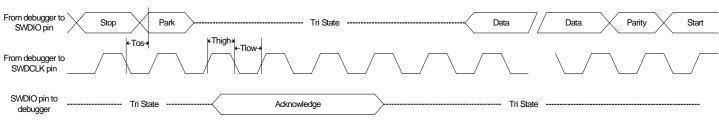

## 9.10.6 SWD Timing

## Read Cycle

## Write Cycle

Atmel

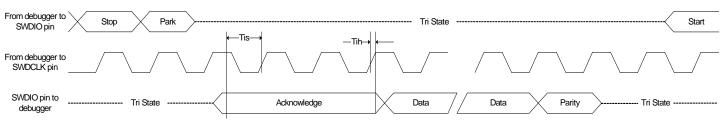

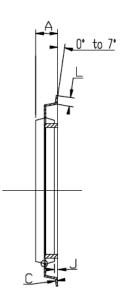

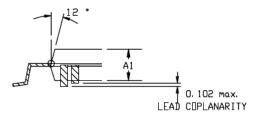

## Figure 10-7. TQFP-64 Package Drawing

## COMMON DIMENSIONS IN MM

| SYMBOL | Min   | Max   | NDTES |

|--------|-------|-------|-------|

| А      |       | 1. 20 |       |

| A1     | 0, 95 | 1. 05 |       |

| С      | 0. 09 | 0. 20 |       |

| D      | 12.0  | O BSC |       |

| D1     | 10.0  | O BSC |       |

| E      | 12.0  | O BSC |       |

| E1     | 10,0  | O BSC |       |

| J      | 0, 05 | 0.15  |       |

| L      | 0, 45 | 0, 75 |       |

| e      | 0. 5  | O BSC |       |

| f      | 0.17  | 0, 27 |       |

## Table 10-20. Device and Package Maximum Weight

| 300 | mg |

|-----|----|

|     |    |

## Table 10-21. Package Characteristics

| bisture Sensitivity Level | MSL3 |

|---------------------------|------|

|---------------------------|------|

## Table 10-22. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

# Atmel

| Table of Contents |                |     |  |  |

|-------------------|----------------|-----|--|--|

| 13.8              | Rev. H– 11/16  | 173 |  |  |

| 13.7              | Rev. G- 03/14  | 173 |  |  |

| 13.6              | Rev. F– 12/13  |     |  |  |

| 13.5              | Rev. E – 07/13 |     |  |  |

| 13.4              | Rev. D – 03/13 | 172 |  |  |

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USA Tel: (+1)(408) 441-0311 Fax: (+1)(408) 487-2600 www.atmel.com Atmel Asia Limited Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369

Atmel Munich GmbH Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY Tel: (+49) 89-31970-0 Fax: (+49) 89-3194621 Atmel Japan

16F, Shin Osaki Kangyo Bldg. 1-6-4 Osaka Shinagawa-ku Tokyo 104-0032 JAPAN Tel: (+81) 3-6417-0300 Fax: (+81) 3-6417-0370

#### © 2013 Atmel Corporation. All rights reserved.

Atmel<sup>®</sup>, Atmel logo and combinations thereof, picoPower<sup>®</sup>, Adjacent Key Suppression<sup>®</sup>, AKS<sup>®</sup>, Qtouch<sup>®</sup>, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. ARM<sup>®</sup>, AMBA<sup>®</sup>, Thumb<sup>®</sup>, Cortex<sup>™</sup> are registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROF-ITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suit-able for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.