#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 48                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.68V ~ 3.6V                                                             |

| Data Converters            | A/D 7x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 64-QFN (9x9)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4ls8ba-mu |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

ATSAM4L8/L4/L2

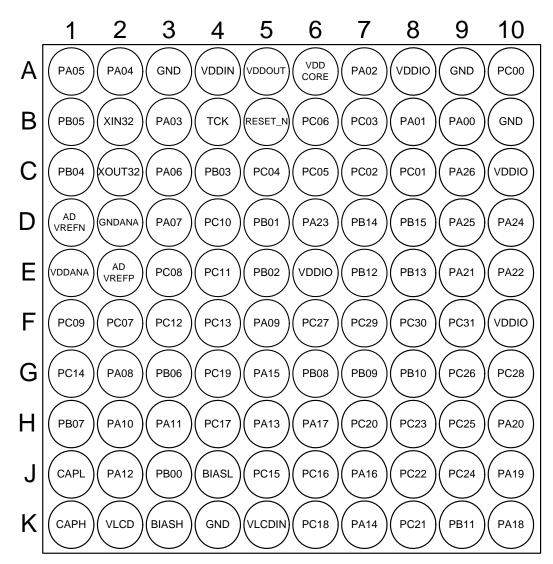

Figure 3-2. ATSAM4LC VFBGA100 Pinout

- Atmel

10

# 3.2 Peripheral Multiplexing on I/O lines

# 3.2.1 Multiplexed Signals

Each GPIO line can be assigned to one of the peripheral functions. The following tables (Section 3-1 "100-pin GPIO Controller Function Multiplexing" on page 19 to Section 3-4 "48-pin GPIO Controller Function Multiplexing" on page 28) describes the peripheral signals multiplexed to the GPIO lines.

Peripheral functions that are not relevant in some parts of the family are grey-shaded.

For description of differents Supply voltage source, refer to the Section 6. "Power and Startup Considerations" on page 46.

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 1 of 4)

| lable | •          |     |            | 0 0011 | 101101 | i unotion | manupiox       | ng (Oneer     | 1 01 1)          |                 |                   |                |                 |

|-------|------------|-----|------------|--------|--------|-----------|----------------|---------------|------------------|-----------------|-------------------|----------------|-----------------|

|       | ATSAM4LC   |     | ATSAM4LS   | Pin    | GPIO   | Supply    | GPIO Functions |               |                  |                 |                   |                |                 |

| QFN   | VFBGA      | QFN | VFBGA      |        |        |           | Α              | В             | С                | D               | E                 | F              | G               |

| 5     | B9         | 5   | B9         | PA00   | 0      | VDDIO     |                |               |                  |                 |                   |                |                 |

| 6     | B8         | 6   | B8         | PA01   | 1      | VDDIO     |                |               |                  |                 |                   |                |                 |

| 12    | A7         | 12  | A7         | PA02   | 2      | VDDIN     | SCIF<br>GCLK0  | SPI<br>NPCS0  |                  |                 |                   |                | CATB<br>DIS     |

| 19    | В3         | 19  | В3         | PA03   | 3      | VDDIN     |                | SPI<br>MISO   |                  |                 |                   |                |                 |

| 24    | A2         | 24  | A2         | PA04   | 4      | VDDANA    | ADCIFE<br>AD0  | USART0<br>CLK | EIC<br>EXTINT2   | GLOC<br>IN1     |                   |                | CATB<br>SENSE0  |

| 25    | A1         | 25  | A1         | PA05   | 5      | VDDANA    | ADCIFE<br>AD1  | USART0<br>RXD | EIC<br>EXTINT3   | GLOC<br>IN2     | ADCIFE<br>TRIGGER |                | CATB<br>SENSE1  |

| 30    | C3         | 30  | C3         | PA06   | 6      | VDDANA    | DACC<br>VOUT   | USART0<br>RTS | EIC<br>EXTINT1   | GLOC<br>IN0     | ACIFC<br>ACAN0    |                | CATB<br>SENSE2  |

| 31    | D3         | 31  | D3         | PA07   | 7      | VDDANA    | ADCIFE<br>AD2  | USART0<br>TXD | EIC<br>EXTINT4   | GLOC<br>IN3     | ACIFC<br>ACAP0    |                | CATB<br>SENSE3  |

| 44    | G2         | 44  | G2         | PA08   | 8      | LCDA      | USART0<br>RTS  | TC0<br>A0     | PEVC<br>PAD EVT0 | GLOC<br>OUT0    |                   | LCDCA<br>SEG23 | CATB<br>SENSE4  |

| 47    | F5         | 47  | F5         | PA09   | 9      | LCDA      | USART0<br>CTS  | ТС0<br>В0     | PEVC<br>PAD EVT1 | PARC<br>PCDATA0 |                   | LCDCA<br>COM3  | CATB<br>SENSE5  |

| 48    | H2         | 48  | H2         | PA10   | 10     | LCDA      | USART0<br>CLK  | TC0<br>A1     | PEVC<br>PAD EVT2 | PARC<br>PCDATA1 |                   | LCDCA<br>COM2  | CATB<br>SENSE6  |

| 49    | H3         | 49  | H3         | PA11   | 11     | LCDA      | USART0<br>RXD  | TC0<br>B1     | PEVC<br>PAD EVT3 | PARC<br>PCDATA2 |                   | LCDCA<br>COM1  | CATB<br>SENSE7  |

| 50    | J2         | 50  | J2         | PA12   | 12     | LCDA      | USART0<br>TXD  | TC0<br>A2     |                  | PARC<br>PCDATA3 |                   | LCDCA<br>COM0  | CATB<br>DIS     |

| 63    | H5         | 63  | H5         | PA13   | 13     | LCDA      | USART1<br>RTS  | TC0<br>B2     | SPI<br>NPCS1     | PARC<br>PCDATA4 |                   | LCDCA<br>SEG5  | CATB<br>SENSE8  |

| 64    | <b>K</b> 7 | 64  | <b>K</b> 7 | PA14   | 14     | LCDA      | USART1<br>CLK  | TC0<br>CLK0   | SPI<br>NPCS2     | PARC<br>PCDATA5 |                   | LCDCA<br>SEG6  | CATB<br>SENSE9  |

| 65    | G5         | 65  | G5         | PA15   | 15     | LCDA      | USART1<br>RXD  | TC0<br>CLK1   | SPI<br>NPCS3     | PARC<br>PCDATA6 |                   | LCDCA<br>SEG7  | CATB<br>SENSE10 |

### **Table 3-8.**Signal Descriptions List (Sheet 4 of 4)

| Signal Name | Function                           | Туре | Active<br>Level | Comments |

|-------------|------------------------------------|------|-----------------|----------|

| PA31 - PA00 | Parallel I/O Controller I/O Port A | I/O  |                 |          |

| PB15 - PB00 | Parallel I/O Controller I/O Port B | I/O  |                 |          |

| PC31 - PC00 | Parallel I/O Controller I/O Port C | I/O  |                 |          |

Note: 1. See "Power and Startup Considerations" section.

# 3.4 I/O Line Considerations

### 3.4.1 SW/JTAG Pins

The JTAG pins switch to the JTAG functions if a rising edge is detected on TCK low after the RESET\_N pin has been released. The TMS, and TDI pins have pull-up resistors when used as JTAG pins. The TCK pin always has pull-up enabled during reset. The JTAG pins can be used as GPIO pins and multiplexed with peripherals when the JTAG is disabled. Refer to Section 3.2.3 "JTAG Port Connections" on page 29 for the JTAG port connections.

For more details, refer to Section 1.1 "Enhanced Debug Port (EDP)" on page 3.

# 3.4.2 RESET\_N Pin

The RESET\_N pin is a schmitt input and integrates a permanent pull-up resistor to VDDIN. As the product integrates a power-on reset detector, the RESET\_N pin can be left unconnected in case no reset from the system needs to be applied to the product.

### 3.4.3 TWI Pins

When these pins are used for TWI, the pins are open-drain outputs with slew-rate limitation andinputs with inputs with spike-filtering. When used as GPIO-pins or used for other peripherals, the pins have the same characteristics as GPIO pins.

### 3.4.4 GPIO Pins

All the I/O lines integrate a pull-up/pull-down resistor and slew rate controller. Programming these features is performed independently for each I/O line through the GPIO Controllers. After reset, I/O lines default as inputs with pull-up and pull-down resistors disabled and slew rate enabled.

### 3.4.5 High-drive Pins

The six pins PA02, PB00, PB01, PC04, PC05 and PC06 have high-drive output capabilities. Refer to Section 9.6.2 "High-drive I/O Pin : PA02, PC04, PC05, PC06" on page 115 for electrical characteristics.

#### 3.4.6 USB Pins

When these pins are used for USB, the pins are behaving according to the USB specification. When used as GPIO pins or used for other peripherals, the pins have the same behavior as other normal I/O pins, but the characteristics are different. Refer to Section 9.6.3 "USB I/O Pin : PA25, PA26" on page 116 for electrical characteristics.

These pins are compliant to USB standard only when VDDIO power supply is 3.3V nominal.

# 3.4.7 ADC Input Pins

These pins are regular I/O pins powered from the VDDANA.

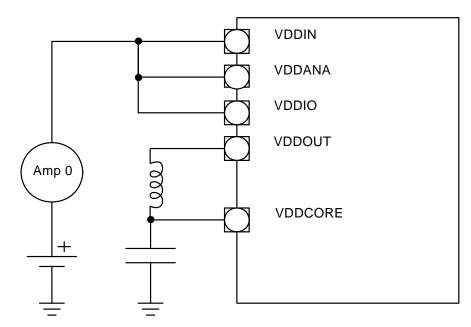

# 6.2 Power Supplies

The ATSAM4L8/L4/L2 has several types of power supply pins:

- VDDIO: Powers I/O lines, the general purpose oscillator (OSC), the 80MHz integrated RC oscillator (RC80M). Voltage is 1.68V to 3.6V.

- VLCDIN: (ATSAM4LC only) Powers the LCD voltage pump. Voltage is 1.68V to 3.6V.

- VDDIN: Powers the internal voltage regulator. Voltage is 1.68V to 3.6V.

- VDDANA: Powers the ADC, the DAC, the Analog Comparators, the 32kHz oscillator (OSC32K), the 32kHz integrated RC oscillator (RC32K) and the Brown-out detectors (BOD18 and BOD33). Voltage is 1.68V to 3.6V nominal.

- VDDCORE: Powers the core, memories, peripherals, the PLL, the DFLL, the 4MHz integrated RC oscillator (RCFAST) and the 115kHz integrated RC oscillator (RCSYS).

- VDDOUT is the output voltage of the regulator and must be connected with or without an inductor to VDDCORE.

The ground pins GND are common to VDDCORE, VDDIO, and VDDIN. The ground pin for VDDANA is GNDANA.

For decoupling recommendations for the different power supplies, refer to the schematic document.

### 6.2.1 Voltage Regulator

An embedded voltage regulator supplies all the digital logic in the Core and the Backup power domains.

The regulator has two functionnal mode depending of BUCK/LDOn (PA02) pin value. When this pin is low, the regulator is in linear mode and VDDOUT must be connected to VDDCORE externally. When this pin is high, it behaves as a switching regulator and an inductor must be placed between VDDOUT and VDDCORE. The value of this pin is sampled during the power-up phase when the Power On Reset 33 reaches  $V_{POT+}$  (Section 9.9 "Analog Characteristics" on page 129)

Its output voltages in the Core domain ( $V_{CORE}$ ) and in the Backup domain ( $V_{BKUP}$ ) are always equal except in Backup mode where the Core domain is not powered ( $V_{CORE}$ =0). The Backup domain is always powered. The voltage regulator features three different modes:

- Normal mode: the regulator is configured as linear or switching regulator. It can support all different Run and Sleep modes.

- Low Power (LP) mode: the regulator consumes little static current. It can be used in Wait modes.

- Ultra Low Power (ULP) mode: the regulator consumes very little static current. It is dedicated to Retention and Backup modes. In Backup mode, the regulator only supplies the backup domain.

At power-up or after a reset, the ATSAM4L8/L4/L2 is in the RUN0 mode. Only the necessary clocks are enabled allowing software execution. The Power Manager (PM) can be used to adjust the clock frequencies and to enable and disable the peripheral clocks.

When the CPU is entering a Power Save Mode, the CPU stops executing code. The user can choose between four Power Save Modes to optimize power consumption:

- SLEEP mode: the Cortex-M4 core is stopped, optionally some clocks are stopped, peripherals are kept running if enabled by the user.

- WAIT mode: all clock sources are stopped, the core and all the peripherals are stopped except the modules running with the 32kHz clock if enabled. This is the lowest power configuration where SleepWalking is supported.

- RETENTION mode: similar to the WAIT mode in terms of clock activity. This is the lowest power configuration where the logic is retained.

- BACKUP mode: the Core domain is powered off, the Backup domain is kept powered.

A wake up source exits the system to the RUN mode from which the Power Save Mode was entered.

A reset source always exits the system from the Power Save Mode to the RUN0 mode.

The configuration of the I/O lines are maintained in all Power Save Modes. Refer to Section 9. "Backup Power Manager (BPM)" on page 677.

### 7.1.1 SLEEP mode

The SLEEP mode allows power optimization with the fastest wake up time.

The CPU is stopped. To further reduce power consumption, the user can switch off modulesclocks and synchronous clock sources through the BPM.PMCON.SLEEP field (See Table 7-1). The required modules will be halted regardless of the bit settings of the mask registers in the Power Manager (PM.AHBMASK, PM.APBxMASK).

| BPM.PSAVE.SLEEP | CPU<br>clock | AHB<br>clocks | APB clocks<br>GCLK | Clock sources:<br>OSC, RCFAST,<br>RC80M, PLL,<br>DFLL | RCSYS | OSC32K<br>RC32K <sup>(2)</sup> | Wake up Sources              |

|-----------------|--------------|---------------|--------------------|-------------------------------------------------------|-------|--------------------------------|------------------------------|

| 0               | Stop         | Run           | Run                | Run                                                   | Run   | Run                            | Any interrupt                |

| 1               | Stop         | Stop          | Run                | Run                                                   | Run   | Run                            | Any interrupt <sup>(1)</sup> |

| 2               | Stop         | Stop          | Stop               | Run                                                   | Run   | Run                            | Any interrupt <sup>(1)</sup> |

| 3               | Stop         | Stop          | Stop               | Stop                                                  | Run   | Run                            | Any interrupt <sup>(1)</sup> |

Table 7-1.

SLEEP mode Configuration

Notes: 1. from modules with clock running.

2. OSC32K and RC32K will only remain operational if pre-enabled.

### 7.1.1.1 Entering SLEEP mode

The SLEEP mode is entered by executing the WFI instruction.

Atmel

Additionally, if the SLEEPONEXIT bit in the Cortex-M4 System Control Register (SCR) is set, the SLEEP mode will also be entered when the Cortex-M4 exits the lowest priority ISR. This

# 7.1.4 Wakeup Time

7.1.4.1 Wakeup Time From SLEEP Mode

The latency depends on the clock sources wake up time. If the clock sources are not stopped, there is no latency to wake the clocks up.

7.1.4.2 Wakeup Time From WAIT or RETENTION Mode

The wake up latency consists of:

- the switching time from the low power configuration to the RUN mode power configuration. By default, the switching time is completed when all the voltage regulation system is ready. To speed-up the startup time, the user can set the Fast Wakeup bit in BPM.PMCON register.

- the wake up time of the RC oscillator used to start the system up. By default, the RCSYS oscillator is used to startup the system. The user can use another clock source (RCFAST for example) to speed up the startup time by configuring the PM.FASTWKUP register. Refer to Section 9. "Power Manager (PM)" on page 677.

- the Flash memory wake up time.

To have the shortest wakeup time, the user should:

Atmel

- set the BPM.PMCON.FASTWKUP bit.

- configure the PM.FASTSLEEP.FASTRCOSC field to use the RCFAST main clock.

- enter the WAIT or RETENTION mode

Upon a wakeup, this is required to keep the main clock connected to RCFAST until the voltage regulation system is fully ready (when BPM.ISR.PSOK bit is one). During this wakeup period, the FLASHCALW module is automatically configured to operate in "1 wait state mode".

### 7.1.4.3 Wake time from BACKUP mode

It is equal to the Core domain logic reset latency (similar to the reset latency caused by an external reset in RESET\_N pin) added to the time required for the voltage regulation system to be stabilized.

### 8.9.9 Unlimited Flash User Page Read Access

The SMAP can access the User page even if the protected state is set. Prior to operate such an access, the user should check that the module is not busy by checking that SR.STATE is equal to zerp. Once the offset of the word to access inside the page is written in ADDR.ADDR, the read operation can be initiated by writing a one in CR.FSPR. The SR.STATE field will indicate the FSPR state. Addresses written to ADDR.ADDR must be world aligned. Failing to do so will result in unpredictable behavior. The result can be read in the DATA register as soon as SR.DONE rises. The ADDR field is used as an offset in the page, bits outside a page boundary will be silently discarded. The ADDR register is automatically incremented at the end of the read operation making possible to dump consecutive words without writing the next offset into ADDR.ADDR.

### 8.9.10 32-bit Cyclic Redundancy Check (CRC)

The SMAP unit provides support for calculating a Cyclic Redundancy Check (CRC) value for a memory area. The algorithm used is the industry standard CRC32 algorithm using the generator polynomial 0xEDB88320.

# 8.9.10.1 Starting CRC Calculation

To calculate CRC for a memory range, the start address must be written into the ADDR register, and the size of the memory range into the LENGTH register. Both the start address and the length must be word aligned.

The initial value used for the CRC calculation must be written to the DATA register. This value will usually be 0xFFFFFFF, but can be e.g. the result of a previous CRC calculation if generating a common CRC of separate memory blocks.

Once completed, the calculated CRC value can be read out of the DATA register. The read value must be inverted to match standard CRC32 implementations, or kept non-inverted if used as starting point for subsequent CRC calculations.

If the device is in protected state, it is only possible to calculate the CRC of the whole flash array. In most cases this area will be the entire onboard nonvolatile memory. The ADDR, LENGTH, and DATA registers will be forced to predefined values once the CRC operation is started, and user-written values are ignored. This allows the user to verify the contents of a protected device.

The actual test is started by writing a one in CR.CRC. A running CRC operation can be cancelled by disabling the module (write a one in CR.DIS). This has the effect of resetting the module. The module has to be restarted by issuing an enable command (write a one in CR.EN).

### 8.9.10.2 Interpreting the Results

The user should monitor the SR register (Refer to Section 8.9.11.2 "Status Register" on page 83). When the operation is completed SR.DONE is set. Then the SR.BERR and SR.FAIL must be read to ensure that no bus error nor functional error occured.

| 8.9.11.3   | Status | Clear Register |

|------------|--------|----------------|

| Name:      |        | SCR            |

| Access Ty  | pe:    | Write-Only     |

| Offset:    |        | 0x08           |

| Reset Valu | ie:    | 0x00000000     |

| 31 | 30 | 29 | 28  | 27   | 26   | 25  | 24   |

|----|----|----|-----|------|------|-----|------|

| -  | -  | -  | -   | -    | -    | -   | -    |

|    |    |    |     |      |      |     |      |

| 23 | 22 | 21 | 20  | 19   | 18   | 17  | 16   |

| -  | -  | -  | -   | -    | -    | -   | -    |

|    |    |    |     |      |      |     |      |

| 15 | 14 | 13 | 12  | 11   | 10   | 9   | 8    |

| -  | -  | -  | -   | -    | -    | -   | -    |

|    |    |    |     |      |      |     |      |

| 7  | 6  | 5  | 4   | 3    | 2    | 1   | 0    |

| -  | -  | -  | LCK | FAIL | BERR | HCR | DONE |

Writing a zero to a bit in this register has no effect. Writing a one to a bit clears the corresponding SR bit

Note: Writing a one to bit HCR while the chip is in protected state has no effect

# **Table 9-3.**Supply Rise Rates and Order <sup>(1)</sup>

VDDIO, VDDIN and VDDANA must be connected together and as a consequence, rise synchronously

|                     |                                                  | Rise Rate |     |      |         |  |

|---------------------|--------------------------------------------------|-----------|-----|------|---------|--|

| Symbol              | Parameter                                        | Min       | Max | Unit | Comment |  |

| V <sub>VDDIO</sub>  | DC supply peripheral I/Os                        | 0.0001    | 2.5 | V/µs |         |  |

| V <sub>VDDIN</sub>  | DC supply peripheral I/Os and internal regulator | 0.0001    | 2.5 | V/µs |         |  |

| V <sub>VDDANA</sub> | Analog supply voltage                            | 0.0001    | 2.5 | V/µs |         |  |

1. These values are based on characterization. These values are not covered by test limits in production.

# ATSAM4L8/L4/L2

# 9.5 Power Consumption

# 9.5.1 Power Scaling 0 and 2

The values in Table 9-6 are measured values of power consumption under the following conditions, except where noted:

- Operating conditions for power scaling mode 0 and 2

- $-V_{VDDIN} = 3.3V$

- Power Scaling mode 0 is used for CPU frequencies under 36MHz

- Power Scaling mode 2 is used for CPU frequencies above 36MHz

- Wake up time from low power modes is measured from the edge of the wakeup signal to the first instruction fetched in flash.

- Oscillators

- OSC0 (crystal oscillator) stopped

- OSC32K (32kHz crystal oscillator) running with external 32kHz crystal

- DFLL using OSC32K as reference and running at 48MHz

- Clocks

- DFLL used as main clock source

- CPU, AHB clocks undivided

- APBC and APBD clocks divided by 4

- APBA and APBB bridges off

- The following peripheral clocks running

- PM, SCIF, AST, FLASHCALW, APBC and APBD bridges

- All other peripheral clocks stopped

- I/Os are inactive with internal pull-up

- CPU is running on flash with 1 wait state

- Low power cache enabled

- BOD18 and BOD33 disabled

# Table 9-6. ATSAM4L4/2 Current consumption and Wakeup time for power scaling mode 0 and 2

| Mode | Conditions                        | T <sub>A</sub> | Typical<br>Wakeup Time | Тур | Max <sup>(1)</sup> | Unit   |

|------|-----------------------------------|----------------|------------------------|-----|--------------------|--------|

|      | CPU running a Fibonacci algorithm | 25°C           | N/A                    | 296 | 326                |        |

|      | Linear mode                       | 85°C           | N/A                    | 300 | 332                |        |

|      | CPU running a CoreMark algorithm  | 25°C           | N/A                    | 320 | 377                |        |

|      | Linear mode                       | 85°C           |                        | 326 | 380                |        |

| RUN  | CPU running a Fibonacci algorithm | 25°C           | N/A                    | 177 | 198                | µA/MHz |

|      | Switching mode                    | 85°C           |                        | 179 | 200                | -      |

|      | CPU running a CoreMark algorithm  | 25°C           | N/A                    | 186 | 232                | -      |

|      | Switching mode                    | 85°C           |                        | 195 | 239                |        |

| Mode             | Conditions                                    | T <sub>A</sub>                   | Typical<br>Wakeup Time | Тур  | Max <sup>(1)</sup> | Unit |

|------------------|-----------------------------------------------|----------------------------------|------------------------|------|--------------------|------|

|                  | Quuitabing mode                               | 25°C                             | 9 * Main clock         | 3817 | 4033               |      |

| SLEEP0           | Switching mode                                | 85°C                             | cycles                 | 4050 | 4507               |      |

|                  | Quitabing mode                                | 25°C                             | 9 * Main clock         | 2341 | 2477               |      |

|                  | Switching mode                                | 85°C                             | cycles + 500ns         | 2525 | 2832               |      |

| SLEEP2<br>SLEEP3 | Switching mode                                | 25°C                             | 9 * Main clock         | 1758 | 1862               |      |

|                  | Switching mode                                | 85°C                             | cycles + 500ns         | 1925 | 1971               |      |

| SLEEP3           | Linear mode                                   |                                  |                        | 51   | 60                 |      |

|                  | OSC32K and AST running<br>Fast wake-up enable |                                  |                        | 6.7  |                    | μΑ   |

| WAIT             | OSC32K and AST stopped<br>Fast wake-up enable | running<br>ble<br>stopped<br>ble | 5.5                    |      |                    |      |

| RETENTION        | OSC32K running<br>AST running at 1kHz         | 25°C                             | 1.5µs                  | 3.9  |                    |      |

|                  | AST and OSC32K stopped                        |                                  |                        | 3.0  |                    |      |

| BACKUP           | OSC32K running<br>AST running at 1 kHz        |                                  |                        | 1.5  | 3.1                |      |

|                  | AST and OSC32K stopped                        |                                  |                        | 0.9  | 1.7                |      |

Table 9-7.

ATSAM4L8 Current consumption and Wakeup time for power scaling mode 0 and 2

1. These values are based on characterization. These values are not covered by test limits in production.

# 9.5.2 Power Scaling 1

The values in Table 34-7 are measured values of power consumption under the following conditions, except where noted:

Operating conditions for power scaling mode 1

$-V_{VDDIN} = 3.3V$

- Wake up time from low power modes is measured from the edge of the wakeup signal to the first instruction fetched in flash.

- Oscillators

- OSC0 (crystal oscillator) and OSC32K (32kHz crystal oscillator) stopped

- RCFAST Running at 12MHz

- Clocks

- RCFAST used as main clock source

- CPU, AHB clocks undivided

- APBC and APBD clocks divided by 4

- APBA and APBB bridges off

- The following peripheral clocks running

- PM, SCIF, AST, FLASHCALW, APBC and APBD bridges

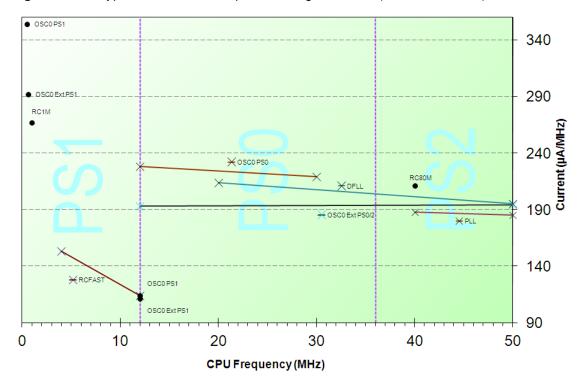

Figure 9-1. Typical Power Consumption running Coremark (from above table)

Note: For variable frequency oscillators, linear interpolation between high and low settings

Figure 9-2. Measurement Schematic, Switching Mode

# ATSAM4L8/L4/L2

# 9.6 I/O Pin Characteristics

# 9.6.1 Normal I/O Pin

Table 9-13.

Normal I/O Pin Characteristics <sup>(1)</sup>

| Symbol                | Parameter                                | Conditions |                                                   | Min                    | Тур                                                                                                                                                                                                                                                                                                                           | Max                                                                               | Units |

|-----------------------|------------------------------------------|------------|---------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------|

| R <sub>PULLUP</sub>   | Pull-up resistance (2)                   |            |                                                   |                        | 40                                                                                                                                                                                                                                                                                                                            |                                                                                   | kΩ    |

| R <sub>PULLDOWN</sub> | Pull-down resistance <sup>(2)</sup>      |            |                                                   |                        | 40                                                                                                                                                                                                                                                                                                                            |                                                                                   | kΩ    |

| V <sub>IL</sub>       | Input low-level voltage                  |            |                                                   | -0.3                   |                                                                                                                                                                                                                                                                                                                               | 0.2 * V <sub>VDD</sub>                                                            |       |

| V <sub>IH</sub>       | Input high-level voltage                 |            |                                                   | 0.8 * V <sub>VDD</sub> |                                                                                                                                                                                                                                                                                                                               | V <sub>VDD</sub> + 0.3                                                            | M     |

| V <sub>OL</sub>       | Output low-level voltage                 |            |                                                   |                        |                                                                                                                                                                                                                                                                                                                               | 0.4                                                                               | V     |

| V <sub>OH</sub>       | Output high-level voltage                |            |                                                   | V <sub>VDD</sub> - 0.4 |                                                                                                                                                                                                                                                                                                                               |                                                                                   | •     |

|                       |                                          |            | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                  |                        |                                                                                                                                                                                                                                                                                                                               | 0.8                                                                               | 0     |

|                       | Quite at least least 1 and 1 (3)         | ODCR0=0    | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                   |                        |                                                                                                                                                                                                                                                                                                                               | 1.6                                                                               | mA    |

| I <sub>OL</sub>       | Output low-level current <sup>(3)</sup>  | 00000 4    | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                  |                        |                                                                                                                                                                                                                                                                                                                               | 1.6                                                                               |       |

|                       |                                          | ODCR0=1    | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                   |                        | 40         40 $0.2 * V_{VDD}$ $V_{VDD} + 0.3$ $0.4$ $0.4$ $0.4$ $0.8$ $1.6$ $3.2$ $0.8$ $1.6$ $3.2$ $0.8$ $1.6$ $3.2$ $0.8$ $1.6$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $3.2$ $2.3$ $4.45$ $1.7$ $2.24$ $1.7$ $1.5$ $2.7$ $2.3$ | mA                                                                                |       |

|                       |                                          |            | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                  |                        |                                                                                                                                                                                                                                                                                                                               | 0.8                                                                               |       |

|                       | Outrast bisk laurel summer (3)           | ODCR0=0    | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                   |                        |                                                                                                                                                                                                                                                                                                                               | 1.6                                                                               | mA    |

| I <sub>ОН</sub>       | Output high-level current <sup>(3)</sup> | ODCR0=1    | 1.68V <v<sub>VDD&lt;2.7V</v<sub>                  |                        |                                                                                                                                                                                                                                                                                                                               | 1.6                                                                               | mA    |

|                       |                                          | ODCR0=1    | 2.7V <v<sub>VDD&lt;3.6V</v<sub>                   |                        |                                                                                                                                                                                                                                                                                                                               | 3.2                                                                               |       |

|                       | Rise time <sup>(2)</sup>                 | OSRR0=0    | ODCR0=0                                           |                        |                                                                                                                                                                                                                                                                                                                               | 35                                                                                |       |

|                       |                                          | OSRR0=1    | 1.68V <v<sub>VDD&lt;2.7V,<br/>load = 25pF</v<sub> |                        |                                                                                                                                                                                                                                                                                                                               | 45                                                                                | ns    |

| t <sub>RISE</sub>     |                                          | OSRR0=0    | ODCR0=0                                           |                        |                                                                                                                                                                                                                                                                                                                               | 19                                                                                |       |

|                       |                                          | OSRR0=1    | 2.7V <v<sub>VDD&lt;3.6V,<br/>load = 25pF</v<sub>  |                        |                                                                                                                                                                                                                                                                                                                               | 23                                                                                | ns    |

|                       |                                          | OSRR0=0    | ODCR0=0                                           |                        |                                                                                                                                                                                                                                                                                                                               | 1.6         3.2         35         45         19         23         36         47 |       |

|                       | Fall time <sup>(2)</sup>                 | OSRR0=1    | 1.68V <v<sub>VDD&lt;2.7V,<br/>load = 25pF</v<sub> |                        |                                                                                                                                                                                                                                                                                                                               | 47                                                                                | ns    |

| t <sub>FALL</sub>     |                                          | OSRR0=0    | ODCR0=0                                           |                        |                                                                                                                                                                                                                                                                                                                               | 20                                                                                |       |

|                       |                                          | OSRR0=1    | 2.7V <v<sub>VDD&lt;3.6V,<br/>load = 25pF</v<sub>  |                        |                                                                                                                                                                                                                                                                                                                               | 24                                                                                | ns    |

|                       |                                          | OSRR0=0    | ODCR0=0, V <sub>VDD</sub> >2.7V                   |                        |                                                                                                                                                                                                                                                                                                                               | 17                                                                                | MHz   |

| -                     | Output frequency (2)                     | OSRR0=1    | load = 25pF                                       |                        |                                                                                                                                                                                                                                                                                                                               | 15                                                                                | MHz   |

| F <sub>PINMAX</sub>   | Output frequency <sup>(2)</sup>          | OSRR0=0    | ODCR0=1, V <sub>VDD</sub> >2.7V                   |                        |                                                                                                                                                                                                                                                                                                                               | 27                                                                                | MHz   |

|                       |                                          | OSRR0=1    | load = 25pF                                       |                        |                                                                                                                                                                                                                                                                                                                               | 23                                                                                | MHz   |

| I <sub>LEAK</sub>     | Input leakage current <sup>(3)</sup>     |            | Pull-up resistors disabled                        |                        | 0.01                                                                                                                                                                                                                                                                                                                          | 1                                                                                 | μA    |

| C <sub>IN</sub>       | Input capacitance <sup>(2)</sup>         |            |                                                   |                        | 5                                                                                                                                                                                                                                                                                                                             |                                                                                   | pF    |

1. V<sub>VDD</sub> corresponds to either V<sub>VDDIN</sub> or V<sub>VDDIO</sub>, depending on the supply for the pin. Refer to Section 3-5 on page 13 for details

2. These values are based on simulation. These values are not covered by test limits in production or characterization

# 9.7 Oscillator Characteristics

# 9.7.1 Oscillator 0 (OSC0) Characteristics

### 9.7.1.1 Digital Clock Characteristics

The following table describes the characteristics for the oscillator when a digital clock is applied on XIN.

### Table 9-22. Digital Clock Characteristics

| Symbol               | Parameter                           | Conditions | Min | Тур | Max | Units  |

|----------------------|-------------------------------------|------------|-----|-----|-----|--------|

| f <sub>CPXIN</sub>   | XIN clock frequency (1)             |            |     |     | 50  | MHz    |

| t <sub>CPXIN</sub>   | XIN clock duty cycle <sup>(1)</sup> |            | 40  |     | 60  | %      |

| t <sub>STARTUP</sub> | Startup time                        |            |     | N/A |     | cycles |

1. These values are based on simulation. These values are not covered by test limits in production or characterization.

# 9.7.1.2 Crystal Oscillator Characteristics

The following table describes the characteristics for the oscillator when a crystal is connected between XIN and XOUT as shown in Figure 9-3. The user must choose a crystal oscillator where the crystal load capacitance  $C_L$  is within the range given in the table. The exact value of  $C_L$  can be found in the crystal datasheet. The capacitance of the external capacitors ( $C_{LEXT}$ ) can then be computed as follows:

$$C_{LEXT} = 2(C_{L} - C_{STRAY} - C_{SHUNT})$$

where  $C_{STRAY}$  is the capacitance of the pins and PCB,  $C_{SHUNT}$  is the shunt capacitance of the crystal.

| Symbol           | Parameter                                | Conditions                                                     | Min | Тур | Max   | Unit |

|------------------|------------------------------------------|----------------------------------------------------------------|-----|-----|-------|------|

| f <sub>OUT</sub> | Crystal oscillator frequency (1)         |                                                                | 0.6 |     | 30    | MHz  |

|                  |                                          | $f = 0.455 MHz$ , $C_{LEXT} = 100 pF$<br>SCIF.OSCCTRL.GAIN = 0 |     |     | 17000 |      |

|                  |                                          | f = 2MHz, C <sub>LEXT</sub> = 20pF<br>SCIF.OSCCTRL.GAIN = 0    |     |     | 2000  |      |

| ESR              | Crystal Equivalent Series Resistance (2) | f = 4MHz, C <sub>LEXT</sub> = 20pF<br>SCIF.OSCCTRL.GAIN = 1    |     |     | 1500  | Ω    |

| ESK              |                                          | f = 8MHz, C <sub>LEXT</sub> = 20pF<br>SCIF.OSCCTRL.GAIN = 2    |     |     | 300   | 52   |

|                  |                                          | f = 16MHz, C <sub>LEXT</sub> = 20pF<br>SCIF.OSCCTRL.GAIN = 3   |     |     | 350   |      |

|                  |                                          | f = 30MHz, C <sub>LEXT</sub> = 18pF<br>SCIF.OSCCTRL.GAIN = 4   |     |     | 45    |      |

| Table 9-23. | Crystal Oscillator Characteristics |

|-------------|------------------------------------|

|             |                                    |

# 9.7.7 1MHz RC Oscillator (RC1M) Characteristics

| Table 9-30. | RC1M | Oscillator | Characteristics |

|-------------|------|------------|-----------------|

|             |      | Oscillator | Characteristics |

| Symbol            | Parameter                 | Conditions | Min  | Тур  | Max  | Unit |

|-------------------|---------------------------|------------|------|------|------|------|

| f <sub>OUT</sub>  | Output frequency (1)      |            | 0.91 | 1    | 1.12 | MHz  |

| I <sub>RC1M</sub> | Current consumption (2)   |            |      | 35   |      | μA   |

| Duty              | Duty cycle <sup>(1)</sup> |            | 48.6 | 49.9 | 54.4 | %    |

1. These values are based on characterization. These values are not covered by test limits in production.

2. These values are based on simulation. These values are not covered by test limits in production or characterization.

# 9.7.8 4/8/12MHz RC Oscillator (RCFAST) Characteristics

### Table 9-31. RCFAST Oscillator Characteristics

| Symbol               | Parameter                          | Conditions           | Min  | Тур  | Max  | Unit |  |

|----------------------|------------------------------------|----------------------|------|------|------|------|--|

| f <sub>оит</sub>     |                                    | Calibrated, FRANGE=0 | 4    | 4.3  | 4.6  |      |  |

|                      | Output frequency (1)               | Calibrated, FRANGE=1 | 7.8  | 8.2  | 8.5  | MHz  |  |

|                      |                                    | Calibrated, FRANGE=2 | 11.3 | 12   | 12.3 |      |  |

| I <sub>RCFAST</sub>  | Current consumption <sup>(2)</sup> | Calibrated, FRANGE=0 |      | 90   | 110  | μΑ   |  |

|                      |                                    | Calibrated, FRANGE=1 |      | 130  | 150  |      |  |

|                      |                                    | Calibrated, FRANGE=2 |      | 180  | 205  |      |  |

|                      | Duty cycle <sup>(1)</sup>          | Calibrated, FRANGE=0 | 48.8 | 49.6 | 50.1 |      |  |

| Duty                 |                                    | Calibrated, FRANGE=1 | 47.8 | 49.2 | 50.1 | %    |  |

|                      |                                    | Calibrated, FRANGE=2 | 46.7 | 48.8 | 50.0 |      |  |

| t <sub>STARTUP</sub> | Startup time <sup>(1)</sup>        | Calibrated, FRANGE=2 | 0.1  | 0.31 | 0.71 | μs   |  |

1. These values are based on characterization. These values are not covered by test limits in production.

2. These values are based on simulation. These values are not covered by test limits in production or characterization.

| Symbol           | ol Parameter Conditions                                               |                                                                           | Min  | Тур  | Max | Units |  |

|------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------|------|------|-----|-------|--|

| I <sub>OUT</sub> | DC output current <sup>(1)</sup>                                      | V <sub>VDDCORE</sub> > 1.65V                                              |      |      | 55  | mA    |  |

|                  | Output DC load regulation <sup>(1)</sup><br>Transient load regulation | I <sub>OUT</sub> = 0 to 50mA,<br>V <sub>VDDIN</sub> = 3V                  | -136 | -101 | -82 | mV    |  |

|                  | Output DC regulation <sup>(1)</sup>                                   | $I_{OUT} = 50 \text{ mA},$<br>$V_{VDDIN} = 2 \text{ V to } 3.6 \text{ V}$ | -20  | 38   | 99  | mV    |  |

| I <sub>Q</sub>   | Quescient current <sup>(1)</sup>                                      | $V_{VDDIN} = 2V, I_{OUT} = 0 \text{ mA}$                                  | 97   | 186  | 546 |       |  |

|                  |                                                                       | $V_{VDDIN} > 2.2V, I_{OUT} = 0 \text{ mA}$                                | 97   | 111  | 147 | μA    |  |

| $P_{EFF}$        | Power efficiency <sup>(1)</sup>                                       | I <sub>OUT</sub> = 5mA, 50mA<br>Reference power not included              | 82.7 | 88.3 | 95  | %     |  |

1. These values are based on characterization. These values are not covered by test limits in production.

Table 9-40.

Decoupling Requirements in Switching Mode

| Symbol               | Parameter                              | Technology                    | Тур | Units |

|----------------------|----------------------------------------|-------------------------------|-----|-------|

| C <sub>IN1</sub>     | Input regulator capacitor 1            |                               | 33  | - F   |

| C <sub>IN2</sub>     | Input regulator capacitor 2            |                               | 100 | nF    |

| C <sub>IN3</sub>     | Input regulator capacitor 3            |                               | 10  | μF    |

| C <sub>OUT1</sub>    | Output regulator capacitor 1           | X7R MLCC                      | 100 | nF    |

| C <sub>OUT2</sub>    | Output regulator capacitor 2           | X7R MLCC (ex : GRM31CR71A475) | 4.7 | μF    |

| L <sub>EXT</sub>     | External inductance                    | (ex: Murata LQH3NPN220MJ0)    | 22  | μH    |

| R <sub>DCLEXT</sub>  | Serial resistance of L <sub>EXT</sub>  |                               | 0.7 | Ω     |

| ISAT <sub>LEXT</sub> | Saturation current of L <sub>EXT</sub> |                               | 300 | mA    |

Note: 1. Refer to Section 6. on page 46.

The maximum SPI master output frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(f_{PINMAX}, \frac{1}{SPIn})$$

Where *SPIn* is the MOSI delay, SPI2 or SPI5 depending on CPOL and NCPHA.  $f_{PINMAX}$  is the maximum frequency of the SPI pins. refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

#### Maximum SPI Frequency, Master Input

The maximum SPI master input frequency is given by the following formula:

$$f_{SPCKMAX} = \frac{1}{SPIn + t_{VALID}}$$

Where *SPIn* is the MISO setup and hold time, SPI0 + SPI1 or SPI3 + SPI4 depending on CPOL and NCPHA.  $t_{VALID}$  is the SPI slave response time. refer to the SPI slave datasheet for  $t_{VALID}$ .

9.10.3.2 Slave mode

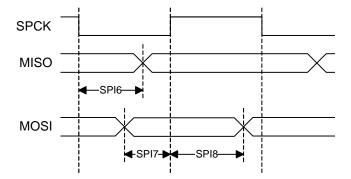

Figure 9-14. SPI Slave Mode with (CPOL= 0 and NCPHA= 1) or (CPOL= 1 and NCPHA= 0)

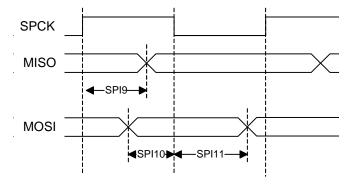

Figure 9-15. SPI Slave Mode with (CPOL= NCPHA= 0) or (CPOL= NCPHA= 1)

Where *SPIn* is the MISO delay, SPI6 or SPI9 depending on CPOL and NCPHA.  $t_{SETUP}$  is the SPI master setup time. refer to the SPI master datasheet for  $t_{SETUP}$ .  $f_{PINMAX}$  is the maximum frequency of the SPI pins. refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

## 9.10.4 TWIM/TWIS Timing

Figure 9-64 shows the TWI-bus timing requirements and the compliance of the device with them. Some of these requirements ( $t_r$  and  $t_f$ ) are met by the device without requiring user intervention. Compliance with the other requirements ( $t_{HD-STA}$ ,  $t_{SU-STA}$ ,  $t_{SU-STO}$ ,  $t_{HD-DAT}$ ,  $t_{SU-DAT-TWI}$ ,  $t_{LOW-TWI}$ ,  $t_{HIGH}$ , and  $f_{TWCK}$ ) requires user intervention through appropriate programming of the relevant TWIM and TWIS user interface registers. refer to the TWIM and TWIS sections for more information.

|                         |                                 |                         | Minimum     |                     | Maximum            |                                               |      |

|-------------------------|---------------------------------|-------------------------|-------------|---------------------|--------------------|-----------------------------------------------|------|

| Symbol                  | Parameter                       | Mode                    | Requirement | Device              | Requirement        | Device                                        | Unit |

| 4                       |                                 | Standard <sup>(1)</sup> | -           |                     | 1000               |                                               |      |

| t <sub>r</sub>          | TWCK and TWD rise time          | Fast <sup>(1)</sup>     | 20 + 0      | .1C <sub>b</sub>    |                    |                                               | ns   |

| 4                       |                                 | Standard                | -           |                     | 30                 |                                               |      |

| t <sub>f</sub>          | TWCK and TWD fall time          | Fast                    | 20 + 0      | .1C <sub>b</sub>    | 30                 | ns                                            |      |

| +                       | (Depented) START hold time      | Standard                | 4           |                     |                    |                                               | 1    |

| t <sub>HD-STA</sub>     | (Repeated) START hold time      | Fast                    | 0.6         | t <sub>clkpb</sub>  | -                  |                                               | μs   |

| +                       | (Dependented) START act up time | Standard                | 4.7         |                     |                    |                                               |      |

| t <sub>SU-STA</sub>     | (Repeated) START set-up time    | Fast                    | 0.6         | t <sub>clkpb</sub>  | -                  |                                               | μs   |

| 4                       | STOP set-up time                | Standard                | 4.0         | 41                  | -                  |                                               | μs   |

| t <sub>SU-STO</sub>     |                                 | Fast                    | 0.6         | 4t <sub>clkpb</sub> |                    |                                               |      |

| 4                       | Data hold time                  | Standard                |             | 2t <sub>clkpb</sub> | 3.45 <sup>()</sup> | 15+ +                                         |      |

| t <sub>HD-DAT</sub>     |                                 | Fast                    |             |                     | 0.9()              | 15t <sub>prescaled</sub> + t <sub>clkpb</sub> | μs   |

| +                       | Data set-up time                | Standard                | 250         | 2t <sub>clkpb</sub> |                    |                                               | ns   |

| t <sub>SU-DAT-TWI</sub> |                                 | Fast                    | 100         |                     | -                  |                                               |      |

| t <sub>SU-DAT</sub>     |                                 | -                       | -           | t <sub>clkpb</sub>  | -                  |                                               | -    |

| +                       | TWCK LOW period                 | Standard                | 4.7         | 44                  | -                  |                                               | μs   |

| t <sub>LOW-TWI</sub>    |                                 | Fast                    | 1.3         | 4t <sub>clkpb</sub> |                    |                                               |      |

| t <sub>LOW</sub>        |                                 | -                       | -           | t <sub>clkpb</sub>  | -                  |                                               | -    |

| +                       | TWCK HIGH pariod                | Standard                | 4.0         | Q+                  | -                  |                                               | μs   |

| t <sub>HIGH</sub>       | TWCK HIGH period                | Fast                    | 0.6         | 8t <sub>clkpb</sub> |                    |                                               |      |

| f                       |                                 | Standard                |             |                     | 100                | 1                                             | kHz  |

| f <sub>TWCK</sub>       | TWCK frequency                  | Fast                    | -           |                     | 400                | <sup>12t</sup> clkpb                          | κΠΖ  |

**Table 9-64.**TWI-Bus Timing Requirements

Notes: 1. Standard mode:  $f_{TWCK} \le 100 \text{ kHz}$ ; fast mode:  $f_{TWCK} > 100 \text{ kHz}$ .

### 12.1.7 FLASHCALW

# Corrupted data in flash may happen after flash page write operations.

After a flash page write operation, reading (data read or code fetch) in flash may fail. This may lead to an expectition or to others errors derived from this corrupted read access. **Fix/Workaround**