#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                     |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 80                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.68V ~ 3.6V                                                             |

| Data Converters            | A/D 15x12b; D/A 1x10b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-TQFP                                                                 |

| Supplier Device Package    | 100-TQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4ls8ca-au |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2 Configuration Summary

Table 2-1.Sub Series Summary

| Feature     | ATSAM4LC      | ATSAM4LS    |

|-------------|---------------|-------------|

| SEGMENT LCD | Yes           | No          |

| AESA        | Yes           | No          |

| USB         | Device + Host | Device Only |

Table 2-2.

ATSAM4LC Configuration Summary

- Atmel

| Feature                 | ATSAM4LC8/4/2C | ATSAM4LC8/4/2B                             | ATSAM4LC8/4/2A |  |  |  |

|-------------------------|----------------|--------------------------------------------|----------------|--|--|--|

| Number of Pins          | 100            | 64                                         | 48             |  |  |  |

| Max Frequency           |                | 48MHz                                      |                |  |  |  |

| Flash                   |                | 512/256/128KB                              |                |  |  |  |

| SRAM                    |                | 64/32/32KB                                 |                |  |  |  |

| SEGMENT LCD             | 4x40           |                                            |                |  |  |  |

| GPIO                    | 75             | 43                                         | 27             |  |  |  |

| High-drive pins         | 6              | 3                                          | 1              |  |  |  |

| External Interrupts     |                | 8 + 1 NMI                                  | 1              |  |  |  |

| TWI                     | 2 Masters + 2  | 2 Masters/Slaves 1 Master +<br>Master/Slav |                |  |  |  |

| USART                   |                | 4                                          |                |  |  |  |

| PICOUART                |                | 1                                          | 0              |  |  |  |

| Peripheral DMA Channels |                | 16                                         | 1              |  |  |  |

| AESA                    |                | 1                                          |                |  |  |  |

| Peripheral Event System |                | 1                                          |                |  |  |  |

| SPI                     |                | 1                                          |                |  |  |  |

| Asynchronous Timers     |                | 1                                          |                |  |  |  |

| Timer/Counter Channels  | 6              |                                            | 3              |  |  |  |

| Parallel Capture Inputs |                | 8                                          |                |  |  |  |

| Frequency Meter         |                | 1                                          |                |  |  |  |

| Watchdog Timer          |                | 1                                          |                |  |  |  |

| Power Manager           |                | 1                                          |                |  |  |  |

| Glue Logic LUT          |                | 2                                          | 1              |  |  |  |

## 3.2 Peripheral Multiplexing on I/O lines

### 3.2.1 Multiplexed Signals

Each GPIO line can be assigned to one of the peripheral functions. The following tables (Section 3-1 "100-pin GPIO Controller Function Multiplexing" on page 19 to Section 3-4 "48-pin GPIO Controller Function Multiplexing" on page 28) describes the peripheral signals multiplexed to the GPIO lines.

Peripheral functions that are not relevant in some parts of the family are grey-shaded.

For description of differents Supply voltage source, refer to the Section 6. "Power and Startup Considerations" on page 46.

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 1 of 4)

| lable | •          |     |            | 0 0011 | 101101 | i unotion | manupiox       | ng (Oneer     | 1 01 1)          |                 |                   |                |                 |

|-------|------------|-----|------------|--------|--------|-----------|----------------|---------------|------------------|-----------------|-------------------|----------------|-----------------|

|       | ATSAM4LC   |     | ATSAM4LS   | Pin    | GPIO   | Supply    | GPIO Functions |               |                  |                 |                   |                |                 |

| QFN   | VFBGA      | QFN | VFBGA      |        |        |           | Α              | В             | С                | D               | E                 | F              | G               |

| 5     | B9         | 5   | B9         | PA00   | 0      | VDDIO     |                |               |                  |                 |                   |                |                 |

| 6     | B8         | 6   | B8         | PA01   | 1      | VDDIO     |                |               |                  |                 |                   |                |                 |

| 12    | A7         | 12  | A7         | PA02   | 2      | VDDIN     | SCIF<br>GCLK0  | SPI<br>NPCS0  |                  |                 |                   |                | CATB<br>DIS     |

| 19    | В3         | 19  | В3         | PA03   | 3      | VDDIN     |                | SPI<br>MISO   |                  |                 |                   |                |                 |

| 24    | A2         | 24  | A2         | PA04   | 4      | VDDANA    | ADCIFE<br>AD0  | USART0<br>CLK | EIC<br>EXTINT2   | GLOC<br>IN1     |                   |                | CATB<br>SENSE0  |

| 25    | A1         | 25  | A1         | PA05   | 5      | VDDANA    | ADCIFE<br>AD1  | USART0<br>RXD | EIC<br>EXTINT3   | GLOC<br>IN2     | ADCIFE<br>TRIGGER |                | CATB<br>SENSE1  |

| 30    | C3         | 30  | C3         | PA06   | 6      | VDDANA    | DACC<br>VOUT   | USART0<br>RTS | EIC<br>EXTINT1   | GLOC<br>IN0     | ACIFC<br>ACAN0    |                | CATB<br>SENSE2  |

| 31    | D3         | 31  | D3         | PA07   | 7      | VDDANA    | ADCIFE<br>AD2  | USART0<br>TXD | EIC<br>EXTINT4   | GLOC<br>IN3     | ACIFC<br>ACAP0    |                | CATB<br>SENSE3  |

| 44    | G2         | 44  | G2         | PA08   | 8      | LCDA      | USART0<br>RTS  | TC0<br>A0     | PEVC<br>PAD EVT0 | GLOC<br>OUT0    |                   | LCDCA<br>SEG23 | CATB<br>SENSE4  |

| 47    | F5         | 47  | F5         | PA09   | 9      | LCDA      | USART0<br>CTS  | TC0<br>B0     | PEVC<br>PAD EVT1 | PARC<br>PCDATA0 |                   | LCDCA<br>COM3  | CATB<br>SENSE5  |

| 48    | H2         | 48  | H2         | PA10   | 10     | LCDA      | USART0<br>CLK  | TC0<br>A1     | PEVC<br>PAD EVT2 | PARC<br>PCDATA1 |                   | LCDCA<br>COM2  | CATB<br>SENSE6  |

| 49    | H3         | 49  | H3         | PA11   | 11     | LCDA      | USART0<br>RXD  | TC0<br>B1     | PEVC<br>PAD EVT3 | PARC<br>PCDATA2 |                   | LCDCA<br>COM1  | CATB<br>SENSE7  |

| 50    | J2         | 50  | J2         | PA12   | 12     | LCDA      | USART0<br>TXD  | TC0<br>A2     |                  | PARC<br>PCDATA3 |                   | LCDCA<br>COM0  | CATB<br>DIS     |

| 63    | H5         | 63  | H5         | PA13   | 13     | LCDA      | USART1<br>RTS  | TC0<br>B2     | SPI<br>NPCS1     | PARC<br>PCDATA4 |                   | LCDCA<br>SEG5  | CATB<br>SENSE8  |

| 64    | <b>K</b> 7 | 64  | <b>K</b> 7 | PA14   | 14     | LCDA      | USART1<br>CLK  | TC0<br>CLK0   | SPI<br>NPCS2     | PARC<br>PCDATA5 |                   | LCDCA<br>SEG6  | CATB<br>SENSE9  |

| 65    | G5         | 65  | G5         | PA15   | 15     | LCDA      | USART1<br>RXD  | TC0<br>CLK1   | SPI<br>NPCS3     | PARC<br>PCDATA6 |                   | LCDCA<br>SEG7  | CATB<br>SENSE10 |

| Signal Name            | Function                             | Туре               | Active<br>Level | Comments |

|------------------------|--------------------------------------|--------------------|-----------------|----------|

|                        | Inter-IC Sound (I2S)                 | Controller - IIS   | С               |          |

| IMCK                   | I2S Master Clock                     | Output             |                 |          |

| ISCK                   | I2S Serial Clock                     | I/O                |                 |          |

| ISDI                   | I2S Serial Data In                   | Input              |                 |          |

| ISDO                   | I2S Serial Data Out                  | Output             |                 |          |

| IWS                    | I2S Word Select                      | I/O                |                 |          |

|                        | LCD Controll                         | er - LCDCA         |                 |          |

| BIASL                  | Bias voltage (1/3 VLCD)              | Analog             |                 |          |

| BIASH                  | Bias voltage (2/3 VLCD)              | Analog             |                 |          |

| CAPH                   | High voltage end of flying capacitor | Analog             |                 |          |

| CAPL                   | Low voltage end of flying capacitor  | Analog             |                 |          |

| COM3 - COM0            | Common terminals                     | Analog             |                 |          |

| SEG39 - SEG0           | Segment terminals                    | Analog             |                 |          |

| VLCD                   | Bias voltage                         | Analog             |                 |          |

|                        | Parallel Capt                        | ure - PARC         |                 |          |

| PCCK                   | Clock                                | Input              |                 |          |

| PCDATA7 - PCDATA0      | Data lines                           | Input              |                 |          |

| PCEN1                  | Data enable 1                        | Input              |                 |          |

| PCEN2                  | Data enable 2                        | Input              |                 |          |

|                        | Peripheral Event C                   | ontroller - PEVC   | ;               |          |

| PAD_EVT3 -<br>PAD_EVT0 | Event Inputs                         | Input              |                 |          |

|                        | Power Mana                           | ager - PM          |                 |          |

| RESET_N                | Reset                                | Input              | Low             |          |

|                        | System Control I                     | nterface - SCIF    |                 |          |

| GCLK3 - GCLK0          | Generic Clock Outputs                | Output             |                 |          |

| GCLK_IN1 - GCLK_IN0    | Generic Clock Inputs                 | Input              |                 |          |

| XIN0                   | Crystal 0 Input                      | Analog/<br>Digital |                 |          |

| XOUT0                  | Crystal 0 Output                     | Analog             |                 |          |

|                        | Serial Peripheral                    | Interface - SPI    |                 | •        |

| MISO                   | Master In Slave Out                  | I/O                |                 |          |

| MOSI                   | Master Out Slave In                  | I/O                |                 |          |

|                        | SPI Peripheral Chip Selects          | I/O                | Low             |          |

| NPCS3 - NPCS0          |                                      |                    |                 |          |

## Table 3-8. Signal Descriptions List (Sheet 2 of 4)

| Signal Name | Function                                | Туре             | Active<br>Level | Comments                                                                |

|-------------|-----------------------------------------|------------------|-----------------|-------------------------------------------------------------------------|

| A0          | Channel 0 Line A                        | I/O              |                 |                                                                         |

| A1          | Channel 1 Line A                        | I/O              |                 |                                                                         |

| A2          | Channel 2 Line A                        | I/O              |                 |                                                                         |

| B0          | Channel 0 Line B                        | I/O              |                 |                                                                         |

| B1          | Channel 1 Line B                        | I/O              |                 |                                                                         |

| B2          | Channel 2 Line B                        | I/O              |                 |                                                                         |

| CLK0        | Channel 0 External Clock Input          | Input            |                 |                                                                         |

| CLK1        | Channel 1 External Clock Input          | Input            |                 |                                                                         |

| CLK2        | Channel 2 External Clock Input          | Input            |                 |                                                                         |

|             | Two-wire Interface - TWIMS              | 0, TWIMS1, TWI   | M2, TWIM3       |                                                                         |

| TWCK        | Two-wire Serial Clock                   | I/O              |                 |                                                                         |

| TWD         | Two-wire Serial Data                    | I/O              |                 |                                                                         |

| Univer      | sal Synchronous Asynchronous Receiver T | ransmitter - USA | RT0, USAR       | T1, USART2, USART3                                                      |

| CLK         | Clock                                   | I/O              |                 |                                                                         |

| CTS         | Clear To Send                           | Input            | Low             |                                                                         |

| RTS         | Request To Send                         | Output           | Low             |                                                                         |

| RXD         | Receive Data                            | Input            |                 |                                                                         |

| TXD         | Transmit Data                           | Output           |                 |                                                                         |

|             | USB 2.0 Inter                           | face - USBC      |                 |                                                                         |

| DM          | USB Full Speed Interface Data -         | I/O              |                 |                                                                         |

| DP          | USB Full Speed Interface Data +         | I/O              |                 |                                                                         |

|             | Ρον                                     | ver              |                 |                                                                         |

| GND         | Ground                                  | Ground           |                 |                                                                         |

| GNDANA      | Analog Ground                           | Ground           |                 |                                                                         |

| VDDANA      | Analog Power Supply                     | Power<br>Input   |                 | 1.68V to 3.6V                                                           |

| VDDCORE     | Core Power Supply                       | Power<br>Input   |                 | 1.68V to 1.98V                                                          |

| VDDIN       | Voltage Regulator Input                 | Power<br>Input   |                 | 1.68V to 3.6V                                                           |

| VDDIO       | I/O Pads Power Supply                   | Power<br>Input   |                 | 1.68V to 3.6V. VDDIO must<br>always be equal to or lower than<br>VDDIN. |

| VDDOUT      | Voltage Regulator Output                | Power<br>Output  |                 | 1.08V to 1.98V                                                          |

|             | General Po                              | urpose I/O       |                 |                                                                         |

## **Table 3-8.**Signal Descriptions List (Sheet 3 of 4)

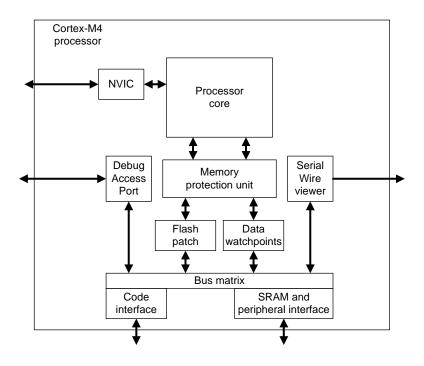

## 4. Cortex-M4 processor and core peripherals

## 4.1 Cortex-M4

The Cortex-M4 processor is a high performance 32-bit processor designed for the microcontroller market. It offers significant benefits to developers, including:

- outstanding processing performance combined with fast interrupt handling

- enhanced system debug with extensive breakpoint and trace capabilities

- efficient processor core, system and memories

- ultra-low power consumption with integrated sleep modes

- platform security robustness, with integrated memory protection unit (MPU).

The Cortex-M4 processor is built on a high-performance processor core, with a 3-stage pipeline Harvard architecture, making it ideal for demanding embedded applications. The processor delivers exceptional power efficiency through an efficient instruction set and extensively optimized design, providing high-end processing hardware including a range of single-cycle and SIMD multiplication and multiply-with-accumulate capabilities, saturating arithmetic and dedicated hardware division.

To facilitate the design of cost-sensitive devices, the Cortex-M4 processor implements tightlycoupled system components that reduce processor area while significantly improving interrupt handling and system debug capabilities. The Cortex-M4 processor implements a version of the Thumb<sup>®</sup> instruction set based on Thumb-2 technology, ensuring high code density and reduced program memory requirements. The Cortex-M4 instruction set provides the exceptional performance expected of a modern 32-bit architecture, with the high code density of 8-bit and 16-bit microcontrollers.

The Cortex-M4 processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC includes a *non-maskable interrupt* (NMI), and provides up to 80 interrupt priority levels. The tight integration of the proces-

sor core and NVIC provides fast execution of interrupt service routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to suspend load-multiple and store-multiple operations. Interrupt handlers do not require wrapping in assembler code, removing any code overhead from the ISRs. A tail-chain optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep function enabling the entire device to be rapidly powered down while still retaining program state.

### 4.2 System level interface

The Cortex-M4 processor provides multiple interfaces using AMBA<sup>®</sup> technology to provide high speed, low latency memory accesses. It supports unaligned data accesses and implements atomic bit manipulation that enables faster peripheral controls, system spinlocks and thread-safe Boolean data handling.

The Cortex-M4 processor has an *memory protection unit* (MPU) that provides fine grain memory control, enabling applications to utilize multiple privilege levels, separating and protecting code, data and stack on a task-by-task basis. Such requirements are becoming critical in many embedded applications such as automotive.

#### 4.3 Integrated configurable debug

The Cortex-M4 processor implements a complete hardware debug solution. This provides high system visibility of the processor and memory through either a traditional JTAG port or a 2-pin *Serial Wire Debug* (SWD) port that is ideal for microcontrollers and other small package devices.

For system trace the processor integrates an *Instrumentation Trace Macrocell* (ITM) alongside data watchpoints and a profiling unit. To enable simple and cost-effective profiling of the system events these generate, a *Serial Wire Viewer* (SWV) can export a stream of software-generated messages, data trace, and profiling information through a single pin.

The *Flash Patch and Breakpoint Unit* (FPB) provides 8 hardware breakpoint comparators that debuggers can use. The comparators in the FPB also provide remap functions of up to 8 words in the program code in the CODE memory region. This enables applications stored on a nonerasable, ROM-based microcontroller to be patched if a small programmable memory, for example flash, is available in the device. During initialization, the application in ROM detects, from the programmable memory, whether a patch is required. If a patch is required, the application programs the FPB to remap a number of addresses. When those addresses are accessed, the accesses are redirected to a remap table specified in the FPB configuration, which means the program in the non-modifiable ROM can be patched.

A specific Peripheral Debug (PDBG) register is implemented in the Private Peripheral Bus address map. This register allows the user to configure the behavior of some modules in debug mode.

Atmel

### 4.4 Cortex-M4 processor features and benefits summary

- · tight integration of system peripherals reduces area and development costs

- · Thumb instruction set combines high code density with 32-bit performance

- code-patch ability for ROM system updates

- · power control optimization of system components

- integrated sleep modes for low power consumption

- fast code execution permits slower processor clock or increases sleep mode time

- hardware division and fast digital-signal-processing orientated multiply accumulate

- · saturating arithmetic for signal processing

- · deterministic, high-performance interrupt handling for time-critical applications

- memory protection unit (MPU) for safety-critical applications

- extensive debug and trace capabilities:

- Serial Wire Debug and Serial Wire Trace reduce the number of pins required for debugging, tracing, and code profiling.

#### 4.5 Cortex-M4 core peripherals

These are:

Nested Vectored Interrupt Controller

The NVIC is an embedded interrupt controller that supports low latency interrupt processing.

System control block

The System control block (SCB) is the programmers model interface to the processor. It provides system implementation information and system control, including configuration, control, and reporting of system exceptions.

#### System timer

The system timer, SysTick, is a 24-bit count-down timer. Use this as a Real Time Operating System (RTOS) tick timer or as a simple counter.

Memory protection unit

The *Memory protection unit* (MPU) improves system reliability by defining the memory attributes for different memory regions. It provides up to eight different regions, and an optional predefined background region.

The complete Cortex-M4 User Guide can be found on the ARM web site:

http://infocenter.arm.com/help/topic/com.arm.doc.dui0553a/DUI0553A cortex m4 dgug.pdf

## 4.6 Cortex-M4 implementations options

This table provides the specific configuration options implemented in the SAM4L series

| Option                   | Implementation     |

|--------------------------|--------------------|

| Inclusion of MPU         | yes                |

| Inclusion of FPU         | No                 |

| Number of interrupts     | 80                 |

| Number of priority bits  | 4                  |

| Inclusion of the WIC     | No                 |

| Embedded Trace Macrocell | No                 |

| Sleep mode instruction   | Only WFI supported |

| Endianness               | Little Endian      |

| Bit-banding              | No                 |

| SysTick timer            | Yes                |

| Register reset values    | No                 |

Table 4-1.

Cortex-M4 implementation options

## 4.7 Cortex-M4 Interrupts map

The table below shows how the interrupt request signals are connected to the NVIC.

| Line | Module                    | Signal  |  |  |  |

|------|---------------------------|---------|--|--|--|

| 0    | Flash Controller          | HFLASHC |  |  |  |

| 1    | Peripheral DMA Controller | PDCA 0  |  |  |  |

| 2    | Peripheral DMA Controller | PDCA 1  |  |  |  |

| 3    | Peripheral DMA Controller | PDCA 2  |  |  |  |

| 4    | Peripheral DMA Controller | PDCA 3  |  |  |  |

| 5    | Peripheral DMA Controller | PDCA 4  |  |  |  |

| 6    | Peripheral DMA Controller | PDCA 5  |  |  |  |

| 7    | Peripheral DMA Controller | PDCA 6  |  |  |  |

| 8    | Peripheral DMA Controller | PDCA 7  |  |  |  |

| 9    | Peripheral DMA Controller | PDCA 8  |  |  |  |

| 10   | Peripheral DMA Controller | PDCA 9  |  |  |  |

| 11   | Peripheral DMA Controller | PDCA 10 |  |  |  |

**Table 4-2.**Interrupt Request Signal Map (Sheet 1 of 3)

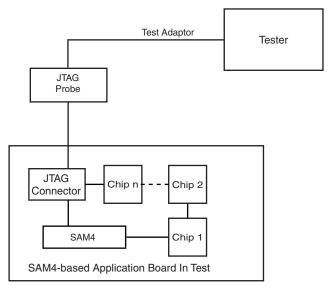

#### 8.11.3 How to initialize test and debug features

To enable the JTAG pins a falling edge event must be detected on the TCK pin at any time after the RESET\_N pin is released.

Certain operations requires that the system is prevented from running code after reset is released. This is done by holding low the TCK pin after the RESET\_N is released. This makes the SMAP assert the core\_hold\_reset signal that hold the Cortex-M4 core under reset.

To make the CPU run again, clear the CHR bit in the Status Register (SR.CHR) to de-assert the core\_hold\_reset signal. Independent of the initial state of the TAP Controller, the Test-Logic-Reset state can always be entered by holding TMS high for 5 TCK clock periods. This sequence should always be applied at the start of a JTAG session and after enabling the JTAG pins to bring the TAP Controller into a defined state before applying JTAG commands. Applying a 0 on TMS for 1 TCK period brings the TAP Controller to the Run-Test/Idle state, which is the starting point for JTAG operations.

#### 8.11.4 How to disable test and debug features

To disable the JTAG pins the TCK pin must be held high while RESET\_N pin is released.

#### 8.11.5 Typical JTAG sequence

Assuming Run-Test/Idle is the present state, a typical scenario for using the JTAG interface is:

#### 8.11.5.1 Scanning in JTAG instruction

At the TMS input, apply the sequence 1, 1, 0, 0 at the rising edges of TCK to enter the Shift Instruction Register - Shift-IR state. While in this state, shift the 4 bits of the JTAG instructions into the JTAG instruction register from the TDI input at the rising edge of TCK. The TMS input must be held low during input of the 4 LSBs in order to remain in the Shift-IR state. The JTAG Instruction selects a particular Data Register as path between TDI and TDO and controls the circuitry surrounding the selected Data Register.

| Symbol              | Parameter                 | Description                                                          | Мах  | Units |

|---------------------|---------------------------|----------------------------------------------------------------------|------|-------|

| f <sub>CPU</sub>    | CPU clock frequency       |                                                                      | 12   |       |

| f <sub>PBA</sub>    | PBA clock frequency       |                                                                      | 12   |       |

| f <sub>PBB</sub>    | PBB clock frequency       |                                                                      | 12   |       |

| f <sub>PBC</sub>    | PBC clock frequency       |                                                                      | 12   |       |

| f <sub>PBD</sub>    | PBD clock frequency       |                                                                      | 12   |       |

| f <sub>GCLK0</sub>  | GCLK0 clock frequency     | DFLLIF main reference, GCLK0 pin                                     | 16.6 |       |

| f <sub>GCLK1</sub>  | GCLK1 clock frequency     | DFLLIF dithering and SSGreference,<br>GCLK1 pin                      | 16.6 |       |

| f <sub>GCLK2</sub>  | GCLK2 clock frequency     | AST, GCLK2 pin                                                       | 6.6  |       |

| f <sub>GCLK3</sub>  | GCLK3 clock frequency     | CATB, GCLK3 pin                                                      | 17.3 |       |

| f <sub>GCLK4</sub>  | GCLK4 clock frequency     | FLO and AESA                                                         | 16.6 |       |

| f <sub>GCLK5</sub>  | GCLK5 clock frequency     | GLOC, TC0 and RC32KIFB_REF                                           | 26.6 |       |

| f <sub>GCLK6</sub>  | GCLK6 clock frequency     | ABDACB and IISC                                                      | 16.6 | MHz   |

| f <sub>GCLK7</sub>  | GCLK7 clock frequency     | USBC                                                                 | 16.6 |       |

| f <sub>GCLK8</sub>  | GCLK8 clock frequency     | TC1 and PEVC[0]                                                      | 16.6 |       |

| f <sub>GCLK9</sub>  | GCLK9 clock frequency     | PLL0 and PEVC[1]                                                     | 16.6 |       |

| f <sub>GCLK10</sub> | GCLK10 clock<br>frequency | ADCIFE                                                               | 16.6 |       |

| f <sub>GCLK11</sub> | GCLK11 clock<br>frequency | Master generic clock. Can be used as source for other generic clocks | 51.2 |       |

|                     | 0000 1 11                 | Oscillator 0 in crystal mode                                         | 16   |       |

| f <sub>OSC0</sub>   | OSC0 output frequency     | Oscillator 0 in digital clock mode                                   | 16   |       |

| f <sub>PLL</sub>    | PLL output frequency      | Phase Locked Loop                                                    | N/A  |       |

| f <sub>DFLL</sub>   | DFLL output frequency     | Digital Frequency Locked Loop                                        | N/A  |       |

| f <sub>RC80M</sub>  | RC80M output<br>frequency | Internal 80MHz RC Oscillator                                         | N/A  |       |

**Table 9-5.**Maximum Clock Frequencies in Power Scaling Mode 1 and RUN Mode

| Mode   | Conditions                                    | T <sub>A</sub> | Typical<br>Wakeup Time | Тур  | Max <sup>(1)</sup> | Unit |

|--------|-----------------------------------------------|----------------|------------------------|------|--------------------|------|

|        | Switching mode                                | 25°C           | 9 * Main clock         | 3817 | 4033               |      |

| SLEEP0 | Switching mode                                | 85°C           | cycles                 | 3934 | 4174               |      |

|        |                                               | 25°C           | 9 * Main clock         | 2341 | 2477               |      |

| SLEEP1 | Switching mode                                | 85°C           | cycles + 500ns         | 2437 | 2585               | -    |

| SLEEP2 |                                               | 25°C           | 9 * Main clock         | 1758 | 1862               | -    |

|        | Switching mode                                | 85°C           | cycles + 500ns         | 1847 | 1971               |      |

| SLEEP3 | Linear mode                                   |                |                        | 51   | 60                 |      |

| WAIT   | OSC32K and AST running<br>Fast wake-up enable |                |                        | 5.9  | 8.7                | μA   |

|        | OSC32K and AST stopped<br>Fast wake-up enable |                | 1.5µs                  | 4.7  | 7.6                | •    |

|        | OSC32K running<br>AST running at 1kHz         | 25°C           | 1.5µs                  | 3.1  | 5.1                | -    |

|        | AST and OSC32K stopped                        |                |                        | 2.2  | 4.2                | -    |

| BACKUP | OSC32K running<br>AST running at 1 kHz        |                |                        | 1.5  | 3.1                |      |

|        | AST and OSC32K stopped                        |                |                        | 0.9  | 1.7                | Ī    |

Table 9-6.

ATSAM4L4/2 Current consumption and Wakeup time for power scaling mode 0 and 2

1. These values are based on characterization. These values are not covered by test limits in production.

| Table 9-7. | ATSAM4L8 Current consumption and Wakeup time for power scaling mode 0 and 2 |

|------------|-----------------------------------------------------------------------------|

|            |                                                                             |

| Mode | Conditions                                      | T <sub>A</sub> | Typical<br>Wakeup Time | Тур | Max <sup>(1)</sup> | Unit   |

|------|-------------------------------------------------|----------------|------------------------|-----|--------------------|--------|

|      | CPU running a Fibonacci algorithm               | 25°C           | NI/A                   | 319 | 343                |        |

| 5.00 | Linear mode                                     | 85°C           | N/A                    | 326 | 350                |        |

|      | CPU running a CoreMark algorithm<br>Linear mode | 25°C           | N/A                    | 343 | 387                |        |

|      |                                                 | 85°C           |                        | 351 | 416                |        |

| RUN  | CPU running a Fibonacci algorithm               | 25°C           | N/A                    | 181 | 198                | µA/MHz |

|      | Switching mode                                  | 85°C           |                        | 186 | 203                |        |

|      | CPU running a CoreMark algorithm                | 25°C           | N/A                    | 192 | 232                | _      |

|      | Switching mode                                  | 85°C           |                        | 202 | 239                |        |

- Atmel

| Mode                                                                                                                                                                                                                                                                                                                                                                                                                    | Conditions                                    | T <sub>A</sub> | Typical<br>Wakeup Time | Тур | Max <sup>(1)</sup>                                                                                         | Unit   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------|------------------------|-----|------------------------------------------------------------------------------------------------------------|--------|

|                                                                                                                                                                                                                                                                                                                                                                                                                         | CPU running a Fibonacci algorithm             | 25°C           |                        | 222 | 240                                                                                                        |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                         | Linear mode                                   | 85°C           | N/A                    | 233 | 276                                                                                                        |        |

| RUN<br>SLEEP0<br>SLEEP1<br>SLEEP2<br>SLEEP3<br>WAIT                                                                                                                                                                                                                                                                                                                                                                     | CPU running a CoreMark algorithm              | 25°C           | N/A                    | 233 | 276                                                                                                        |        |

| DUN                                                                                                                                                                                                                                                                                                                                                                                                                     | Linear mode                                   | 85°C           |                        | 230 | 270                                                                                                        |        |

| Linear mode         RUN         CPU running a CoreMark         Linear mode         CPU running a Fibonacci         Switching mode         CPU running a CoreMark         Switching mode         CPU running a CoreMark         Switching mode         SLEEP0         SLEEP1         Switching mode         SLEEP2         Switching mode         SLEEP3         Linear mode         WAIT         OSC32K and AST stopped | CPU running a Fibonacci algorithm             | 25°C           | N/A                    | 100 | 112                                                                                                        | µA/MHz |

|                                                                                                                                                                                                                                                                                                                                                                                                                         | Switching mode                                | 85°C           |                        | 100 | 119                                                                                                        |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                         | CPU running a CoreMark algorithm              | 25°C           | N/A                    | 104 | 128                                                                                                        |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                         | Switching mode                                | 85°C           |                        | 107 | 138                                                                                                        |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                         | Quitaking mode                                | 25°C           | 9 * Main clock         | 527 | 627                                                                                                        |        |

| SLEEPU                                                                                                                                                                                                                                                                                                                                                                                                                  | Switching mode                                | 85°C           | cycles                 | 579 | 739                                                                                                        |        |

| SLEEP1                                                                                                                                                                                                                                                                                                                                                                                                                  | Switching mode                                | 25°C           | 9 * Main clock         | 369 | 445                                                                                                        |        |

| SLEEPT                                                                                                                                                                                                                                                                                                                                                                                                                  | Switching mode                                | 85°C           | cycles + 500ns         | 404 | 564                                                                                                        | l I    |

|                                                                                                                                                                                                                                                                                                                                                                                                                         | Switching mode                                | 25°C           | 9 * Main clock         | 305 | 381                                                                                                        |        |

| SLEEP2                                                                                                                                                                                                                                                                                                                                                                                                                  | Switching mode                                | 85°C           | cycles + 500ns         | 334 | 240<br>276<br>276<br>270<br>112<br>119<br>128<br>138<br>627<br>739<br>445<br>564<br>381<br>442<br>55<br>55 |        |

| SLEEP3                                                                                                                                                                                                                                                                                                                                                                                                                  | Linear mode                                   |                |                        | 46  | 55                                                                                                         |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                         | OSC32K and AST running<br>Fast wake-up enable |                | 4 500                  | 5.5 |                                                                                                            | μΑ     |

| VVAIT                                                                                                                                                                                                                                                                                                                                                                                                                   | OSC32K and AST stopped<br>Fast wake-up enable |                | 1.5µs                  | 4.3 | 240<br>276<br>276<br>270<br>112<br>119<br>128<br>138<br>627<br>739<br>445<br>564<br>381<br>442<br>55       |        |

| RETENTION                                                                                                                                                                                                                                                                                                                                                                                                               | OSC32K running<br>AST running at 1 kHz        | 25°C           | 1.5µs                  | 3.4 |                                                                                                            | _      |

|                                                                                                                                                                                                                                                                                                                                                                                                                         | AST and OSC32K stopped                        |                | -                      | 2.3 |                                                                                                            |        |

| BACKUP                                                                                                                                                                                                                                                                                                                                                                                                                  | OSC32K running<br>AST running at 1 kHz        |                |                        | 1.5 | 3.1                                                                                                        |        |

| SLEEP1<br>SLEEP2<br>SLEEP3<br>WAIT<br>RETENTION                                                                                                                                                                                                                                                                                                                                                                         | AST and OSC32K stopped                        |                |                        | 0.9 | 1.7                                                                                                        |        |

| Table 9-9. | ATSAM4L8 Current consumption and Wakeup time for power scaling mode 1 |

|------------|-----------------------------------------------------------------------|

|------------|-----------------------------------------------------------------------|

1. These values are based on characterization. These values are not covered by test limits in production.

- Atmel

## Table 9-10. Typical Power Consumption running CoreMark on CPU clock sources<sup>(1)</sup>

| Clock Source | Conditions | Regulator | Frequency<br>(MHz) | Тур | Unit |  |

|--------------|------------|-----------|--------------------|-----|------|--|

|--------------|------------|-----------|--------------------|-----|------|--|

| RCSYS<br>(MCSEL = 0)                                                    | Power scaling mode 1                                         |           | 0.115 | 978 |        |

|-------------------------------------------------------------------------|--------------------------------------------------------------|-----------|-------|-----|--------|

|                                                                         | Dever eesting mode 4                                         |           | 0.5   | 354 |        |

| OSC0                                                                    | Power scaling mode 1                                         |           | 12    | 114 |        |

| (MCSEL = 1)                                                             | Power scaling mode 0                                         |           | 12    | 228 |        |

|                                                                         | Power scaling mode 0                                         |           | 30    | 219 |        |

| OSC0<br>(MCSEL = 1)<br>External Clock<br>(MODE=0)<br>PLL<br>(MCSEL = 2) | Power scaling mode 1                                         |           | 0.6   | 292 |        |

| (MCSEL = 1)                                                             | Power scaling mode 1                                         |           | 12    | 111 |        |

| (MCSEL = 1)<br>External Clock<br>(MODE=0)<br>PLL<br>(MCSEL = 2)         | Power scaling mode 0                                         |           | 12    | 193 |        |

|                                                                         | Power scaling mode 2                                         |           | 50    | 194 |        |

| PLL                                                                     | Power scaling mode 2                                         | Switching | 40    | 188 | µA/MHz |

| (MCSEL = 2)                                                             | Input Freq = 4MHz from OSC0                                  | Mode      | 50    | 185 |        |

| DFLL                                                                    | Power scaling mode 0<br>Input Freq = 32kHz from OSC32K       |           | 20    | 214 |        |

| (MCSEL = 3)                                                             | Power scaling mode 2<br>Input Freq = 32kHz from OSC32K       |           | 50    | 195 |        |

| RC1M<br>(MCSEL = 4)                                                     | Power scaling mode 1                                         |           | 1     | 267 |        |

| RCFAST                                                                  | Power scaling mode 1                                         |           | 4     | 153 |        |

| (MCSEL = 5)                                                             | RCFAST frequency is configurable from 4 to 12MHz             |           | 12    | 114 |        |

| RC80M<br>(MCSEL = 6)                                                    | Power scaling mode 2<br>f <sub>CPU</sub> = RC80M / 2 = 40MHz |           | 40    | 211 |        |

| Table 9-10. | Typical Power Consumption running CoreMark on CPU clock sources <sup>(1)</sup> |

|-------------|--------------------------------------------------------------------------------|

|             | i jpicari enerie enerie ann piciri ranning e erennant en er e ereen eeu        |

1. These values are based on characterization. These values are not covered by test limits in production.

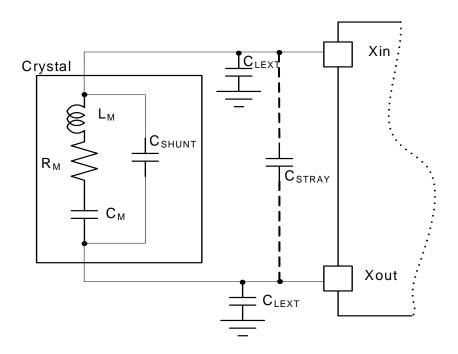

Table 9-23.

Crystal Oscillator Characteristics

| Symbol               | Parameter                                | Conditions                                        | Min | Тур                  | Мах | Unit   |

|----------------------|------------------------------------------|---------------------------------------------------|-----|----------------------|-----|--------|

| CL                   | Crystal load capacitance <sup>(1)</sup>  |                                                   | 6   |                      | 18  |        |

| C <sub>SHUNT</sub>   | Crystal shunt capacitance <sup>(1)</sup> |                                                   |     |                      | 7   |        |

| C <sub>XIN</sub>     | Parasitic capacitor load <sup>(2)</sup>  |                                                   |     | 4.91                 |     | рF     |

| C <sub>XOUT</sub>    | Parasitic capacitor load <sup>(2)</sup>  | TQFP100 package                                   |     | 3.22                 |     | -      |

| t <sub>STARTUP</sub> | Startup time <sup>(1)</sup>              | SCIF.OSCCTRL.GAIN = 2                             |     | 30000 <sup>(3)</sup> |     | cycles |

|                      |                                          | Active mode, f = 0.6MHz,<br>SCIF.OSCCTRL.GAIN = 0 |     | 30                   |     |        |

|                      |                                          | Active mode, f = 4MHz,<br>SCIF.OSCCTRL.GAIN = 1   |     | 130                  |     |        |

| I <sub>OSC</sub>     | Current consumption <sup>(1)</sup>       | Active mode, f = 8MHz,<br>SCIF.OSCCTRL.GAIN = 2   |     | 260                  |     | μA     |

|                      |                                          | Active mode, f = 16MHz,<br>SCIF.OSCCTRL.GAIN = 3  |     | 590                  |     |        |

|                      |                                          | Active mode, f = 30MHz,<br>SCIF.OSCCTRL.GAIN = 4  |     | 960                  |     |        |

1. These values are based on simulation. These values are not covered by test limits in production or characterization.

2. These values are based on characterization. These values are not covered by test limits in production.

3. Nominal crystal cycles.

#### Figure 9-3. Oscillator Connection

Atmel

#### **Analog Characteristics** 9.9

#### 9.9.1

Voltage Regulator Characteristics6. VREG Electrical Characteristics in Linear and Switching Modes Table 9-36.

| Symbol               | Parameter                                                    | Conditions                          | Min         | Тур  | Max   | Units |

|----------------------|--------------------------------------------------------------|-------------------------------------|-------------|------|-------|-------|

|                      |                                                              | Low power mode (WAIT)               | 2000        | 3600 | 5600  |       |

|                      | DC output current <sup>(1)</sup><br>Power scaling mode 0 & 2 | Ultra Low power mode<br>(RETENTION) | 100 180 300 |      |       |       |

| OUT                  | DC output current <sup>(1)</sup><br>Power scaling mode 1     | Low power mode (WAIT)               | 4000        | 7000 | 10000 | μA    |

|                      |                                                              | Ultra Low power mode<br>(RETENTION) | 200         | 350  | 600   |       |

| V <sub>VDDCORE</sub> | DC output voltage                                            | All modes                           |             |      | 1.9   | V     |

1. These values are based on simulation. These values are not covered by test limits in production.

## Table 9-37. VREG Electrical Characteristics in Linear mode

| Symbol               | Parameter                                                             | Conditions                                                                | Min   | Тур   | Max   | Units |

|----------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------|-------|-------|-------|-------|

| M                    | Input veltage renge                                                   | I <sub>OUT</sub> =10mA                                                    | 1.68  |       | 3.6   |       |

| V <sub>VDDIN</sub>   | Input voltage range                                                   | I <sub>OUT</sub> =50mA                                                    | 1.8   |       | -     | V     |

| M                    | DC output voltage <sup>(1)</sup>                                      | I <sub>OUT</sub> = 0 mA                                                   | 1.777 | 1.814 | 1.854 |       |

| V <sub>VDDCORE</sub> | Power scaling mode 0 & 2                                              | I <sub>OUT</sub> = 50 mA                                                  | 1.75  | 1.79  | 1.83  |       |

| I <sub>OUT</sub>     | DC output current <sup>(1)</sup>                                      | V <sub>VDDCORE</sub> > 1.65V                                              |       |       | 100   | mA    |

|                      | Output DC load regulation <sup>(1)</sup><br>Transient load regulation | $I_{OUT} = 0$ to 80 mA,<br>$V_{VDDIN} = 3 V$                              | -34   | -27   | -19   | mV    |

|                      | Output DC regulation <sup>(1)</sup>                                   | $I_{OUT} = 80 \text{ mA},$<br>$V_{VDDIN} = 2 \text{ V to } 3.6 \text{ V}$ | 10    | 28    | 48    | mV    |

| Ι <sub>Q</sub>       | Quescient current <sup>(1)</sup>                                      | I <sub>OUT</sub> = 0 mA<br>RUN and SLEEPx modes                           | 88    | 107   | 128   | μA    |

1. These values are based on characterization. These values are not covered by test limits in production.

#### Table 9-38. External components requirements in Linear Mode

| Symbol            | Parameter                    | Technology                                                                 | Тур | Units |

|-------------------|------------------------------|----------------------------------------------------------------------------|-----|-------|

| C <sub>IN1</sub>  | Input regulator capacitor 1  |                                                                            | 33  | nF    |

| C <sub>IN2</sub>  | Input regulator capacitor 2  |                                                                            | 100 | nr.   |

| C <sub>IN3</sub>  | Input regulator capacitor 3  |                                                                            | 10  | μF    |

| C <sub>OUT1</sub> | Output regulator capacitor 1 |                                                                            | 100 | nF    |

| C <sub>OUT2</sub> | Output regulator capacitor 2 | Tantalum or MLCC<br>0.5 <esr<10ω< td=""><td>4.7</td><td>μF</td></esr<10ω<> | 4.7 | μF    |

#### Table 9-39. VREG Electrical Characteristics in Switching mode

| Symbol             | Parameter                        | Conditions                                           | Min  | Тур  | Max  | Units |

|--------------------|----------------------------------|------------------------------------------------------|------|------|------|-------|

| V <sub>VDDIN</sub> | Input voltage range              | V <sub>VDDCORE</sub> = 1.65V, I <sub>OUT</sub> =50mA | 2.0  |      | 3.6  |       |

| V                  | DC output voltage <sup>(1)</sup> | I <sub>OUT</sub> = 0 mA                              | 1.75 | 1.82 | 1.87 | V     |

| VVDDCORE           | Power scaling mode 0 & 2         | I <sub>OUT</sub> = 50 mA                             | 1.66 | 1.71 | 1.79 |       |

| Symbol | Parameter                         | Conditions                           | Min                                                                       | Мах    | Units |

|--------|-----------------------------------|--------------------------------------|---------------------------------------------------------------------------|--------|-------|

| USPI6  | SPCK falling to MISO delay        |                                      |                                                                           | 593.9  |       |

| USPI7  | MOSI setup time before SPCK rises |                                      | $45.93 + t_{SAMPLE}^{(2)} + t_{CLK\_USART}$                               |        |       |

| USPI8  | MOSI hold time after SPCK rises   |                                      | 47.03 -( t <sub>SAMPLE</sub> <sup>(2)</sup> +<br>t <sub>CLK_USART )</sub> |        |       |

| USPI9  | SPCK rising to MISO delay         | V <sub>VDDIO</sub> from              |                                                                           | 593.38 |       |

| USPI10 | MOSI setup time before SPCK falls | 3.0V to 3.6V,<br>maximum<br>external | 45.93 +( $t_{SAMPLE}^{(2)}$ +<br>$t_{CLK_USART}$ )                        |        | ns    |

| USPI11 | MOSI hold time after SPCK falls   | capacitor =<br>40pF                  | 47.03 -( t <sub>SAMPLE</sub> <sup>(2)</sup> +<br>t <sub>CLK_USART</sub> ) |        |       |

| USPI12 | NSS setup time before SPCK rises  |                                      | 237.5                                                                     |        |       |

| USPI13 | NSS hold time after SPCK falls    |                                      | -1.81                                                                     |        |       |

| USPI14 | NSS setup time before SPCK falls  |                                      | 237.5                                                                     |        | 1     |

| USPI15 | NSS hold time after SPCK rises    |                                      | -1.81                                                                     |        |       |

Table 9-61.

USART3 in SPI mode Timing, Slave Mode<sup>(1)</sup>

Notes: 1. These values are based on simulation. These values are not covered by test limits in production.

2. Where:

$$t_{SAMPLE} = t_{SPCK} - \left( \left\lfloor \frac{t_{SPCK}}{2 \times t_{CLKUSART}} \right\rfloor + \frac{1}{2} \right) \times t_{CLKUSART}$$

#### Maximum SPI Frequency, Slave Input Mode

The maximum SPI slave input frequency is given by the following formula:

$$f_{SPCKMAX} = MIN(\frac{f_{CLKSPI} \times 2}{9}, \frac{1}{SPIn})$$

Where *SPIn* is the MOSI setup and hold time, USPI7 + USPI8 or USPI10 + USPI11 depending on CPOL and NCPHA.  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.

#### Maximum SPI Frequency, Slave Output Mode

The maximum SPI slave output frequency is given by the following formula:

Atmel

$$f_{SPCKMAX} = MIN(\frac{f_{CLKSPI} \times 2}{9}, f_{PINMAX}, \frac{1}{SPIn + t_{SETUP}})$$

Where *SPIn* is the MISO delay, USPI6 or USPI9 depending on CPOL and NCPHA.  $T_{SETUP}$  is the SPI master setup time. refer to the SPI master datasheet for  $T_{SETUP}$ .  $f_{CLKSPI}$  is the maximum frequency of the CLK\_SPI. Refer to the SPI chapter for a description of this clock.  $f_{PINMAX}$  is the maximum frequency of the SPI pins. refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

Where *SPIn* is the MISO delay, SPI6 or SPI9 depending on CPOL and NCPHA.  $t_{SETUP}$  is the SPI master setup time. refer to the SPI master datasheet for  $t_{SETUP}$ .  $f_{PINMAX}$  is the maximum frequency of the SPI pins. refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

#### 9.10.4 TWIM/TWIS Timing

Figure 9-64 shows the TWI-bus timing requirements and the compliance of the device with them. Some of these requirements ( $t_r$  and  $t_f$ ) are met by the device without requiring user intervention. Compliance with the other requirements ( $t_{HD-STA}$ ,  $t_{SU-STA}$ ,  $t_{SU-STO}$ ,  $t_{HD-DAT}$ ,  $t_{SU-DAT-TWI}$ ,  $t_{LOW-TWI}$ ,  $t_{HIGH}$ , and  $f_{TWCK}$ ) requires user intervention through appropriate programming of the relevant TWIM and TWIS user interface registers. refer to the TWIM and TWIS sections for more information.

|                         |                                 |                         | Minim       | num                 | Maximum            |                                               |      |

|-------------------------|---------------------------------|-------------------------|-------------|---------------------|--------------------|-----------------------------------------------|------|

| Symbol                  | Parameter                       | Mode                    | Requirement | Device              | Requirement        | Device                                        | Unit |

|                         |                                 | Standard <sup>(1)</sup> | -           |                     | 1000               |                                               |      |

| t <sub>r</sub>          | TWCK and TWD rise time          | Fast <sup>(1)</sup>     | 20 + 0      | .1C <sub>b</sub>    | 30                 | ns                                            |      |

|                         |                                 | Standard                | -           |                     | 300                |                                               |      |

| t <sub>f</sub>          | TWCK and TWD fall time          | Fast                    | 20 + 0      | .1C <sub>b</sub>    | 30                 | ns                                            |      |

| +                       | (Dependented) STADT hold time   | Standard                | 4           |                     |                    |                                               |      |

| t <sub>HD-STA</sub>     | (Repeated) START hold time      | Fast                    | 0.6         | t <sub>clkpb</sub>  | -                  |                                               | μs   |

| +                       | (Dependented) STADT act up time | Standard                | 4.7         |                     |                    |                                               |      |

| t <sub>SU-STA</sub>     | (Repeated) START set-up time    | Fast                    | 0.6         | t <sub>clkpb</sub>  | -                  |                                               | μs   |

| +                       | STOD oot up time                | Standard                | 4.0         | 4+                  | -                  |                                               |      |

| t <sub>SU-STO</sub>     | STOP set-up time                | Fast                    | 0.6         | 4t <sub>clkpb</sub> |                    |                                               | μs   |

| +                       | Data hold time                  | Standard                | 0.3(2)      | 2+                  | 3.45 <sup>()</sup> | 15+ +                                         |      |

| t <sub>HD-DAT</sub>     |                                 | Fast                    | 0.317       | 2t <sub>clkpb</sub> | 0.9()              | 15t <sub>prescaled</sub> + t <sub>clkpb</sub> | μs   |

| +                       | Data set-up time                | Standard                | 250         | 2+                  |                    |                                               |      |

| t <sub>SU-DAT-TWI</sub> | Data set-up time                | Fast                    | 100         | 2t <sub>clkpb</sub> | -                  |                                               | ns   |

| t <sub>SU-DAT</sub>     |                                 | -                       | -           | t <sub>clkpb</sub>  | -                  |                                               | -    |

| +                       | TWCK LOW period                 | Standard                | 4.7         | <i>/</i> +          |                    |                                               |      |

| t <sub>LOW-TWI</sub>    | TWOR LOW period                 | Fast                    | 1.3         | 4t <sub>clkpb</sub> | -                  |                                               | μs   |

| t <sub>LOW</sub>        |                                 | -                       | -           | t <sub>clkpb</sub>  | -                  |                                               | -    |

| +                       | TWCK HIGH period                | Standard                | 4.0         | Q+                  |                    |                                               |      |

| t <sub>HIGH</sub>       |                                 | Fast                    | 0.6         | 8t <sub>clkpb</sub> | -                  |                                               | μs   |

| f                       | TWCK frequency                  | Standard                |             |                     | 100                | 1                                             | kHz  |

| f <sub>TWCK</sub>       |                                 | Fast                    | -           |                     | 400                | <sup>12t</sup> clkpb                          | KIIZ |

**Table 9-64.**TWI-Bus Timing Requirements

Notes: 1. Standard mode:  $f_{TWCK} \le 100 \text{ kHz}$ ; fast mode:  $f_{TWCK} > 100 \text{ kHz}$ .

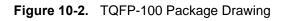

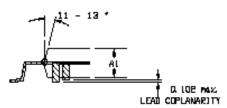

| SYMBOL | Min   | NOTES |  |  |  |  |

|--------|-------|-------|--|--|--|--|

| A      |       | 1. 20 |  |  |  |  |

| A1     | D. 95 | 1. 05 |  |  |  |  |

| С      | D. D9 | 0, 20 |  |  |  |  |

| п      | 16. O |       |  |  |  |  |

| D1     | 14, 0 |       |  |  |  |  |

| E      | 16. 0 |       |  |  |  |  |

| E 1    | 14. O |       |  |  |  |  |

| J      | D. D5 | 0.15  |  |  |  |  |

| L      | 0, 45 | D. 75 |  |  |  |  |

| e      | 0, 5  | O BSC |  |  |  |  |

| f      | 0, 17 |       |  |  |  |  |

| COMMON | DIMENSIONS IN MM |

|--------|------------------|

|        |                  |

| Table 10-5. | Device and Package Maximum Weight |

|-------------|-----------------------------------|

|-------------|-----------------------------------|

| 500         |                         | mg |

|-------------|-------------------------|----|

| Table 10-6. | Package Characteristics |    |

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

|----------------------------|------|

### Table 10-7. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

| Table 11-3. AT SAM4LOZ SUD Selle Oldening Informatio | Table 11-3. | ATSAM4LC2 Sub Serie Ordering Information |

|------------------------------------------------------|-------------|------------------------------------------|

|------------------------------------------------------|-------------|------------------------------------------|

| Ordering Code    | Flash<br>(Kbytes) | RAM<br>(Kbytes) | Package  | Conditioning | Package<br>Type | Temperature Operating<br>Range |

|------------------|-------------------|-----------------|----------|--------------|-----------------|--------------------------------|

| ATSAM4LC2CA-AU   |                   |                 |          | Tray         |                 |                                |

| ATSAM4LC2CA-AUR  | 128               |                 | TQFP100  | Reel         | Green           | Industrial -40°C to 85°C       |

| ATSAM4LC2CA-CFU  |                   | 32              | VFBGA100 | Tray         |                 |                                |

| ATSAM4LC2CA-CFUR |                   |                 |          | Reel         |                 |                                |

| ATSAM4LC2BA-AU   |                   |                 | TQFP64   | Tray         |                 |                                |

| ATSAM4LC2BA-AUR  |                   |                 |          | Reel         |                 |                                |

| ATSAM4LC2BA-MU   |                   |                 | QFN64    | Tray         |                 |                                |

| ATSAM4LC2BA-MUR  |                   |                 |          | Reel         |                 |                                |