Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB                       |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 80                                                                         |

| Program Memory Size        | 512KB (512K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 64K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.68V ~ 3.6V                                                               |

| Data Converters            | A/D 15x12b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-VFBGA                                                                  |

| Supplier Device Package    | 100-VFBGA (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam4ls8ca-cfur |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

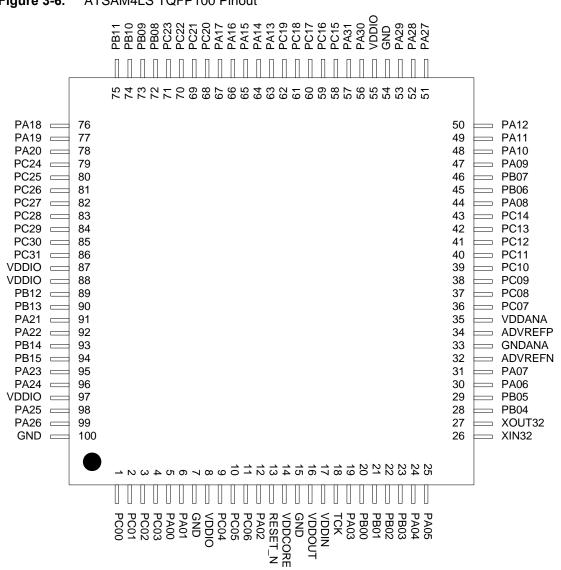

### 3.1.2 ATSAM4LSx Pinout

Atmel

Figure 3-6. ATSAM4LS TQFP100 Pinout

14

ATSAM4L8/L4/L2

Figure 3-8. ATSA

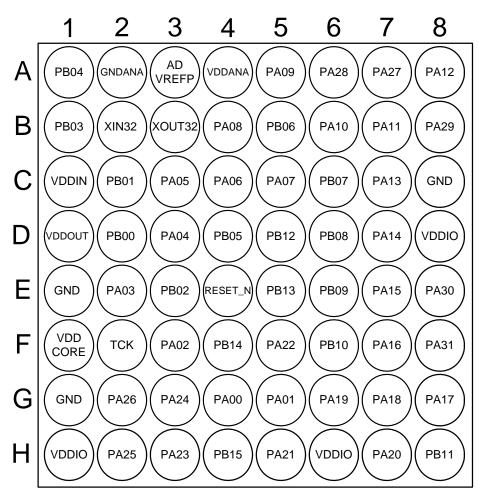

B. ATSAM4LS WLCSP64 Pinout

- Atmel

| ATSAM4LC | ATSAM4LS | Pin  | GPIO | Supply |               |                 | G                | PIO Functio     | ns                |                |                 |

|----------|----------|------|------|--------|---------------|-----------------|------------------|-----------------|-------------------|----------------|-----------------|

| WLCSP    |          |      |      |        | Α             | В               | С                | D               | E                 | F              | G               |

| G4       | G4       | PA00 | 0    | VDDIO  |               |                 |                  |                 |                   |                |                 |

| G5       | G5       | PA01 | 1    | VDDIO  |               |                 |                  |                 |                   |                |                 |

| F3       | F3       | PA02 | 2    | VDDIN  | SCIF<br>GCLK0 | SPI<br>NPCS0    |                  |                 |                   |                | CATB<br>DIS     |

| E2       | E2       | PA03 | 3    | VDDIN  |               | SPI<br>MISO     |                  |                 |                   |                |                 |

| D3       | D3       | PA04 | 4    | VDDANA | ADCIFE<br>AD0 | USART0<br>CLK   | EIC<br>EXTINT2   | GLOC<br>IN1     |                   |                | CATB<br>SENSE0  |

| C3       | C3       | PA05 | 5    | VDDANA | ADCIFE<br>AD1 | USART0<br>RXD   | EIC<br>EXTINT3   | GLOC<br>IN2     | ADCIFE<br>TRIGGER |                | CATB<br>SENSE1  |

| C4       | C4       | PA06 | 6    | VDDANA | DACC<br>VOUT  | USART0<br>RTS   | EIC<br>EXTINT1   | GLOC<br>IN0     | ACIFC<br>ACAN0    |                | CATB<br>SENSE2  |

| C5       | C5       | PA07 | 7    | VDDANA | ADCIFE<br>AD2 | USART0<br>TXD   | EIC<br>EXTINT4   | GLOC<br>IN3     | ACIFC<br>ACAP0    |                | CATB<br>SENSE3  |

| B4       | B4       | PA08 | 8    | LCDA   | USART0<br>RTS | TC0<br>A0       | PEVC<br>PAD EVT0 | GLOC<br>OUT0    |                   | LCDCA<br>SEG23 | CATB<br>SENSE4  |

| A5       | A5       | PA09 | 9    | LCDA   | USART0<br>CTS | ТС0<br>В0       | PEVC<br>PAD EVT1 | PARC<br>PCDATA0 |                   | LCDCA<br>COM3  | CATB<br>SENSE5  |

| В6       | В6       | PA10 | 10   | LCDA   | USART0<br>CLK | TC0<br>A1       | PEVC<br>PAD EVT2 | PARC<br>PCDATA1 |                   | LCDCA<br>COM2  | CATB<br>SENSE6  |

| B7       | B7       | PA11 | 11   | LCDA   | USART0<br>RXD | TC0<br>B1       | PEVC<br>PAD EVT3 | PARC<br>PCDATA2 |                   | LCDCA<br>COM1  | CATB<br>SENSE7  |

| A8       | A8       | PA12 | 12   | LCDA   | USART0<br>TXD | TC0<br>A2       |                  | PARC<br>PCDATA3 |                   | LCDCA<br>COM0  | CATB<br>DIS     |

| C7       | С7       | PA13 | 13   | LCDA   | USART1<br>RTS | TC0<br>B2       | SPI<br>NPCS1     | PARC<br>PCDATA4 |                   | LCDCA<br>SEG5  | CATB<br>SENSE8  |

| D7       | D7       | PA14 | 14   | LCDA   | USART1<br>CLK | TC0<br>CLK0     | SPI<br>NPCS2     | PARC<br>PCDATA5 |                   | LCDCA<br>SEG6  | CATB<br>SENSE9  |

| E7       | E7       | PA15 | 15   | LCDA   | USART1<br>RXD | TC0<br>CLK1     | SPI<br>NPCS3     | PARC<br>PCDATA6 |                   | LCDCA<br>SEG7  | CATB<br>SENSE10 |

| F7       | F7       | PA16 | 16   | LCDA   | USART1<br>TXD | TC0<br>CLK2     | EIC<br>EXTINT1   | PARC<br>PCDATA7 |                   | LCDCA<br>SEG8  | CATB<br>SENSE11 |

| G8       | G8       | PA17 | 17   | LCDA   | USART2<br>RTS | ABDACB<br>DAC0  | EIC<br>EXTINT2   | PARC<br>PCCK    |                   | LCDCA<br>SEG9  | CATB<br>SENSE12 |

| G7       | G7       | PA18 | 18   | LCDA   | USART2<br>CLK | ABDACB<br>DACN0 | EIC<br>EXTINT3   | PARC<br>PCEN1   |                   | LCDCA<br>SEG18 | CATB<br>SENSE13 |

| G6       | G6       | PA19 | 19   | LCDA   | USART2<br>RXD | ABDACB<br>DAC1  | EIC<br>EXTINT4   | PARC<br>PCEN2   | SCIF<br>GCLK0     | LCDCA<br>SEG19 | CATB<br>SENSE14 |

| H7       | H7       | PA20 | 20   | LCDA   | USART2<br>TXD | ABDACB<br>DACN1 | EIC<br>EXTINT5   | GLOC<br>IN0     | SCIF<br>GCLK1     | LCDCA<br>SEG20 | CATB<br>SENSE15 |

| H5       | H5       | PA21 | 21   | LCDC   | SPI<br>MISO   | USART1<br>CTS   | EIC<br>EXTINT6   | GLOC<br>IN1     | TWIM2<br>TWD      | LCDCA<br>SEG34 | CATB<br>SENSE16 |

| F5       | F5       | PA22 | 22   | LCDC   | SPI<br>MOSI   | USART2<br>CTS   | EIC<br>EXTINT7   | GLOC<br>IN2     | TWIM2<br>TWCK     | LCDCA<br>SEG35 | CATB<br>SENSE17 |

Table 3-3.

64-pin GPIO Controller Function Multiplexing for WLCSP package (Sheet 1 of 3)

### 3.2.4 ITM Trace Connections

If the ITM trace is enabled, the ITM will take control over the pin PA23, irrespectively of the I/O Controller configuration. The Serial Wire Trace signal is available on pin PA23

### 3.2.5 Oscillator Pinout

The oscillators are not mapped to the normal GPIO functions and their muxings are controlled by registers in the System Control Interface (SCIF) or Backup System Control Interface (BSCIF). Refer to the Section 15. "System Control Interface (SCIF)" on page 308 and Section 15. "Backup System Control Interface (BSCIF)" on page 308 for more information about this.

|   | 48-pin Packages | 64-pin QFN/QFP | 64-pin WLCSP | 100-pin Packages | 100-ball VFBGA | Pin Name | Oscillator Pin |

|---|-----------------|----------------|--------------|------------------|----------------|----------|----------------|

|   | 1               | 1              | G4           | 5                | B9             | PA00     | XIN0           |

|   | 13              | 17             | B2           | 26               | B2             | XIN32    | XIN32          |

|   | 2               | 2              | G5           | 6                | B8             | PA01     | XOUT0          |

| , | 14              | 18             | B3           | 27               | C2             | XOUT32   | XOUT32         |

Table 3-7.Oscillator Pinout

### 7.1.4 Wakeup Time

7.1.4.1 Wakeup Time From SLEEP Mode

The latency depends on the clock sources wake up time. If the clock sources are not stopped, there is no latency to wake the clocks up.

7.1.4.2 Wakeup Time From WAIT or RETENTION Mode

The wake up latency consists of:

- the switching time from the low power configuration to the RUN mode power configuration. By default, the switching time is completed when all the voltage regulation system is ready. To speed-up the startup time, the user can set the Fast Wakeup bit in BPM.PMCON register.

- the wake up time of the RC oscillator used to start the system up. By default, the RCSYS oscillator is used to startup the system. The user can use another clock source (RCFAST for example) to speed up the startup time by configuring the PM.FASTWKUP register. Refer to Section 9. "Power Manager (PM)" on page 677.

- the Flash memory wake up time.

To have the shortest wakeup time, the user should:

Atmel

- set the BPM.PMCON.FASTWKUP bit.

- configure the PM.FASTSLEEP.FASTRCOSC field to use the RCFAST main clock.

- enter the WAIT or RETENTION mode

Upon a wakeup, this is required to keep the main clock connected to RCFAST until the voltage regulation system is fully ready (when BPM.ISR.PSOK bit is one). During this wakeup period, the FLASHCALW module is automatically configured to operate in "1 wait state mode".

### 7.1.4.3 Wake time from BACKUP mode

It is equal to the Core domain logic reset latency (similar to the reset latency caused by an external reset in RESET\_N pin) added to the time required for the voltage regulation system to be stabilized.

### 8.7.12 JTAG Instructions Summary

The implemented JTAG instructions are shown in the table below.

|                      |                | Implemented JTAG Instructions list                                                        |                                   |                          |

|----------------------|----------------|-------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|

| IR instruction value | Instruction    | Description                                                                               | availability<br>when<br>protected | Component                |

| b0000                | EXTEST         | Select boundary-scan chain as data register for testing circuitry external to the device. | yes                               |                          |

| b0001                | SAMPLE_PRELOAD | Take a snapshot of external pin values without affecting system operation.                | yes                               |                          |

| b0100                | INTEST         | Select boundary-scan chain for internal testing of the device.                            | yes                               |                          |

| b0101                | CLAMP          | Bypass device through Bypass register, while driving outputs from boundary-scan register. | yes                               | BSCAN-TAP                |

| b1000                | ABORT          | ARM JTAG-DP Instruction                                                                   | yes                               |                          |

| b1010                | DPACC          | ARM JTAG-DP Instruction                                                                   | yes                               |                          |

| b1011                | APACC          | ARM JTAG-DP Instruction                                                                   | yes                               |                          |

| b1100                | -              | Reserved                                                                                  | yes                               | SWJ-DP<br>(in JTAG mode) |

| b1101                | -              | Reserved                                                                                  | yes                               |                          |

| b1110                | IDCODE         | ARM JTAG-DP Instruction                                                                   | yes                               |                          |

| b1111                | BYPASS         | Bypass this device through the bypass register.                                           | yes                               |                          |

Table 8-2.

Implemented JTAG instructions list

### 8.9.9 Unlimited Flash User Page Read Access

The SMAP can access the User page even if the protected state is set. Prior to operate such an access, the user should check that the module is not busy by checking that SR.STATE is equal to zerp. Once the offset of the word to access inside the page is written in ADDR.ADDR, the read operation can be initiated by writing a one in CR.FSPR. The SR.STATE field will indicate the FSPR state. Addresses written to ADDR.ADDR must be world aligned. Failing to do so will result in unpredictable behavior. The result can be read in the DATA register as soon as SR.DONE rises. The ADDR field is used as an offset in the page, bits outside a page boundary will be silently discarded. The ADDR register is automatically incremented at the end of the read operation making possible to dump consecutive words without writing the next offset into ADDR.ADDR.

### 8.9.10 32-bit Cyclic Redundancy Check (CRC)

The SMAP unit provides support for calculating a Cyclic Redundancy Check (CRC) value for a memory area. The algorithm used is the industry standard CRC32 algorithm using the generator polynomial 0xEDB88320.

### 8.9.10.1 Starting CRC Calculation

To calculate CRC for a memory range, the start address must be written into the ADDR register, and the size of the memory range into the LENGTH register. Both the start address and the length must be word aligned.

The initial value used for the CRC calculation must be written to the DATA register. This value will usually be 0xFFFFFFF, but can be e.g. the result of a previous CRC calculation if generating a common CRC of separate memory blocks.

Once completed, the calculated CRC value can be read out of the DATA register. The read value must be inverted to match standard CRC32 implementations, or kept non-inverted if used as starting point for subsequent CRC calculations.

If the device is in protected state, it is only possible to calculate the CRC of the whole flash array. In most cases this area will be the entire onboard nonvolatile memory. The ADDR, LENGTH, and DATA registers will be forced to predefined values once the CRC operation is started, and user-written values are ignored. This allows the user to verify the contents of a protected device.

The actual test is started by writing a one in CR.CRC. A running CRC operation can be cancelled by disabling the module (write a one in CR.DIS). This has the effect of resetting the module. The module has to be restarted by issuing an enable command (write a one in CR.EN).

### 8.9.10.2 Interpreting the Results

The user should monitor the SR register (Refer to Section 8.9.11.2 "Status Register" on page 83). When the operation is completed SR.DONE is set. Then the SR.BERR and SR.FAIL must be read to ensure that no bus error nor functional error occured.

Atmel

| 8.9.11.1   | Contr | ol Register |

|------------|-------|-------------|

| Name:      |       | CR          |

| Access Ty  | pe:   | Write-Only  |

| Offset:    |       | 0x00        |

| Reset Valu | e:    | 0x0000000   |

| 31 | 30 | 29 | 28 | 27   | 26  | 25  | 24 |

|----|----|----|----|------|-----|-----|----|

| -  | -  | -  | -  | -    | -   | -   | -  |

|    |    |    |    |      |     |     |    |

| 23 | 22 | 21 | 20 | 19   | 18  | 17  | 16 |

| -  | -  | -  | -  | -    | -   | -   | -  |

|    |    |    |    |      |     |     |    |

| 15 | 14 | 13 | 12 | 11   | 10  | 9   | 8  |

| -  | -  | -  | -  | -    | -   | -   | -  |

|    |    |    |    |      |     |     |    |

| 7  | 6  | 5  | 4  | 3    | 2   | 1   | 0  |

| -  | -  | -  | CE | FSPR | CRC | DIS | EN |

Writing a zero to a bit in this register has no effect.

### • CE: Chip Erase

Writing a one to this bit triggers the FLASH Erase All (EA) operation which clears all volatile memories, the whole flash array, the general purpose fuses and the protected state. The Status register DONE field indicates the completion of the operation. Reading this bit always returns 0

### • FSPR: Flash User Page Read

Writing a one to this bit triggers a read operation in the User page. The word pointed by the ADDR register in the page is read and written to the DATA register. ADDR is post incremented allowing a burst of reads without modifying ADDR. SR.DONE must be read high prior to reading the DATA register.

Reading this bit always returns 0

### CRC: Cyclic Redundancy Code

Writing a one triggers a CRC calculation over a memory area defined by the ADDR and LENGTH registers. Reading this bit always returns 0

Note: This feature is restricted while in protected state

### DIS: Disable

Writing a one to this bit disables the module. Disabling the module resets the whole module immediately.

Atmel

#### • EN: Enable

Writing a one to this bit enables the module.

| 8.9.11.10  | Identific | ation Register |

|------------|-----------|----------------|

| Name:      |           | IDR            |

| Access Ty  | pe:       | Read-Only      |

| Offset:    |           | 0xFC           |

| Reset Valu | e:        | -              |

| 31 | 30   | 29   | 28   | 27   | 26 | 25  | 24   |

|----|------|------|------|------|----|-----|------|

|    | REVI | SION |      |      | С  | С   |      |

|    |      |      |      |      |    |     |      |

| 23 | 22   | 21   | 20   | 19   | 18 | 17  | 16   |

|    |      |      | IC   |      |    |     | CLSS |

|    |      |      |      |      |    |     |      |

| 15 | 14   | 13   | 12   | 11   | 10 | 9   | 8    |

|    |      |      | Rese | rved |    |     |      |

|    |      |      |      |      |    |     |      |

| 7  | 6    | 5    | 4    | 3    | 2  | 1   | 0    |

|    | AF   | PID  |      |      | AP | IDV |      |

- **REVISION:** Revision

- CC: JEP-106 Continuation Code

Atmel continuation code is 0x0

- IC: JEP-106 Identity Code

Atmel identification code is 0x1F

- CLSS: Class

- 0: This AP is not a Memory Access Port

- 1: This AP is a Memory Access Port

- APID: AP Identification

- APIDV: AP Identification Variant

For more information about this register, refer to the ARM Debug Interface v5.1 Architecture Specification document.

# 9. Electrical Characteristics

# 9.1 Absolute Maximum Ratings\*

Table 9-1.

Absolute Maximum Ratings

| Operating temperature40°C to +85°C<br>Storage temperature                          | *NOTICE:                                | Stresses beyond those listed under "Absolute Maxi-<br>mum Ratings" may cause permanent damage to the                                                                     |

|------------------------------------------------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Voltage on input pins with respect to ground0.3V to $V_{VDD}$ <sup>(1)</sup> +0.3V | beyond those indicated in the operation | operation of the device at these or other conditions<br>beyond those indicated in the operational sections of<br>this specification is not implied. Exposure to absolute |

| Total DC output current on all I/O pins<br>VDDIO                                   |                                         | maximum rating conditions for extended periods may<br>affect device reliability.                                                                                         |

| Total DC output current on all I/O pins<br>VDDIN                                   |                                         |                                                                                                                                                                          |

| Total DC output current on all I/O pins<br>VDDANA                                  |                                         |                                                                                                                                                                          |

| Maximum operating voltage VDDIO, VDDIN                                             |                                         |                                                                                                                                                                          |

1. V<sub>VDD</sub> corresponds to either V<sub>VDDIN</sub> or V<sub>VDDIO</sub>, depending on the supply for the pin. Refer to Section 3-5 on page 13 for details

## 9.2 Operating Conditions

All the electrical characteristics are applicable to the following conditions unless otherwise specified :

- operating voltage range 1,68V to 3,6V for VDDIN, VDDIO & VDDANA

- Power Scaling 0 and 2 modes

- operating temperature range: TA = -40°C to 85°C and for a junction temperature up to TJ = 100°C.

Typical values are base on TA =  $25^{\circ}$ c and VDDIN,VDDIO,VDDANA = 3,3V unless otherwise specified

# 9.3 Supply Characteristics

|                                                                   |                                       | Voltage |     |      |  |

|-------------------------------------------------------------------|---------------------------------------|---------|-----|------|--|

| Symbol                                                            | Conditions                            | Min     | Max | Unit |  |

| V <sub>VDDIO,</sub><br>V <sub>VDDIN,</sub><br>V <sub>VDDANA</sub> | PS1 (FCPU<=12MHz)<br>Linear mode      | 1.68    |     |      |  |

|                                                                   | PS0 & PS2 (FCPU>12MHz)<br>Linear mode | 1.8     | 3.6 | V    |  |

|                                                                   | Switching mode                        | 2.0 (1) |     |      |  |

**Table 9-2.**Supply Characteristics

1. Below 2.3V, linear mode is more power efficient than switching mode.

Atmel

Refer to Section 6. "Power and Startup Considerations" on page 46 for details about Power Supply

| Mode      | Conditions                                    | T <sub>A</sub> | Typical<br>Wakeup Time | Тур  | Max <sup>(1)</sup> | Unit |

|-----------|-----------------------------------------------|----------------|------------------------|------|--------------------|------|

| SLEEP0    | Switching mode                                | 25°C           | 9 * Main clock         | 3817 | 4033               |      |

| SLEEPU    | Switching mode                                | 85°C           | cycles                 | 3934 | 4174               |      |

|           |                                               | 25°C           | 9 * Main clock         | 2341 | 2477               |      |

| SLEEP1    | Switching mode                                | 85°C           | cycles + 500ns         | 2437 | 2585               | -    |

|           |                                               | 25°C           | 9 * Main clock         | 1758 | 1862               | -    |

| SLEEP2    | Switching mode                                | 85°C           | cycles + 500ns         | 1847 | 1971               |      |

| SLEEP3    | Linear mode                                   |                |                        | 51   | 60                 |      |

|           | OSC32K and AST running<br>Fast wake-up enable |                |                        | 5.9  | 8.7                | μA   |

| WAIT      | OSC32K and AST stopped<br>Fast wake-up enable |                | 1.5µs                  | 4.7  | 7.6                | •    |

| RETENTION | OSC32K running<br>AST running at 1kHz         | 25°C           | 1.5µs                  | 3.1  | 5.1                |      |

|           | AST and OSC32K stopped                        |                |                        | 2.2  | 4.2                | -    |

| BACKUP    | OSC32K running<br>AST running at 1 kHz        |                |                        | 1.5  | 3.1                |      |

|           | AST and OSC32K stopped                        |                |                        | 0.9  | 1.7                | Ī    |

Table 9-6.

ATSAM4L4/2 Current consumption and Wakeup time for power scaling mode 0 and 2

1. These values are based on characterization. These values are not covered by test limits in production.

| Table 9-7. | ATSAM4L8 Current consumption and Wakeup time for power scaling mode 0 and 2 |

|------------|-----------------------------------------------------------------------------|

|            |                                                                             |

| Mode | Conditions                        | T <sub>A</sub> | Typical<br>Wakeup Time | Тур | Max <sup>(1)</sup> | Unit   |

|------|-----------------------------------|----------------|------------------------|-----|--------------------|--------|

|      | CPU running a Fibonacci algorithm | 25°C           | N/A                    | 319 | 343                |        |

|      | Linear mode                       | 85°C           | N/A                    | 326 | 350                |        |

|      | CPU running a CoreMark algorithm  | 25°C           | N/A                    | 343 | 387                |        |

|      | Linear mode                       | 85°C           |                        | 351 | 416                |        |

| RUN  | CPU running a Fibonacci algorithm | 25°C           | N/A                    | 181 | 198                | µA/MHz |

|      | Switching mode                    | 85°C           |                        | 186 | 203                |        |

|      | CPU running a CoreMark algorithm  | 25°C           | N/A                    | 192 | 232                |        |

|      | Switching mode                    | 85°C           |                        | 202 | 239                |        |

- Atmel

# 9.10 Timing Characteristics

### 9.10.1 RESET\_N Timing

Table 9-53. RESET\_N Waveform Parameters (1)

| Symbol                                          | Parameter | Conditions | Min | Max | Units |

|-------------------------------------------------|-----------|------------|-----|-----|-------|

| t <sub>RESET</sub> RESET_N minimum pulse length |           |            | 10  |     | ns    |

1. These values are based on simulation. These values are not covered by test limits in production.

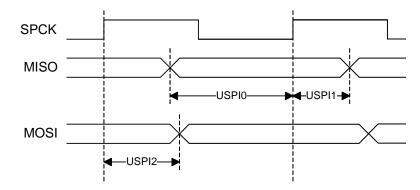

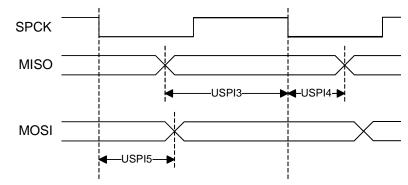

### 9.10.2 USART in SPI Mode Timing

9.10.2.1 Master mode

Figure 9-7. USART in SPI Master Mode with (CPOL= CPHA= 0) or (CPOL= CPHA= 1)

**Figure 9-8.** USART in SPI Master Mode with (CPOL= 0 and CPHA= 1) or (CPOL= 1 and CPHA= 0)

# ATSAM4L8/L4/L2

# Table 9-59. USART1 in SPI mode Timing, Slave Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions                           | Min                                                                       | Max    | Units |

|--------|-----------------------------------|--------------------------------------|---------------------------------------------------------------------------|--------|-------|

| USPI6  | SPCK falling to MISO delay        |                                      |                                                                           | 373.58 |       |

| USPI7  | MOSI setup time before SPCK rises |                                      | $4.16 + t_{SAMPLE}^{(2)} + t_{CLK_USART}$                                 |        |       |

| USPI8  | MOSI hold time after SPCK rises   |                                      | 46.69 -( t <sub>SAMPLE</sub> <sup>(2)</sup> +<br>t <sub>CLK_USART )</sub> |        |       |

| USPI9  | SPCK rising to MISO delay         | V <sub>VDDIO</sub> from              |                                                                           | 373.54 |       |

| USPI10 | MOSI setup time before SPCK falls | 3.0V to 3.6V,<br>maximum<br>external | $4.16 + (t_{SAMPLE}^{(2)} + t_{CLK_USART})$                               |        | ns    |

| USPI11 | MOSI hold time after SPCK falls   | capacitor =<br>40pF                  | 46.69 -( t <sub>SAMPLE</sub> <sup>(2)</sup> +<br>t <sub>CLK_USART )</sub> |        |       |

| USPI12 | NSS setup time before SPCK rises  |                                      | 200.43                                                                    |        |       |

| USPI13 | NSS hold time after SPCK falls    |                                      | -16.5                                                                     |        |       |

| USPI14 | NSS setup time before SPCK falls  |                                      | 200.43                                                                    |        |       |

| USPI15 | NSS hold time after SPCK rises    |                                      | -16.5                                                                     |        |       |

Table 9-60.

USART2 in SPI mode Timing, Slave Mode<sup>(1)</sup>

| Symbol | Parameter                         | Conditions                           | Min                                                                      | Max    | Units |

|--------|-----------------------------------|--------------------------------------|--------------------------------------------------------------------------|--------|-------|

| USPI6  | SPCK falling to MISO delay        |                                      |                                                                          | 770.02 |       |

| USPI7  | MOSI setup time before SPCK rises |                                      | 136.56 + $t_{SAMPLE}^{(2)}$ + $t_{CLK_USART}$                            |        |       |

| USPI8  | MOSI hold time after SPCK rises   |                                      | 47.9 -( t <sub>SAMPLE</sub> <sup>(2)</sup> +<br>t <sub>CLK_USART</sub> ) |        |       |

| USPI9  | SPCK rising to MISO delay         | V <sub>VDDIO</sub> from              |                                                                          | 570.19 |       |

| USPI10 | MOSI setup time before SPCK falls | 3.0V to 3.6V,<br>maximum<br>external | $136.73 + (t_{SAMPLE}^{(2)} + t_{CLK_USART})$                            |        | ns    |

| USPI11 | MOSI hold time after SPCK falls   | capacitor =<br>40pF                  | 47.9 -( t <sub>SAMPLE</sub> <sup>(2)</sup> +<br>t <sub>CLK_USART</sub> ) |        |       |

| USPI12 | NSS setup time before SPCK rises  |                                      | 519.87                                                                   |        |       |

| USPI13 | NSS hold time after SPCK falls    |                                      | -1.83                                                                    |        |       |

| USPI14 | NSS setup time before SPCK falls  |                                      | 519.87                                                                   |        |       |

| USPI15 | NSS hold time after SPCK rises    |                                      | -1.83                                                                    |        |       |

Where *SPIn* is the MISO delay, SPI6 or SPI9 depending on CPOL and NCPHA.  $t_{SETUP}$  is the SPI master setup time. refer to the SPI master datasheet for  $t_{SETUP}$ .  $f_{PINMAX}$  is the maximum frequency of the SPI pins. refer to the I/O Pin Characteristics section for the maximum frequency of the pins.

### 9.10.4 TWIM/TWIS Timing

Figure 9-64 shows the TWI-bus timing requirements and the compliance of the device with them. Some of these requirements ( $t_r$  and  $t_f$ ) are met by the device without requiring user intervention. Compliance with the other requirements ( $t_{HD-STA}$ ,  $t_{SU-STA}$ ,  $t_{SU-STO}$ ,  $t_{HD-DAT}$ ,  $t_{SU-DAT-TWI}$ ,  $t_{LOW-TWI}$ ,  $t_{HIGH}$ , and  $f_{TWCK}$ ) requires user intervention through appropriate programming of the relevant TWIM and TWIS user interface registers. refer to the TWIM and TWIS sections for more information.

|                         |                                 |                         | Minim       | num                 | Maxii                | mum                  |                                               |

|-------------------------|---------------------------------|-------------------------|-------------|---------------------|----------------------|----------------------|-----------------------------------------------|

| Symbol                  | Parameter                       | Mode                    | Requirement | Device              | Requirement          | Device               | Unit                                          |

|                         |                                 | Standard <sup>(1)</sup> | -           |                     | 1000                 |                      |                                               |

| t <sub>r</sub>          | TWCK and TWD rise time          | Fast <sup>(1)</sup>     | 20 + 0      | .1C <sub>b</sub>    | 300                  |                      | ns                                            |

|                         |                                 | Standard                | -           |                     | 30                   | 00                   |                                               |

| t <sub>f</sub>          | TWCK and TWD fall time          | Fast                    | 20 + 0      | .1C <sub>b</sub>    | 30                   | 00                   | ns                                            |

| +                       | (Dependented) STADT hold time   | Standard                | 4           |                     |                      |                      |                                               |

| t <sub>HD-STA</sub>     | (Repeated) START hold time      | Fast                    | 0.6         | <sup>I</sup> clkpb  | t <sub>clkpb</sub> - |                      | μs                                            |

| +                       | (Dependented) STADT act up time | Standard                | 4.7         |                     |                      |                      |                                               |

| t <sub>SU-STA</sub>     | (Repeated) START set-up time    | Fast                    | 0.6         | t <sub>clkpb</sub>  | -                    |                      | μs                                            |

| +                       | STOD oot up time                | Standard                | 4.0         | 4+                  | -                    |                      |                                               |

| t <sub>SU-STO</sub>     | STOP set-up time                | Fast                    | 0.6         | 4t <sub>clkpb</sub> |                      |                      | μs                                            |

| +                       | Data hold time                  | Standard                | 0.3(2)      | 2t <sub>clkpb</sub> | 3.45 <sup>()</sup>   | 15+ +                |                                               |

| t <sub>HD-DAT</sub>     |                                 | Fast                    | 0.317       |                     | ∠ıclkpb              | 0.9()                | 15t <sub>prescaled</sub> + t <sub>clkpb</sub> |

| +                       | Data set-up time                | Standard                | 250         | 2+                  |                      |                      |                                               |

| t <sub>SU-DAT-TWI</sub> | Data set-up time                | Fast                    | 100         | 2t <sub>clkpb</sub> | -                    |                      | ns                                            |

| t <sub>SU-DAT</sub>     |                                 | -                       | -           | t <sub>clkpb</sub>  | -                    |                      | -                                             |

| +                       | TWCK LOW period                 | Standard                | 4.7         | <i>/</i> +          |                      |                      |                                               |

| t <sub>LOW-TWI</sub>    | TWOR LOW period                 | Fast                    | 1.3         | 4t <sub>clkpb</sub> | φb <sup>–</sup>      |                      | μs                                            |

| t <sub>LOW</sub>        |                                 | -                       | -           | t <sub>clkpb</sub>  | -                    |                      | -                                             |

| +                       | TWCK HIGH period                | Standard                | 4.0         | Q+                  |                      |                      |                                               |

| t <sub>HIGH</sub>       |                                 | Fast                    | 0.6         | 8t <sub>clkpb</sub> | -                    |                      | μs                                            |

| f                       | TWCK frequency                  | Standard                |             |                     | 100                  | 1                    | kHz                                           |

| f <sub>TWCK</sub>       |                                 | Fast                    | -           |                     | 400                  | <sup>12t</sup> clkpb | KIIZ                                          |

**Table 9-64.**TWI-Bus Timing Requirements

Notes: 1. Standard mode:  $f_{TWCK} \le 100 \text{ kHz}$ ; fast mode:  $f_{TWCK} > 100 \text{ kHz}$ .

### Table 9-65.JTAG Timings(1)

| Symbol | Parameter                          | Conditions              | Min  | Max  | Units |

|--------|------------------------------------|-------------------------|------|------|-------|

| JTAG0  | TCK Low Half-period                |                         | 21.8 |      |       |

| JTAG1  | TCK High Half-period               |                         | 8.6  |      |       |

| JTAG2  | TCK Period                         |                         | 30.3 |      |       |

| JTAG3  | TDI, TMS Setup before TCK High     | V <sub>VDDIO</sub> from | 2.0  |      |       |

| JTAG4  | TDI, TMS Hold after TCK High       | 3.0V to 3.6V,           | 2.3  |      |       |

| JTAG5  | TDO Hold Time                      | maximum<br>external     | 9.5  |      | ns    |

| JTAG6  | TCK Low to TDO Valid               | capacitor =             |      | 21.8 |       |

| JTAG7  | Boundary Scan Inputs Setup Time    | 40pF                    | 0.6  |      |       |

| JTAG8  | Boundary Scan Inputs Hold Time     |                         | 6.9  |      |       |

| JTAG9  | Boundary Scan Outputs Hold Time    |                         | 9.3  |      |       |

| JTAG10 | TCK to Boundary Scan Outputs Valid |                         |      | 32.2 |       |

Note: 1. These values are based on simulation. These values are not covered by test limits in production.

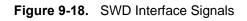

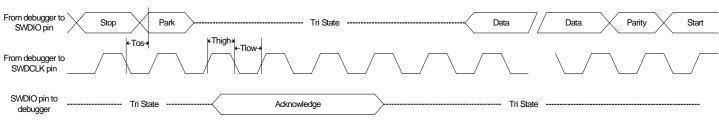

### 9.10.6 SWD Timing

## Read Cycle

### Write Cycle

Atmel

# Table 9-66.SWD Timings(1)

| Symbol | Parameter                                                     | Conditions                               | Min | Мах     | Units |

|--------|---------------------------------------------------------------|------------------------------------------|-----|---------|-------|

| Thigh  | SWDCLK High period                                            |                                          | 10  | 500 000 |       |

| Tlow   | SWDCLK Low period                                             | V <sub>VDDIO</sub> from<br>3.0V to 3.6V, | 10  | 500 000 |       |

| Tos    | SWDIO output skew to falling edge SWDCLK                      | maximum                                  | -5  | 5       | ns    |

| Tis    | Input Setup time required between SWDIO                       | external<br>capacitor =                  | 4   | -       | 10    |

| Tih    | Input Hold time required between SWDIO and rising edge SWDCLK | 40pF                                     | 1   | -       | 1     |

Note: 1. These values are based on simulation. These values are not covered by test limits in production or characterization.

# **10. Mechanical Characteristics**

# 10.1 Thermal Considerations

# 10.1.1 Thermal Data

Table 10-1 summarizes the thermal resistance data depending on the package.

| Symbol               | Parameter                              | Condition | Package  | Тур  | Unit  |  |

|----------------------|----------------------------------------|-----------|----------|------|-------|--|

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | TQFP100  | 48.1 | ·C/W  |  |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | TQFP100  | 13.3 | ·C/vv |  |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | VFBGA100 | 31.1 | CAN   |  |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | VFBGA100 | 6.9  | ·C/W  |  |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | WLCSP64  | 26.9 | 0.00  |  |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | WLCSP64  | 0.2  | ·C/W  |  |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | TQFP64   | 49.6 | CAN   |  |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | TQFP64   | 13.5 | ·C/W  |  |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | QFN64    | 22.0 | 0.000 |  |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | QFN64    | 1.3  | ·C/W  |  |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | TQFP48   | 51.1 | 0.000 |  |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | TQFP48   | 13.7 | ·C/W  |  |

| $\theta_{JA}$        | Junction-to-ambient thermal resistance | Still Air | QFN48    | 24.9 | CAN   |  |

| $\theta_{\text{JC}}$ | Junction-to-case thermal resistance    |           | QFN48    | 1.3  | ·C/W  |  |

Table 10-1. Thermal Resistance Data

### 10.1.2 Junction Temperature

The average chip-junction temperature,  $T_J$ , in °C can be obtained from the following:

1.

$$T_J = T_A + (P_D \times \theta_{JA})$$

2.  $T_J = T_A + (P_D \times (\theta_{HEATSINK} + \theta_{JC}))$ where:

- $\theta_{JA}$  = package thermal resistance, Junction-to-ambient (°C/W), provided in Table 10-1.

- $\theta_{JC}$  = package thermal resistance, Junction-to-case thermal resistance (°C/W), provided in Table 10-1.

- $\theta_{HEAT SINK}$  = cooling device thermal resistance (°C/W), provided in the device datasheet.

Atmel

- $P_D$  = device power consumption (W) estimated from data provided in Section 9.5 on page 103.

- $T_A$  = ambient temperature (°C).

From the first equation, the user can derive the estimated lifetime of the chip and decide if a cooling device is necessary or not. If a cooling device is to be fitted on the chip, the second equation should be used to compute the resulting average chip-junction temperature  $T_J$  in °C.

# ATSAM4L8/L4/L2

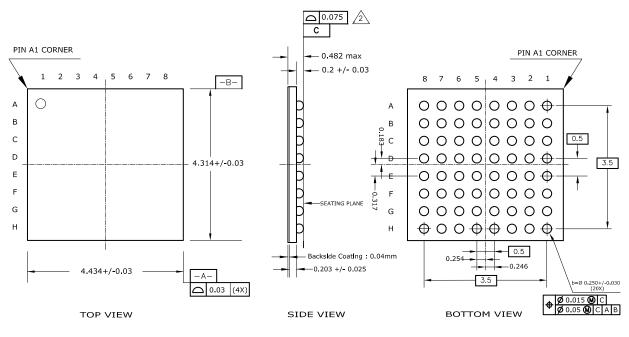

#### COMMON DIMENSIONS (Unit of Measure = mm)

| BALL | SIGNAL  | X COORD | Y COORD |

|------|---------|---------|---------|

| A1   | PB04    | 1.746   | 1.683   |

| A2   | GNDANA  | 1.246   | 1.683   |

| A3   | ADVREFP | 0.746   | 1.683   |

| A4   | VDDANA  | 0.246   | 1.683   |

| A5   | PA09    | -0.254  | 1.683   |

| A6   | PA28    | -0.754  | 1.683   |

| A7   | PA27    | -1.254  | 1.683   |

| A8   | PA12    | -1.754  | 1.683   |

| B1   | PB03    | 1.746   | 1.183   |

| B2   | XIN32   | 1.246   | 1.183   |

| B3   | XOUT32  | 0.746   | 1.183   |

| B4   | PA08    | 0.246   | 1.183   |

| B5   | PB06    | -0.254  | 1,183   |

| B6   | PA10    | -0.754  | 1.183   |

| B7   | PA11    | -1.254  | 1.183   |

| B8   | PA29    | -1.754  | 1.183   |

| C1   | VDDIN   | 1.746   | 0.683   |

| C2   | PB01    | 1.246   | 0.683   |

| C3   | PA05    | 0.746   | 0.683   |

| C4   | PA06    | 0.246   | 0.683   |

| C5   | PA07    | -0.254  | 0.683   |

| C6   | PB07    | -0.754  | 0.683   |

|      |         |         |         |

SIGNAL

X COORD

Y COORD

PA13

-1.254

0.683

GNDIO0

-1.754

0.683

VDDOUT

1.746

0.183

PB00

1.246

0.183

PA00

1.246

0.183

CE DI D 0.746 D PA04 0.18 PB05 0.1 PB12 PB08 PA14 VLCDIN GNDIN D5 D6 -0.254 0.18 -1.254 D7 D8 0.1 1 746 E1 E2 E3 PA03 PB02 RESET\_N PB13 PB09 PA15 1.246 0.746 0.246 -0.254 E4 E5 -0 E6 F7 0.254 -0.754 -1.254 -1.754 1.746 PA30 VDDCORE TCK E8 -0.317 -0.81 .246 -0.8 PA02 PB14 F3 F4 0.746

| BALL | SIGNAL | X COORD | Y COORD |

|------|--------|---------|---------|

| F5   | PA22   | -0.254  | -0.817  |

| F6   | PB10   | -0.754  | -0.817  |

| F7   | PA16   | -1.254  | -0.817  |

| F8   | PA31   | -1.754  | -0.817  |

| G1   | GNDIO1 | 1.746   | -1.317  |

| G2   | PA26   | 1.246   | -1.317  |

| G3   | PA24   | 0.746   | -1.317  |

| G4   | PA00   | 0.246   | -1.317  |

| G5   | PA01   | -0.254  | -1.317  |

| G6   | PA19   | -0.754  | -1.317  |

| G7   | PA18   | -1.254  | -1.317  |

| G8   | PA17   | -1.754  | -1.317  |

| H1   | VDDI01 | 1.746   | -1.817  |

| H2   | PA25   | 1.246   | -1.817  |

| H3   | PA23   | 0.746   | -1.817  |

| H4   | PB15   | 0.246   | -1.817  |

| H5   | PA21   | -0.254  | -1.817  |

| H6   | VDDIO0 | -0.754  | -1.817  |

| H7   | PA20   | -1.254  | -1.817  |

| H8   | PB11   | -1.754  | -1.817  |

|      |        |         |         |

Notes : 1. Dimension "b" is measured at the maximum ball diameter in a plane to the seating plane.

2. Applied to whole wafer.

## Table 10-11. Device and Package Maximum Weight

| 14.8                                         | mg   |

|----------------------------------------------|------|

| Table 10-12.         Package Characteristics |      |

| Moisture Sensitivity Level                   | MSL3 |

### Table 10-13. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E1     |

Atmel

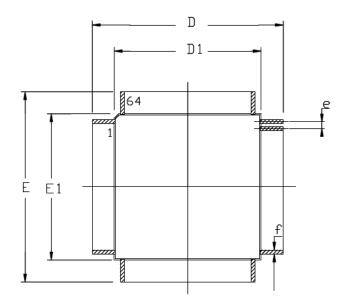

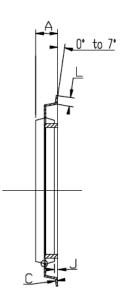

### Figure 10-7. TQFP-64 Package Drawing

### COMMON DIMENSIONS IN MM

| SYMBOL | Min   | Max   | NUTES |

|--------|-------|-------|-------|

| A      |       | 1. 20 |       |

| A1     | 0, 95 | 1. 05 |       |

| С      | 0. 09 | 0. 20 |       |

| D      | 12.0  | O BSC |       |

| D1     | 10.0  | O BSC |       |

| E      | 12.0  | O BSC |       |

| E1     | 10,0  | O BSC |       |

| J      | 0, 05 | 0.15  |       |

| L      | 0, 45 | 0, 75 |       |

| e      | 0. 5  | O BSC |       |

| f      | 0.17  | 0, 27 |       |

### Table 10-20. Device and Package Maximum Weight

| 300 | mg |

|-----|----|

|     |    |

### Table 10-21. Package Characteristics

| bisture Sensitivity Level | MSL3 |

|---------------------------|------|

|---------------------------|------|

### Table 10-22. Package Reference

| JEDEC Drawing Reference | MS-026 |

|-------------------------|--------|

| JESD97 Classification   | E3     |

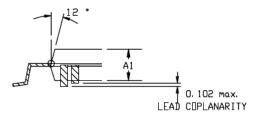

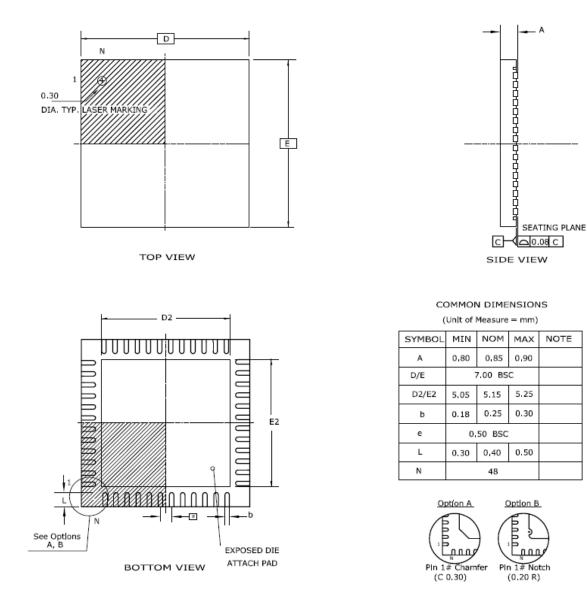

### Figure 10-10. QFN-48 Package Drawing for ATSAM4LC4/2 and ATSAM4LS4/2

Note: The exposed pad is not connected to anything internally, but should be soldered to ground to increase board level reliability.

| Table 10-29  | Device and Package Maximum Weight |

|--------------|-----------------------------------|

| Table 10-29. | Device and Fackage Maximum vergin |

| 140 | mg |

|-----|----|

|     |    |

### Table 10-30. Package Characteristics

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

|----------------------------|------|

### Table 10-31.Package Reference

| JEDEC Drawing Reference | MO-220 |

|-------------------------|--------|

| JESD97 Classification   | E3     |