### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |  |

|----------------------------|-----------------------------------------------------------------------|--|

| Product Status             | Active                                                                |  |

| Core Processor             | ARM® Cortex®-M0+                                                      |  |

| Core Size                  | 32-Bit Single-Core                                                    |  |

| Speed                      | 48MHz                                                                 |  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                |  |

| Peripherals                | DMA, I <sup>2</sup> S, LCD, LVD, POR, PWM, WDT                        |  |

| Number of I/O              | 50                                                                    |  |

| Program Memory Size        | 256KB (256K x 8)                                                      |  |

| Program Memory Type        | FLASH                                                                 |  |

| EEPROM Size                | -                                                                     |  |

| RAM Size                   | 32K x 8                                                               |  |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                          |  |

| Data Converters            | A/D 16x16b; D/A 1x12b                                                 |  |

| Oscillator Type            | Internal                                                              |  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |  |

| Mounting Type              | Surface Mount                                                         |  |

| Package / Case             | 64-LFBGA                                                              |  |

| Supplier Device Package    | 64-MAPBGA (5x5)                                                       |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl43z256vmp4 |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Operating Characteristics**

• Voltage range: 1.71 to 3.6 V

Flash write voltage range: 1.71 to 3.6 V

Temperature range: -40 to 105 °C

### **Packages**

- 64 LQFP 10mm x 10mm, 0.5mm pitch, 1.6mm thickness

- 64 MAPBGA 5mm x 5mm, 0.5mm pitch, 1.23mm thickness

### **Low Power**

- Down to 54uA/MHz in very low power run mode

- Down to 1.96uA in VLLS3 mode (RAM + RTC retained)

- · Six flexible static modes

### **Timers**

- One 6-channel Timer/PWM module

- Two 2-channel Timer/PWM modules

- One low-power timer

- Periodic interrupt timer

- · Real time clock

### Security and Integrity

- 80-bit unique identification number per chip

- · Advanced flash security

### I/O

• Up to 50 general-purpose input/output pins (GPIO) and 6 high-drive pad

### **Ordering Information**

| Pro           | duct                      | Mer           | nory         | Pa           | ckage   | IO and ADC cha |                                | annel                      |

|---------------|---------------------------|---------------|--------------|--------------|---------|----------------|--------------------------------|----------------------------|

| Part number   | Marking (Line1/<br>Line2) | Flash<br>(KB) | SRAM<br>(KB) | Pin<br>count | Package | GPIOs          | GPIOs<br>(INT/HD) <sup>1</sup> | ADC<br>channels<br>(SE/DP) |

| MKL43Z128VLH4 | MKL43Z128V//LH4           | 128           | 16           | 64           | LQFP    | 50             | 31/6                           | 16/2                       |

| MKL43Z256VLH4 | MKL43Z256V//LH4           | 256           | 32           | 64           | LQFP    | 50             | 31/6                           | 16/2                       |

| MKL43Z128VMP4 | M43P7V                    | 128           | 16           | 64           | MAPBGA  | 50             | 31/6                           | 16/2                       |

| MKL43Z256VMP4 | M43P8V                    | 256           | 32           | 64           | MAPBGA  | 50             | 31/6                           | 16/2                       |

1. INT: interrupt pin numbers; HD: high drive pin numbers

### **Related Resources**

| Туре                | Description                                                                                                                      | Resource                                                                 |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| Selector<br>Guide   | The Freescale Solution Advisor is a web-based tool that features interactive application wizards and a dynamic product selector. | Solution Advisor                                                         |

| Product Brief       | The Product Brief contains concise overview/summary information to enable quick evaluation of a device for design suitability.   | KLX3PB <sup>1</sup>                                                      |

| Reference<br>Manual | The Reference Manual contains a comprehensive description of the structure and function (operation) of a device.                 | KL43P64M48SF6RM <sup>1</sup>                                             |

| Data Sheet          | The Data Sheet includes electrical characteristics and signal connections.                                                       | This document.                                                           |

| Chip Errata         | The chip mask set Errata provides additional or corrective information for a particular device mask set.                         | KINETIS_L_1N71K <sup>1</sup>                                             |

| Package<br>drawing  | Package dimensions are provided in package drawings.                                                                             | 64-LQFP: 98ASS23234W <sup>1</sup> 64<br>MAPBGA: 98ASA00420D <sup>1</sup> |

1. To find the associated resource, go to http://www.freescale.com and perform a search using this term.

## 1.4 Voltage and current operating ratings

Table 4. Voltage and current operating ratings

| Symbol              | Description                                                               | Min.                  | Max.                  | Unit |

|---------------------|---------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>DD</sub>     | Digital supply voltage                                                    | -0.3                  | 3.8                   | V    |

| I <sub>DD</sub>     | Digital supply current                                                    | _                     | 120                   | mA   |

| V <sub>IO</sub>     | IO pin input voltage                                                      | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| I <sub>D</sub>      | Instantaneous maximum current single pin limit (applies to all port pins) | -25                   | 25                    | mA   |

| $V_{DDA}$           | Analog supply voltage                                                     | V <sub>DD</sub> – 0.3 | V <sub>DD</sub> + 0.3 | V    |

| V <sub>USB_DP</sub> | USB_DP input voltage                                                      | -0.3                  | 3.63                  | V    |

| V <sub>USB_DM</sub> | USB_DM input voltage                                                      | -0.3                  | 3.63                  | V    |

| V <sub>REGIN</sub>  | USB regulator input                                                       | -0.3                  | 6.0                   | V    |

## 2 General

### 2.1 AC electrical characteristics

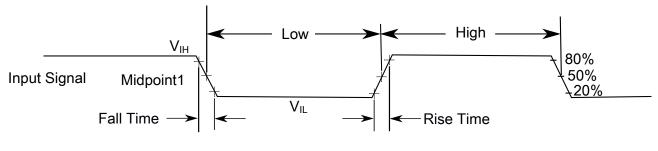

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is  $V_{IL} + (V_{IH} - V_{IL}) / 2$

Figure 1. Input signal measurement reference

All digital I/O switching characteristics, unless otherwise specified, assume that the output pins have the following characteristics.

- $C_L=30 pF loads$

- Slew rate disabled

- Normal drive strength

Table 7. Voltage and current operating behaviors (continued)

| Symbol           | Description                                                                                                                                                                   | Min. | Max.  | Unit | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

|                  | • $2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{I}_{OL} = 5 \text{ mA}$<br>• $1.71 \text{ V} \le \text{V}_{DD} \le 2.7 \text{ V}, \text{I}_{OL} = 1.5 \text{ mA}$ | _    | 0.5   | V    |       |

| V <sub>OL</sub>  | Output low voltage — high drive pad                                                                                                                                           |      |       |      | 1     |

|                  | • $2.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}, \text{I}_{OL} = 18 \text{ mA}$                                                                                          | _    | 0.5   | V    |       |

|                  | • $1.71 \text{ V} \le \text{V}_{DD} \le 2.7 \text{ V}, \text{I}_{OL} = 6 \text{ mA}$                                                                                          | _    | 0.5   | V    |       |

| I <sub>OLT</sub> | Output low current total for all ports                                                                                                                                        | _    | 100   | mA   |       |

| I <sub>IN</sub>  | Input leakage current (per pin) for full temperature range                                                                                                                    | _    | 1     | μA   | 2     |

| I <sub>IN</sub>  | Input leakage current (per pin) at 25 °C                                                                                                                                      | _    | 0.025 | μA   | 2     |

| I <sub>IN</sub>  | Input leakage current (total all pins) for full temperature range                                                                                                             | _    | 64    | μА   | 2     |

| I <sub>OZ</sub>  | Hi-Z (off-state) leakage current (per pin)                                                                                                                                    | _    | 1     | μA   |       |

| R <sub>PU</sub>  | Internal pullup resistors                                                                                                                                                     | 20   | 50    | kΩ   | 3     |

<sup>1.</sup> PTB0, PTB1, PTC3, PTC4, PTD6, and PTD7 I/O have both high drive and normal drive capability selected by the associated PTx\_PCRn[DSE] control bit. All other GPIOs are normal drive only.

## 2.2.4 Power mode transition operating behaviors

All specifications except  $t_{POR}$  and VLLSx $\rightarrow$ RUN recovery times in the following table assume this clock configuration:

- CPU and system clocks = 48 MHz

- Bus and flash clock = 24 MHz

- HIRC clock mode

Table 8. Power mode transition operating behaviors

| Symbol           | Description                                                                                                                                                       | Min. | Тур. | Max. | Unit | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| t <sub>POR</sub> | After a POR event, amount of time from the point $V_{DD}$ reaches 1.8 V to execution of the first instruction across the operating temperature range of the chip. | _    | _    | 300  | μs   | 1     |

|                  | • VLLS0 → RUN                                                                                                                                                     | _    | 152  | 166  | μs   |       |

|                  | • VLLS1 → RUN                                                                                                                                                     | _    | 152  | 166  | μs   |       |

|                  | • VLLS3 → RUN                                                                                                                                                     | _    | 93   | 104  | μs   |       |

<sup>2.</sup> Measured at V<sub>DD</sub> = 3.6 V

<sup>3.</sup> Measured at  $V_{DD}$  supply voltage =  $V_{DD}$  min and Vinput =  $V_{SS}$

| Symbol | Description  | Min. | Тур. | Max. | Unit | Notes |

|--------|--------------|------|------|------|------|-------|

|        | • LLS → RUN  |      |      |      |      |       |

|        |              | _    | 7.5  | 8    | μs   |       |

|        | VLPS → RUN   |      |      |      |      |       |

|        |              | _    | 7.5  | 8    | μs   |       |

|        | • STOP → RUN |      |      |      |      |       |

|        |              | _    | 7.5  | 8    | μs   |       |

<sup>1.</sup> Normal boot (FTFA\_FOPT[LPBOOT]=11)

## 2.2.5 Power consumption operating behaviors

The maximum values stated in the following table represent characterized results equivalent to the mean plus three times the standard deviation (mean + 3 sigma).

### **NOTE**

The while (1) test is executed with flash cache enabled.

Table 9. Power consumption operating behaviors

| Symbol                | Description                                                                                                                                     | Min. | Тур. | Max.     | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|------|-------|

| I <sub>DDA</sub>      | Analog supply current                                                                                                                           | _    | _    | See note | mA   | 1     |

| I <sub>DD_RUNCO</sub> | Running CoreMark in flash in compute operation mode—48M HIRC mode, 48 MHz core / 24 MHz flash, V <sub>DD</sub> = 3.0 V                          |      |      |          |      | 2     |

|                       | • at 25 °C                                                                                                                                      | _    | 5.76 | 6.40     | mA   |       |

|                       | • at 105 °C                                                                                                                                     | _    | 6.04 | 6.68     |      |       |

| I <sub>DD_RUNCO</sub> | Running While(1) loop in flash in compute operation mode—48M HIRC mode, 48 MHz core / 24 MHz flash, V <sub>DD</sub> = 3.0 V                     |      |      |          |      |       |

|                       | • at 25 °C                                                                                                                                      | _    | 3.21 | 3.85     | mA   |       |

|                       | • at 105 °C                                                                                                                                     | _    | 3.49 | 4.13     |      |       |

| I <sub>DD_RUN</sub>   | Run mode current—48M HIRC mode, running<br>CoreMark in Flash all peripheral clock disable 48<br>MHz core/24 MHz flash, V <sub>DD</sub> = 3.0 V  |      |      |          |      | 2     |

|                       | • at 25 °C                                                                                                                                      | _    | 6.45 | 7.09     | mA   |       |

|                       | • at 105 °C                                                                                                                                     | _    | 6.75 | 7.39     |      |       |

| I <sub>DD_RUN</sub>   | Run mode current—48M HIRC mode, running<br>CoreMark in flash all peripheral clock disable, 24<br>MHz core/12 MHz flash, V <sub>DD</sub> = 3.0 V |      |      |          |      | 2     |

|                       |                                                                                                                                                 | _    | 3.95 | 4.59     |      |       |

|                       |                                                                                                                                                 | _    | 4.23 | 4.87     | mA   |       |

Table 9. Power consumption operating behaviors (continued)

| Symbol              | Description                                                                                                                                    | Min. | Тур. | Max. | Unit | Notes |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

|                     | • at 25 °C                                                                                                                                     |      |      |      |      |       |

|                     | • at 105 °C                                                                                                                                    |      |      |      |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running<br>CoreMark in Flash all peripheral clock disable 12<br>MHz core/6 MHz flash, V <sub>DD</sub> = 3.0 V  |      |      |      |      | 2     |

|                     | • at 25 °C                                                                                                                                     |      | 2.68 | 3.32 | mA   |       |

|                     | • at 105 °C                                                                                                                                    | _    | 2.96 | 3.60 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running<br>CoreMark in Flash all peripheral clock enable 48<br>MHz core/24 MHz flash, V <sub>DD</sub> = 3.0 V  |      |      |      |      | 2     |

|                     | • at 25 °C                                                                                                                                     | _    | 8.08 | 8.72 | mA   |       |

|                     | • at 105 °C                                                                                                                                    | _    | 8.39 | 9.03 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running While(1) loop in flash all peripheral clock disable, 48 MHz core/24 MHz flash, V <sub>DD</sub> = 3.0 V |      |      |      |      |       |

|                     | • at 25 °C                                                                                                                                     | _    | 3.90 | 4.54 | mA   |       |

|                     | • at 105 °C                                                                                                                                    | _    | 4.21 | 4.85 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running While(1) loop in Flash all peripheral clock disable, 24 MHz core/12 MHz flash, V <sub>DD</sub> = 3.0 V |      | 2.66 | 3.30 | m A  |       |

|                     | • at 25 °C                                                                                                                                     | _    |      |      | mA   |       |

|                     | • at 105 °C                                                                                                                                    | _    | 2.94 | 3.58 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, Running While(1) loop in Flash all peripheral clock disable, 12 MHz core/6 MHz flash, V <sub>DD</sub> = 3.0 V  |      |      |      |      |       |

|                     | • at 25 °C                                                                                                                                     | _    | 2.03 | 2.67 | mA   |       |

|                     | • at 105 °C                                                                                                                                    | _    | 2.31 | 2.95 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, Running While(1) loop in Flash all peripheral clock enable, 48 MHz core/24 MHz flash, V <sub>DD</sub> = 3.0 V  |      |      |      |      |       |

|                     | • at 25 °C                                                                                                                                     | _    | 5.52 | 6.16 | mA   |       |

|                     | • at 105 °C                                                                                                                                    | _    | 5.83 | 6.47 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running While(1) loop in SRAM all peripheral clock disable, 48 MHz core/24 MHz flash, V <sub>DD</sub> = 3.0 V  |      |      |      |      |       |

|                     | • at 25 °C                                                                                                                                     |      | 5.29 | 5.93 | mA   |       |

|                     | • at 105 °C                                                                                                                                    | _    | 5.56 | 6.20 |      |       |

| I <sub>DD_RUN</sub> | Run mode current—48M HIRC mode, running While(1) loop in SRAM all peripheral clock enable, 48 MHz core/24 MHz flash, V <sub>DD</sub> = 3.0 V   |      |      |      |      |       |

|                     |                                                                                                                                                | _    | 6.91 | 7.55 | mA   |       |

|                     |                                                                                                                                                | _    | 7.19 | 7.91 |      |       |

Table 9. Power consumption operating behaviors (continued)

| Symbol                | Description                                                                                                                      | Min.             | Тур.                                   | Max.                                    | Unit | Notes |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------|-----------------------------------------|------|-------|

|                       | • at 50 °C                                                                                                                       | _                | 10.26                                  | 17.62                                   |      |       |

|                       | • at 85 °C                                                                                                                       | _                | 33.49                                  | 60.19                                   | μA   |       |

|                       | • at 105 °C                                                                                                                      | _                | 102.92                                 | 162.20                                  |      |       |

| I <sub>DD_LLS</sub>   | Low-leakage stop mode current, all peripheral disable, at 3.0 V  • at 25 °C and below                                            | _                | 2.06                                   | 3.33                                    | μΑ   |       |

|                       | • at 50 °C                                                                                                                       |                  | 4.72                                   | 6.85                                    |      |       |

|                       | • at 70 °C                                                                                                                       | _                | 8.13                                   | 13.30                                   |      |       |

|                       | • at 85 °C                                                                                                                       | _                | 13.34                                  | 24.70                                   |      |       |

|                       | • at 105 °C                                                                                                                      | _                | 41.08                                  | 52.43                                   |      |       |

| I <sub>DD_LLS</sub>   | Low-leakage stop mode current with RTC current, at 3.0 V  • at 25 °C and below                                                   | _                | 2.46<br>5.12                           | 3.73<br>7.25                            | μА   |       |

|                       | • at 50 °C                                                                                                                       |                  |                                        |                                         |      |       |

|                       | • at 70 °C                                                                                                                       | _                | 8.53                                   | 11.78                                   |      |       |

|                       | • at 85 °C                                                                                                                       |                  | 13.74                                  | 18.91                                   |      |       |

|                       | • at 105 °C                                                                                                                      | _                | 41.48                                  | 52.83                                   |      |       |

| I <sub>DD_LLS</sub>   | Low-leakage stop mode current with RTC current, at 1.8 V  • at 25 °C and below  • at 50 °C  • at 70 °C  • at 85 °C  • at 105 °C  | -<br>-<br>-<br>- | 2.35<br>4.91<br>8.32<br>13.44<br>40.47 | 2.70<br>6.75<br>11.78<br>18.21<br>51.85 | μА   | 3     |

| I <sub>DD_VLLS3</sub> | Very-low-leakage stop mode 3 current, all peripheral disable, at 3.0 V  • at 25 °C and below  • at 50 °C  • at 70 °C  • at 85 °C | -<br>-<br>-<br>- | 1.45<br>3.37<br>5.76<br>9.72<br>30.41  | 1.85<br>4.39<br>8.48<br>14.30<br>37.50  | μА   |       |

| I <sub>DD_VLLS3</sub> | at 105 °C  Very-low-leakage stop mode 3 current with RTC current, at 3.0 V                                                       |                  |                                        |                                         | μА   | 3     |

|                       | • at 25 °C and below                                                                                                             | _                | 2.05                                   | 2.45                                    | μΑ   |       |

|                       | • at 50 °C                                                                                                                       | _                | 3.97                                   | 4.99                                    |      |       |

|                       | • at 70 °C                                                                                                                       | _                | 6.36                                   | 9.08                                    |      |       |

|                       | • at 85 °C                                                                                                                       | _                | 10.32                                  | 14.73                                   |      |       |

|                       | • at 105 °C                                                                                                                      | _                | 31.01                                  | 38.10                                   |      |       |

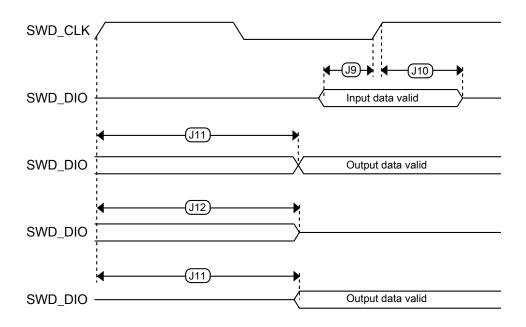

Figure 5. Serial wire data timing

## 3.2 System modules

There are no specifications necessary for the device's system modules.

## 3.3 Clock modules

## 3.3.1 MCG-Lite specifications

Table 18. IRC48M specification

| Symbol                     | Description                                                                                     | Min. | Тур.  | Max.  | Unit                 | Notes |

|----------------------------|-------------------------------------------------------------------------------------------------|------|-------|-------|----------------------|-------|

| I <sub>DD</sub>            | Supply current                                                                                  | _    | 400   | 500   | μΑ                   | _     |

| f <sub>IRC</sub>           | Output frequency                                                                                | _    | 48    | _     | MHz                  | _     |

| Δf <sub>irc48m_ol_lv</sub> | Open loop total deviation of IRC48M frequency at low voltage (VDD=1.71V-1.89V) over temperature | _    | ± 0.5 | ± 1.5 | %f <sub>irc48m</sub> | 1     |

| Δf <sub>irc48m_ol_hv</sub> | Open loop total deviation of IRC48M frequency at high voltage (VDD=1.89V-3.6V) over temperature | _    | ± 0.5 | ± 1.0 | %f <sub>irc48m</sub> | 1     |

## Table 18. IRC48M specification (continued)

| Symbol          | Description         | Min. | Тур. | Max. | Unit | Notes |

|-----------------|---------------------|------|------|------|------|-------|

| Tj              | Period jitter (RMS) | _    | 35   | 150  | ps   |       |

| T <sub>su</sub> | Startup time        | _    | 2    | 3    | μs   | _     |

1. The maximum value represents characterized results equivalent to mean plus or minus three times the standard deviation (mean +/-3sigma).

Table 19. IRC8M/2M specification

| Symbol                | Description                      | Min. | Тур. | Max. | Unit              | Notes |

|-----------------------|----------------------------------|------|------|------|-------------------|-------|

| I <sub>DD_2M</sub>    | Supply current in 2 MHz mode     | _    | 14   | 17   | μΑ                | _     |

| I <sub>DD_8M</sub>    | Supply current in 8 MHz mode     | _    | 30   | 35   | μΑ                | _     |

| f <sub>IRC_2M</sub>   | Output frequency                 | _    | 2    | _    | MHz               | _     |

| f <sub>IRC_8M</sub>   | Output frequency                 | _    | 8    | _    | MHz               | _     |

| f <sub>IRC_T_2M</sub> | Output frequency range (trimmed) | _    | _    | ±3   | %f <sub>IRC</sub> | _     |

| f <sub>IRC_T_8M</sub> | Output frequency range (trimmed) | _    | _    | ±3   | %f <sub>IRC</sub> | _     |

| T <sub>su_2M</sub>    | Startup time                     | _    | _    | 12.5 | μs                | _     |

| T <sub>su_8M</sub>    | Startup time                     | _    | _    | 12.5 | μs                | _     |

Table 27. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ ) (continued)

| Symbol              | Description                     | Conditions <sup>1</sup>                         | Min. | Typ. <sup>2</sup>      | Max.            | Unit             | Notes                                                                        |

|---------------------|---------------------------------|-------------------------------------------------|------|------------------------|-----------------|------------------|------------------------------------------------------------------------------|

|                     |                                 |                                                 |      |                        | -0.7 to<br>+0.5 |                  |                                                                              |

| E <sub>FS</sub>     | Full-scale error                | 12-bit modes                                    | _    | -4                     | -5.4            | LSB <sup>4</sup> | $V_{ADIN} = V_{DDA}^{5}$                                                     |

|                     |                                 | • <12-bit modes                                 | _    | -1.4                   | -1.8            |                  | V <sub>DDA</sub> <sup>5</sup>                                                |

| E <sub>Q</sub>      | Quantization                    | 16-bit modes                                    | _    | -1 to 0                | _               | LSB <sup>4</sup> |                                                                              |

|                     | error                           | • ≤13-bit modes                                 | _    | _                      | ±0.5            |                  |                                                                              |

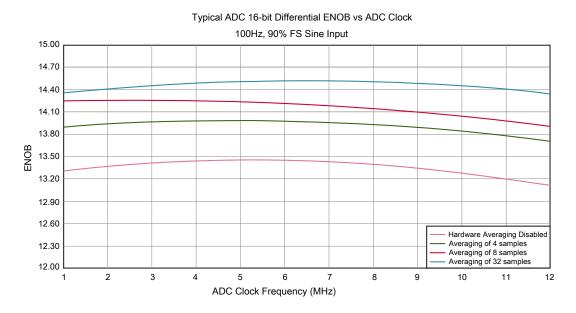

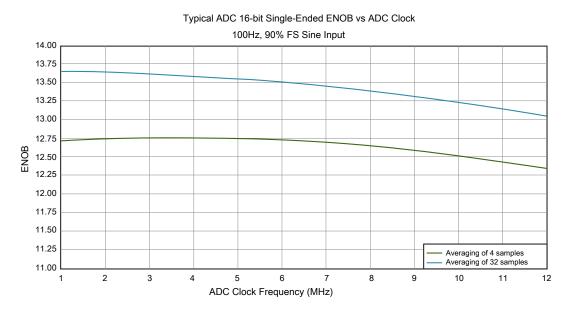

| ENOB                | Effective                       | 16-bit differential mode                        |      |                        |                 | bits             | 6                                                                            |

|                     | number of bits                  | • Avg = 32                                      | 12.8 | 14.5                   |                 | bits             |                                                                              |

|                     |                                 | • Avg = 4                                       | 11.9 | 13.8                   | _               |                  |                                                                              |

|                     |                                 | 16-bit single-ended mode                        |      |                        | _               | bits             |                                                                              |

|                     |                                 | • Avg = 32                                      | 400  | 40.0                   |                 | bits             |                                                                              |

|                     |                                 | • Avg = 4                                       | 12.2 | 13.9                   | _               |                  |                                                                              |

|                     | Oi-mark to main                 | See ENOB                                        | 11.4 | 13.1                   | _               |                  |                                                                              |

| SINAD               | Signal-to-noise plus distortion | 6.02 × ENOB + 1.76                              |      |                        | 1.76            | dB               |                                                                              |

| THD                 | Total harmonic                  | 16-bit differential mode                        |      |                        |                 | dB               | 7                                                                            |

|                     | distortion                      | • Avg = 32                                      | _    | -94                    | _               | dB               |                                                                              |

|                     |                                 | 16-bit single-ended mode                        |      | 05                     |                 | u.b              |                                                                              |

|                     |                                 | • Avg = 32                                      | _    | -85                    | _               |                  |                                                                              |

| SFDR                | Spurious free                   | 16-bit differential mode                        |      |                        | _               | dB               | 7                                                                            |

|                     | dynamic range                   | • Avg = 32                                      | 82   | 95                     |                 | dB               |                                                                              |

|                     |                                 | 16-bit single-ended mode                        | 78   | 90                     | _               | иь               |                                                                              |

|                     |                                 | • Avg = 32                                      | . •  |                        |                 |                  |                                                                              |

| E <sub>IL</sub>     | Input leakage<br>error          |                                                 |      | $I_{ln} \times R_{AS}$ |                 | mV               | I <sub>In</sub> = leakage current                                            |

|                     |                                 |                                                 |      |                        |                 |                  | (refer to<br>the MCU's<br>voltage<br>and<br>current<br>operating<br>ratings) |

|                     | Temp sensor slope               | Across the full temperature range of the device | 1.55 | 1.62                   | 1.69            | mV/°C            | 8                                                                            |

| V <sub>TEMP25</sub> | Temp sensor voltage             | 25 °C                                           | 706  | 716                    | 726             | mV               | 8                                                                            |

<sup>1.</sup> All accuracy numbers assume the ADC is calibrated with  $V_{\mbox{\scriptsize REFH}}$  =  $V_{\mbox{\scriptsize DDA}}$

### Peripheral operating requirements and behaviors

- 2. Typical values assume  $V_{DDA} = 3.0 \text{ V}$ , Temp = 25 °C,  $f_{ADCK} = 2.0 \text{ MHz}$  unless otherwise stated. Typical values are for reference only and are not tested in production.

- 3. The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

- 4.  $1 LSB = (V_{REFH} V_{REFL})/2^{N}$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

- 8. ADC conversion clock < 3 MHz

Figure 8. Typical ENOB vs. ADC\_CLK for 16-bit differential mode

Figure 9. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

### Peripheral operating requirements and behaviors

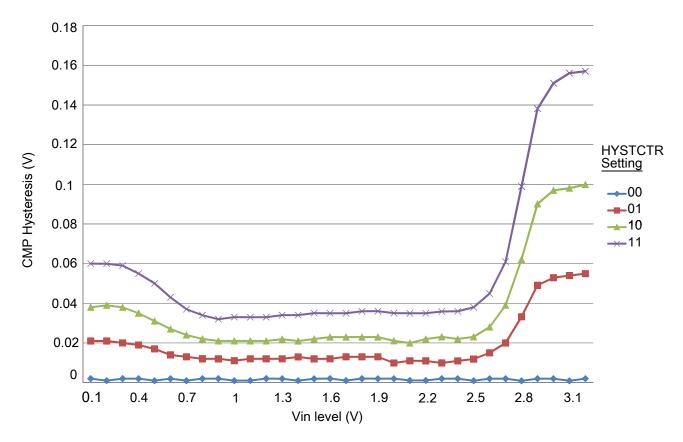

Figure 11. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 1)

## 3.6.4 12-bit DAC electrical characteristics

# 3.6.4.1 12-bit DAC operating requirements Table 33. 12-bit DAC operating requirements

| Symbol            | Desciption              | Min. | Max. | Unit | Notes |

|-------------------|-------------------------|------|------|------|-------|

| $V_{DDA}$         | Supply voltage          |      | 3.6  | V    |       |

| V <sub>DACR</sub> | Reference voltage       | 1.13 | 3.6  | V    | 1     |

| C <sub>L</sub>    | Output load capacitance | _    | 100  | pF   | 2     |

| ΙL                | Output load current     | _    | 1    | mA   |       |

- 1. The DAC reference can be selected to be  $V_{\text{DDA}}$  or  $V_{\text{REFH}}$ .

- 2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC.

# 3.6.4.2 12-bit DAC operating behaviors Table 34. 12-bit DAC operating behaviors

| Symbol                | Description                                                                      | Min. | Тур.     | Max.       | Unit   | Notes |

|-----------------------|----------------------------------------------------------------------------------|------|----------|------------|--------|-------|

| I <sub>DDA_DACL</sub> | Supply current — low-power mode                                                  | _    | _        | 250        | μΑ     |       |

| I <sub>DDA_DACH</sub> | Supply current — high-speed mode                                                 | _    | _        | 900        | μΑ     |       |

| t <sub>DACLP</sub>    | Full-scale settling time (0x080 to 0xF7F) — low-power mode                       | _    | 100      | 200        | μs     | 1     |

| t <sub>DACHP</sub>    | Full-scale settling time (0x080 to 0xF7F) — high-power mode                      | _    | 15       | 30         | μs     | 1     |

| t <sub>CCDACLP</sub>  | Code-to-code settling time (0xBF8 to 0xC08) — low-power mode and high-speed mode | _    | 0.7      | 1          | μs     | 1     |

| V <sub>dacoutl</sub>  | DAC output voltage range low — high-<br>speed mode, no load, DAC set to 0x000    | _    | _        | 100        | mV     |       |

| V <sub>dacouth</sub>  | DAC output voltage range high — high-<br>speed mode, no load, DAC set to 0xFFF   |      | _        | $V_{DACR}$ | mV     |       |

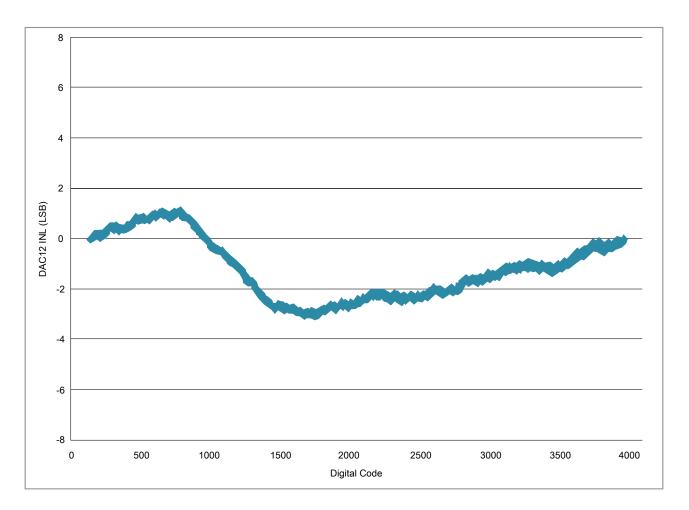

| INL                   | Integral non-linearity error — high speed mode                                   | _    | _        | ±8         | LSB    | 2     |

| DNL                   | Differential non-linearity error — V <sub>DACR</sub> > 2<br>V                    | _    | _        | ±1         | LSB    | 3     |

| DNL                   | Differential non-linearity error — V <sub>DACR</sub> = VREF_OUT                  | _    | _        | ±1         | LSB    | 4     |

| V <sub>OFFSET</sub>   | Offset error                                                                     | _    | ±0.4     | ±0.8       | %FSR   | 5     |

| E <sub>G</sub>        | Gain error                                                                       | _    | ±0.1     | ±0.6       | %FSR   | 5     |

| PSRR                  | Power supply rejection ratio, V <sub>DDA</sub> ≥ 2.4 V                           | 60   | _        | 90         | dB     |       |

| $T_CO$                | Temperature coefficient offset voltage                                           | _    | 3.7      | _          | μV/C   | 6     |

| $T_GE$                | Temperature coefficient gain error                                               | _    | 0.000421 | _          | %FSR/C |       |

| Rop                   | Output resistance (load = $3 \text{ k}\Omega$ )                                  | _    | _        | 250        | Ω      |       |

| SR                    | Slew rate -80h→ F7Fh→ 80h                                                        |      |          |            | V/µs   |       |

|                       | High power (SP <sub>HP</sub> )                                                   | 1.2  | 1.7      | _          |        |       |

|                       | Low power (SP <sub>LP</sub> )                                                    | 0.05 | 0.12     | _          |        |       |

| BW                    | 3dB bandwidth                                                                    |      |          |            | kHz    |       |

|                       | High power (SP <sub>HP</sub> )                                                   | 550  | _        | _          |        |       |

|                       | Low power (SP <sub>LP</sub> )                                                    | 40   | _        | _          |        |       |

- 1. Settling within ±1 LSB

- 2. The INL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV

- 3. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV

- 4. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV with  $V_{DDA}$  > 2.4 V

- 5. Calculated by a best fit curve from  $V_{SS}$  + 100 mV to  $V_{DACR}$  100 mV

- 6. V<sub>DDA</sub> = 3.0 V, reference select set for V<sub>DDA</sub> (DACx\_CO:DACRFS = 1), high power mode (DACx\_CO:LPEN = 0), DAC set to 0x800, temperature range is across the full range of the device

### Peripheral operating requirements and behaviors

Figure 12. Typical INL error vs. digital code

### **NOTE**

The IRC48M do not meet the USB jitter specifications for certification for Host mode operation.

This device cannot support Host mode operation.

# 3.8.2 USB VREG electrical specifications Table 35. USB VREG electrical specifications

| Symbol                | Description                                                                          | Min. | Typ. <sup>1</sup> | Max. | Unit | Notes |

|-----------------------|--------------------------------------------------------------------------------------|------|-------------------|------|------|-------|

| VREGIN                | Input supply voltage                                                                 | 2.7  | _                 | 5.5  | V    |       |

| I <sub>DDon</sub>     | Quiescent current — Run mode, load current equal zero, input supply (VREGIN) > 3.6 V | _    | 125               | 186  | μA   |       |

| I <sub>DDstby</sub>   | Quiescent current — Standby mode, load current equal zero                            | _    | 1.1               | 10   | μA   |       |

| I <sub>DDoff</sub>    | Quiescent current — Shutdown mode                                                    |      |                   |      |      |       |

|                       | <ul> <li>VREGIN = 5.0 V and temperature=25 °C</li> </ul>                             | _    | 650               | _    | nA   |       |

|                       | Across operating voltage and temperature                                             | _    | _                 | 4    | μA   |       |

| I <sub>LOADrun</sub>  | Maximum load current — Run mode                                                      | _    | _                 | 120  | mA   |       |

| I <sub>LOADstby</sub> | Maximum load current — Standby mode                                                  | _    | _                 | 1    | mA   |       |

| V <sub>Reg33out</sub> | Regulator output voltage — Input supply (VREGIN) > 3.6 V                             |      |                   |      |      |       |

|                       | Run mode                                                                             | 3    | 3.3               | 3.6  | V    |       |

|                       | Standby mode                                                                         | 2.1  | 2.8               | 3.6  | V    |       |

| V <sub>Reg33out</sub> | Regulator output voltage — Input supply (VREGIN) < 3.6 V, pass-through mode          | 2.1  | _                 | 3.6  | V    | 2     |

| C <sub>OUT</sub>      | External output capacitor                                                            | 1.76 | 2.2               | 8.16 | μF   |       |

| ESR                   | External output capacitor equivalent series resistance                               | 1    | _                 | 100  | mΩ   |       |

| I <sub>LIM</sub>      | Short circuit current                                                                | _    | 290               | _    | mA   |       |

<sup>1.</sup> Typical values assume VREGIN = 5.0 V, Temp =  $25 \,^{\circ}\text{C}$  unless otherwise stated.

<sup>2.</sup> Operating in pass-through mode: regulator output voltage equal to the input voltage minus a drop proportional to I<sub>Load</sub>.

Table 46. LCD electricals (continued)

| Symbol             | Description                                                     | Min. | Тур. | Max.                   | Unit                | Notes |

|--------------------|-----------------------------------------------------------------|------|------|------------------------|---------------------|-------|

|                    | • RVTRIM=1110                                                   | _    | 0.99 | _                      |                     |       |

|                    | • RVTRIM=0001                                                   | _    | 1.01 | _                      |                     |       |

|                    | • RVTRIM=1001                                                   | _    | 1.02 | _                      |                     |       |

|                    | • RVTRIM=0101                                                   | _    | 1.03 | _                      |                     |       |

|                    | • RVTRIM=1101                                                   | _    | 1.05 | _                      |                     |       |

|                    | • RVTRIM=0011                                                   | _    | 1.06 | _                      |                     |       |

|                    | • RVTRIM=1011                                                   | _    | 1.07 | _                      |                     |       |

|                    | • RVTRIM=0111                                                   | _    | 1.08 | _                      |                     |       |

|                    | • RVTRIM=1111                                                   | _    | 1.09 | _                      |                     |       |

| $\Delta_{RTRIM}$   | V <sub>IREG</sub> TRIM resolution                               | _    | _    | 3.0                    | % V <sub>IREG</sub> |       |

| I <sub>VIREG</sub> | V <sub>IREG</sub> current adder — RVEN = 1                      | _    | 1    | _                      | μA                  |       |

| I <sub>RBIAS</sub> | RBIAS current adder                                             |      |      |                        |                     |       |

|                    | • LADJ = 10 or 11 — High load (LCD glass capacitance ≤ 8000 pF) | _    | 10   | _                      | μΑ                  |       |

|                    | • LADJ = 00 or 01 — Low load (LCD glass capacitance ≤ 2000 pF)  | _    | 1    | _                      | μΑ                  |       |

| R <sub>RBIAS</sub> | RBIAS resistor values                                           |      |      |                        |                     |       |

|                    | • LADJ = 10 or 11 — High load (LCD glass capacitance ≤ 8000 pF) | _    | 0.28 | _                      | МΩ                  |       |

|                    | • LADJ = 00 or 01 — Low load (LCD glass capacitance ≤ 2000 pF)  | _    | 2.98 | _                      | ΜΩ                  |       |

| VLL1               | VLL1 voltage                                                    | _    | _    | V <sub>IREG</sub>      | V                   | 4     |

| VLL2               | VLL2 voltage                                                    | _    | _    | 2 x V <sub>IREG</sub>  | V                   | 4     |

| VLL3               | VLL3 voltage                                                    |      |      | 3 x V <sub>IREG</sub>  | V                   | 4     |

| VLL1               | VLL1 voltage                                                    | _    | _    | V <sub>DDA</sub> / 3   | V                   | 5     |

| VLL2               | VLL2 voltage                                                    | _    | _    | V <sub>DDA</sub> / 1.5 | V                   | 5     |

| VLL3               | VLL3 voltage                                                    | _    | _    | $V_{DDA}$              | V                   | 5     |

- 1. The actual value used could vary with tolerance.

- 2. For highest glass capacitance values, LCD\_GCR[LADJ] should be configured as specified in the LCD Controller chapter within the device's reference manual.

- 3.  $V_{IREG}$  maximum should never be externally driven to any level other than  $V_{DD}$  0.15 V

- 4. VLL1, VLL2 and VLL3 are a function of V<sub>IREG</sub> only when the regulator is enabled (GCR[RVEN]=1) and the charge pump is enabled (GCR[CPSEL]=1).

- 5. VLL1, VLL2 and VLL3 are a function of  $V_{DDA}$  only under either of the following conditions:

- The charge pump is enabled (GCR[CPSEL]=1), the regulator is disabled (GCR[RVEN]=0), and VLL3 = V<sub>DDA</sub> through the internal power switch (GCR[VSUPPLY]=0).

- The resistor bias string is enabled (GCR[CPSEL]=0), the regulator is disabled (GCR[RVEN]=0), and VLL3 is connected to V<sub>DDA</sub> externally (GCR[VSUPPLY]=1).

## 4 Dimensions

## 4.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

To find a package drawing, go to freescale.com and perform a keyword search for the drawing's document number:

| If you want the drawing for this package | Then use this document number |  |  |  |  |

|------------------------------------------|-------------------------------|--|--|--|--|

| 64-pin LQFP                              | 98ASS23234W                   |  |  |  |  |

| 64-pin MAPBGA                            | 98ASA00420D                   |  |  |  |  |

## 5 Pinouts and Packaging

## 5.1 KL43 Signal Multiplexing and Pin Assignments

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The Port Control Module is responsible for selecting which ALT functionality is available on each pin.

### NOTE

VREFH can act as VREF\_OUT when VREFV1 module is enabled.

| 64<br>MAP<br>BGA | 64<br>LQFP | Pin Name | Default  | ALT0    | ALT1               | ALT2      | ALT3       | ALT4       | ALT5      | ALT6     | ALT7    |

|------------------|------------|----------|----------|---------|--------------------|-----------|------------|------------|-----------|----------|---------|

| A1               | 1          | PTE0     | DISABLED | LCD_P48 | PTE0/<br>CLKOUT32K | SPI1_MISO | LPUART1_TX | RTC_CLKOUT | CMP0_OUT  | I2C1_SDA | LCD_P48 |

| B1               | 2          | PTE1     | DISABLED | LCD_P49 | PTE1               | SPI1_MOSI | LPUART1_RX |            | SPI1_MISO | I2C1_SCL | LCD_P49 |

| _                | 3          | VDD      | VDD      | VDD     |                    |           |            |            |           |          |         |

| C4               | 4          | VSS      | VSS      | VSS     |                    |           |            |            |           |          |         |

| E1               | 5          | USB0_DP  | USB0_DP  | USB0_DP |                    |           |            |            |           |          |         |

| D1               | 6          | USB0_DM  | USB0_DM  | USB0_DM |                    |           |            |            |           |          |         |

| E2               | 7          | VOUT33   | VOUT33   | VOUT33  |                    |           |            |            |           |          |         |

| D2               | 8          | VREGIN   | VREGIN   | VREGIN  |                    |           |            |            |           |          |         |

### **Pinouts and Packaging**

| 64<br>MAP<br>BGA | 64<br>LQFP | Pin Name          | Default               | ALT0                  | ALT1              | ALT2      | ALT3       | ALT4 | ALT5      | ALT6     | ALT7    |

|------------------|------------|-------------------|-----------------------|-----------------------|-------------------|-----------|------------|------|-----------|----------|---------|

| B2               | 63         | PTD6/<br>LLWU_P15 | LCD_P46/<br>ADC0_SE7b | LCD_P46/<br>ADC0_SE7b | PTD6/<br>LLWU_P15 | SPI1_MOSI | LPUART0_RX |      | SPI1_MISO | FXIO0_D6 | LCD_P46 |

| A2               | 64         | PTD7              | LCD_P47               | LCD_P47               | PTD7              | SPI1_MISO | LPUART0_TX |      | SPI1_MOSI | FXIO0_D7 | LCD_P47 |

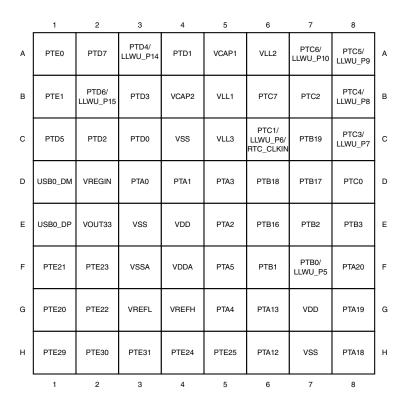

# 5.2 KL43 Family Pinouts

Figure below shows the 64 LQFP pinouts

Figure 24. 64 MAPBGA Pinout diagram

# 6 Ordering parts

## 6.1 Determining valid orderable parts

Valid orderable part numbers are provided on the Web. To determine the orderable part numbers for this device, go to freescale.com and perform a part number search for the following device numbers:

## 7 Part identification

# 8 Terminology and guidelines

## 8.1 Definitions

Key terms are defined in the following table:

| Term                  | Definition                                                                                                                                                                                                                          |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rating                | A minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:                                                                                                                       |

|                       | <ul> <li>Operating ratings apply during operation of the chip.</li> <li>Handling ratings apply when the chip is not powered.</li> </ul>                                                                                             |

|                       | NOTE: The likelihood of permanent chip failure increases rapidly as soon as a characteristic begins to exceed one of its operating ratings.                                                                                         |

| Operating requirement | A specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip                                       |

| Operating behavior    | A specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions                                                  |

| Typical value         | A specified value for a technical characteristic that:                                                                                                                                                                              |

|                       | <ul> <li>Lies within the range of values specified by the operating behavior</li> <li>Is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions</li> </ul> |

|                       | NOTE: Typical values are provided as design guidelines and are neither tested nor guaranteed.                                                                                                                                       |

# 8.2 Examples

## Operating rating:

| Symbol          | Description               | Min.     | Max. | Unit |

|-----------------|---------------------------|----------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | -0.3 IRM | 1.2  | V    |

### Operating requirement:

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | 0.9  | 1.1  | V    |

## Operating behavior that includes a typical value:

| Symbol | Description                                    | Min.    | Тур. | Max. | Unit |

|--------|------------------------------------------------|---------|------|------|------|

|        | Digital I/O weak<br>pullup/pulldown<br>current | 10 tank | 70   | 130  | μΑ   |

# 8.3 Typical-value conditions

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol         | Description          | Value | Unit |

|----------------|----------------------|-------|------|

| T <sub>A</sub> | Ambient temperature  | 25    | °C   |

| $V_{DD}$       | 3.3 V supply voltage | 3.3   | V    |