Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Product Status             | Not For New Designs                                                               |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | C166SV2                                                                           |

| Core Size                  | 16/32-Bit                                                                         |

| Speed                      | 66MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                       |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                   |

| Number of I/O              | 48                                                                                |

| Program Memory Size        | 160KB (160K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 10K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                         |

| Data Converters            | A/D 19x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-LQFP Exposed Pad                                                               |

| Supplier Device Package    | PG-LQFP-64-22                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2234l20f66lraakxuma1 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Summary of Features**

As this document refers to all of these derivatives, some descriptions may not apply to a specific product, in particular to the special device types.

For simplicity the term XC223[04]L is used for all derivatives throughout this document.

### **General Device Information**

# 2 General Device Information

The XC223[04]L series (16/32-Bit Single-Chip Microcontroller

with 32-Bit Performance) is a part of the Infineon XC2000 Family of full-feature singlechip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 80 million instructions per second) with extended peripheral functionality and enhanced IO capabilities. Optimized peripherals can be adapted flexibly to meet the application requirements. These derivatives utilize clock generation via PLL and internal or external clock sources. On-chip memory modules include program Flash, program RAM, and data RAM.

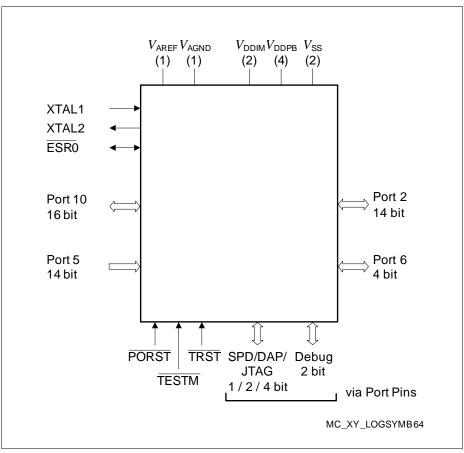

Figure 1 XC223[04]L Logic Symbol

# XC2230L, XC2234L XC2000 Family / Econo Line

# **General Device Information**

| Table |                  | 1      |      | Functions (cont'd)                            |  |  |  |  |  |

|-------|------------------|--------|------|-----------------------------------------------|--|--|--|--|--|

| Pin   | Symbol           | Ctrl.  | Туре |                                               |  |  |  |  |  |

| 34    | P2.6             | 00 / I |      | Bit 6 of Port 2, General Purpose Input/Output |  |  |  |  |  |

|       | U0C0_SELO<br>0   | 01     | St/B | USIC0 Channel 0 Select/Control 0 Output       |  |  |  |  |  |

|       | U0C1_SELO<br>1   | O2     | St/B | USIC0 Channel 1 Select/Control 1 Output       |  |  |  |  |  |

|       | CC2_CC19         | O3 / I | St/B | CAPCOM2 CC19IO Capture Inp./ Compare Out.     |  |  |  |  |  |

|       | CLKIN1           | I      | St/B | Clock Signal Input 1                          |  |  |  |  |  |

|       | U0C0_DX2D        | I      | St/B | USIC0 Channel 0 Shift Control Input           |  |  |  |  |  |

|       | RxDC0D           | I      | St/B | CAN Node 0 Receive Data Input                 |  |  |  |  |  |

|       | ESR2_6           | I      | St/B | ESR2 Trigger Input 6                          |  |  |  |  |  |

| 35    | P2.7             | O0 / I | St/B | Bit 7 of Port 2, General Purpose Input/Output |  |  |  |  |  |

|       | U0C1_SELO<br>0   | 01     | St/B | USIC0 Channel 1 Select/Control 0 Output       |  |  |  |  |  |

|       | U0C0_SELO<br>1   | O2     | St/B | USIC0 Channel 0 Select/Control 1 Output       |  |  |  |  |  |

|       | CC2_CC20         | O3 / I | St/B | CAPCOM2 CC20IO Capture Inp./ Compare Out.     |  |  |  |  |  |

|       | U0C1_DX2C        | I      | St/B | USIC0 Channel 1 Shift Control Input           |  |  |  |  |  |

|       | ESR2_7           | Ι      | St/B | ESR2 Trigger Input 7                          |  |  |  |  |  |

|       | RxDC1C           | Ι      | St/B | CAN Node 1 Receive Data Input                 |  |  |  |  |  |

|       | U1C0_DX0A        | I      | St/B | USIC1 Channel 0 Shift Data Input              |  |  |  |  |  |

| 36    | P2.8             | O0 / I | St/B | Bit 8 of Port 2, General Purpose Input/Output |  |  |  |  |  |

|       | U0C1_SCLK<br>OUT | O1     | St/B | USIC0 Channel 1 Shift Clock Output            |  |  |  |  |  |

|       | EXTCLK           | 02     | St/B | Programmable Clock Signal Output              |  |  |  |  |  |

|       | CC2_CC21         | O3 / I | St/B | CAPCOM2 CC21IO Capture Inp./ Compare Out.     |  |  |  |  |  |

|       | U0C1_DX1D        | I      | St/B | USIC0 Channel 1 Shift Clock Input             |  |  |  |  |  |

| 37    | P2.9             | O0 / I | St/B | Bit 9 of Port 2, General Purpose Input/Output |  |  |  |  |  |

|       | U0C1_DOUT        | 01     | St/B | USIC0 Channel 1 Shift Data Output             |  |  |  |  |  |

|       | TxDC1            | O2     | St/B | CAN Node 1 Transmit Data Output               |  |  |  |  |  |

|       | CC2_CC22         | O3 / I | St/B | CAPCOM2 CC22IO Capture Inp./ Compare Out.     |  |  |  |  |  |

|       | C1               | I      | St/B | Configuration Pin 1                           |  |  |  |  |  |

|       | TCK_A            | I      | St/B | DAP0/JTAG Clock Input                         |  |  |  |  |  |

# XC2230L, XC2234L XC2000 Family / Econo Line

# **General Device Information**

| Pin | Symbol           | Ctrl.  | Туре | Function                                       |

|-----|------------------|--------|------|------------------------------------------------|

|     |                  |        |      |                                                |

| 47  | P10.4            | O0 / I | St/B | Bit 4 of Port 10, General Purpose Input/Output |

|     | U0C0_SELO<br>3   | 01     | St/B | USIC0 Channel 0 Select/Control 3 Output        |

|     | CCU60_COU<br>T61 | O2     | St/B | CCU60 Channel 1 Output                         |

|     | U0C0_DX2B        | I      | St/B | USIC0 Channel 0 Shift Control Input            |

|     | U0C1_DX2B        | I      | St/B | USIC0 Channel 1 Shift Control Input            |

|     | ESR1_9           | I      | St/B | ESR1 Trigger Input 9                           |

| 48  | P10.5            | O0 / I | St/B | Bit 5 of Port 10, General Purpose Input/Output |

|     | U0C1_SCLK<br>OUT | 01     | St/B | USIC0 Channel 1 Shift Clock Output             |

|     | CCU60_COU<br>T62 | O2     | St/B | CCU60 Channel 2 Output                         |

|     | U0C1_DX1B        | I      | St/B | USIC0 Channel 1 Shift Clock Input              |

| 49  | P10.6            | O0 / I | St/B | Bit 6 of Port 10, General Purpose Input/Output |

|     | U0C0_DOUT        | 01     | St/B | USIC0 Channel 0 Shift Data Output              |

|     | U1C0_DOUT        | 02     | St/B | USIC1 Channel 0 Shift Data Output              |

|     | U1C0_SELO<br>0   | O3     | St/B | USIC1 Channel 0 Select/Control 0 Output        |

|     | U0C0_DX0C        | I      | St/B | USIC0 Channel 0 Shift Data Input               |

|     | U1C0_DX2D        | I      | St/B | USIC1 Channel 0 Shift Control Input            |

|     | CCU6x_CTR<br>APA | 1      | St/B | CCU60/CCU63 Emergency Trap Input               |

|     | U1C0_DX0F        | I      | St/B | USIC1 Channel 0 Shift Data Input               |

# **General Device Information**

| Table     | Table 6         Pin Definitions and Functions (cont'd) |        |      |                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|-----------|--------------------------------------------------------|--------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin       | Symbol                                                 | Ctrl.  | Туре | Function                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 62        | XTAL1                                                  | I      | Sp/M | <b>Crystal Oscillator Amplifier Input</b><br>To clock the device from an external source, drive XTAL1, while leaving XTAL2 unconnected. Voltages on XTAL1 must comply to the core supply voltage $V_{\text{DDIM}}$ .                                                                                                                        |  |  |  |  |

|           | ESR2_9                                                 | I      | St/B | ESR2 Trigger Input 9                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 63        | PORST                                                  | 1      | In/B | Power On Reset Input<br>A low level at this pin resets the XC223[04]L<br>completely. A spike filter suppresses input pulses<br><10 ns. Input pulses >100 ns safely pass the filter.<br>The minimum duration for a safe recognition<br>should be 120 ns.<br>An internal pullup device will hold this pin high<br>when nothing is driving it. |  |  |  |  |

| 64        | ESR0                                                   | O0 / I | St/B | External Service Request 0                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|           |                                                        |        |      | Note: After power-up, ESR0 operates as open-<br>drain bidirectional reset with a weak pull-up.                                                                                                                                                                                                                                              |  |  |  |  |

|           | U1C0_DX0E                                              | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|           | U1C0_DX2B                                              | I      | St/B | USIC1 Channel 0 Shift Control Input                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 9         | V <sub>AREF</sub>                                      | -      | PS/B | Reference Voltage for A/D Converters ADC0                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 10        | V <sub>AGND</sub>                                      | -      | PS/B | Reference Ground for A/D Converters ADC0                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 27,<br>57 | V <sub>DDIM</sub>                                      | -      | PS/M | <b>Digital Core Supply Voltage for Domain M</b><br>Decouple with a ceramic capacitor, see Data<br>Sheet for details.<br>All $V_{\text{DDIM}}$ pins must be connected to each other.                                                                                                                                                         |  |  |  |  |

# 3 Functional Description

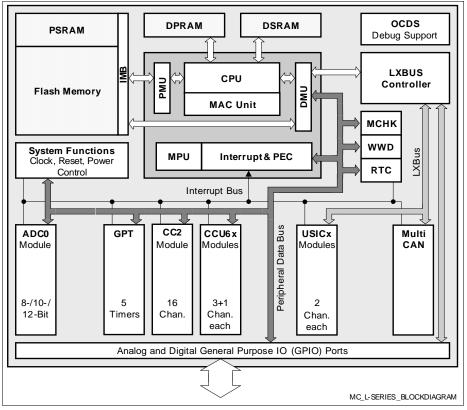

The architecture of the XC223[04]L combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a well-balanced design. On-chip memory blocks allow the design of compact systems-on-silicon with maximum performance suited for computing, control, and communication.

The on-chip memory blocks (program code memory and SRAM, dual-port RAM, data SRAM) and the generic peripherals are connected to the CPU by separate high-speed buses. Another bus, the LXBus, connects additional on-chip resources and external resources (see **Figure 3**). This bus structure enhances overall system performance by enabling the concurrent operation of several subsystems of the XC223[04]L.

The block diagram gives an overview of the on-chip components and the advanced internal bus structure of the XC223[04]L.

Figure 3 Block Diagram

(branching to a dedicated vector table location). The occurrence of a hardware trap is also indicated by a single bit in the trap flag register (TFR). Unless another higher-priority trap service is in progress, a hardware trap will interrupt any ongoing program execution. In turn, hardware trap services can normally not be interrupted by standard or PEC interrupts.

Depending on the package option up to 3 External Service Request (ESR) pins are provided. The ESR unit processes their input values and allows to implement user controlled trap functions (System Requests SR0 and SR1). In this way reset, wakeup and power control can be efficiently realized.

Software interrupts are supported by the 'TRAP' instruction in combination with an individual trap (interrupt) number. Alternatively to emulate an interrupt by software a program can trigger interrupt requests by writing the Interrupt Request (IR) bit of an interrupt control register.

# 3.6 On-Chip Debug Support (OCDS)

The On-Chip Debug Support system built into the XC223[04]L provides a broad range of debug and emulation features. User software running on the XC223[04]L can be debugged within the target system environment.

The OCDS is controlled by an external debugging device via the debug interface. This consists of the 2-pin Device Access Port (DAP) or of the 1-pin Single Pin DAP (SPD) or of the JTAG port conforming to IEEE-1149. The debug interface can be completed with an optional break interface.

The debugger controls the OCDS with a set of dedicated registers accessible via the debug interface (SPD, DAP or JTAG). In addition the OCDS system can be controlled by the CPU, e.g. by a monitor program. An injection interface allows the execution of OCDS-generated instructions by the CPU.

Multiple breakpoints can be triggered by on-chip hardware, by software, or by an external trigger input. Single stepping is supported, as is the injection of arbitrary instructions and read/write access to the complete internal address space. A breakpoint trigger can be answered with a CPU halt, a monitor call, a data transfer, or/and the activation of an external signal.

Tracing of data can be obtained via the debug interface, or via the external bus interface for increased performance.

Tracing of program execution is supported by the XC2000 Family emulation device.

The SPD interface uses one interface signal, DAP interface uses two interface signals, the JTAG interface uses four interface signals, to communicate with external circuitry. The debug interface can be amended with two optional break lines.

# 3.7 Capture/Compare Unit (CC2)

The CAPCOM unit supports generation and control of timing sequences on up to 16 channels with a maximum resolution of one system clock cycle (eight cycles in staggered mode). The CAPCOM unit is typically used to handle high-speed I/O tasks such as pulse and waveform generation, pulse width modulation (PWM), digital to analog (D/A) conversion, software timing, or time recording with respect to external events.

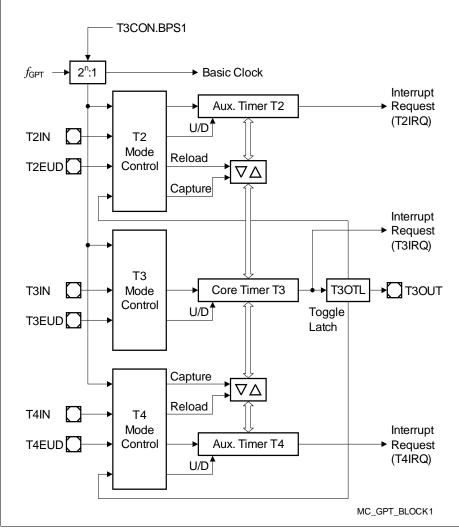

Two 16-bit timers with reload registers provide two independent time bases for the capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal system clock, or may be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range of variation for the timer period and resolution and allows precise adjustments to the application specific requirements. In addition, external count inputs allow event scheduling for the capture/compare registers relative to external events.

The capture/compare register array contains 16 dual purpose capture/compare registers, each of which may be individually allocated to either CAPCOM timer and programmed for capture or compare function.

All registers have each one port pin associated with it which serves as an input pin for triggering the capture function, or as an output pin to indicate the occurrence of a compare event.

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare register in response to an external event at the port pin which is associated with this register. In addition, a specific interrupt request for this capture/compare register is generated. Either a positive, a negative, or both a positive and a negative external signal transition at the pin can be selected as the triggering event.

The contents of all registers which have been selected for one of the five compare modes are continuously compared with the contents of the allocated timers.

When a match occurs between the timer value and the value in a capture/compare register, specific actions will be taken based on the selected compare mode.

| Compare Modes | Function                                                                                   |

|---------------|--------------------------------------------------------------------------------------------|

| Mode 0        | Interrupt-only compare mode;<br>Several compare interrupts per timer period are possible   |

| Mode 1        | Pin toggles on each compare match;<br>Several compare events per timer period are possible |

Table 9 Compare Modes

# XC2230L, XC2234L XC2000 Family / Econo Line

# **Functional Description**

# XC2230L, XC2234L XC2000 Family / Econo Line

# **Functional Description**

#### **MultiCAN Features**

- CAN functionality conforming to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- Independent CAN nodes

- Set of independent message objects (shared by the CAN nodes)

- Dedicated control registers for each CAN node

- Data transfer rate up to 1 Mbit/s, individually programmable for each node

- Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality for message objects:

- Can be assigned to one of the CAN nodes

- Configurable as transmit or receive objects, or as message buffer FIFO

- Handle 11-bit or 29-bit identifiers with programmable acceptance mask for filtering

- Remote Monitoring Mode, and frame counter for monitoring

- Automatic Gateway Mode support

- 16 individually programmable interrupt nodes

- Analyzer mode for CAN bus monitoring

### 3.14 System Timer

The System Timer consists of a programmable prescaler and two concatenated timers (10 bits and 6 bits). Both timers can generate interrupt requests. The clock source can be selected and the timers can also run during power reduction modes.

Therefore, the System Timer enables the software to maintain the current time for scheduling functions or for the implementation of a clock.

# 3.15 Window Watchdog Timer

The Window Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Window Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Window Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Window Watchdog Timer overflows, generating a reset request.

The Window Watchdog Timer has a 'programmable window boundary', it disallows refresh during the Window Watchdog Timer's count-up. A refresh during this window-boundary will cause the Window Watchdog Timer to also generate a reset request.

The Window Watchdog Timer is a 16-bit timer clocked with either the system clock or the independent wake-up oscillator clock, divided by 16,384 or 256. The Window Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Window Watchdog Timer is reloaded.

### 3.18 Power Management

The XC223[04]L provides the means to control the power it consumes either at a given time or averaged over a certain duration.

Two mechanisms can be used (and partly in parallel):

Clock Generation Management controls the frequency of internal and external clock signals. Clock signals for currently inactive parts of logic are disabled automatically. The user can drastically reduce the consumed power by reducing the XC223[04]L system clock frequency.

External circuits can be controlled using the programmable frequency output EXTCLK.

Peripheral Management permits temporary disabling of peripheral modules. Each peripheral can be disabled and enabled separately. The CPU can be switched off while the peripherals can continue to operate.

Wake-up from power reduction modes can be triggered either externally with signals generated by the external system, or internally by the on-chip wake-up timer. This supports intermittent operation of the XC223[04]L by generating cyclic wake-up signals. Full performance is available to quickly react to action requests while the intermittent sleep phases greatly reduce the average system power consumption.

Note: When selecting the supply voltage and the clock source and generation method, the required parameters must be carefully written to the respective bit fields, to avoid unintended intermediate states. Recommended sequences are provided which ensure the intended operation of power supply system and clock system. Please refer to the Programmer's Guide.

### 4.3 DC Parameters

These parameters are static or average values that may be exceeded during switching transitions (e.g. output current).

The XC223[04]L can operate within a wide supply voltage range from 3.0 V to 5.5 V. However, during operation this supply voltage must remain within 10 percent of the selected nominal supply voltage. It cannot vary across the full operating voltage range.

Because of the supply voltage restriction and because electrical behavior depends on the supply voltage, the parameters are specified separately for the upper and the lower voltage range.

During operation, the supply voltages may only change with a maximum speed of dV/dt < 1 V/ms.

Leakage current is strongly dependent on the operating temperature and the voltage level at the respective pin. The maximum values in the following tables apply under worst case conditions, i.e. maximum temperature and an input level equal to the supply voltage.

The value for the leakage current in an application can be determined by using the respective leakage derating formula (see tables) with values from that application.

The pads of the XC223[04]L are designed to operate in various driver modes. The DC parameter specifications refer to the pad current limits specified in **Section 4.7.4**.

| Parameter                               | Symbol               |                                   | Values | 5                          | Unit | Note /                                   |

|-----------------------------------------|----------------------|-----------------------------------|--------|----------------------------|------|------------------------------------------|

|                                         |                      | Min.                              | Тур.   | Max.                       |      | Test Condition                           |

| Input high voltage (all except XTAL1)   | $V_{IH}SR$           | $0.7 	ext{ x}$<br>$V_{	ext{DDP}}$ | -      | V <sub>DDP</sub> + 0.3     | V    |                                          |

| Input low voltage<br>(all except XTAL1) | $V_{IL}SR$           | -0.3                              | -      | 0.3  x<br>$V_{\text{DDP}}$ | V    |                                          |

| Output High voltage <sup>6)</sup>       | V <sub>OH</sub> CC   | V <sub>DDP</sub> - 1.0            | -      | -                          | V    | $I_{\text{OH}} \ge I_{\text{OHmax}}$     |

|                                         |                      | V <sub>DDP</sub> - 0.4            | -      | -                          | V    | $I_{\text{OH}} \ge I_{\text{OHnom}}^{7}$ |

| Output Low Voltage <sup>6)</sup>        | $V_{\rm OL}{\rm CC}$ | -                                 | -      | 0.4                        | V    | $I_{\rm OL} \leq I_{\rm OLnom}^{8}$      |

|                                         |                      | -                                 | -      | 1.0                        | V    | $I_{\rm OL} \leq I_{\rm OLmax}$          |

#### Table 17 DC Characteristics for Lower Voltage Range (cont'd)

Not subject to production test - verified by design/characterization. Hysteresis is implemented to avoid metastable states and switching due to internal ground bounce. It cannot suppress switching due to external system noise under all conditions.

- 2) If the input voltage exceeds the respective supply voltage due to ground bouncing ( $V_{\rm IN} < V_{\rm SS}$ ) or supply ripple ( $V_{\rm IN} > V_{\rm DDP}$ ), a certain amount of current may flow through the protection diodes. This current adds to the leakage current. An additional error current ( $I_{\rm INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{\rm OV}$ .

- 3) The given values are worst-case values. In production test, this leakage current is only tested at 125 °C; other values are ensured by correlation. For derating, please refer to the following descriptions: Leakage derating depending on temperature (*T*<sub>J</sub> = junction temperature [°C]): *I*<sub>OZ</sub> = 0.05 x e<sup>(1.5 + 0.028 × TJ-)</sup> [µA]. For example, at a temperature of 95 °C the resulting leakage current is 3.2 µA. Leakage derating depending on voltage level (DV = *V*<sub>DDP</sub> *V*<sub>PIN</sub> [V]): *I*<sub>OZ</sub> = *I*<sub>OZtempmax</sub> (1.6 x DV) (µA]. This voltage derating formula is an approximation which applies for maximum temperature.

- Drive the indicated minimum current through this pin to change the default pin level driven by the enabled pull device.

- 5) Limit the current through this pin to the indicated value so that the enabled pull device can keep the default pin level.

- 6) The maximum deliverable output current of a port driver depends on the selected output driver mode. This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage is determined by the external circuit.

- As a rule, with decreasing output current the output levels approach the respective supply level (VOL->VSS, VOH->VDDP). However, only the levels for nominal output currents are verified.

- 8) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL}$ -> $V_{SS}$ ,  $V_{OH}$ -> $V_{DDP}$ ). However, only the levels for nominal output currents are verified.

| Table 23 A/D Converter Computation Table |                                           |                     |                                             |  |  |  |  |  |  |

|------------------------------------------|-------------------------------------------|---------------------|---------------------------------------------|--|--|--|--|--|--|

| GLOBCTR.5-0<br>(DIVA)                    | A/D Converter Analog Clock $f_{\rm ADCI}$ | INPCRx.7-0<br>(STC) | Sample Time <sup>1)</sup><br>t <sub>s</sub> |  |  |  |  |  |  |

| 000000 <sub>B</sub>                      | $f_{\rm SYS}$                             | 00 <sub>H</sub>     | $t_{ADCI} 	imes 2$                          |  |  |  |  |  |  |

| 000001 <sub>B</sub>                      | f <sub>SYS</sub> / 2                      | 01 <sub>H</sub>     | $t_{ADCI} 	imes 3$                          |  |  |  |  |  |  |

| 000010 <sub>B</sub>                      | f <sub>SYS</sub> / 3                      | 02 <sub>H</sub>     | $t_{ADCI} 	imes 4$                          |  |  |  |  |  |  |

| :                                        | $f_{\rm SYS}$ / (DIVA+1)                  | :                   | $t_{ADCI} \times (STC+2)$                   |  |  |  |  |  |  |

| 111110 <sub>B</sub>                      | f <sub>SYS</sub> / 63                     | FE <sub>H</sub>     | $t_{\rm ADCI} 	imes 256$                    |  |  |  |  |  |  |

| 111111 <sub>B</sub>                      | f <sub>SYS</sub> / 64                     | FF <sub>H</sub>     | $t_{\rm ADCI} 	imes 257$                    |  |  |  |  |  |  |

# Table 23 A/D Converter Computation Table

1) The selected sample time is doubled if broken wire detection is active (due to the presampling phase).

### **Converter Timing Example A:**

| Assumptions:          | $f_{\rm SYS}$           | = 80 MHz (i.e. $t_{SYS}$ = 12.5 ns), DIVA = 03 <sub>H</sub> , STC = 00 <sub>H</sub>                  |

|-----------------------|-------------------------|------------------------------------------------------------------------------------------------------|

| Analog clock          | $f_{\rm ADCI}$          | $= f_{SYS} / 4 = 20 \text{ MHz}$ , i.e. $t_{ADCI} = 50 \text{ ns}$                                   |

| Sample time           | t <sub>S</sub>          | $= t_{ADCI} \times 2 = 100 \text{ ns}$                                                               |

| Conversion 12-        | bit:                    |                                                                                                      |

|                       | <i>t</i> <sub>C12</sub> | = $16 \times t_{ADCI}$ + 2 × $t_{SYS}$ = 16 × 50 ns + 2 × 12.5 ns = 0.825 µs                         |

| Conversion 10-        | bit:                    |                                                                                                      |

|                       | <i>t</i> <sub>C10</sub> | = $12 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $12 \times 50$ ns + $2 \times 12.5$ ns = 0.625 $\mu$ s |

| <b>Conversion 8-b</b> | it:                     |                                                                                                      |

|                       | t <sub>C8</sub>         | = $10 \times t_{ADCI}$ + $2 \times t_{SYS}$ = $10 \times 50$ ns + $2 \times 12.5$ ns = 0.525 µs      |

| Converter Timir       | ng Exar                 | nple B:                                                                                              |

|                       | _                       |                                                                                                      |

| Assumptions:          | $f_{\rm SYS}$           | = 66 MHz (i.e. $t_{SYS}$ = 15.2 ns), DIVA = 03 <sub>H</sub> , STC = 00 <sub>H</sub>                  |

| Analog clock          | $f_{\rm ADCI}$          | $= f_{SYS} / 4 = 16.5 \text{ MHz}$ , i.e. $t_{ADCI} = 60.6 \text{ ns}$                               |

| Sample time           | t <sub>S</sub>          | $= t_{ADCI} \times 2 = 121.2 \text{ ns}$                                                             |

| Conversion 12-        | bit:                    |                                                                                                      |

| 0                     | <i>t</i> <sub>C12</sub> | = $16 \times t_{ADCI}$ + 2 × $t_{SYS}$ = 16 × 60.6 ns + 2 × 15.2 ns = 1.0 µs                         |

### Conversion 10-bit:

$$t_{C10} = 12 \times t_{ADCI} + 2 \times t_{SYS} = 12 \times 60.6 \text{ ns} + 2 \times 15.2 \text{ ns} = 0.758 \ \mu \text{s}$$

### 4.6 Flash Memory Parameters

The XC223[04]L is delivered with all Flash sectors erased and with no protection installed.

The data retention time of the XC223[04]L's Flash memory (i.e. the time after which stored data can still be retrieved) depends on the number of times the Flash memory has been erased and programmed.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

#### Table 27Flash Parameters

| Parameter                                                  | Symbol                     | Values |                 |                 | Unit       | Note /                          |

|------------------------------------------------------------|----------------------------|--------|-----------------|-----------------|------------|---------------------------------|

|                                                            |                            | Min.   | Тур.            | Max.            | _          | Test Condition                  |

| Parallel Flash module                                      | $N_{\rm PP}{\rm SR}$       | -      | _               | 2 <sup>1)</sup> |            | $N_{FL_RD} \leq 1$              |

| program/erase limit<br>depending on Flash read<br>activity |                            | -      | -               | 1 <sup>2)</sup> |            | N <sub>FL_RD</sub> > 1          |

| Flash erase endurance for security pages                   | $N_{\rm SEC}~{ m SR}$      | 10     | -               | -               | cycle<br>s | $t_{\rm RET} \ge 20$ years      |

| Flash wait states <sup>3)</sup>                            | N <sub>WSFLASH</sub><br>SR | 1      | -               | -               |            | f <sub>SYS</sub> ≤ 8 MHz        |

|                                                            |                            | 2      | -               | -               |            | $f_{SYS} \le 13 \text{ MHz}$    |

|                                                            |                            | 3      | -               | -               |            | $f_{\rm SYS} \le 17 \ { m MHz}$ |

|                                                            |                            | 4      | -               | -               |            | $f_{\rm SYS}$ > 17 MHz          |

| Erase time per<br>sector/page                              | t <sub>ER</sub> CC         | -      | 7 <sup>4)</sup> | 8.0             | ms         |                                 |

| Programming time per page                                  | t <sub>PR</sub> CC         | -      | 3 <sup>4)</sup> | 3.5             | ms         |                                 |

| Data retention time                                        | t <sub>RET</sub> CC        | 20     | -               | -               | year<br>s  | $N_{\rm ER} \le$ 1,000 cycl es  |

| Drain disturb limit                                        | $N_{\rm DD}{ m SR}$        | 32     | -               | -               | cycle<br>s |                                 |

| Parameter              | Symbol             |      | Values |       | Unit       | Note /                                                                                               |

|------------------------|--------------------|------|--------|-------|------------|------------------------------------------------------------------------------------------------------|

|                        |                    | Min. | Тур.   | Max.  | 1          | Test Condition                                                                                       |

| Number of erase cycles | N <sub>ER</sub> SR | -    | -      | 15000 | cycle<br>s | $t_{\text{RET}} \ge 5$ years;<br>Valid for up to<br>64 user<br>selected<br>sectors (data<br>storage) |

|                        |                    | -    | -      | 1000  | cycle<br>s | $t_{\text{RET}} \ge 20$ years                                                                        |

### Table 27 Flash Parameters (cont'd)

All Flash module(s) can be erased/programmed while code is executed and/or data is read from only one Flash module or from PSRAM. The Flash module that delivers code/data can, of course, not be erased/programmed.

2) Flash module 1 can be erased/programmed while code is executed and/or data is read from Flash module 0.

- 3) Value of IMB\_IMBCTRL.WSFLASH.

- 4) Programming and erase times depend on the internal Flash clock source. The control state machine needs a few system clock cycles. This increases the stated durations noticably only at extremely low system clock frequencies.

Access to the XC223[04]L Flash modules is controlled by the IMB. Built-in prefetch mechanisms optimize the performance for sequential access.

Flash access waitstates only affect non-sequential access. Due to prefetch mechanisms, the performance for sequential access (depending on the software structure) is only partially influenced by waitstates.

# 4.7.4 Pad Properties

The output pad drivers of the XC223[04]L can operate in several user-selectable modes. Strong driver mode allows controlling external components requiring higher currents such as power bridges or LEDs. Reducing the driving power of an output pad reduces electromagnetic emissions (EME). In strong driver mode, selecting a slower edge reduces EME.

The dynamic behavior, i.e. the rise time and fall time, depends on the applied external capacitance that must be charged and discharged. Timing values are given for a capacitance of 20 pF, unless otherwise noted.

In general, the performance of a pad driver depends on the available supply voltage  $V_{\text{DDP}}$ . Therefore the following tables list the pad parameters for the upper voltage range and the lower voltage range, respectively.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

**Table 30** is valid under the following conditions:  $V_{\text{DDP}} \le 5.5 \text{ V}$ ;  $V_{\text{DDP}}$  typ. 5 V;  $V_{\text{DDP}} \ge 4.5 \text{ V}$

| Parameter                                                       | Symbol                  |      | Value | S    | Unit | Note /                      |

|-----------------------------------------------------------------|-------------------------|------|-------|------|------|-----------------------------|

|                                                                 |                         | Min. | Тур.  | Max. |      | Test Condition              |

| Maximum output driver<br>current (absolute value) <sup>1)</sup> | I <sub>Omax</sub><br>CC | -    | -     | 3.0  | mA   | Driver_Strength<br>= Medium |

|                                                                 |                         | -    | -     | 5.0  | mA   | Driver_Strength<br>= Strong |

|                                                                 |                         | -    | -     | 0.5  | mA   | Driver_Strength<br>= Weak   |

| Nominal output driver current (absolute value)                  | Onom                    | -    | -     | 1.0  | mA   | Driver_Strength<br>= Medium |

|                                                                 |                         | -    | -     | 1.6  | mA   | Driver_Strength<br>= Strong |

|                                                                 |                         | -    | -     | 0.25 | mA   | Driver_Strength<br>= Weak   |

Table 30 Standard Pad Parameters for Upper Voltage Range

### Debug via JTAG

The following parameters are applicable for communication through the JTAG debug interface. The JTAG module is fully compliant with IEEE1149.1-2000.

Note: These parameters are not subject to production test but verified by design and/or characterization.

Note: Operating Conditions apply.

**Table 38** is valid under the following conditions:  $C_1 = 20 \text{ pF}$ ; voltage\_range= upper

| Parameter                                                                | Symbol                    |                   | Values | 5    | Unit | Note /         |

|--------------------------------------------------------------------------|---------------------------|-------------------|--------|------|------|----------------|

|                                                                          |                           | Min.              | Тур.   | Max. |      | Test Condition |

| TCK clock period                                                         | t <sub>1</sub> SR         | 100 <sup>1)</sup> | -      | -    | ns   | 2)             |

| TCK high time                                                            | t <sub>2</sub> SR         | 16                | -      | -    | ns   |                |

| TCK low time                                                             | t <sub>3</sub> SR         | 16                | -      | -    | ns   |                |

| TCK clock rise time                                                      | $t_4$ SR                  | -                 | -      | 8    | ns   |                |

| TCK clock fall time                                                      | t <sub>5</sub> SR         | -                 | -      | 8    | ns   |                |

| TDI/TMS setup to TCK rising edge                                         | t <sub>6</sub> SR         | 6                 | -      | -    | ns   |                |

| TDI/TMS hold after TCK rising edge                                       | t <sub>7</sub> SR         | 6                 | -      | -    | ns   |                |

| TDO valid from TCK falling edge (propagation delay) <sup>3)</sup>        | t <sub>8</sub> CC         | -                 | 29     | 32   | ns   |                |

| TDO high impedance to valid output from TCK falling edge <sup>4)3)</sup> | t <sub>9</sub> CC         | _                 | 29     | 32   | ns   |                |

| TDO valid output to high impedance from TCK falling edge <sup>3)</sup>   | <i>t</i> <sub>10</sub> CC | _                 | 29     | 32   | ns   |                |

| TDO hold after TCK falling edge <sup>3)</sup>                            | <i>t</i> <sub>18</sub> CC | 5                 | -      | -    | ns   |                |

#### Table 38 JTAG Interface Timing for Upper Voltage Range

1) The debug interface cannot operate faster than the overall system, therefore  $t_1 \ge t_{SYS}$ .

2) Under typical conditions, the JTAG interface can operate at transfer rates up to 10 MHz.

3) The falling edge on TCK is used to generate the TDO timing.

4) The setup time for TDO is given implicitly by the TCK cycle time.

### Package and Reliability

# 5 Package and Reliability

The XC2000 Family devices use the package type:

• PG-LQFP (Plastic Green - Low Profile Quad Flat Package)

The following specifications must be regarded to ensure proper integration of the XC223[04]L in its target environment.

# 5.1 Packaging

These parameters specify the packaging rather than the silicon.

| Parameter                              | Symbol           | Limit Values |               | Unit | Notes                                    |

|----------------------------------------|------------------|--------------|---------------|------|------------------------------------------|

|                                        |                  | Min.         | Max.          |      |                                          |

| Exposed Pad Dimension                  | $E x \times E y$ | _            | 5.4 	imes 5.4 | mm   | -                                        |

| Power Dissipation                      | $P_{DISS}$       | -            | 0.7           | W    | -                                        |

| Thermal resistance<br>Junction-Ambient | $R_{\odot JA}$   | -            | 65            | K/W  | No thermal via,<br>2-layer <sup>1)</sup> |

|                                        |                  |              | 47            | K/W  | No thermal via,<br>4-layer <sup>2)</sup> |

|                                        |                  |              | 45            | K/W  | 4-layer, no pad <sup>3)</sup>            |

|                                        |                  |              | 32            | K/W  | 4-layer, pad <sup>4)</sup>               |

### Table 40 Package Parameters (PG-LQFP-64-22/-24)

Device mounted on a 2-layer JEDEC board (according to JESD 51-3) without thermal vias; exposed pad not soldered.

Device mounted on a 4-layer JEDEC board (according to JESD 51-7) without thermal vias; exposed pad not soldered.

- Device mounted on a 4-layer JEDEC board (according to JESD 51-7) with thermal vias; exposed pad not soldered.

- Device mounted on a 4-layer JEDEC board (according to JESD 51-7) with thermal vias; exposed pad soldered to the board.

- Note: To improve the EMC behavior, it is recommended to connect the exposed pad to the board ground, independent of the thermal requirements. Board layout examples are given in an application note.

# Package Compatibility Considerations

The XC223[04]L is a member of the XC2000 Family of microcontrollers. It is also compatible to a certain extent with members of similar families or subfamilies.

Each package is optimized for the device it houses. Therefore, there may be slight differences between packages of the same pin-count but for different device types. In