# E·XFL

## Intel - 10AS066K2F40E1SG Datasheet

Welcome to E-XFL.COM

Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| 2000                    |                                                                            |

|-------------------------|----------------------------------------------------------------------------|

| Product Status          | Discontinued at Digi-Key                                                   |

| Architecture            | MCU, FPGA                                                                  |

| Core Processor          | Dual ARM® Cortex®-A9 MPCore <sup>™</sup> with CoreSight <sup>™</sup>       |

| Flash Size              | -                                                                          |

| RAM Size                | 256KB                                                                      |

| Peripherals             | DMA, POR, WDT                                                              |

| Connectivity            | EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Speed                   | 1.5GHz                                                                     |

| Primary Attributes      | FPGA - 660K Logic Elements                                                 |

| Operating Temperature   | 0°C ~ 100°C (TJ)                                                           |

| Package / Case          | 1517-BBGA, FCBGA                                                           |

| Supplier Device Package | 1517-FCBGA (40x40)                                                         |

| Purchase URL            | https://www.e-xfl.com/product-detail/intel/10as066k2f40e1sg                |

|                         |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Contents

|                                                          | _              |

|----------------------------------------------------------|----------------|

| Intel <sup>®</sup> Arria <sup>®</sup> 10 Device Overview |                |

| Key Advantages of Intel Arria 10 Devices                 |                |

| Summary of Intel Arria 10 Features                       |                |

| Intel Arria 10 Device Variants and Packages              |                |

| Intel Arria 10 GX                                        | 7              |

|                                                          |                |

|                                                          |                |

| I/O Vertical Migration for Intel Arria 10 Devices        |                |

| Adaptive Logic Module                                    |                |

| Variable-Precision DSP Block                             |                |

| Embedded Memory Blocks                                   |                |

|                                                          |                |

| Embedded Memory Capacity in Intel Arria 1                | 0 Devices      |

| Embedded Memory Configurations for Single                | e-port Mode 22 |

| Clock Networks and PLL Clock Sources                     |                |

| Clock Networks                                           |                |

|                                                          |                |

| FPGA General Purpose I/O                                 |                |

| External Memory Interface                                |                |

|                                                          | 10 Devices 24  |

| PCIe Gen1, Gen2, and Gen3 Hard IP                        |                |

| Enhanced PCS Hard IP for Interlaken and 10 Gbps          | Ethernet26     |

| Interlaken Support                                       |                |

| 10 Gbps Ethernet Support                                 |                |

| Low Power Serial Transceivers                            | 27             |

| Transceiver Channels                                     |                |

| PMA Features                                             |                |

| PCS Features                                             |                |

| SoC with Hard Processor System                           |                |

| Key Advantages of 20-nm HPS                              |                |

| Features of the HPS                                      |                |

| FPGA Configuration and HPS Booting                       |                |

| Hardware and Software Development                        |                |

| Dynamic and Partial Reconfiguration                      |                |

| Dynamic Reconfiguration                                  |                |

| Partial Reconfiguration                                  |                |

| Enhanced Configuration and Configuration via Prot        | ocol           |

| SEU Error Detection and Correction                       |                |

| Power Management                                         |                |

| Incremental Compilation                                  |                |

| Document Revision History for Intel Arria 10 Devic       | e Overview40   |

| Feature                              |                                                                                                                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Embedded Hard IP<br>blocks           | Variable-precision DSP                                                                                                                | <ul> <li>Native support for signal processing precision levels from 18 x 19 to 54 x 54</li> <li>Native support for 27 x 27 multiplier mode</li> <li>64-bit accumulator and cascade for systolic finite impulse responses (FIRs)</li> <li>Internal coefficient memory banks</li> <li>Preadder/subtractor for improved efficiency</li> <li>Additional pipeline register to increase performance and reduce power</li> <li>Supports floating point arithmetic:         <ul> <li>Perform multiplication, addition, subtraction, multiply-add, multiply-subtract, and complex multiplication.</li> <li>Supports multiplication with accumulation capability, cascade summation, and cascade subtraction capability.</li> <li>Dynamic accumulator reset control.</li> <li>Support direct vector dot and complex multiplication chaining multiply floating point DSP blocks.</li> </ul> </li> </ul> |

|                                      | Memory controller                                                                                                                     | DDR4, DDR3, and DDR3L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                      | PCI Express*                                                                                                                          | PCI Express (PCIe*) Gen3 (x1, x2, x4, or x8), Gen2 (x1, x2, x4, or x8) and Gen1 (x1, x2, x4, or x8) hard IP with complete protocol stack, endpoint, and root port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                      | Transceiver I/O                                                                                                                       | <ul> <li>10GBASE-KR/40GBASE-KR4 Forward Error Correction (FEC)</li> <li>PCS hard IPs that support: <ul> <li>10-Gbps Ethernet (10GbE)</li> <li>PCIe PIPE interface</li> <li>Interlaken</li> <li>Gbps Ethernet (GbE)</li> <li>Common Public Radio Interface (CPRI) with deterministic latency support</li> <li>Gigabit-capable passive optical network (GPON) with fast lock-time support</li> </ul> </li> <li>13.5G JESD204b</li> <li>8B/10B, 64B/66B, 64B/67B encoders and decoders</li> <li>Custom mode support for proprietary protocols</li> </ul>                                                                                                                                                                                                                                                                                                                                        |

| Core clock networks                  | <ul> <li>667 MHz externa</li> <li>800 MHz LVDS in</li> <li>Global, regional, and</li> </ul>                                           | c clocking, depending on the application:<br>I memory interface clocking with 2,400 Mbps DDR4 interface<br>terface clocking with 1,600 Mbps LVDS interface<br>I peripheral clock networks<br>are not used can be gated to reduce dynamic power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Phase-locked loops<br>(PLLs)         | <ul> <li>Support integer r</li> <li>Fractional mode s</li> <li>Integer PLLs:         <ul> <li>Adjacent to gene</li> </ul> </li> </ul> | nthesis, clock delay compensation, and zero delay buffering (ZDB)<br>node and fractional mode<br>support with third-order delta-sigma modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FPGA General-purpose<br>I/Os (GPIOs) | On-chip termination                                                                                                                   | ry pair can be configured as receiver or transmitter<br>(OCT)<br>-ended LVTTL/LVCMOS interfacing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| External Memory<br>Interface         | <ul> <li>DDR4—speeds up</li> <li>DDR3—speeds up</li> </ul>                                                                            | Iller— DDR4, DDR3, and DDR3L support<br>to 1,200 MHz/2,400 Mbps<br>to 1,067 MHz/2,133 Mbps<br>Ier—provides support for RLDRAM 3 <sup>(2)</sup> , QDR IV <sup>(2)</sup> , and QDR II+<br><b>continued</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Feature            | Description                                                                                                                                                                                                                                                       |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | <ul> <li>Dynamic reconfiguration of the transceivers and PLLs</li> <li>Fine-grained partial reconfiguration of the core fabric</li> <li>Active Serial x4 Interface</li> </ul>                                                                                     |

| Power management   | <ul> <li>SmartVID</li> <li>Low static power device options</li> <li>Programmable Power Technology</li> <li>Intel Quartus Prime integrated power analysis</li> </ul>                                                                                               |

| Software and tools | <ul> <li>Intel Quartus Prime design suite</li> <li>Transceiver toolkit</li> <li>Platform Designer system integration tool</li> <li>DSP Builder for Intel FPGAs</li> <li>OpenCL<sup>™</sup> support</li> <li>Intel SoC FPGA Embedded Design Suite (EDS)</li> </ul> |

#### Intel Arria 10 Transceiver PHY Overview Provides details on Intel Arria 10 transceivers.

## **Intel Arria 10 Device Variants and Packages**

#### Table 4. Device Variants for the Intel Arria 10 Device Family

| Variant           | Description                                                                                                                                                                                                                                         |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Intel Arria 10 GX | FPGA featuring 17.4 Gbps transceivers for short reach applications with 12.5 backplane driving capability.                                                                                                                                          |

| Intel Arria 10 GT | <ul> <li>FPGA featuring:</li> <li>17.4 Gbps transceivers for short reach applications with 12.5 backplane driving capability.</li> <li>25.8 Gbps transceivers for supporting CAUI-4 and CEI-25G applications with CFP2 and CFP4 modules.</li> </ul> |

| Intel Arria 10 SX | SoC integrating ARM-based HPS and FPGA featuring 17.4 Gbps transceivers for short reach applications with 12.5 backplane driving capability.                                                                                                        |

## **Intel Arria 10 GX**

This section provides the available options, maximum resource counts, and package plan for the Intel Arria 10 GX devices.

The information in this section is correct at the time of publication. For the latest information and to get more details, refer to the Intel FPGA Product Selector.

#### **Related Information**

#### Intel FPGA Product Selector

Provides the latest information on Intel products.

## **Available Options**

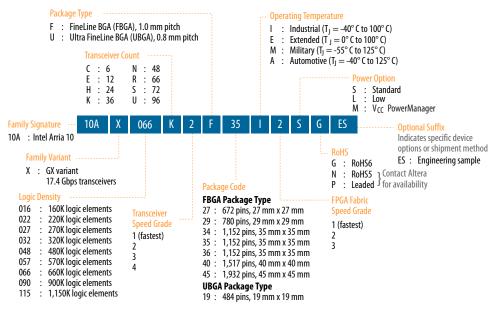

#### Figure 1. Sample Ordering Code and Available Options for Intel Arria 10 GX Devices

#### **Related Information**

Transceiver Performance for Intel Arria 10 GX/SX Devices Provides more information about the transceiver speed grade.

#### **Maximum Resources**

## Table 5.Maximum Resource Counts for Intel Arria 10 GX Devices (GX 160, GX 220, GX<br/>270, GX 320, and GX 480)

| Resource                 |                              |         | Product Line |         |         |         |  |  |  |

|--------------------------|------------------------------|---------|--------------|---------|---------|---------|--|--|--|

|                          |                              | GX 160  | GX 220       | GX 270  | GX 320  | GX 480  |  |  |  |

| Logic Elements           | (LE) (K)                     | 160     | 220          | 270     | 320     | 480     |  |  |  |

| ALM                      |                              | 61,510  | 80,330       | 101,620 | 119,900 | 183,590 |  |  |  |

| Register                 |                              | 246,040 | 321,320      | 406,480 | 479,600 | 734,360 |  |  |  |

| Memory (Kb)              | M20K                         | 8,800   | 11,740       | 15,000  | 17,820  | 28,620  |  |  |  |

|                          | MLAB                         | 1,050   | 1,690        | 2,452   | 2,727   | 4,164   |  |  |  |

| Variable-precisi         | Variable-precision DSP Block |         | 192          | 830     | 985     | 1,368   |  |  |  |

| 18 x 19 Multipli         | er                           | 312     | 384 1        |         | 1,970   | 2,736   |  |  |  |

| PLL                      | Fractional<br>Synthesis      | 6       | 6            | 8       | 8       | 12      |  |  |  |

|                          | I/O                          | 6       | 6            | 8       | 8       | 12      |  |  |  |

| 17.4 Gbps Trans          | sceiver                      | 12      | 12           | 24      | 24      | 36      |  |  |  |

| GPIO <sup>(3)</sup>      |                              | 288     | 288          | 384     | 384     | 492     |  |  |  |

| LVDS Pair <sup>(4)</sup> |                              | 120     | 120          | 168     | 168     | 222     |  |  |  |

| PCIe Hard IP Block       |                              | 1       | 1            | 2       | 2       | 2       |  |  |  |

| Hard Memory C            | ontroller                    | 6       | 6            | 8       | 8       | 12      |  |  |  |

<sup>&</sup>lt;sup>(3)</sup> The number of GPIOs does not include transceiver I/Os. In the Intel Quartus Prime software, the number of user I/Os includes transceiver I/Os.

<sup>&</sup>lt;sup>(4)</sup> Each LVDS I/O pair can be used as differential input or output.

## Table 6.Maximum Resource Counts for Intel Arria 10 GX Devices (GX 570, GX 660, GX 900, and GX 1150)

| Re                       | source                  |         | Produc    | t Line    |           |

|--------------------------|-------------------------|---------|-----------|-----------|-----------|

|                          |                         | GX 570  | GX 660    | GX 900    | GX 1150   |

| Logic Elements           | s (LE) (K)              | 570     | 660       | 900       | 1,150     |

| ALM                      |                         | 217,080 | 251,680   | 339,620   | 427,200   |

| Register                 |                         | 868,320 | 1,006,720 | 1,358,480 | 1,708,800 |

| Memory (Kb)              | M20K                    | 36,000  | 42,620    | 48,460    | 54,260    |

| MLAB                     |                         | 5,096   | 5,788     | 9,386     | 12,984    |

| Variable-precis          | sion DSP Block          | 1,523   | 1,687     | 1,518     | 1,518     |

| 18 x 19 Multip           | lier                    | 3,046   | 3,374     | 3,036     | 3,036     |

| PLL                      | Fractional<br>Synthesis | 16      | 16        | 32        | 32        |

|                          | I/O                     | 16      | 16        | 16        | 16        |

| 17.4 Gbps Trai           | nsceiver                | 48      | 48        | 96        | 96        |

| GPIO <sup>(3)</sup>      |                         | 696     | 696       | 768       | 768       |

| LVDS Pair <sup>(4)</sup> |                         | 324     | 324 38    |           | 384       |

| PCIe Hard IP E           | Block                   | 2       | 2         | 4         | 4         |

| Hard Memory              | Controller              | 16      | 16        | 16        | 16        |

## Package Plan

## Table 7.Package Plan for Intel Arria 10 GX Devices (U19, F27, and F29)

Refer to I/O and High Speed I/O in Intel Arria 10 Devices chapter for the number of 3 V I/O, LVDS I/O, and LVDS channels in each device package.

| Product Line | U19<br>(19 mm × 19 mm,<br>484-pin UBGA) |          |      | (19 mm × 19 mm, (27 mm × 27 mm, |     |    | F29<br>(29 mm × 29 mm,<br>780-pin FBGA) |          |      |

|--------------|-----------------------------------------|----------|------|---------------------------------|-----|----|-----------------------------------------|----------|------|

|              | 3 V I/O                                 | LVDS I/O | XCVR | 3 V I/O LVDS I/O XCVR           |     |    | 3 V I/O                                 | LVDS I/O | XCVR |

| GX 160       | 48                                      | 192      | 6    | 48                              | 192 | 12 | 48                                      | 240      | 12   |

| GX 220       | 48                                      | 192      | 6    | 48                              | 192 | 12 | 48                                      | 240      | 12   |

| GX 270       | -                                       | -        | _    | 48                              | 192 | 12 | 48                                      | 312      | 12   |

| GX 320       | -                                       | -        | _    | 48                              | 192 | 12 | 48                                      | 312      | 12   |

| GX 480       | _                                       | _        | _    | _                               | _   | _  | 48                                      | 312      | 12   |

#### **Maximum Resources**

#### Table 10. Maximum Resource Counts for Intel Arria 10 GT Devices

| Reso                         | urce                     | Product Line      |                   |  |

|------------------------------|--------------------------|-------------------|-------------------|--|

|                              |                          | GT 900            | GT 1150           |  |

| Logic Elements (LE) (K)      |                          | 900               | 1,150             |  |

| ALM                          |                          | 339,620           | 427,200           |  |

| Register                     |                          | 1,358,480         | 1,708,800         |  |

| Memory (Kb)                  | M20K                     | 48,460            | 54,260            |  |

|                              | MLAB                     | 9,386             | 12,984            |  |

| Variable-precision DSP Block | able-precision DSP Block |                   | 1,518             |  |

| 18 x 19 Multiplier           |                          | 3,036             | 3,036             |  |

| PLL                          | Fractional Synthesis     | 32                | 32                |  |

|                              | I/O                      | 16                | 16                |  |

| Transceiver                  | 17.4 Gbps                | 72 <sup>(5)</sup> | 72 <sup>(5)</sup> |  |

|                              | 25.8 Gbps                | 6                 | 6                 |  |

| GPIO <sup>(6)</sup>          |                          | 624               | 624               |  |

| LVDS Pair <sup>(7)</sup>     |                          | 312               | 312               |  |

| PCIe Hard IP Block           |                          | 4                 | 4                 |  |

| Hard Memory Controller       |                          | 16                | 16                |  |

#### **Related Information**

#### Intel Arria 10 GT Channel Usage

Configuring GT/GX channels in Intel Arria 10 GT devices.

## Package Plan

#### Table 11.Package Plan for Intel Arria 10 GT Devices

Refer to I/O and High Speed I/O in Intel Arria 10 Devices chapter for the number of 3 V I/O, LVDS I/O, and LVDS channels in each device package.

| Product Line | SF45<br>(45 mm × 45 mm, 1932-pin FBGA) |          |      |  |  |

|--------------|----------------------------------------|----------|------|--|--|

|              | 3 V I/O                                | LVDS I/O | XCVR |  |  |

| GT 900       | —                                      | 624      | 72   |  |  |

| GT 1150      | _                                      | 624      | 72   |  |  |

<sup>&</sup>lt;sup>(5)</sup> If all 6 GT channels are in use, 12 of the GX channels are not usable.

<sup>&</sup>lt;sup>(6)</sup> The number of GPIOs does not include transceiver I/Os. In the Intel Quartus Prime software, the number of user I/Os includes transceiver I/Os.

<sup>&</sup>lt;sup>(7)</sup> Each LVDS I/O pair can be used as differential input or output.

I/O and High-Speed Differential I/O Interfaces in Intel Arria 10 Devices chapter, Intel Arria 10 Device Handbook

Provides the number of 3 V and LVDS I/Os, and LVDS channels for each Intel Arria 10 device package.

### **Intel Arria 10 SX**

This section provides the available options, maximum resource counts, and package plan for the Intel Arria 10 SX devices.

The information in this section is correct at the time of publication. For the latest information and to get more details, refer to the Intel FPGA Product Selector.

#### **Related Information**

Intel FPGA Product Selector

Provides the latest information on Intel products.

#### **Available Options**

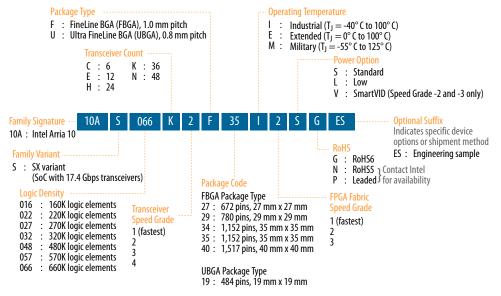

#### Figure 3. Sample Ordering Code and Available Options for Intel Arria 10 SX Devices

#### **Related Information**

Transceiver Performance for Intel Arria 10 GX/SX Devices Provides more information about the transceiver speed grade.

| Product Line | U19<br>(19 mm × 19 mm,<br>484-pin UBGA) |             |      | F27<br>nm × 27<br>2-pin FB( |             |      | F29<br>nm × 29<br>)-pin FB( |             |      | F34<br>nm × 35<br>2-pin FB |             |      |

|--------------|-----------------------------------------|-------------|------|-----------------------------|-------------|------|-----------------------------|-------------|------|----------------------------|-------------|------|

|              | 3 V<br>I/O                              | LVDS<br>I/O | XCVR | 3 V<br>I/O                  | LVDS<br>I/O | XCVR | 3 V<br>I/O                  | LVDS<br>I/O | XCVR | 3 V<br>I/O                 | LVDS<br>I/O | XCVR |

| SX 480       | -                                       | -           | _    | _                           | -           | -    | 48                          | 312         | 12   | 48                         | 444         | 24   |

| SX 570       | -                                       | -           | _    | _                           | -           | -    | _                           | _           | -    | 48                         | 444         | 24   |

| SX 660       | -                                       | -           | -    | -                           | -           | -    | _                           | -           | -    | 48                         | 444         | 24   |

#### Table 14. Package Plan for Intel Arria 10 SX Devices (F35, KF40, and NF40)

Refer to I/O and High Speed I/O in Intel Arria 10 Devices chapter for the number of 3 V I/O, LVDS I/O, and LVDS channels in each device package.

| Product Line | F35<br>(35 mm × 35 mm,<br>1152-pin FBGA) |          |      | (35 mm × 35 mm, (40 mm × 40 mm, |     |         | NF40<br>(40 mm × 40 mm,<br>1517-pin FBGA) |      |    |

|--------------|------------------------------------------|----------|------|---------------------------------|-----|---------|-------------------------------------------|------|----|

|              | 3 V I/O                                  | LVDS I/O | XCVR | 3 V I/O LVDS I/O XCVR           |     | 3 V I/O | LVDS I/O                                  | XCVR |    |

| SX 270       | 48                                       | 336      | 24   | -                               | _   | _       | -                                         | -    | _  |

| SX 320       | 48                                       | 336      | 24   | -                               | _   | _       | _                                         | _    | _  |

| SX 480       | 48                                       | 348      | 36   | -                               | _   | _       | -                                         | -    | _  |

| SX 570       | 48                                       | 348      | 36   | 96                              | 600 | 36      | 48                                        | 540  | 48 |

| SX 660       | 48                                       | 348      | 36   | 96                              | 600 | 36      | 48                                        | 540  | 48 |

#### **Related Information**

I/O and High-Speed Differential I/O Interfaces in Intel Arria 10 Devices chapter, Intel Arria 10 Device Handbook

Provides the number of 3 V and LVDS I/Os, and LVDS channels for each Intel Arria 10 device package.

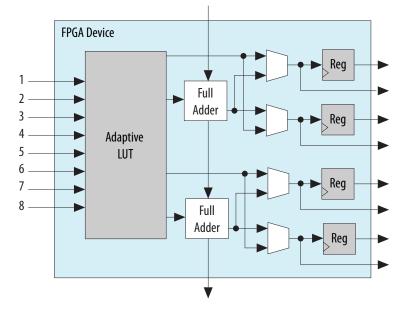

#### Figure 5. ALM for Intel Arria 10 Devices

The Intel Quartus Prime software optimizes your design according to the ALM logic structure and automatically maps legacy designs into the Intel Arria 10 ALM architecture.

## **Variable-Precision DSP Block**

The Intel Arria 10 variable precision DSP blocks support fixed-point arithmetic and floating-point arithmetic.

Features for fixed-point arithmetic:

- High-performance, power-optimized, and fully registered multiplication operations

- 18-bit and 27-bit word lengths

- Two 18 x 19 multipliers or one 27 x 27 multiplier per DSP block

- Built-in addition, subtraction, and 64-bit double accumulation register to combine multiplication results

- Cascading 19-bit or 27-bit when pre-adder is disabled and cascading 18-bit when pre-adder is used to form the tap-delay line for filtering applications

- Cascading 64-bit output bus to propagate output results from one block to the next block without external logic support

- Hard pre-adder supported in 19-bit and 27-bit modes for symmetric filters

- Internal coefficient register bank in both 18-bit and 27-bit modes for filter implementation

- 18-bit and 27-bit systolic finite impulse response (FIR) filters with distributed output adder

- Biased rounding support

## **Types of Embedded Memory**

The Intel Arria 10 devices contain two types of memory blocks:

- 20 Kb M20K blocks—blocks of dedicated memory resources. The M20K blocks are ideal for larger memory arrays while still providing a large number of independent ports.

- 640 bit memory logic array blocks (MLABs)—enhanced memory blocks that are configured from dual-purpose logic array blocks (LABs). The MLABs are ideal for wide and shallow memory arrays. The MLABs are optimized for implementation of shift registers for digital signal processing (DSP) applications, wide and shallow FIFO buffers, and filter delay lines. Each MLAB is made up of ten adaptive logic modules (ALMs). In the Intel Arria 10 devices, you can configure these ALMs as ten 32 x 2 blocks, giving you one 32 x 20 simple dual-port SRAM block per MLAB.

## **Embedded Memory Capacity in Intel Arria 10 Devices**

|                   | Product | M20K  |              | ML     | Total RAM Bit |        |

|-------------------|---------|-------|--------------|--------|---------------|--------|

| Variant           | Line    | Block | RAM Bit (Kb) | Block  | RAM Bit (Kb)  | (Kb)   |

| Intel Arria 10 GX | GX 160  | 440   | 8,800        | 1,680  | 1,050         | 9,850  |

|                   | GX 220  | 587   | 11,740       | 2,703  | 1,690         | 13,430 |

|                   | GX 270  | 750   | 15,000       | 3,922  | 2,452         | 17,452 |

|                   | GX 320  | 891   | 17,820       | 4,363  | 2,727         | 20,547 |

|                   | GX 480  | 1,431 | 28,620       | 6,662  | 4,164         | 32,784 |

|                   | GX 570  | 1,800 | 36,000       | 8,153  | 5,096         | 41,096 |

|                   | GX 660  | 2,131 | 42,620       | 9,260  | 5,788         | 48,408 |

|                   | GX 900  | 2,423 | 48,460       | 15,017 | 9,386         | 57,846 |

|                   | GX 1150 | 2,713 | 54,260       | 20,774 | 12,984        | 67,244 |

| Intel Arria 10 GT | GT 900  | 2,423 | 48,460       | 15,017 | 9,386         | 57,846 |

|                   | GT 1150 | 2,713 | 54,260       | 20,774 | 12,984        | 67,244 |

| Intel Arria 10 SX | SX 160  | 440   | 8,800        | 1,680  | 1,050         | 9,850  |

|                   | SX 220  | 587   | 11,740       | 2,703  | 1,690         | 13,430 |

|                   | SX 270  | 750   | 15,000       | 3,922  | 2,452         | 17,452 |

|                   | SX 320  | 891   | 17,820       | 4,363  | 2,727         | 20,547 |

|                   | SX 480  | 1,431 | 28,620       | 6,662  | 4,164         | 32,784 |

|                   | SX 570  | 1,800 | 36,000       | 8,153  | 5,096         | 41,096 |

|                   | SX 660  | 2,131 | 42,620       | 9,260  | 5,788         | 48,408 |

#### Table 18. Embedded Memory Capacity and Distribution in Intel Arria 10 Devices

#### Intel Arria 10 Device Datasheet

Lists the memory interface performance according to memory interface standards, rank or chip select configurations, and Intel Arria 10 device speed grades.

## PCIe Gen1, Gen2, and Gen3 Hard IP

Intel Arria 10 devices contain PCIe hard IP that is designed for performance and ease-of-use:

- Includes all layers of the PCIe stack—transaction, data link and physical layers.

- Supports PCIe Gen3, Gen2, and Gen1 Endpoint and Root Port in x1, x2, x4, or x8 lane configuration.

- Operates independently from the core logic—optional configuration via protocol (CvP) allows the PCIe link to power up and complete link training in less than 100 ms while the Intel Arria 10 device completes loading the programming file for the rest of the FPGA.

- Provides added functionality that makes it easier to support emerging features such as Single Root I/O Virtualization (SR-IOV) and optional protocol extensions.

- Provides improved end-to-end datapath protection using ECC.

- Supports FPGA configuration via protocol (CvP) using PCIe at Gen3, Gen2, or Gen1 speed.

#### **Related Information**

PCS Features on page 30

## **Enhanced PCS Hard IP for Interlaken and 10 Gbps Ethernet**

#### **Interlaken Support**

The Intel Arria 10 enhanced PCS hard IP provides integrated Interlaken PCS supporting rates up to 25.8 Gbps per lane.

The Interlaken PCS is based on the proven functionality of the PCS developed for Intel's previous generation FPGAs, which demonstrated interoperability with Interlaken ASSP vendors and third-party IP suppliers. The Interlaken PCS is present in every transceiver channel in Intel Arria 10 devices.

#### **Related Information**

PCS Features on page 30

#### **10 Gbps Ethernet Support**

The Intel Arria 10 enhanced PCS hard IP supports 10GBASE-R PCS compliant with IEEE 802.3 10 Gbps Ethernet (10GbE). The integrated hard IP support for 10GbE and the 10 Gbps transceivers save external PHY cost, board space, and system power.

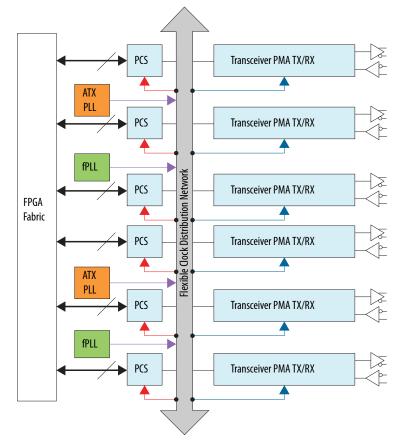

#### Figure 6. Intel Arria 10 Transceiver Block Architecture

#### **Transceiver Channels**

All transceiver channels feature a dedicated Physical Medium Attachment (PMA) and a hardened Physical Coding Sublayer (PCS).

- The PMA provides primary interfacing capabilities to physical channels.

- The PCS typically handles encoding/decoding, word alignment, and other preprocessing functions before transferring data to the FPGA core fabric.

A transceiver channel consists of a PMA and a PCS block. Most transceiver banks have 6 channels. There are some transceiver banks that contain only 3 channels.

A wide variety of bonded and non-bonded data rate configurations is possible using a highly configurable clock distribution network. Up to 80 independent transceiver data rates can be configured.

The following figures are graphical representations of top views of the silicon die, which correspond to reverse views for flip chip packages. Different Intel Arria 10 devices may have different floorplans than the ones shown in the figures.

| PCS           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Standard PCS  | <ul> <li>Operates at a data rate up to 12 Gbps</li> <li>Supports protocols such as PCI-Express, CPRI 4.2+, GigE, IEEE 1588 in Hard PCS</li> <li>Implements other protocols using Basic/Custom (Standard PCS) transceiver configuration rules.</li> </ul>                                                                                                                                                                                           |

| Enhanced PCS  | <ul> <li>Performs functions common to most serial data industry standards, such as word alignment, encoding/decoding, and framing, before data is sent or received off-chip through the PMA</li> <li>Handles data transfer to and from the FPGA fabric</li> <li>Handles data transfer internally to and from the PMA</li> <li>Provides frequency compensation</li> <li>Performs channel bonding for multi-channel low skew applications</li> </ul> |

| PCIe Gen3 PCS | <ul> <li>Supports the seamless switching of Data and Clock between the Gen1, Gen2, and Gen3 data rates</li> <li>Provides support for PIPE 3.0 features</li> <li>Supports the PIPE interface with the Hard IP enabled, as well as with the Hard IP bypassed</li> </ul>                                                                                                                                                                              |

- PCIe Gen1, Gen2, and Gen3 Hard IP on page 26

- Interlaken Support on page 26

- 10 Gbps Ethernet Support on page 26

#### **PCS Protocol Support**

This table lists some of the protocols supported by the Intel Arria 10 transceiver PCS. For more information about the blocks in the transmitter and receiver data paths, refer to the related information.

| Protocol                                        | Data Rate<br>(Gbps) | Transceiver IP              | PCS Support                       |

|-------------------------------------------------|---------------------|-----------------------------|-----------------------------------|

| PCIe Gen3 x1, x2, x4, x8                        | 8.0                 | Native PHY (PIPE)           | Standard PCS and PCIe<br>Gen3 PCS |

| PCIe Gen2 x1, x2, x4, x8                        | 5.0                 | Native PHY (PIPE)           | Standard PCS                      |

| PCIe Gen1 x1, x2, x4, x8                        | 2.5                 | Native PHY (PIPE)           | Standard PCS                      |

| 1000BASE-X Gigabit Ethernet                     | 1.25                | Native PHY                  | Standard PCS                      |

| 1000BASE-X Gigabit Ethernet with<br>IEEE 1588v2 | 1.25                | Native PHY                  | Standard PCS                      |

| 10GBASE-R                                       | 10.3125             | Native PHY                  | Enhanced PCS                      |

| 10GBASE-R with IEEE 1588v2                      | 10.3125             | Native PHY                  | Enhanced PCS                      |

| 10GBASE-R with KR FEC                           | 10.3125             | Native PHY                  | Enhanced PCS                      |

| 10GBASE-KR and 1000BASE-X                       | 10.3125             | 1G/10GbE and 10GBASE-KR PHY | Standard PCS and<br>Enhanced PCS  |

| Interlaken (CEI-6G/11G)                         | 3.125 to 17.4       | Native PHY                  | Enhanced PCS                      |

| SFI-S/SFI-5.2                                   | 11.2                | Native PHY                  | Enhanced PCS                      |

| 10G SDI                                         | 10.692              | Native PHY                  | Enhanced PCS                      |

|                                                 |                     |                             | continued                         |

#### **System Peripherals and Debug Access Port**

Each Ethernet MAC, USB OTG, NAND flash controller, and SD/MMC controller module has an integrated DMA controller. For modules without an integrated DMA controller, an additional DMA controller module provides up to eight channels of high-bandwidth data transfers. Peripherals that communicate off-chip are multiplexed with other peripherals at the HPS pin level. This allows you to choose which peripherals interface with other devices on your PCB.

The debug access port provides interfaces to industry standard JTAG debug probes and supports ARM CoreSight debug and core traces to facilitate software development.

#### **HPS-FPGA AXI Bridges**

The HPS–FPGA bridges, which support the Advanced Microcontroller Bus Architecture (AMBA) Advanced eXtensible Interface (AXI<sup>m</sup>) specifications, consist of the following bridges:

- FPGA-to-HPS AMBA AXI bridge—a high-performance bus supporting 32, 64, and 128 bit data widths that allows the FPGA fabric to issue transactions to slaves in the HPS.

- HPS-to-FPGA Avalon/AMBA AXI bridge—a high-performance bus supporting 32, 64, and 128 bit data widths that allows the HPS to issue transactions to slaves in the FPGA fabric.

- Lightweight HPS-to-FPGA AXI bridge—a lower latency 32 bit width bus that allows the HPS to issue transactions to soft peripherals in the FPGA fabric. This bridge is primarily used for control and status register (CSR) accesses to peripherals in the FPGA fabric.

The HPS–FPGA AXI bridges allow masters in the FPGA fabric to communicate with slaves in the HPS logic, and vice versa. For example, the HPS-to-FPGA AXI bridge allows you to share memories instantiated in the FPGA fabric with one or both microprocessors in the HPS, while the FPGA-to-HPS AXI bridge allows logic in the FPGA fabric to access the memory and peripherals in the HPS.

Each HPS–FPGA bridge also provides asynchronous clock crossing for data transferred between the FPGA fabric and the HPS.

#### **HPS SDRAM Controller Subsystem**

The HPS SDRAM controller subsystem contains a multiport SDRAM controller and DDR PHY that are shared between the FPGA fabric (through the FPGA-to-HPS SDRAM interface), the level 2 (L2) cache, and the level 3 (L3) system interconnect. The FPGA-to-HPS SDRAM interface supports AMBA AXI and Avalon<sup>®</sup> Memory-Mapped (Avalon-MM) interface standards, and provides up to six individual ports for access by masters implemented in the FPGA fabric.

The HPS SDRAM controller supports up to 3 masters (command ports), 3x 64-bit read data ports and 3x 64-bit write data ports.

To maximize memory performance, the SDRAM controller subsystem supports command and data reordering, deficit round-robin arbitration with aging, and high-priority bypass features.

Instead of placing all device functions in the FPGA fabric, you can store some functions that do not run simultaneously in external memory and load them only when required. This capability increases the effective logic density of the device, and lowers cost and power consumption.

In the Intel solution, you do not have to worry about intricate device architecture to perform a partial reconfiguration. The partial reconfiguration capability is built into the Intel Quartus Prime design software, making such time-intensive task simple.

Intel Arria 10 devices support partial reconfiguration in the following configuration options:

- Using an internal host:

- All supported configuration modes where the FPGA has access to external memory devices such as serial and parallel flash memory.

- Configuration via Protocol [CvP (PCIe)]

- Using an external host—passive serial (PS), fast passive parallel (FPP) x8, FPP x16, and FPP x32 I/O interface.

## **Enhanced Configuration and Configuration via Protocol**

#### Table 25. Configuration Schemes and Features of Intel Arria 10 Devices

Intel Arria 10 devices support 1.8 V programming voltage and several configuration schemes.

| Scheme                                                                 | Data<br>Width    | Max Clock<br>Rate<br>(MHz) | Max Data<br>Rate<br>(Mbps)<br>(13) | Decompression | Design<br>Security <sup>(1</sup><br>4) | Partial<br>Reconfiguration<br>(15) | Remote<br>System<br>Update                      |

|------------------------------------------------------------------------|------------------|----------------------------|------------------------------------|---------------|----------------------------------------|------------------------------------|-------------------------------------------------|

| JTAG                                                                   | 1 bit            | 33                         | 33                                 | _             | -                                      | Yes <sup>(16)</sup>                | -                                               |

| Active Serial (AS)<br>through the<br>EPCQ-L<br>configuration<br>device | 1 bit,<br>4 bits | 100                        | 400                                | Yes           | Yes                                    | Yes <sup>(16)</sup>                | Yes                                             |

| Passive serial (PS)<br>through CPLD or<br>external<br>microcontroller  | 1 bit            | 100                        | 100                                | Yes           | Yes                                    | Yes <sup>(16)</sup>                | Parallel<br>Flash<br>Loader<br>(PFL) IP<br>core |

|                                                                        | continued        |                            |                                    |               |                                        |                                    | ntinued                                         |

<sup>&</sup>lt;sup>(13)</sup> Enabling either compression or design security features affects the maximum data rate. Refer to the Intel Arria 10 Device Datasheet for more information.

<sup>&</sup>lt;sup>(14)</sup> Encryption and compression cannot be used simultaneously.

<sup>&</sup>lt;sup>(15)</sup> Partial reconfiguration is an advanced feature of the device family. If you are interested in using partial reconfiguration, contact Intel for support.

<sup>&</sup>lt;sup>(16)</sup> Partial configuration can be performed only when it is configured as internal host.

| Scheme                                         | Data<br>Width              | Max Clock<br>Rate<br>(MHz) | Max Data<br>Rate<br>(Mbps)<br>(13) | Decompression | Design<br>Security <sup>(1</sup><br>4) | Partial<br>Reconfiguration<br>(15) | Remote<br>System<br>Update |

|------------------------------------------------|----------------------------|----------------------------|------------------------------------|---------------|----------------------------------------|------------------------------------|----------------------------|

| Fast passive                                   | 8 bits                     | 100                        | 3200                               | Yes           | Yes                                    | Yes <sup>(17)</sup>                | PFL IP                     |

| parallel (FPP)<br>through CPLD or              | 16 bits                    | ]                          |                                    | Yes           | Yes                                    |                                    | core                       |

| external<br>microcontroller                    | 32 bits                    | ]                          |                                    | Yes           | Yes                                    |                                    |                            |

| Configuration via                              | 16 bits                    | 100                        | 3200                               | Yes           | Yes                                    | Yes <sup>(17)</sup>                | _                          |

| HPS                                            | 32 bits                    |                            |                                    | Yes           | Yes                                    |                                    |                            |

| Configuration via<br>Protocol [CvP<br>(PCIe*)] | x1, x2,<br>x4, x8<br>lanes | -                          | 8000                               | Yes           | Yes                                    | Yes <sup>(16)</sup>                | _                          |

You can configure Intel Arria 10 devices through PCIe using Configuration via Protocol (CvP). The Intel Arria 10 CvP implementation conforms to the PCIe 100 ms power-up-to-active time requirement.

## **SEU Error Detection and Correction**

Intel Arria 10 devices offer robust and easy-to-use single-event upset (SEU) error detection and correction circuitry.

The detection and correction circuitry includes protection for Configuration RAM (CRAM) programming bits and user memories. The CRAM is protected by a continuously running CRC error detection circuit with integrated ECC that automatically corrects one or two errors and detects higher order multi-bit errors. When more than two errors occur, correction is available through reloading of the core programming file, providing a complete design refresh while the FPGA continues to operate.

The physical layout of the Intel Arria 10 CRAM array is optimized to make the majority of multi-bit upsets appear as independent single-bit or double-bit errors which are automatically corrected by the integrated CRAM ECC circuitry. In addition to the CRAM protection, the M20K memory blocks also include integrated ECC circuitry and are layout-optimized for error detection and correction. The MLAB does not have ECC.

## **Power Management**

Intel Arria 10 devices leverage the advanced 20 nm process technology, a low 0.9 V core power supply, an enhanced core architecture, and several optional power reduction techniques to reduce total power consumption by as much as 40% compared to Arria V devices and as much as 60% compared to Stratix V devices.

<sup>&</sup>lt;sup>(13)</sup> Enabling either compression or design security features affects the maximum data rate. Refer to the Intel Arria 10 Device Datasheet for more information.

<sup>&</sup>lt;sup>(14)</sup> Encryption and compression cannot be used simultaneously.

<sup>&</sup>lt;sup>(15)</sup> Partial reconfiguration is an advanced feature of the device family. If you are interested in using partial reconfiguration, contact Intel for support.

<sup>&</sup>lt;sup>(17)</sup> Supported at a maximum clock rate of 100 MHz.

The optional power reduction techniques in Intel Arria 10 devices include:

- SmartVID—a code is programmed into each device during manufacturing that allows a smart regulator to operate the device at lower core V<sub>CC</sub> while maintaining performance

- **Programmable Power Technology**—non-critical timing paths are identified by the Intel Quartus Prime software and the logic in these paths is biased for low power instead of high performance

- Low Static Power Options—devices are available with either standard static power or low static power while maintaining performance

Furthermore, Intel Arria 10 devices feature Intel's industry-leading low power transceivers and include a number of hard IP blocks that not only reduce logic resources but also deliver substantial power savings compared to soft implementations. In general, hard IP blocks consume up to 90% less power than the equivalent soft logic implementations.

## **Incremental Compilation**

The Intel Quartus Prime software incremental compilation feature reduces compilation time and helps preserve performance to ease timing closure. The incremental compilation feature enables the partial reconfiguration flow for Intel Arria 10 devices.

Incremental compilation supports top-down, bottom-up, and team-based design flows. This feature facilitates modular, hierarchical, and team-based design flows where different designers compile their respective design sections in parallel. Furthermore, different designers or IP providers can develop and optimize different blocks of the design independently. These blocks can then be imported into the top level project.

## **Document Revision History for Intel Arria 10 Device Overview**

| Document<br>Version | Changes                                                                                                  |

|---------------------|----------------------------------------------------------------------------------------------------------|

| 2018.04.09          | Updated the lowest $V_{CC}$ from 0.83 V to 0.82 V in the topic listing a summary of the device features. |

| Date         | Version    | Changes                                                                                                                                                                                          |

|--------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January 2018 | 2018.01.17 | • Updated the maximum data rate for HPS (Intel Arria 10 SX devices external memory interface DDR3 controller from 2,166 Mbps to 2,133 Mbps.                                                      |

|              |            | <ul> <li>Updated maximum frequency supported for half rate QDRII and QDRII<br/>+ SRAM to 633 MHz in <i>Memory Standards Supported by the Soft</i><br/><i>Memory Controller</i> table.</li> </ul> |

|              |            | Updated transceiver backplane capability to 12.5 Gbps.                                                                                                                                           |

|              |            | • Removed transceiver speed grade 5 in <i>Sample Ordering Core and Available Options for Intel Arria 10 GX Devices</i> figure.                                                                   |

|              | 1          | continued                                                                                                                                                                                        |

#### Intel<sup>®</sup> Arria<sup>®</sup> 10 Device Overview A10-OVERVIEW | 2018.04.09

| September 2017<br>July 2017<br>July 2017<br>May 2017<br>May 2017 | 2017.09.20<br>2017.07.13<br>2017.07.06<br>2017.05.08 | <ul> <li>Removed package code 40, low static power, SmartVID, industrial, and military operating temperature support from <i>Sample Ordering Core and Available Options for Intel Arria 10 GT Devices</i> figure.</li> <li>Updated short reach transceiver rate for Intel Arria 10 GT devices to 25.8 Gbps.</li> <li>Removed On-Die Instrumentation — EyeQ and Jitter Margin Tool support from <i>PMA Features of the Transceivers in Intel Arria 10 Devices</i> table.</li> <li>Updated the maximum speed of the DDR4 external memory interface from 1,333 MHz/2,666 Mbps to 1,200 MHz/2,400 Mbps.</li> <li>Corrected the automotive temperature range in the figure showing the available options for the Intel Arria 10 GX devices from "-40°C to 125°C".</li> <li>Added automotive temperature option to Intel Arria 10 GX device family.</li> <li>Corrected protocol names with "1588" to "IEEE 1588v2".</li> <li>Updated the vertical migration table to remove vertical migration between Intel Arria 10 GX and Intel Arria 10 SX device variants.</li> </ul> |

|------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 2017<br>July 2017<br>May 2017                               | 2017.07.13<br>2017.07.06                             | <ul> <li>1,333 MHz/2,666 Mbps to 1,200 MHz/2,400 Mbps.</li> <li>Corrected the automotive temperature range in the figure showing the available options for the Intel Arria 10 GX devices from "-40°C to 100°C" to "-40°C to 125°C".</li> <li>Added automotive temperature option to Intel Arria 10 GX device family.</li> <li>Corrected protocol names with "1588" to "IEEE 1588v2".</li> <li>Updated the vertical migration table to remove vertical migration</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| July 2017<br>May 2017                                            | 2017.07.06                                           | <ul> <li>available options for the Intel Arria 10 GX devices from "-40°C to 100°C"<br/>to "-40°C to 125°C".</li> <li>Added automotive temperature option to Intel Arria 10 GX device family.</li> <li>Corrected protocol names with "1588" to "IEEE 1588v2".</li> <li>Updated the vertical migration table to remove vertical migration</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| May 2017                                                         |                                                      | <ul> <li>Corrected protocol names with "1588" to "IEEE 1588v2".</li> <li>Updated the vertical migration table to remove vertical migration</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                  | 2017.05.08                                           | Updated the vertical migration table to remove vertical migration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| March 2017                                                       |                                                      | Removed all "Preliminary" marks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                  | 2017.03.15                                           | <ul> <li>Removed the topic about migration from Intel Arria 10 to Intel Stratix<br/>10 devices.</li> <li>Rebranded as Intel.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| October 2016                                                     | 2016.10.31                                           | <ul> <li>Removed package F36 from Intel Arria 10 GX devices.</li> <li>Updated Intel Arria 10 GT sample ordering code and maximum GX transceiver count. Intel Arria 10 GT devices are available only in the SF45 package option with a maximum of 72 transceivers.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| May 2016                                                         | 2016.05.02                                           | <ul> <li>Updated the FPGA Configuration and HPS Booting topic.</li> <li>Remove V<sub>CC</sub> PowerManager from the Summary of Features, Power Management and Arria 10 Device Variants and packages topics. This feature is no longer supported in Arria 10 devices.</li> <li>Removed LPDDR3 from the Memory Standards Supported by the HPS Hard Memory Controller table in the Memory Standards Supported by Intel Arria 10 Devices topic. This standard is only supported by the FPGA.</li> <li>Removed transceiver speed grade 5 from the Device Variants and Packages topic for Arria 10 GX and SX devices.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| February 2016                                                    | 2016.02.11                                           | <ul> <li>Changed the maximum Arria 10 GT datarate to 25.8 Gbps and the minimum datarate to 1 Gbps globally.</li> <li>Revised the state for Core clock networks in the Summary of Features topic.</li> <li>Changed the transceiver parameters in the "Summary of Features for Arria 10 Devices" table.</li> <li>Changed the transceiver parameters in the "Maximum Resource Counts for Arria 10 GT Devices" table.</li> <li>Changed the package availability for GT devices in the "Package Plan for Arria 10 GT Devices" table.</li> <li>Changed the package configurations for GT devices in the "Migration Capability Across Arria 10 Product Lines" figure.</li> <li>Changed the transceiver descriptions in the "Device Variants for the Arria 10 Device Family" table.</li> <li>Changed the "Sample Ordering Code and Available Options for Arria 10 GT Devices" figure.</li> <li>Changed the datarates for GT devices in the "PMA Features" section.</li> <li>Changed the datarates for GT devices in the "PCS Features" section.</li> </ul>                   |

#### Intel<sup>®</sup> Arria<sup>®</sup> 10 Device Overview A10-OVERVIEW | 2018.04.09

| Date          | Version    | Changes                                                                                                                                                                                                                                                                  |

|---------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| August 2014   | 2014.08.18 | Updated Memory (Kb) M20K maximum resources for Arria 10 GX 660 devices from 42,660 to 42,620.                                                                                                                                                                            |

|               |            | <ul> <li>Added GPIO columns consisting of LVDS I/O Bank and 3V I/O Bank in<br/>the Package Plan table.</li> </ul>                                                                                                                                                        |

|               |            | • Added how to use memory interface clock frequency higher than 533 MHz in the I/O vertical migration.                                                                                                                                                                   |

|               |            | <ul> <li>Added information to clarify that RLDRAM3 support uses hard PHY with<br/>soft memory controller.</li> </ul>                                                                                                                                                     |

|               |            | Added variable precision DSP blocks support for floating-point arithmetic.                                                                                                                                                                                               |

| June 2014     | 2014.06.19 | Updated number of dedicated I/Os in the HPS block to 17.                                                                                                                                                                                                                 |

| February 2014 | 2014.02.21 | Updated transceiver speed grade options for GT devices in Figure 2.                                                                                                                                                                                                      |

| February 2014 | 2014.02.06 | Updated data rate for Arria 10 GT devices from 28.1 Gbps to 28.3 Gbps.                                                                                                                                                                                                   |

| December 2013 | 2013.12.10 | <ul> <li>Updated the HPS memory standards support from LPDDR2 to LPDDR3.</li> <li>Updated HPS block diagram to include dedicated HPS I/O and FPGA<br/>Configuration blocks as well as repositioned SD/SDIO/MMC, DMA, SPI<br/>and NAND Flash with ECC blocks .</li> </ul> |

| December 2013 | 2013.12.02 | Initial release.                                                                                                                                                                                                                                                         |