# E·XFL

### Motorola - MCF5249LCAG120 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                             |

|----------------------------|-------------------------------------------------------------|

| Product Status             | Obsolete                                                    |

| Core Processor             | Coldfire V2                                                 |

| Core Size                  | 32-Bit Single-Core                                          |

| Speed                      | 120MHz                                                      |

| Connectivity               | I <sup>2</sup> C, IDE, Memory Card, SPI, UART/USART         |

| Peripherals                | DMA, I <sup>2</sup> S, POR, Serial Audio, WDT               |

| Number of I/O              | 34                                                          |

| Program Memory Size        | -                                                           |

| Program Memory Type        | ROMIess                                                     |

| EEPROM Size                | -                                                           |

| RAM Size                   | 96K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                   |

| Data Converters            | A/D 4x12b                                                   |

| Oscillator Type            | External                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 144-LQFP                                                    |

| Supplier Device Package    | 144-LQFP (20x20)                                            |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcf5249lcag120 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Paragraph Number

Page Number

| Clock and Reset Signals | 8-3                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |                                                                                                                                                                                                                                                                                                                                                                                            |

| System Bus Clock Output | 8-4                                                                                                                                                                                                                                                                                                                                                                                        |

| Bus Characteristics     | 8-4                                                                                                                                                                                                                                                                                                                                                                                        |

| Data Transfer Operation | 8-5                                                                                                                                                                                                                                                                                                                                                                                        |

| Bus Cycle Execution     | 8-6                                                                                                                                                                                                                                                                                                                                                                                        |

| Read Cycle              | 8-7                                                                                                                                                                                                                                                                                                                                                                                        |

| Write Cycle             | 8-8                                                                                                                                                                                                                                                                                                                                                                                        |

|                         |                                                                                                                                                                                                                                                                                                                                                                                            |

| Burst Cycles            | 8-11                                                                                                                                                                                                                                                                                                                                                                                       |

| Line Transfers          | 8-11                                                                                                                                                                                                                                                                                                                                                                                       |

| Line Read Bus Cycles    | 8-11                                                                                                                                                                                                                                                                                                                                                                                       |

| Line Write Bus Cycles   | 8-12                                                                                                                                                                                                                                                                                                                                                                                       |

| Misaligned Operands     | 8-14                                                                                                                                                                                                                                                                                                                                                                                       |

| Reset Operation         | 8-15                                                                                                                                                                                                                                                                                                                                                                                       |

|                         |                                                                                                                                                                                                                                                                                                                                                                                            |

|                         | Clock and Reset Signals<br>Reset In<br>System Bus Clock Output<br>Bus Characteristics<br>Data Transfer Operation<br>Bus Cycle Execution<br>Read Cycle<br>Write Cycle<br>Back-to-Back Bus Cycles<br>Burst Cycles<br>Line Transfers<br>Line Read Bus Cycles<br>Line Write Bus Cycles<br>Stine Write Bus Cycles<br>Stine Write Bus Cycles<br>Stine Write Bus Cycles<br>Stine Write Bus Cycles |

## SECTION 9 SYSTEM INTEGRATION MODULE

| 9.1     | SIM Introduction                            | 9-1  |

|---------|---------------------------------------------|------|

| 9.1.1   | SIM Features                                | 9-1  |

| 9.2     | Programming Model                           | 9-1  |

| 9.2.1   | SIM Register Memory Map                     | 9-1  |

| 9.3     | SIM Programming and Configuration           |      |

| 9.3.1   | Module Base Address Registers               |      |

| 9.3.2   | Device ID                                   |      |

| 9.3.3   | Interrupt Controller                        |      |

| 9.4     | Interrupt Interface                         |      |

| 9.4.1   | Primary controller Interrupt Registers      |      |

| 9.4.1.1 | Interrupt Mask Register                     |      |

| 9.4.1.2 | Interrupt Pending Register                  |      |

| 9.4.2   | Secondary Interrupt Controller Registers    | 9-11 |

| 9.4.2.1 | Interrupt Level Selection                   |      |

| 9.4.2.2 | Interrupt Vector Generation                 |      |

| 9.4.2.3 | Spurious Vector Register                    |      |

| 9.4.2.4 | Secondary Interrupt Sources                 |      |

| 9.4.3   | Software interrupts                         |      |

| 9.5     | System Protection And Reset Status          |      |

| 9.5.1   | Reset Status Register                       |      |

| 9.5.2   | Software Watchdog Timer                     |      |

| 9.5.2.1 | System Protection Control Register          |      |

| 9.5.2.2 | Software Watchdog Interrupt Vector Register |      |

| 9.5.2.3 | Software Watchdog Service Register          |      |

| 9.6     | CPU STOP Instruction                        |      |

| 9.7     | MCF5249 Bus Arbitration Control             |      |

| 9.7.1   | Default Bus Master Park Register            |      |

| 9.7.1.1 | Internal Arbitration Operation              |      |

| 9.7.1.2 | PARK Register Bit Configuration             |      |

| 9.8     | General Purpose I/Os                        |      |

| 9.8.1   | General Purpose Inputs                      |      |

| 9.8.1.1 | General Purpose Input Interrupts            |      |

| 9.8.2   | General Purpose Outputs                     |      |

|         |                                             |      |

# LIST OF FIGURES

### Page Number

|             |                                                            | Number |

|-------------|------------------------------------------------------------|--------|

| Figure 1-1  | MCF5249 Block Diagram                                      | 1-2    |

| Figure 3-1  | V2 ColdFire Processor Core Pipelines                       |        |

| Figure 3-2  | User Programming Model                                     | 2-3    |

| Figure 3-3  | Supervisor Programming Model                               | 2-5    |

| Figure 3-4  | Vector Base Register (VBR)                                 |        |

| Figure 3-5  | Exception Stack Frame Form                                 |        |

| Figure 4-1  | Phase-Locked Loop Module Block Diagram                     |        |

| Figure 5-1  | Instruction Cache Block Diagram                            |        |

| Figure 7-1  | Synchronous DRAM Controller Block Diagram                  |        |

| Figure 7-2  | MCF5249 SDRAM Interface                                    |        |

| Figure 7-3  | DRAM Control Register (DCR) (Synchronous Mode)             | 7-5    |

| Figure 7-4  | DACR0 and DACR1 (Synchronous Mode)                         |        |

| Figure 7-5  | DRAM Controller Mask Registers (DMR0 and DMR1)             |        |

| Figure 7-6  | Burst Read SDRAM Access                                    |        |

| Figure 7-7  | Burst Write SDRAM Access                                   |        |

| Figure 7-8  | Synchronous, Continuous Page-Mode Access—Consecutive Reads |        |

| Figure 7-9  | Synchronous, Continuous Page-Mode Access—Read after Write  |        |

| Figure 7-10 | Auto-Refresh Operation                                     |        |

| Figure 7-11 | Self-Refresh Operation                                     |        |

| Figure 7-12 | Mode Register Set (mrs) Command                            |        |

| Figure 7-13 | Initialization Values for DCR                              |        |

| Figure 7-14 | SDRAM Configuration                                        |        |

| Figure 7-15 | DACR Register Configuration                                |        |

| Figure 7-16 | DMR0 Register                                              |        |

| Figure 7-17 | Mode Register Mapping to MCF5249 A[31:0]                   |        |

| Figure 8-1  | Connections for External Memory Port Sizes                 |        |

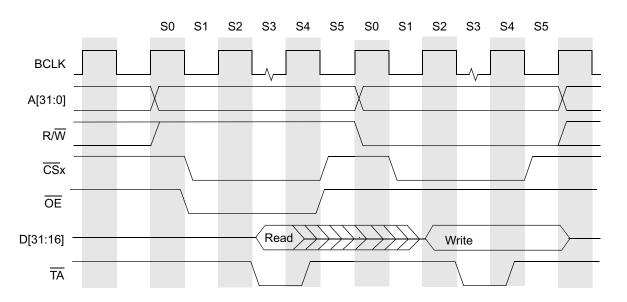

| Figure 8-2  | Signal Relationship to BCLK for Non-DRAM Access            |        |

| Figure 8-3  | Read Cycle Flowchart                                       |        |

| Figure 8-4  | Basic Read Bus Cycle                                       |        |

| Figure 8-5  | Write Cycle Flowchart                                      |        |

| Figure 8-6  | Basic Write Bus Cycle                                      |        |

| Figure 8-7  | Back-to-Back Bus Cycles                                    |        |

| Figure 8-8  | Line Read Burst (one wait cycle)                           |        |

| Figure 8-9  | Line Read Burst (no wait cycles)                           |        |

| Figure 8-10 | Line Write Burst (no wait cycles)                          |        |

| Figure 8-11 | Line Read Burst-Inhibited                                  |        |

| Figure 8-12 | Line Write Burst with One Wait State                       |        |

| Figure 8-13 | Line Write Burst-Inhibited                                 |        |

| Figure 8-14 | Misaligned Longword Transfer                               |        |

| Figure 8-15 | Misaligned Word Transfer                                   |        |

| Figure 8-16 | Master Reset Timing                                        |        |

|             | Software Watchdog Reset Timing                             |        |

| Figure 8-17 | MCF5249 Unterminated Access Recovery                       |        |

| Figure 9-1  |                                                            |        |

| Figure 9-2  | General-Purpose Pin Logic for Pin ddata3/gpio34            |        |

| Figure 11-1 | Timer Block Diagram Module Operation                       |        |

| Figure 12-1 | ADC with On-chip and External Parts                        |        |

| Figure 13-1 | Bus Setup with IDE and SmartMedia Interface                |        |

| Figure 13-2 | Buffer Enables (BUFENB1 and BUFENB2)                       |        |

| Figure 13-3 | DIOR and SRE Timing Diagram                                |        |

| Figure 13-4 | Non-IORDY Controlled IDE/SmartMedia TA Timing              |        |

| Figure 13-5 | CS2 (DIOR, DIOW) and CS3 (SRE, SWE) Cycle Timing           |        |

The timer unit has an 8-bit prescaler that allows programming of the clock input frequency, which is derived from the system clock. In addition to the ÷1 and ÷16 clock derived from the bus clock (CPU clock / 2), the programmable timer-output pins either generate an active-low pulse or toggle the outputs.

## 1.6.16 IDE AND SMARTMEDIA INTERFACES

The MCF5249 system bus allows connection of an IDE hard disk drive and SmartMedia flash card with a minimum of external hardware. The external hardware consists of bus buffers for address and data and are intended to reduce the load on the bus and prevent SDRAM and Flash accesses to propagate to the IDE bus. The control signals for the buffers are generated in the MCF5249.

# 1.6.17 ANALOG/DIGITAL CONVERTER (ADC)

The four channel ADC is based on the Sigma-Delta concept with 12-bit resolution. The digital portion of the ADC is provided internally. The analog voltage comparator must be provided externally as well as an external integrator circuit (resistor/capacitor) which is driven by the ADC output. A software interrupt is provided when the ADC measurement cycle is complete.

# 1.6.18 FLASH MEMORY CARD INTERFACE

The interface is Sony MemoryStick and SecureDigital compatible. However, there is no hardware support for MagicGate™.

# 1.6.19 I<sup>2</sup>C MODULE

The two-wire  $I^2C$  bus interface, which is compliant with the Philips  $I^2C$  bus standard, is a bidirectional serial bus that exchanges data between devices. The  $I^2C$  bus minimizes the interconnection between devices in the end system and is best suited for applications that need occasional bursts of rapid communication over short distances among several devices. Bus capacitance and the number of unique addresses limit the maximum communication length and the number of devices that can be connected.

# 1.6.20 CHIP-SELECTS

There are four programmable chip selects on the MCF5249:

- Two programmable chip-select outputs (CS0 and CS1) provide signals that enable glueless connection to external memory and peripheral circuits. The base address, access permissions, and automatic wait-state insertion are programmable with configuration registers. These signals also interface to 16-bit ports.

- Two dedicated chip selects (CS2 and CS3) are used for the IDE and/or SmartMedia interface

CS0 is active after reset to provide boot-up from external FLASH/ROM.

# 1.6.21 GPIO INTERFACE

A total of 44 General Purpose inputs and 46 General Purpose outputs are available. These are multiplexed with various other signals. Eight of the GPIO inputs have edge sensitive interrupt capability.

# 1.6.22 INTERRUPT CONTROLLER

The MCF5249 has a primary and a secondary interrupt controller. These interrupt controllers handle interrupts from all internal interrupt sources. In addition, there are 8 GPIOs where external interrupts can

# 4.3 AUDIO CLOCK GENERATION

The audio clocks and output DAC clocks are divided directly from the crystal. Clock settings depend on CRSEL, CLSEL, and AUDIOSEL bits, as explained in Table 4-4. As the table shows, the AUDIOCLK is completely derived from the AUDIOSEL bit, and this clock is independent of the other select bits. For the DAC clocks (MCLK2 and MCLK1) the relationship between CRSEL and CLSEL is defined in Table 4-4.

| PLLCR CLSEL<br>(BITS30-28) | PLLCR CRSEL<br>(BIT 23) | PLLCR CONFIG<br>AUDIOSEL<br>(BIT 22) | AUDIOCLK | MCLK2   | MCLK1   |

|----------------------------|-------------------------|--------------------------------------|----------|---------|---------|

| 000                        | 1                       | 1                                    | FXTAL    | FXTAL   | FXTAL/2 |

| 001                        | 1                       | 1                                    | FXTAL    | FXTAL   | FXTAL   |

| 010                        | 1                       | 1                                    | FXTAL    | FXTAL/2 | FXTAL/2 |

| 011                        | 1                       | 1                                    | FXTAL    | FXTAL/2 | FXTAL   |

| 100                        | 1                       | 1                                    | FXTAL    | FXTAL   | FXTAL/2 |

| 101                        | 1                       | 1                                    | FXTAL    | FXTAL   | FXTAL   |

| 110                        | 1                       | 1                                    | FXTAL    | FXTAL/2 | FXTAL/2 |

| 111                        | 1                       | 1                                    | FXTAL    | FXTAL/2 | FXTAL   |

| 000                        | 1                       | 0                                    | FXTAL/2  | FXTAL   | FXTAL/2 |

| 001                        | 1                       | 0                                    | FXTAL/2  | FXTAL   | FXTAL   |

| 010                        | 1                       | 0                                    | FXTAL/2  | FXTAL/2 | FXTAL/2 |

| 011                        | 1                       | 0                                    | FXTAL/2  | FXTAL/2 | FXTAL   |

| 100                        | 1                       | 0                                    | FXTAL/2  | FXTAL   | FXTAL/2 |

| 101                        | 1                       | 0                                    | FXTAL/2  | FXTAL   | FXTAL   |

| 110                        | 1                       | 0                                    | FXTAL/2  | FXTAL/2 | FXTAL/2 |

| 111                        | 1                       | 0                                    | FXTAL/2  | FXTAL/2 | FXTAL   |

**Note:** MCLK1 and MCLK2 will output a clock signal just after reset and before they can be configured as GPIO if so desired. The frequency of the clock will be the same as CRIN prior to initialization of the PLL.

The multiplexer that switches AUDIOCLK between Fxtal and Fxtal/2 is glitch free. No reset is needed after switching audio clock. For the MCLK1 and MCLK2 clocks, the divide by 2 is 50% duty cycle, divide by 3 is 33% duty cycle, and divide by 4 is 25% duty cycle.

| MBAR<br>OFFSET | [31:24]                                                            | [23:16] | [15:8] | [7:0] |

|----------------|--------------------------------------------------------------------|---------|--------|-------|

| 0x100          | DRAM control register (DCR) [See Section 7.2.1]                    |         | Rese   | erved |

| 0x104          | Reserved                                                           |         |        |       |

| 0x108          | DRAM address and control register 0 (DACR0) [See Section 7.3.2.2.] |         |        |       |

| 0x10C          | DRAM mask register block 0 (DMR0) [See Section 7.3.2.3.]           |         |        |       |

| 0x110          | DRAM address and control register 1 (DACR1) [See Section 7.3.2.2.] |         |        |       |

| 0x114          | DRAM mask register block 1 (DMR1) [See Section 7.3.2.3.]           |         |        |       |

## Table 7-1 DRAM Controller Registers

# 7.3 SYNCHRONOUS OPERATION

By running synchronously with the system clock, SDRAM can (after an initial latency period) be accessed on every clock; 5-1-1-1 is a typical MCF5249 burst rate to SDRAM.

**Note:**Because the MCF5249 cannot have more than one page open at a time, it does not support interleaving.

Table 7-2 lists common SDRAM commands.

| COMMAND | DEFINITION                                                                                              |

|---------|---------------------------------------------------------------------------------------------------------|

| ACTV    | Activate. Executed before READ or WRITE executes; SDRAM registers and decodes row address.              |

| MRS     | Mode register set.                                                                                      |

| NOP     | No-op. Does not affect SDRAM state machine; DRAM controller control signals negated; SDRAM_CS asserted. |

| PALL    | Precharge all. Precharges all internal banks of an SDRAM component; executed before new page is opened. |

| READ    | Read access. SDRAM registers column address and decodes that a read access is occurring.                |

| REF     | Refresh. Refreshes internal bank rows of an SDRAM component.                                            |

| SELF    | Self refresh. Refreshes internal bank rows of an SDRAM component when it is in low-power mode.          |

| SELFX   | Exit self refresh. This command is sent to the DRAM controller when DCR[IS] is cleared.                 |

| WRITE   | Write access. SDRAM registers column address and decodes that a write access is occurring.              |

### Table 7-2 SDRAM Commands

Commands are issued to memory using specific encoding on address and control pins. Soon after system reset, a command must be sent to the SDRAM mode register to configure SDRAM operating parameters.

| BITS | NAME | SETTING | DESCRIPTION                                 |  |

|------|------|---------|---------------------------------------------|--|

| 3    | IP   | 0       | Indicates precharge has not been initiated. |  |

| 2    | PM   | 1       | Indicates continuous page mode              |  |

| 1–0  | _    |         | Reserved. Don't care.                       |  |

Table 7-18 DACR Initialization Values (Continued)

## 7.4.4 DMR INITIALIZATION

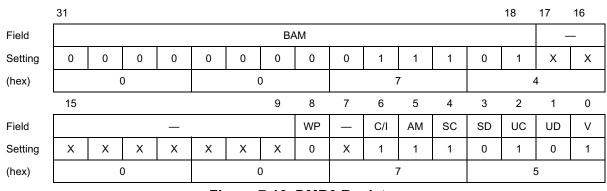

In this example, again, only the second 512-Kbyte block of each 1-Mbyte space is accessed in each bank. In addition the SDRAM component is mapped only to readable and writable supervisor and user data. The DMRs have the following configuration.

### Figure 7-16 DMR0 Register

With this configuration, the DMR0 = 0x0074\_0075, as described in Table 7-19.

| BITS  | NAME | SETTING | DESCRIPTION                                                                                                                                                                                                                                                 |

|-------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–16 | BAM  |         | With bits 17 and 16 as don't cares, BAM = 0x0074, which leaves bank select bits<br>and upper 512K select bits unmasked.<br>Bits 22 and 21 are set because they are used as bank selects; bit 20 is set<br>because it controls the 1-Mbyte boundary address. |

| 15–9  | _    |         | Reserved. Don't care.                                                                                                                                                                                                                                       |

| 8     | WP   | 0       | Allow reads and writes                                                                                                                                                                                                                                      |

| 7     |      |         | Reserved                                                                                                                                                                                                                                                    |

| 6     | C/I  | 1       | Disable CPU space access                                                                                                                                                                                                                                    |

| 5     | AM   | 1       | Disable alternate master access                                                                                                                                                                                                                             |

| 4     | SC   | 1       | Disable supervisor code accesses                                                                                                                                                                                                                            |

| 3     | SD   | 0       | Enable supervisor data accesses                                                                                                                                                                                                                             |

| 2     | UC   | 1       | Disable user code accesses                                                                                                                                                                                                                                  |

| 1     | UD   | 0       | Enable user data accesses                                                                                                                                                                                                                                   |

| 0     | V    | 1       | Enable accesses.                                                                                                                                                                                                                                            |

### Table 7-19 DMR0 Initialization Values

| STATE<br>NAME | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATE 3       | During state 3 (S3), the MCF5249 waits for a cycle termination signal ( $\overline{TA}$ ). If $\overline{TA}$ is not asserted before the rising edge of BCLK at the end of the first clock cycle, the MCF5249 inserts wait states (full clock cycles) until $\overline{TA}$ is asserted. TA is generated internally by the chip select module. If internal $\overline{TA}$ is requested (auto-acknowledge enabled in the chip select control register, CSCR) then $\overline{TA}$ is generated internally by the chip select module. |

| STATE 4       | During state 4, $\overline{TA}$ should be negated by the external device or if auto-acknowledge is enabled, negated internally by the chip select module.                                                                                                                                                                                                                                                                                                                                                                            |

| STATE 5       | $\overline{\text{CS}}$ is negated on the falling edge of BCLK in state 5 (S5). The MCF5249 stops driving the address lines and R/W, terminating the write cycle. The data bus returns to high impedance on the rising edge of BCLK.<br>The rising edge of BCLK may be the start of state 0 for the next access cycle.                                                                                                                                                                                                                |

# Table 8-6 Write Cycle States (Continued)

# 8.5.4 BACK-TO-BACK BUS CYCLES

The MCF5249 can accommodate back-to-back bus cycles. The processor runs back-to-back bus cycles whenever possible. For example, when a longword read is started on a word-size bus, and burst read enable is disabled into the relevant chip select register, the processor will perform two word reads back to back. Figure 7-9 shows a read, followed by a write that occurs back to back.

A basic read and a write cycle are used to illustrate the back-to-back cycle. There is no restriction as to the type of operation to be placed back to back. The initiation of a back-to-back cycle is not user definable.

Figure 8-7 Back-to-Back Bus Cycles

MOTOROLA

| ADDRESS     | NAME  | SIZE<br>(BYTES) | DESCRIPTION                    |

|-------------|-------|-----------------|--------------------------------|

| CPU + \$C0F | MBAR  | 4               | Module base address register   |

| CPU + \$C0E | MBAR2 | 4               | Module base address register 2 |

# Table 9-1 MBAR Register Addresses

### Table 9-2 SIM Memory Map

| ADDRESS       | DESCRIPTION                   | 0        | 1          | 2     | 3     |

|---------------|-------------------------------|----------|------------|-------|-------|

| MBAR + \$000  | SYSTEM CONTROL REG            | RSR      | SYPCR      | SWIVR | SWSR  |

| MBAR + \$004  |                               | Reserved |            |       |       |

| MBAR + \$008  |                               | Reserved |            |       |       |

| MBAR + \$00C  | BUS MASTER CONTROL REG        | MPARK    | Reserved   |       |       |

| MBAR + \$010  | —                             | Reserved |            |       |       |

| MBAR + \$014  | —                             |          |            |       |       |

| MBAR + \$018  | —                             |          |            |       |       |

| MBAR + \$01C  | —                             |          |            |       |       |

| MBAR + \$020  | —                             |          |            |       |       |

| MBAR + \$024  | —                             |          |            |       |       |

| MBAR + \$028  | —                             |          |            |       |       |

| MBAR + \$02C  | —                             |          |            |       |       |

| MBAR + \$030  | —                             |          |            |       |       |

| MBAR + \$034  | —                             |          |            |       |       |

| MBAR + \$038  | —                             |          |            |       |       |

| MBAR + \$03C  | —                             |          |            |       |       |

| MBAR + \$040  | Primary interrupt Pending Reg | IPR      |            |       |       |

| MBAR + \$044  | Primary Interrupt Mask Reg    | IMR      |            |       |       |

| MBAR + \$04C  | Primary Interrupt Control Reg | ICR0     | ICR1       | ICR2  | ICR3  |

| MBAR + \$050  | Primary Interrupt Control Reg | ICR4     | ICR5       | ICR6  | ICR7  |

| MBAR + \$054  | Primary Interrupt Control Reg | ICR8     | ICR9       | ICR10 | ICR11 |

| MBAR2 + \$000 | gpio 0-31 input reg           | GPIO-REA | D (READ ON | NLY)  | ·     |

| MBAR2 + \$004 | gpio 0-31 output reg          | GPIO-OUT |            |       |       |

| MBAR2 + \$008 | gpio 0-31 output enable reg   | GPIO-ENA | BLE        |       |       |

| MBAR2 + \$00C | gpio 0-31 function select     | GPIO-FUN | CTION      |       |       |

| MBAR + \$0AC  | Device ID Reg                 |          |            |       |       |

| MBAR2 + \$0B0 | gpio 32-63 input reg          | GPIO1-RE | AD (READ C | NLY)  |       |

| MBAR2 + \$0B4 | gpio 32-63 output reg         | GPIO1-OU | Т          |       |       |

9-2

|          | Table 5-4 Module Base Address Bit Descriptions (continued)                         |  |  |  |  |  |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| BIT NAME | DESCRIPTION                                                                        |  |  |  |  |  |  |  |  |  |  |

| V        | This bit defines when the base address is valid:                                   |  |  |  |  |  |  |  |  |  |  |

|          | 0 = MBAR address space not visible by CPU<br>1 = MBAR address space visible by CPU |  |  |  |  |  |  |  |  |  |  |

## Table 9-4 Module Base Address Bit Descriptions (Continued)

The following example shows how to set the MBAR to location \$1000000 using the D0 register. A "1" in the least significant bit validates the MBAR location. This example assumes that all accesses are valid:

move.1 #\$10000001,DO movec DO,MBAR

| Table 9-5 | Second Module | <b>Base Address</b> | Register | (MBAR2) |

|-----------|---------------|---------------------|----------|---------|

|-----------|---------------|---------------------|----------|---------|

| BITS  | 31   | 30   | 29 | 28 | 27 | 26 | 25 | 24 | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

|-------|------|------|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| FIELD | BA31 | BA30 | -  | -  | -  | -  | -  | -  | -   | -   | -   | -   | -   | -   | -   | -   |

| RESET | 0    | 0    | -  | -  | -  | -  | -  | -  | -   | -   | -   | -   | -   | -   | -   | -   |

| R/W   | R/W  | R/W  |    |    |    |    |    |    |     |     |     |     |     |     |     |     |

|       |      |      |    |    |    |    |    |    |     |     |     |     |     |     |     |     |

| BITS  | 15   | 14   | 13 | 12 | 11 | 10 | 9  | 8  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| FIELD |      |      |    |    |    |    |    |    | LS7 | LS6 | LS5 | LS4 | LS3 | LS2 | LS1 | V   |

| RESET | -    | -    | -  | -  | -  | -  | -  | -  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   |      |      |    |    |    |    |    |    | R/W |

### Table 9-6 Second Module Base Address Bit Descriptions

| BIT NAME  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                          |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BA[31:30] | The Base Address field defines the base address for a 1024-MByte address range. If V-bit in MBAR2 is set, address range Base Address to BaseAddress + \$3FFF FFFF are mapped to MBAR2 space, and cannot be used for MBAR, SDRAM or Chip Select.                                                                                                                      |

| LS[7:1]   | If interrupts both "primary" and the "secondary" interrupt controller have interrupt level 7 pending, bit LS7 determines which interrupt controller gets priority. If this bit is cleared, the primary interrupt controller gets priority. If this bit is set, the secondary interrupt controller gets priority. There are 7 LSn bits, one for each interrupt level. |

| V         | The Valid bit defines if the CPU can access the MBAR2 mapped peripherals<br>0 = MBAR2 address space not visible by CPU.<br>1 = MBAR2 address space visible by CPU                                                                                                                                                                                                    |

## 9.3.2 DEVICE ID

The DeviceID register is a read only register that allows the software to determine which hardware it is running on. The register contains the part number in the upper 24 bits, the mask revision number in the lower 8 bits, and is read as 0x005448rr, where *rr* is the revision number.

This register allows developers the flexibility to write code to run on more than one device. The revision number allows developers to distinguish between different mask versions that may have minor changes or

Semiconductor, Inc

reescale

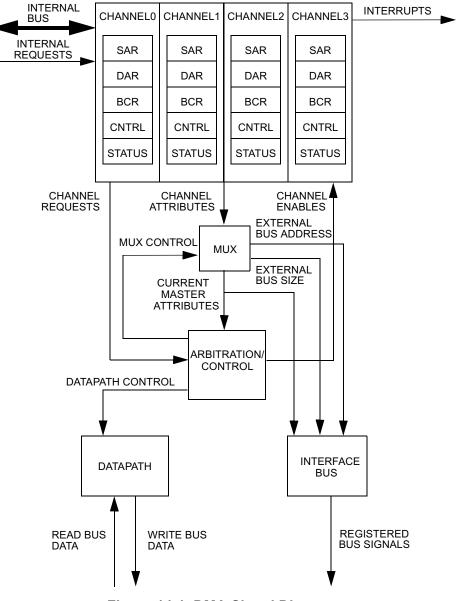

# Section 14 DMA Controller Module

The direct memory access (DMA) controller module quickly and efficiently moves blocks of data with minimal processor overhead. The DMA module, shown in Figure 14-1, provides four channels that allow byte, word, or longword operand transfers. These transfers should be dual address to on-chip devices; such as the UART, SDRAM controller, and audio module.

Figure 14-1 DMA Signal Diagram

DMA Controller Module

DMA ADDRESS [31:24] [23:16] [15:8] [7:0] CHANNEL MBAR2+\$188 DMAROUTE - Request source control Channel 0 MBAR+\$300 Source Address Register 0 MBAR+\$304 **Destination Address Register 0** DMA Control Register 0 MBAR+\$308 MBAR+\$30C Byte Count Register 0 Reserved MBAR+\$310 Status Register 0 Reserved Interrupt Vector MBAR+\$314 Reserved Register 0

### Table 14-2 Memory Map DMA Channel 0

### Table 14-3 Memory Map DMA Channel 1

| DMA<br>CHANNEL | ADDRESS    | [31:24]                        | [23:16]                   | [15:8]           | [7:0]    |  |  |  |  |  |  |

|----------------|------------|--------------------------------|---------------------------|------------------|----------|--|--|--|--|--|--|

| Channel 1      | MBAR+\$340 |                                | Source Address Register 1 |                  |          |  |  |  |  |  |  |

|                | MBAR+\$344 |                                | Destination Add           | Iress Register 1 |          |  |  |  |  |  |  |

|                | MBAR+\$348 |                                | DMA Contro                | ol Register 1    |          |  |  |  |  |  |  |

|                | MBAR+\$34C | Byte Count                     | t Register 1              | Rese             | erved    |  |  |  |  |  |  |

|                | MBAR+\$350 | Status Register 1              |                           | Reserved         | Reserved |  |  |  |  |  |  |

|                | MBAR+\$354 | Interrupt Vector<br>Register 1 |                           | Reserved         |          |  |  |  |  |  |  |

### Table 14-4 Memory Map DMA Channel 2

|                |            |                                | , i                       |              |       |  |  |  |  |  |

|----------------|------------|--------------------------------|---------------------------|--------------|-------|--|--|--|--|--|

| DMA<br>CHANNEL | ADDRESS    | [31:24]                        | [23:16]                   | [15:8]       | [7:0] |  |  |  |  |  |

| Channel 2      | MBAR+\$380 | Source Address Register 2      |                           |              |       |  |  |  |  |  |

|                | MBAR+\$384 | Destination Address Register 2 |                           |              |       |  |  |  |  |  |

|                | MBAR+\$388 |                                | DMA Contro                | l Register 2 |       |  |  |  |  |  |

|                | MBAR+\$38C | Byte Count                     | t Register 2              | Rese         | erved |  |  |  |  |  |

|                | MBAR+\$390 | Status Register 2              |                           | Reserved     |       |  |  |  |  |  |

|                | MBAR+\$394 | Interrupt Vector               | Interrupt Vector Reserved |              |       |  |  |  |  |  |

|                |            | Register 2                     |                           |              |       |  |  |  |  |  |

### Table 14-5 Memory Map DMA Channel 3

| ADDRESS    | [31:24]                                                                          | [23:16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | [15:8]                                                                                                                                                                                                                                  | [7:0]                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| MBAR+\$3C0 |                                                                                  | Source Address Register 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| MBAR+\$3C4 |                                                                                  | Destination Add                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Iress Register 3                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| MBAR+\$3C8 |                                                                                  | DMA Contro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | l Register 3                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| MBAR+\$3CC | Byte Count                                                                       | Register 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Rese                                                                                                                                                                                                                                    | erved                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| MBAR+\$3D0 | Status Register 3                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Reserved                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| MBAR+\$3D4 | D4 Interrupt Vector Reserved<br>Register 3                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

|            | MBAR+\$3C0<br>MBAR+\$3C4<br>MBAR+\$3C8<br>MBAR+\$3CC<br>MBAR+\$3D0<br>MBAR+\$3D4 | MBAR+\$3C0<br>MBAR+\$3C4<br>MBAR+\$3C8<br>MBAR+\$3CC<br>MBAR+\$3D0<br>MBAR+\$3D0<br>MBAR+\$3D4<br>MBAR+\$3D4<br>MBAR+\$3D4<br>MBAR+\$3D4<br>MBAR+\$3D4<br>MBAR+\$3D4<br>MBAR+\$3C4<br>MBAR+\$3C4<br>MBAR+\$3C4<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$3C6<br>MBAR+\$ | MBAR+\$3C0     Source Addres       MBAR+\$3C4     Destination Add       MBAR+\$3C8     DMA Contro       MBAR+\$3C0     Byte Count Register 3       MBAR+\$3D0     Status Register 3       MBAR+\$3D4     Interrupt Vector<br>Register 3 | MBAR+\$3C0     Source Address Register 3       MBAR+\$3C4     Destination Address Register 3       MBAR+\$3C8     DMA Control Register 3       MBAR+\$3C0     Byte Count Register 3       MBAR+\$3D0     Status Register 3       MBAR+\$3D4     Interrupt Vector |  |  |  |  |  |  |

**Note:** Table 14-2 is for BCR24BIT = 0. Table 14-6 shows the difference in the memory map when BCR24BIT = 1.

### Operation

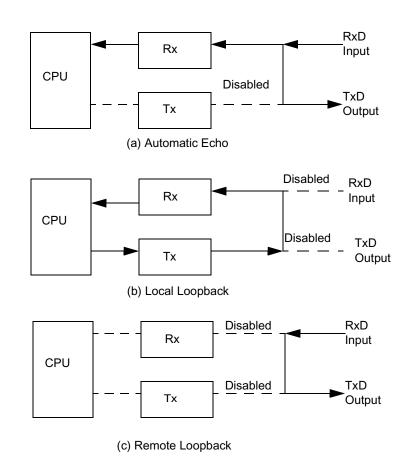

#### 15.3.3.3 **Remote Loopback Mode**

In this mode, the channel automatically transmits received data on the TxD output on a bit-by-bit basis. The local CPU-to-transmitter link is disabled. This mode is useful for testing remote channel receiver and transmitter operation. While in this mode, the receiver clocks the transmitter.

Note: Because the receiver is not active, the CPU cannot read received data. All status conditions are inactive. Received parity is not checked and is not recalculated for transmission. Stop bits are transmitted as received. A received break is echoed as received until the next valid start bit is detected.

#### 15.3.4 MULTIDROP MODE