#### Silicon Labs - C8051F206 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 25MHz                                                       |

| Connectivity               | SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                            |

| Number of I/O              | 32                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1.25K x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | A/D 32x12b                                                  |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 48-TQFP                                                     |

| Supplier Device Package    | 48-TQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f206 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## NOTES:

| SFR Definition 14.4. P0: Port0 Register                          |

|------------------------------------------------------------------|

| SFR Definition 14.5. PRT0CF: Port0 Configuration Register        |

| SFR Definition 14.6. P0MODE: Port0 Digital/Analog Input Mode     |

| SFR Definition 14.7. P1: Port1 Register                          |

| SFR Definition 14.8. PRT1CF: Port1 Configuration Register        |

| SFR Definition 14.9. P1MODE: Port1 Digital/Analog Input Mode     |

| SFR Definition 14.10. P2: Port2 Register 107                     |

| SFR Definition 14.11. PRT2CF: Port2 Configuration Register       |

| SFR Definition 14.12. P2MODE: Port2 Digital/Analog Input Mode    |

| SFR Definition 14.13. P3: Port3 Register* 108                    |

| SFR Definition 14.14. PRT3CF: Port3 Configuration Register*      |

| SFR Definition 14.15. P3MODE: Port3 Digital/Analog Input Mode*   |

| SFR Definition 15.1. SPI0CFG: SPI Configuration                  |

| SFR Definition 15.2. SPI0CN: SPI Control                         |

| SFR Definition 15.3. SPI0CKR: SPI Clock Rate Register            |

| SFR Definition 15.4. SPI0DAT: SPI Data Register                  |

| SFR Definition 16.1. SBUF: Serial (UART) Data Buffer             |

| SFR Definition 17.1. TCON: Timer Control                         |

| SFR Definition 17.2. TMOD: Timer Mode                            |

| SFR Definition 17.3. CKCON: Clock Control                        |

| SFR Definition 17.4. TL0: Timer 0 Low Byte                       |

| SFR Definition 17.5. TL1: Timer 1 Low Byte                       |

| SFR Definition 17.6. TH0: Timer 0 High Byte                      |

| SFR Definition 17.7. TH1: Timer 1 High Byte                      |

| SFR Definition 17.8. T2CON: Timer 2 Control                      |

| SFR Definition 17.9. RCAP2L: Timer 2 Capture Register Low Byte   |

| SFR Definition 17.10. RCAP2H: Timer 2 Capture Register High Byte |

| SFR Definition 17.11. TL2: Timer 2 Low Byte                      |

| SFR Definition 17.12. TH2: Timer 2 High Byte 138                 |

| JTAG Register Definition 18.1. IR: JTAG Instruction              |

| JTAG Register Definition 18.2. FLASHCON: JTAG Flash Control      |

| JTAG Register Definition 18.3. FLASHADR: JTAG Flash Address      |

| JTAG Register Definition 18.4. FLASHDAT: JTAG Flash Data         |

| JTAG Register Definition 18.5. FLASHSCL: JTAG Flash Scale        |

| JTAG Register Definition 18.6. DEVICEID: JTAG Device ID          |

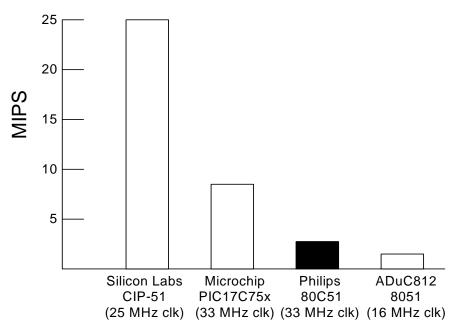

With the CIP-51's maximum system clock at 25 MHz, it has a peak throughput of 25 MIPS. Figure 1.5 shows a comparison of peak throughputs of various 8-bit microcontroller cores with their maximum system clocks.

Figure 1.5. Comparison of Peak MCU Throughputs

#### 1.1.3. Additional Features

The C8051F206, C8051F220/1/6 and C8051F230/1/6 have several key enhancements both inside and outside the CIP-51 core to improve overall performance and ease of use in end applications.

The extended interrupt handler provides 22 interrupt sources into the CIP-51 (as opposed to 7 for the standard 8051), allowing the numerous analog and digital peripherals to interrupt the controller. (An interrupt driven system requires less intervention by the MCU, giving it more effective throughput.) The extra interrupt sources are very useful when building multi-tasking, real-time systems.

There are up to six reset sources for the MCU: an on-board  $V_{DD}$  monitor, a Watchdog Timer, a missing clock detector, a voltage level detection from Comparator 0, a forced software reset, and an external reset pin. The RST pin is bi-directional, accommodating an external reset, or allowing the internally generated reset to be output on the RST pin. The on-board  $V_{DD}$  monitor is enabled by pulling the MONEN pin high (digital 1). The user may disable each reset source except for the  $V_{DD}$  monitor and Reset Input Pin from software. The watchdog timer may be permanently enabled in software after a power-on reset during MCU initialization.

The MCU has an internal, stand-alone clock generator that is used by default as the system clock after reset. If desired, the clock source may be switched "on the fly" to the external oscillator, which can use a crystal, ceramic resonator, capacitor, RC, or external clock source to generate the system clock. This can be extremely useful in low power applications, allowing the MCU to run from a slow (power saving) external crystal source, while periodically switching to the fast (up to 16MHz) internal oscillator as needed.

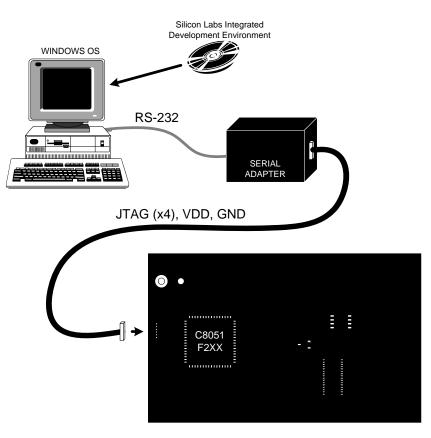

Figure 1.8. Degub Environment Diagram

## 1.4. Digital/Analog Configurable I/O

The standard 8051 Ports (0, 1, 2, and 3) are available on the device. The ports behave like standard 8051 ports with a few enhancements.

Each port pin can be configured as either a push-pull or open-drain output. Any input that is configured as an analog input will have its corresponding weak pull-up turned off.

Digital resources (timers, SPI, UART, system clock, and comparators) are routed to corresponding I/O pins by configuring the port multiplexer. Port multiplexers are programmed by setting bits in SFR's (please see Section 14). Any of the 32 external port pins may be configured as either analog inputs or digital I/O (See Figure 1.9), so effectively, all port pins are dual function.

| R/W      | R/W         | R/W        | R/W          | R/W         | R/W         | R/W         | R/W    | Reset Value  |

|----------|-------------|------------|--------------|-------------|-------------|-------------|--------|--------------|

| ADCSC2   |             | ADCSC0     | -            | -           | AMPGN2      |             | AMPGN0 | 01100000     |

| Bit7     | Bit6        | Bit5       | Bit4         | Bit3        | Bit2        | Bit1        | Bit0   | SFR Address: |

| Biti     | Bito        | Dito       | DRH          | Dito        | DILL        | Bitt        | Bito   | 0xBC         |

|          |             |            |              |             |             |             |        |              |

| Bits7-5: | ADCSC2-0    | : ADC SAR  | Conversior   | n Clock Per | iod Bits    |             |        |              |

|          | 000: SAR (  | Conversion | Clock = 1 S  | system Cloc | :k          |             |        |              |

|          | 001: SAR (  | Conversion | Clock = 2 S  | system Cloc | ks          |             |        |              |

|          | 010: SAR (  |            |              |             |             |             |        |              |

|          | 011: SAR (  |            |              |             |             |             |        |              |

|          | 1xx: SAR C  |            |              | •           |             |             |        |              |

|          | NOTE: SA    |            |              |             | than or equ | al to 2MHz. |        |              |

|          | UNUSED.     |            |              |             |             |             |        |              |

| Bits2–0: | AMPGN2-0    |            | nal Amplifie | er Gain     |             |             |        |              |

|          | 000: Gain : |            |              |             |             |             |        |              |

|          | 001: Gain : | _          |              |             |             |             |        |              |

|          | 010: Gain : |            |              |             |             |             |        |              |

|          | 011: Gain = |            |              |             |             |             |        |              |

|          | 10x: Gain = |            |              |             |             |             |        |              |

|          | 11x: Gain = | = 0.5      |              |             |             |             |        |              |

|          |             |            |              |             |             |             |        |              |

|          |             |            |              |             |             |             |        |              |

|          |             |            |              |             |             |             |        |              |

### SFR Definition 5.2. ADC0CF: ADC Configuration Register

| Input Voltage<br>(Analog Input - GND)                                                                                                         | ADC Data<br>Word |                                         | Input Voltage<br>(Analog Input - GND)                                                                                                    | ADC Data<br>Word |              |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|--|--|

| REF x (255/256)                                                                                                                               | 0xFF             | ]                                       | REF x (255/256)                                                                                                                          | 0xFF             | ])           |  |  |

|                                                                                                                                               |                  | ADWINT<br>not affected                  |                                                                                                                                          |                  | ADWINT=1     |  |  |

|                                                                                                                                               | 0x21             |                                         |                                                                                                                                          | 0x21             |              |  |  |

| REF x (32/256)                                                                                                                                | 0x20             | ADC0LTH                                 | REF x (32/256)                                                                                                                           | 0x20             | ADC0GTH      |  |  |

|                                                                                                                                               | 0x1F             |                                         |                                                                                                                                          | 0x1F             | ADWINT       |  |  |

|                                                                                                                                               | 0x11             | ADWINT=1                                |                                                                                                                                          | 0x11             | not affected |  |  |

| REF x (16/256)                                                                                                                                | 0x10             | ADC0GTH                                 | REF x (16/256)                                                                                                                           | 0x10             | ADCOLTH      |  |  |

|                                                                                                                                               | 0x0F             |                                         |                                                                                                                                          | 0x0F             | $\square$    |  |  |

|                                                                                                                                               |                  | ADWINT<br>not affected                  |                                                                                                                                          |                  | ADWINT=1     |  |  |

| 0                                                                                                                                             | 0x00             |                                         | 0                                                                                                                                        | 0x00             | ])           |  |  |

| Given:<br>AMX0SL = 0x00, $AMX0CF = 0x00$ , $ADLJST = 0$ ,<br>ADC0LTH = 0x20, $ADC0GTH = 0x10$ .<br>An ADC End of Conversion will cause an ADC |                  |                                         | Given:<br>AMX0SL = 0x00, AMX0CF = 0x00, ADLJST = 0,<br>ADC0LTH = 0x10, ADC0GTH = 0x20.                                                   |                  |              |  |  |

|                                                                                                                                               |                  | (ADWINT=1) if the<br>< 0x20 and > 0x10. | An ADC End of Conversion will cause an ADC<br>Window Compare Interrupt (ADWINT=1) if the<br>resulting ADC Data Word is < 0x10 or > 0x20. |                  |              |  |  |

Figure 5.3. 8-Bit ADC Window Interrupt Examples

# Table 6.1. 12-Bit ADC Electrical Characteristics (C8015F206 only)VDD = 3.0 V, VREF = 2.40 V (REFBE=0), PGA Gain = 1, -40 to +85 °C unless otherwise specified.

| Parameter                                                 | Conditions                            | Min      | Тур     | Max             | Units  |

|-----------------------------------------------------------|---------------------------------------|----------|---------|-----------------|--------|

| DC Accuracy                                               | -                                     |          | I       |                 |        |

| Resolution                                                |                                       |          | 12      |                 | bits   |

| Integral Nonlinearity                                     |                                       | —        | ±1      | ±2              | LSB    |

| Differential Nonlinearity                                 | Guaranteed Monotonic                  | —        |         | ±2              | LSB    |

| Offset Error                                              |                                       | ±20      | ±5      |                 | LSB    |

| Full Scale Error                                          | Differential mode                     | —        |         | -20±10          | LSB    |

| Offset Temperature Coefficient                            |                                       | —        | ±0.25   |                 | ppm/°C |

| Dynamic Performance (10 kHz s                             | sine-wave input, 0 to -1 dB of full s | cale, 10 | 0 ksps) |                 |        |

| Signal-to-Noise Plus Distortion                           |                                       | 63       | 66      |                 | dB     |

| Total Harmonic Distortion                                 | Up to the 5 <sup>th</sup> harmonic    | -60      | -72     | —               | dB     |

| Spurious-Free Dynamic Range                               |                                       | 60       | 76      |                 | dB     |

| Conversion Rate                                           | · ·                                   | •        |         |                 |        |

| Conversion Time in SAR Clocks                             |                                       | 16       |         |                 | clocks |

| SAR Clock Frequency                                       |                                       | —        |         | 2.0             | MHz    |

| Track/Hold Acquisition Time                               |                                       | 1.5      | —       |                 | μs     |

| Throughput Rate                                           |                                       | —        | —       | 100             | ksps   |

| Analog Inputs                                             |                                       |          |         |                 |        |

| Voltage Conversion Range                                  |                                       | 0        | —       | VREF            | V      |

| Input Voltage                                             | Any pin (in Analog Input Mode)        | GND      | —       | V <sub>DD</sub> | V      |

| Input Capacitance                                         |                                       | —        | 10      | —               | pF     |

| Power Specifications                                      | •                                     | •        |         | •               |        |

| Power Supply Current<br>(V <sub>DD</sub> supplied to ADC) | Operating Mode, 100 ksps              | _        | 0.45    | 1.0             | mA     |

| Power Supply Rejection                                    |                                       | —        | ±0.3    | —               | mV/V   |

### **Table 7.1. Reference Electrical Characteristics**

$V_{DD}$  = 3.0 V, Temperature –40 to +85 ×C

| External Reference ([REFS | 6L1: REFSL0] = 00), V <sub>REF</sub> = 2.4 V) | Min  | Тур | Max                        | Units |

|---------------------------|-----------------------------------------------|------|-----|----------------------------|-------|

| Input Voltage Range       |                                               | 1.00 |     | (V <sub>DD</sub> ) – 0.3 V | V     |

| Input Current             |                                               | _    | 0.1 | 10                         | μA    |

| Input Resistance          |                                               | 100  |     | —                          | MΩ    |

| R/W     | R                       | R/W          | R/W        | R/W          | R/W            | R/W            | R/W         | Reset Value  |

|---------|-------------------------|--------------|------------|--------------|----------------|----------------|-------------|--------------|

| CP1EN   | CP10UT                  | CP1RIF       | CP1FIF     | CP1HYP1      | CP1HYP0        | CP1HYN1        | CP1HYNC     | 00000000     |

| Bit7    | Bit6                    | Bit5         | Bit4       | Bit3         | Bit2           | Bit1           | Bit0        | SFR Address: |

|         |                         |              |            |              |                |                |             | 0x9F         |

|         | 00/51/0                 |              |            |              |                |                |             |              |

| Bit7:   | CP1EN: Co               | •            |            |              |                |                |             |              |

|         | 0: Compara              |              |            |              |                |                |             |              |

| Dito    | 1: Compara              |              |            | lata Elan    |                |                |             |              |

| Bit6:   | CP1OUT: C<br>0: Voltage | •            | •          | late Flag    |                |                |             |              |

|         | 1: Voltage              |              |            |              |                |                |             |              |

| Bit5:   | CP1RIF: Co              |              |            | ae Interrunt | Flag           |                |             |              |

| Dito.   |                         |              |            |              | s occurred s   | ince this fla  | n was clea  | ared         |

|         |                         |              |            |              | ccurred since  |                |             |              |

| Bit4:   | CP1FIF: Co              |              |            |              |                | o ano nag n    |             | •            |

|         |                         |              | •          | • •          | is occurred s  | since this fla | ad was clea | ared         |

|         |                         |              |            |              | ccurred sinc   |                |             |              |

| Bit3-2: |                         |              | • •        |              | sis Control B  | •              |             |              |

|         | 00: Positive            | e Hysteresis | s Disabled | -            |                |                |             |              |

|         | 01: Positive            | e Hysteresis | s = 2 mV   |              |                |                |             |              |

|         | 10: Positive            | e Hysteresis | s = 4 mV   |              |                |                |             |              |

|         | 11: Positive            | e Hysteresis | s = 10 mV  |              |                |                |             |              |

| Bit1-0: |                         |              | •          |              | esis Control I | Bits           |             |              |

|         | 00: Negativ             |              |            |              |                |                |             |              |

|         | 01: Negativ             |              |            |              |                |                |             |              |

|         | 10: Negativ             |              |            |              |                |                |             |              |

|         | 11: Negativ             | e Hysteres   | is = 10 mV |              |                |                |             |              |

|         |                         |              |            |              |                |                |             |              |

### SFR Definition 8.2. CPT1CN: Comparator 1 Control

#### Notes on Registers, Operands and Addressing Modes:

Rn - Register R0-R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through register R0–R1

**rel -** 8-bit, signed (two's compliment) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00– 0x7F) or an SFR (0x80–0xFF).

#data - 8-bit constant

#data 16 - 16-bit constant

bit - Direct-addressed bit in Data RAM or SFR.

**addr 11 -** 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr 16 -** 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

#### Table 9.3. Special Function Registers (Continued)

SFR's are listed in alphabetical order.

| Address                                                                                                                                  | Register | Description                               | Page No. |

|------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------|----------|

| 0xA4                                                                                                                                     | PRT0CF   | Port 0 Configuration                      | 105      |

| 0xA5                                                                                                                                     | PRT1CF   | Port 1 Configuration                      | 106      |

| 0xA6                                                                                                                                     | PRT2CF   | Port 2 Configuration                      | 107      |

| 0xA7                                                                                                                                     | PRT3CF   | Port 3 Configuration                      | 108      |

| 0xE1                                                                                                                                     | PRT0MX   | Port 0 Multiplexer I/O Configuration      | 103      |

| 0xE2                                                                                                                                     | PRT1MX   | Port 1 Multiplexer I/O Configuration      | 104      |

| 0xE3                                                                                                                                     | PRT2MX   | Port 2 Multiplexer I/O Configuration      | 104      |

| 0x8F                                                                                                                                     | PSCTL    | Program Store RW Control                  | 88       |

| 0xD0                                                                                                                                     | PSW      | Program Status Word                       | 72       |

| 0xCB                                                                                                                                     | RCAP2H   | Counter/Timer 2 Capture (High Byte)       | 138      |

| 0xCA                                                                                                                                     | RCAP2L   | Counter/Timer 2 Capture (Low Byte)        | 138      |

| 0xD1                                                                                                                                     | REF0CN   | Voltage Reference Control Register        | 50       |

| 0xEF                                                                                                                                     | RSTSRC   | Reset Source Register                     | 95       |

| 0x99                                                                                                                                     | SBUF     | Serial Data Buffer (UART)                 | 123      |

| 0x98                                                                                                                                     | SCON     | Serial Port Control (UART)                | 124      |

| 0x81                                                                                                                                     | SP       | Stack Pointer                             | 71       |

| 0x9A                                                                                                                                     | SPI0CFG  | Serial Peripheral Interface Configuration | 114      |

| 0x9D                                                                                                                                     | SPI0CKR  | SPI Clock Rate                            | 116      |

| 0xF8                                                                                                                                     | SPIOCN   | SPI Bus Control                           | 115      |

| 0x9B                                                                                                                                     | SPI0DAT  | SPI Port 1Data                            | 116      |

| 0xAD                                                                                                                                     | SWCINT   | Software Controlled Interrupt Register    | 75       |

| 0xC8                                                                                                                                     | T2CON    | Counter/Timer 2 Control                   | 137      |

| 0x88                                                                                                                                     | TCON     | Counter/Timer Control                     | 129      |

| 0x8C                                                                                                                                     | TH0      | Counter/Timer 0 Data Word (High Byte)     | 132      |

| 0x8D                                                                                                                                     | TH1      | Counter/Timer 1 Data Word (High Byte)     | 132      |

| 0xCD                                                                                                                                     | TH2      | Counter/Timer 2 Data Word (High Byte)     | 138      |

| 0x8A                                                                                                                                     | TL0      | Counter/Timer 0 Data Word (Low Byte)      | 132      |

| 0x8B                                                                                                                                     | TL1      | Counter/Timer 1 Data Word (Low Byte)      | 132      |

| 0xCC                                                                                                                                     | TL2      | Counter/Timer 2 Data Word (Low Byte)      | 138      |

| 0x89                                                                                                                                     | TMOD     | Counter/Timer Mode                        | 130      |

| 0xFF                                                                                                                                     | WDTCN    | Watchdog Timer Control                    | 94       |

| 0x84–86, 0x91–97, 0x9C, 0xA1–A3, 0xA9–<br>AC, 0xAE, 0xB3–B5, 0xB9–BA, 0xBD–<br>BE,0xC0–C4, 0xC6,0xCE–CF,0xD2–<br>DF,0xE9–EE,0xF5,0xF9–FE |          | Reserved                                  |          |

#### Notes:

- 1. C8051F230/1/6 Do not have these registers.

- 2. C8051F221/231 Does not have this register (32 pin package).

- 3. On the C8051F206 and C8051F226/236 only.

- **4.** On the C8051F206 only (12-bit ADC)

| R/W   | R/W                                                                                                                                                                                                                                                                                                        | R/W                                                                                                                                                                                                                                                                                                     | R/W                            | R/W                           | R/W                             | R/W   | R/W  | Reset Value          |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------|---------------------------------|-------|------|----------------------|--|--|--|

| PXVLD | -                                                                                                                                                                                                                                                                                                          | PSCI3                                                                                                                                                                                                                                                                                                   | PSCI2                          | PSCI1                         | PSCI0                           | PADC0 | -    | 00000000             |  |  |  |

| Bit7  | Bit6                                                                                                                                                                                                                                                                                                       | Bit5                                                                                                                                                                                                                                                                                                    | Bit4                           | Bit3                          | Bit2                            | Bit1  | Bit0 | SFR Address:<br>0xF7 |  |  |  |

| Bit7: | <ul> <li>PXVLD: External Clock Source Valid (XTLVLD) Interrupt Priority Control.</li> <li>This bit sets the priority of the XTLVLD interrupt.</li> <li>0: XTLVLD interrupt set to low priority level.</li> <li>1: XTLVLD interrupt set to high priority level.</li> </ul>                                  |                                                                                                                                                                                                                                                                                                         |                                |                               |                                 |       |      |                      |  |  |  |

| Bit6: | Reserved.                                                                                                                                                                                                                                                                                                  | Must write                                                                                                                                                                                                                                                                                              | 0. Reads 0                     |                               |                                 |       |      |                      |  |  |  |

| Bit5: | This bit sets<br>0: External                                                                                                                                                                                                                                                                               | tware Contr<br>s the priority<br>I Interrupt 7<br>I Interrupt 7                                                                                                                                                                                                                                         | / of the Soft<br>set to low p  | ware Contro<br>priority level | olled Interru                   | pt 3. |      |                      |  |  |  |

| Bit4: | This bit sets<br>0: Software                                                                                                                                                                                                                                                                               | tware Contr<br>s the priority<br>e Controlled<br>e Controlled                                                                                                                                                                                                                                           | / of the Soft<br>I Interrupt 2 | ware Contro<br>set to low p   | olled Interru<br>priority level | •     |      |                      |  |  |  |

| Bit3: | This bit sets<br>0: Software                                                                                                                                                                                                                                                                               | <ul> <li>PSCI1: Software Controlled Interrupt 1 Priority Control.</li> <li>This bit sets the priority of the Software Controlled Interrupt 1.</li> <li>0: Software Controlled Interrupt 1 set to low priority level.</li> <li>1: Software Controlled Interrupt 1 set to high priority level.</li> </ul> |                                |                               |                                 |       |      |                      |  |  |  |

| Bit2: | This bit sets<br>0: Software                                                                                                                                                                                                                                                                               | <ul> <li>PSCI0: Software Controlled Interrupt 0 Priority Control.</li> <li>This bit sets the priority of the Software Controlled Interrupt 0.</li> <li>0: Software Controlled Interrupt 0 set to low priority level.</li> <li>1: Software Controlled Interrupt 0 set to high priority level.</li> </ul> |                                |                               |                                 |       |      |                      |  |  |  |

| Bit1: | <ul> <li>PADC0: ADC End of Conversion Interrupt Priority Control.</li> <li>This bit sets the priority of the ADC0 End of Conversion Interrupt.</li> <li>0: ADC0 End of Conversion interrupt set to low priority level.</li> <li>1: ADC0 End of Conversion interrupt set to high priority level.</li> </ul> |                                                                                                                                                                                                                                                                                                         |                                |                               |                                 |       |      |                      |  |  |  |

| Bit0: | Reserved.                                                                                                                                                                                                                                                                                                  | Read = 0, \                                                                                                                                                                                                                                                                                             | Write = don'                   | t care.                       |                                 |       |      |                      |  |  |  |

## SFR Definition 9.13. EIP2: Extended Interrupt Priority 2

write/erase operations are disabled. Note that code execution in the 8051 is stalled while the Flash is being programmed or erased.

#### **Table 10.1. Flash Memory Electrical Characteristics**

$V_{DD}$  = 2.7 to 3.6 V, -40 to +85 ×C unless otherwise specified.

| Parameter              | Conditions | Min  | Тур   | Max | Units    |

|------------------------|------------|------|-------|-----|----------|

| Endurance              |            | 20 k | 100 k | _   | Erase/Wr |

| Erase/Write Cycle Time |            |      | 10    |     | ms       |

#### Non-volatile Data Storage

The Flash memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX instruction and read using the MOVC instruction.

The MCU incorporates an additional 128-byte sector of Flash memory located at 0x2000 – 0x207F. This sector can be used for program code or data storage. However, its smaller sector size makes it particularly well suited as general purpose, non-volatile scratchpad memory. Even though Flash memory can be written a single byte at a time, an entire sector must be erased first. In order to change a single byte of a multibyte data set, the data must be moved to temporary storage. Next, the sector is erased, the data set updated and the data set returned to the original sector. The 128-byte sector-size facilitates updating data without wasting program memory space by allowing the use of internal data RAM for temporary storage. (A normal 512-byte sector is too large to be stored in the 256-byte internal data memory.)

#### **10.2. Security Options**

The CIP-51 provides security options to protect the Flash memory from inadvertent modification by software as well as prevent the viewing of proprietary program code and constants. The Program Store Write Enable (PSCTL.0) and the Program Store Erase Enable (PSCTL.1) bits protect the Flash memory from accidental modification by software. These bits must be explicitly set to logic 1 before software can modify the Flash memory. Additional security features prevent proprietary program code and data constants from being read or altered across the JTAG interface or by software running on the system controller.

A set of security lock bytes stored at 0x1DFE and 0x1DFF protect the Flash program memory from being read or altered across the JTAG interface. Each bit in a security lock-byte protects one 1 kB block of memory. Clearing a bit to logic 0 in a Read lock byte prevents the corresponding block of Flash memory from being read across the JTAG interface. Clearing a bit in the Write/Erase lock byte protects the block from JTAG erasures and/or writes. The Read lock byte is at location 0x1DFF. The Write/Erase lock byte is located at 0x1DFE. Figure 10.1 shows the location and bit definitions of the security bytes. The 512-byte sector containing the lock byte cannot be erased by software. Writing to the reserved area should not be performed.

| SFR Definition 13.2 | . OSCXCN: External | <b>Oscillator Control</b> |

|---------------------|--------------------|---------------------------|

|---------------------|--------------------|---------------------------|

| R                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                              | R/W                                                                                                                                                       | R/W             | R/W          | R/W                      | R/W      | R/W              | Reset Value  |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|--------------------------|----------|------------------|--------------|--|--|--|

| XTLVLD            |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                           |                 |              | XFCN2                    | XFCN1    | XFCN0            | 00110000     |  |  |  |

| Bit7              | Bit6                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                           | Bit4            | Bit3         | Bit2                     | Bit1     | Bit0             | SFR Address: |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                           |                 |              |                          |          |                  | 0xB1         |  |  |  |

| Bit7:             | (Valid o<br>0: Crys                                                                                                                                                                                                                                                                                                                                                                                              | <ul> <li>KTLVLD: Crystal Oscillator Valid Flag</li> <li>Valid only when XOSCMD = 1xx.)</li> <li>Crystal Oscillator is unused or not yet stable</li> </ul> |                 |              |                          |          |                  |              |  |  |  |

| Bits6–4:          | <ol> <li>Crystal Oscillator is running and stable</li> <li>KOSCMD2–0: External Oscillator Mode Bits</li> <li>O0x: Off. XTAL1 pin is grounded internally.</li> <li>O10: System Clock from External CMOS Clock on XTAL1 pin.</li> <li>O11: System Clock from External CMOS Clock on XTAL1 pin divided by 2.</li> <li>10x: RC/C Oscillator Mode with divide by 2 stage.</li> <li>Crystal Oscillator Mode</li> </ol> |                                                                                                                                                           |                 |              |                          |          |                  |              |  |  |  |

| D:+0.             |                                                                                                                                                                                                                                                                                                                                                                                                                  | ystal Oscillator N                                                                                                                                        |                 | •            | -                        |          |                  |              |  |  |  |

| Bit3:<br>Bits2–0: |                                                                                                                                                                                                                                                                                                                                                                                                                  | VED. Read = u<br>-0: External Osc                                                                                                                         |                 |              |                          |          |                  |              |  |  |  |

| Dit32-0.          |                                                                                                                                                                                                                                                                                                                                                                                                                  | 1: see table belo                                                                                                                                         |                 |              |                          |          |                  |              |  |  |  |

|                   | XFCN                                                                                                                                                                                                                                                                                                                                                                                                             | Crystal (XOSC                                                                                                                                             |                 | RC (XO       | SCMD = 10                | )x) C (X | OSCMD =          | 10x)         |  |  |  |

|                   | 000                                                                                                                                                                                                                                                                                                                                                                                                              | f ≤ 12.5                                                                                                                                                  |                 | -            | 25 kHz                   |          | Factor = 0       |              |  |  |  |

|                   | 001                                                                                                                                                                                                                                                                                                                                                                                                              | 12.5 kHz < f ≤                                                                                                                                            |                 |              | < f ≤ 50 kH              |          | Factor = $1$     |              |  |  |  |

|                   | 010                                                                                                                                                                                                                                                                                                                                                                                                              | 30.35 kHz < f s                                                                                                                                           |                 | -            | $< f \le 100 \text{ kH}$ |          | K Factor = $4.4$ |              |  |  |  |

|                   | 011                                                                                                                                                                                                                                                                                                                                                                                                              | 93.8 kHz < f ≤                                                                                                                                            |                 |              | < f ≤ 200 k              |          | Factor = 1       |              |  |  |  |

|                   | 100                                                                                                                                                                                                                                                                                                                                                                                                              | 267 kHz < f ≤                                                                                                                                             |                 |              | < f ≤ 400 k              |          | Factor = 3       |              |  |  |  |

|                   | 101                                                                                                                                                                                                                                                                                                                                                                                                              | 722 kHz < f ≤                                                                                                                                             | 2.23 MHz        | 400 kHz      | < f ≤ 800 k              | Hz K     | Factor = 1       | 00           |  |  |  |

|                   | 110                                                                                                                                                                                                                                                                                                                                                                                                              | 2.23 MHz < f ≤                                                                                                                                            | 6.74 MHz        | 800 kHz      | < f ≤ 1.6 M              | Hz K     | Factor = 4       | 20           |  |  |  |

|                   | 111                                                                                                                                                                                                                                                                                                                                                                                                              | f > 6.74                                                                                                                                                  | MHz             | 1.6 MHz      | < f ≤ 3.2 M              | Hz K     | Factor = 14      | 400          |  |  |  |

|                   | Choose                                                                                                                                                                                                                                                                                                                                                                                                           | (Circuit from Fig<br>XFCN value to<br>t from Figure 13                                                                                                    | match the c     | rystal frequ | iency.                   | 1x)      |                  |              |  |  |  |

|                   | •                                                                                                                                                                                                                                                                                                                                                                                                                | oscillation frequ                                                                                                                                         | •               |              | - 100                    |          |                  |              |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                  | (10 <sup>3</sup> ) / (R x C), v                                                                                                                           |                 | -            |                          |          |                  |              |  |  |  |

|                   | f = frequ                                                                                                                                                                                                                                                                                                                                                                                                        | ency of oscillati                                                                                                                                         | on in MHz       |              |                          |          |                  |              |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                  | acitor value in p                                                                                                                                         |                 |              |                          |          |                  |              |  |  |  |

|                   | R = Pul                                                                                                                                                                                                                                                                                                                                                                                                          | -up resistor valu                                                                                                                                         | e in k $\Omega$ |              |                          |          |                  |              |  |  |  |

| C MODE            | <pre>C MODE (Circuit from Figure 13.1, Option 3; XOSCMD = 10x)<br/>Choose K Factor (KF) for the oscillation frequency desired:<br/>f = KF / (C x AV+), where<br/>f = frequency of oscillation in MHz<br/>C = capacitor value on XTAL1, XTAL2 pins in pF</pre>                                                                                                                                                    |                                                                                                                                                           |                 |              |                          |          |                  |              |  |  |  |

|                   | $V_{DD} = F$                                                                                                                                                                                                                                                                                                                                                                                                     | ower supply vol                                                                                                                                           | tage on MC      | U in volts   |                          |          |                  |              |  |  |  |

#### 13.1. External Crystal Example

If a crystal were used to generate the system clock for the MCU, the circuit would be as shown in Figure 13.1, Option 1. For an ECS-110.5-20-4 crystal, the resonate frequency is 11.0592 MHz, the intrinsic capacitance is 7 pF, and the ESR is 60 W. The compensation capacitors should be 33 pF each, and the PWB parasitic capacitance is estimated to be 2 pF. The appropriate External Oscillator Frequency Control value (XFCN) from the Crystal column in the table in SFR Definition 13.2 (OSCXCN Register) should be 111b.

The Crystal Oscillator Valid Flag (XTLVLD in register OSCXCN) is set to logic 1 by hardware when the external oscillator is running and stable. The XTLVLD detection circuit requires a startup time of at least 1ms between enabling the oscillator and checking the XTLVLD flag. Switching to the external oscillator before 1ms can result in unpredictable behavior. The recommend procedure is:

- 1. Enable the external oscillator

- 2. Wait 1 ms

- 3. Poll for XTLVLD '0' ==> '1'

- 4. Switch to the external oscillator

Switching to the external oscillator before the crystal oscillator has stabilized could result in unpredictable behavior.

NOTE: Crystal oscillator circuits are quite sensitive to PCB layout. The crystal should be placed as close as possible to the XTAL pins on the device, keeping the traces as short as possible and shielded with ground plane from any other traces which could introduce noise or interference.

#### 13.2. External RC Example

If an external RC network were used to generate the system clock for the MCU, the circuit would be as shown in Figure 13.1, Option 2. The capacitor must be no greater than 100 pF, but using a very small capacitor will increase the frequency drift due to the PWB parasitic capacitance. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, first select the RC network value to produce the desired frequency of oscillation. If the frequency desired is 100 kHz, let R = 246 kW and C = 50 pF:

f = 1.23(103)/RC = 1.23(103) / [246 x 50] = 0.1 MHz = 100 kHz XFCN <sup>3</sup> log2(f/25 kHz) XFCN <sup>3</sup> log2(100 kHz/25 kHz) = log2(4) XFCN <sup>3</sup> 2, or code 010

#### 13.3. External Capacitor Example

If an external capacitor were used to generate the system clock for the MCU, the circuit would be as shown in Figure 13.1, Option 3. The capacitor must be no greater than 100 pF, but using a very small capacitor will increase the frequency drift due to the PWB parasitic capacitance. To determine the required External Oscillator Frequency Control value (XFCN) in the OSCXCN Register, select the capacitor to be used and find the frequency of oscillation from the equations below. Assume  $V_{DD} = 3.0$  V and C = 50 pF:

$f = KF / (C \times V_{DD}) = KF / (50 \times 3)$ f = KF / 150

If a frequency of roughly 90kHz is desired, select the K Factor from the table in SFR Definition 13.2 as KF = 13:

f = 13 /150 = 0.087 MHz, or 87 kHz

Therefore, the XFCN value to use in this example is 011.

#### 16.1. UART Operational Modes

The UART provides four operating modes (one synchronous and three asynchronous) selected by setting configuration bits in the SCON register. These four modes offer different baud rates and communication protocols. The four modes are summarized in Table 16.1 below. Detailed descriptions follow.

| Mode | Synchronization | Baud Clock                  | Data Bits | Start/Stop Bits |

|------|-----------------|-----------------------------|-----------|-----------------|

| 0    | Synchronous     | SYSCLK/12                   | 8         | None            |

| 1    | Asynchronous    | Timer 1 or Timer 2 Overflow | 8         | 1 Start, 1 Stop |

| 2    | Asynchronous    | SYSCLK/32 or SYSCLK/64      | 9         | 1 Start, 1 Stop |

| 3    | Asynchronous    | Timer 1 or Timer 2 Overflow | 9         | 1 Start, 1 Stop |

Table 16.1. UART Modes

#### 16.1.1. Mode 0: Synchronous Mode

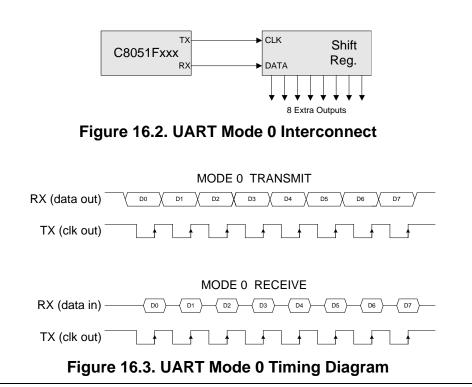

Mode 0 provides synchronous, half-duplex communication. Serial data is transmitted and received on the RX pin. The TX pin provides the shift clock for both transmit and receive. The MCU must be the master since it generates the shift clock for transmission in both directions (see the interconnect diagram in Figure 16.2).

Eight data bits are transmitted/received, LSB first (see the timing diagram in Figure 16.3). Data transmission begins when an instruction writes a data byte to the SBUF register. The TI Transmit Interrupt Flag (SCON.1) is set at the end of the eighth bit time. Data reception begins when the REN Receive Enable bit (SCON.4) is set to logic 1 and the RI Receive Interrupt Flag (SCON.0) is cleared. One cycle after the eighth bit is shifted in, the RI flag is set and reception stops until software clears the RI bit. An interrupt will occur if enabled when either TI or RI are set.

The Mode 0 baud rate is system clock frequency divided by twelve.

#### 16.1.2. Mode 1: 8-Bit UART, Variable Baud Rate

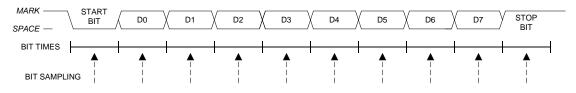

Mode 1 provides standard asynchronous, full duplex communication using a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit (see the timing diagram in Figure 16.4). Data are transmitted from the TX pin and received at the RX pin (see the interconnection diagram in Figure 16.5). On receive, the eight data bits are stored in SBUF and the stop bit goes into RB8 (SCON.2).

Data transmission begins when an instruction writes a data byte to the SBUF register. The TI Transmit Interrupt Flag (SCON.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN Receive Enable bit (SCON.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF receive register if the following conditions are met: RI must be logic 0, and if SM2 is logic 1, the stop bit must be logic 1.

If these conditions are met, the eight bits of data are stored in SBUF, the stop bit is stored in RB8, and the RI flag is set. If these conditions are not met, SBUF and RB8 will not be loaded and the RI flag will not be set. An interrupt will occur if enabled when either TI or RI is set.

Figure 16.4. UART Mode 1 Timing Diagram

The baud rate generated in Mode 1 is a function of timer overflow. The UART can use Timer 1 operating in 8-bit Counter/Timer with Auto-Reload Mode, or Timer 2 operating in Baud Rate Generator Mode to generate the baud rate (note that the TX and RX clock sources are selected separately). On each timer overflow event (a rollover from all ones (0xFF for Timer 1, 0xFFFF for Timer 2) to zero), a clock is sent to the baud rate logic.

When Timer 1 is selected as a baud rate source, the SMOD bit (PCON.7) selects whether or not to divide the Timer 1 overflow rate by two. On reset, the SMOD bit is logic 0, thus selecting the lower speed baud rate by default. The SMOD bit affects the baud rate generated by Timer 1 as follows:

Mode 1 Baud Rate =  $(1 / 32) \times T1_OVERFLOWRATE$  (when the SMOD bit is set to logic 0). Mode 1 Baud Rate =  $(1 / 16) \times T1_OVERFLOWRATE$  (when the SMOD bit is set to logic 1).

When Timer 2 is selected as a baud rate source, the baud rate generated by Timer 2 is as follows:

Mode 1 Baud Rate =  $(1 / 16) \times T2_OVERFLOWRATE$ .

The Timer 1 overflow rate is determined by the Timer 1 clock source (T1CLK) and reload value (TH1). The frequency of T1CLK can be selected as SYSCLK, SYSCLK/12, or an external clock source. The Timer 1 overflow rate can be calculated as follows:

$T1_OVERFLOWRATE = T1CLK / (256 - TH1).$

For example, assume TMOD = 0x20.

| Oscillator Frequency<br>(MHz) | Divide Factor | Timer 1 Load Value* | Resulting Baud Rate** |

|-------------------------------|---------------|---------------------|-----------------------|

| 7.3728                        | 64            | 0xFC                | 115200                |

| 5.5296                        | 48            | 0xFD                | 115200                |

| 3.6864                        | 32            | 0xFE                | 115200                |

| 1.8432                        | 16            | 0xFF                | 115200                |

| 24.576                        | 320           | 0xEC                | 76800                 |

| 25.0                          | 434           | 0xE5                | 57600 (57870)         |

| 25.0                          | 868           | 0xCA                | 28800                 |

| 24.576                        | 848           | 0xCB                | 28800 (28921)         |

| 24.0                          | 833           | 0xCC                | 28800 (28846)         |

| 23.592                        | 819           | 0xCD                | 28800 (28911)         |

| 22.1184                       | 768           | 0xD0                | 28800                 |

| 18.432                        | 640           | 0xD8                | 28800                 |

| 16.5888                       | 576           | 0xDC                | 28800                 |

| 14.7456                       | 512           | 0xE0                | 28800                 |

| 12.9024                       | 448           | 0xE4                | 28800                 |

| 11.0592                       | 348           | 0xE8                | 28800                 |

| 9.216                         | 320           | 0xEC                | 28800                 |

| 7.3728                        | 256           | 0xF0                | 28800                 |

| 5.5296                        | 192           | 0xF4                | 28800                 |

| 3.6864                        | 128           | 0xF8                | 28800                 |

| 1.8432                        | 64            | 0xFC                | 28800                 |

### Table 16.2. Oscillator Frequencies for Standard Baud Rates (Continued)

### SFR Definition 16.1. SBUF: Serial (UART) Data Buffer

| R/W      | R/W           | R/W                                         | R/W                           | R/W                                       | R/W                          | R/W          | R/W       | Reset Value<br>00000000                      |

|----------|---------------|---------------------------------------------|-------------------------------|-------------------------------------------|------------------------------|--------------|-----------|----------------------------------------------|

| Bit7     | Bit6          | Bit5                                        | Bit4                          | Bit3                                      | Bit2                         | Bit1         | Bit0      | SFR Address:<br>0x99                         |

| Bits7–0: | to SBUF, it g | ally two reg<br>goes to the<br>at initiates | isters; a trai<br>transmit bu | nsmit <sup>`</sup> and a<br>ffer and is h | receive but<br>eld for seria | al transmiss | ion. Movi | ita is moved<br>ng a byte to<br>nes from the |

## SFR Definition 17.8. T2CON: Timer 2 Control

| R/W   | R/W                                                                                                                                                                                          | R/W                                                                                                                                                                                              | R/W          | R/W            | R/W          | R/W          | R/W                               | Reset Value   |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|--------------|--------------|-----------------------------------|---------------|--|--|--|

| TF2   | EXF2                                                                                                                                                                                         | RCLK                                                                                                                                                                                             | TCLK         | EXEN2          | TR2          | C/T2         | CP/RL2                            | 00000000      |  |  |  |

| Bit7  | Bit6                                                                                                                                                                                         | Bit5                                                                                                                                                                                             | Bit4         | Bit3           | Bit2         | Bit1         | Bit0                              | SFR Address:  |  |  |  |