# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SPI, UART/USART                                                |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                               |

| Number of I/O              | 32                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                |                                                                |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 32x8b                                                      |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f220-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

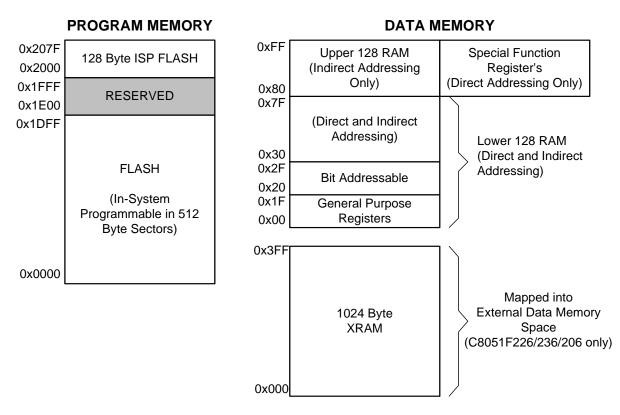

Figure 1.7. On-Board Memory Map

#### 1.3. JTAG

The C8051F2xx have on-chip JTAG and debug logic that provide non-intrusive, full speed, in-circuit debug using the production part installed in the end application using the four-pin JTAG I/F. The C8051F2xxDK is a development kit with all the hardware and software necessary to develop application code and perform in-circuit debug with the C8051F2xx. The kit includes software with a developer's studio and debugger, an integrated 8051 assembler, and an RS-232 to JTAG interface module referred to as the EC. It also has a target application board with a C8051F2xx installed and large prototyping area, plus the RS-232 and JTAG cables, and wall-mount power supply. The Development Kit requires a Windows OS (Windows 95 or later) computer with one available RS-232 serial port. As shown in Figure 1.8, the PC is connected via RS-232 to the EC. A six-inch ribbon cable connects the EC to the user's application board. It requires roughly 20 mA at 2.7–3.6 V. For applications where there is not sufficient power available from the target board, the provided power supply can be connected directly to the EC.

This is a vastly superior configuration for developing and debugging embedded applications compared to standard MCU Emulators, which use on-board "ICE Chips" and target cables and require the MCU in the application board to be socketed. Silicon Labs' debug environment both increases ease of use, and preserves the performance of the precision analog peripherals.

#### **Global DC Electrical Characteristics** 3.

#### **Table 3.1. Global DC Electrical Characteristics**

-40 to +85 °C unless otherwise specified.

| Parameter                                                                                    | Conditions                                        | Min | Тур               | Мах | Units          |

|----------------------------------------------------------------------------------------------|---------------------------------------------------|-----|-------------------|-----|----------------|

| Analog Supply Voltage <sup>1</sup>                                                           |                                                   | 2.7 | 3.0               | 3.6 | V              |

| V <sub>DD</sub> supply current with ADC and comparators active, and CPU active               | Clock = 25 MHz<br>Clock = 1 MHz<br>Clock = 32 kHz | _   | 13<br>1.5<br>300  | _   | mA<br>mA<br>μA |

| $V_{\text{DD}}$ supply current with ADC and comparators active, and CPU inactive (Idle Mode) | Clock = 25 MHz<br>Clock = 1 MHz<br>Clock = 32 kHz | _   | 9<br>1.8<br>275   | _   | mA<br>mA<br>μA |

| V <sub>DD</sub> supply current with ADC and comparators inactive, and CPU active             | Clock = 25 MHz<br>Clock = 1 MHz<br>Clock = 32 kHz | _   | 12.5<br>1.0<br>25 | _   | mA<br>mA<br>μA |

| Digital Supply Current with CPU inactive (Idle Mode)                                         | Clock = 25 MHz<br>Clock = 1 MHz<br>Clock = 32 kHz | _   | 8.5<br>1.4<br>25  | _   | mA<br>mA<br>μA |

| Digital Supply Current (Stop Mode),<br>V <sub>DD</sub> monitor enabled                       | Oscillator not running                            | _   | 10                | _   | μA             |

| Digital Supply Current (Stop Mode),<br>V <sub>DD</sub> monitor disabled                      | Oscillator not running                            | -   | 0.1               | _   | μA             |

| Digital Supply RAM Data Retention Voltage                                                    |                                                   | -   | 1.5               | _   | V              |

| Specified Operating Temperature<br>Range                                                     |                                                   | -40 | _                 | +85 | °C             |

| SYSCLK (system clock<br>frequency) <sup>2</sup>                                              |                                                   | 0   | _                 | 25  | MHz            |

| Tsysl (SYSCLK low time)                                                                      |                                                   | 18  | —                 | _   | ns             |

| Tsysh (SYSCLK high time)                                                                     |                                                   | 18  | —                 | _   | ns             |

Notes:

Analog Supply AV+ must be greater than 1 V for V<sub>DD</sub> monitor to operate.

SYSCLK must be at least 32 kHz to enable debugging.

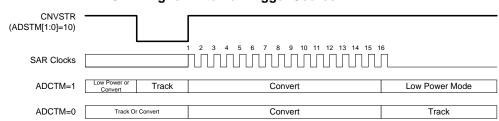

#### 5.2. ADC Modes of Operation

The ADC has a maximum conversion speed of 100ksps. The ADC conversion clock is derived from the system clock. The ADC conversion clock is derived from a divided version of SYSCLK. Divide ratios of 1,2,4,8, or 16 are supported by setting the ADCSC bits in the ADC0CF Register. This is useful to adjust conversion speed to accommodate different system clock speeds.

A conversion can be initiated in one of two ways, depending on the programmed states of the ADC Start of Conversion Mode bits (ADSTM1, ADSTM0) in ADC0CN. Conversions may be initiated by:

- 1. Writing a 1 to the ADBUSY bit of ADC0CN;

- 2. A Timer 2 overflow (i.e., timed continuous conversions).

Writing a 1 to ADBUSY provides software control of the ADC whereby conversions are performed "ondemand". During conversion, the ADBUSY bit is set to 1 and restored to 0 when conversion is complete. The falling edge of ADBUSY triggers an interrupt (when enabled) and sets the ADCINT interrupt flag in the ADC0CN register. Note: When conversions are performed "on-demand", the ADCINT flag, not ADBUSY, should be polled to determine when the conversion has completed. Converted data is available in the ADC data word register, ADC0H.

The ADCTM bit in register ADC0CN controls the ADC track-and-hold mode. In its default state, the ADC input is continuously tracked, except when a conversion is in progress. Setting ADCTM to 1 allows one of two different low power track-and-hold modes to be specified by states of the ADSTM1-0 bits (also in ADC0CN):

- 1. Tracking begins with a write of 1 to ADBUSY and lasts for 3 SAR clocks;

- 2. Tracking starts with an overflow of Timer 2 and lasts for 3 SAR clocks.

Tracking can be disabled (shutdown) when the entire chip is in low power standby or sleep modes.

#### A. ADC Timing for External Trigger Source

| Timer2, Timer3 Overflow;<br>Write 1 to ADBUSY<br>(ADSTM[1:0]=00, 01, 11)<br>SAR Clocks |                                                                                                                                                                                                                                                                                  |         | 6 17 18 19     |  |  |  |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|----------------|--|--|--|

| ADCTM=1                                                                                | Low Power or<br>Convert Track                                                                                                                                                                                                                                                    | Convert | Low Power Mode |  |  |  |

| SAR Clocks                                                                             | Convert         Hotek         Convert         Low Folder Midde           1         2         3         4         5         6         7         8         9         10         11         12         13         14         15         16           Track or Convert         Track |         |                |  |  |  |

Figure 5.2. 12-Bit ADC Track and Conversion Example Timing

# C8051F2xx

| Input Voltage<br>(Analog Input - GND) | ADC Data<br>Word       |                                         | Input Voltage<br>(Analog Input - GND)                                                                                                    | ADC Data<br>Word |              |  |

|---------------------------------------|------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|--|

| REF x (255/256)                       | 0xFF                   | ]                                       | REF x (255/256)                                                                                                                          | 0xFF             |              |  |

|                                       |                        | ADWINT<br>not affected                  |                                                                                                                                          |                  | ADWINT=1     |  |

|                                       | 0x21                   |                                         |                                                                                                                                          | 0x21             |              |  |

| REF x (32/256)                        | 0x20                   | ADC0LTH                                 | REF x (32/256)                                                                                                                           | 0x20             | ADC0GTH      |  |

|                                       | 0x1F                   |                                         |                                                                                                                                          | 0x1F             | ADWINT       |  |

|                                       | 0x11                   | ADWINT=1                                |                                                                                                                                          | 0x11             | not affected |  |

| REF x (16/256)                        | 0x10                   | ADC0GTH                                 | REF x (16/256)                                                                                                                           | 0x10             | ADCOLTH      |  |

|                                       | 0x0F                   |                                         |                                                                                                                                          | 0x0F             | $\square$    |  |

|                                       |                        | ADWINT<br>not affected                  |                                                                                                                                          |                  | ADWINT=1     |  |

| 0                                     | 0x00                   |                                         | 0                                                                                                                                        | 0x00             | ])           |  |

| ADC0LTH = 0x20<br>An ADC End of       | ), ADC0G<br>Conversion | will cause an ADC                       | Given:<br>AMX0SL = 0x00, AM<br>ADC0LTH = 0x10,                                                                                           | ADC0GTH          | = 0x20.      |  |

|                                       |                        | (ADWINT=1) if the<br>< 0x20 and > 0x10. | An ADC End of Conversion will cause an ADC<br>Window Compare Interrupt (ADWINT=1) if the<br>resulting ADC Data Word is < 0x10 or > 0x20. |                  |              |  |

Figure 5.3. 8-Bit ADC Window Interrupt Examples

### Table 5.1. 8-Bit ADC Electrical Characteristics

VDD = 3.0 V, VREF = 2.40 V, PGA Gain = 1, -40 to +85 ×C unless otherwise specified.

| Parameter                        | Conditions                         | Min       | Тур     | Max      | Units  |

|----------------------------------|------------------------------------|-----------|---------|----------|--------|

| DC Accuracy                      |                                    | •         |         |          | •      |

| Resolution                       |                                    |           | 8       | —        | bits   |

| Integral Nonlinearity            |                                    |           | —       | ±1/2     | LSB    |

| Differential Nonlinearity        | Guaranteed Monotonic               | _         | —       | ±1/2     | LSB    |

| Offset Error                     |                                    | ±2        | —       | ±1/2     | LSB    |

| Gain Error                       |                                    | ±2        | —       | ±1/2     | LSB    |

| Offset Temperature Coefficient   |                                    |           | ±0.25   | _        | ppm/°C |

| Dynamic Performance (10 kHz sine | wave input, 0 to –1 dB of full     | scale, 10 | 0 ksps) |          |        |

| Signal-to-Noise Plus Distortion  |                                    | 49.5      | —       | _        | dB     |

| Total Harmonic Distortion        | Up to the 5 <sup>th</sup> harmonic | -60       | -65     | _        | dB     |

| Spurious-Free Dynamic Range      |                                    |           | -65     | _        | dB     |

| Conversion Rate                  |                                    | •         |         |          | •      |

| Conversion Time in SAR Clocks    |                                    | 16        | —       | —        | clocks |

| SAR Clock Frequency              |                                    |           | —       | 2.5      | MHz    |

| Track/Hold Acquisition Time      |                                    | 1.5       | —       | _        | μs     |

| Throughput Rate                  |                                    | _         | —       | 100      | ksps   |

| Analog Inputs                    | ·                                  |           |         |          |        |

| Input Voltage Range              |                                    | 0         | —       | $V_{DD}$ | V      |

| Input Capacitance                |                                    |           | 10      | _        | pF     |

| Power Specifications             |                                    |           |         |          |        |

| Power Supply Current             | Operating Mode, 100 ksps           |           | 0.45    | 1.0      | mA     |

| Power Supply Current in Shutdown |                                    |           | 0.1     | 1        | μA     |

| Power Supply Rejection           |                                    |           | ±0.3    |          | mV/V   |

| R/W                                                                                                                                                                                                                                                                                                                                                                     | R/W                                                    | R/W    | R/W  | R/W  | R/W    | R/W    | R/W    | Reset Value  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------|------|------|--------|--------|--------|--------------|

| ADCSC2                                                                                                                                                                                                                                                                                                                                                                  | ADCSC1                                                 | ADCSC0 | -    | -    | AMPGN2 | AMPGN1 | AMPGN0 | 01100000     |

| Bit7                                                                                                                                                                                                                                                                                                                                                                    | Bit6                                                   | Bit5   | Bit4 | Bit3 | Bit2   | Bit1   | Bit0   | SFR Address: |

|                                                                                                                                                                                                                                                                                                                                                                         |                                                        |        |      |      |        |        |        | 0xBC         |

| Bits7–5: ADCSC2–0: ADC SAR Conversion Clock Period Bits<br>000: SAR Conversion Clock = 1 System Clock<br>001: SAR Conversion Clock = 2 System Clocks<br>010: SAR Conversion Clock = 4 System Clocks<br>011: SAR Conversion Clock = 8 System Clocks<br>1xx: SAR Conversion Clock = 16 Systems Clocks<br>NOTE: SAR conversion clock should be less than or equal to 2MHz. |                                                        |        |      |      |        |        |        |              |

|                                                                                                                                                                                                                                                                                                                                                                         | UNUSED.                                                |        | ,    |      |        |        |        |              |

| DIG2 0.                                                                                                                                                                                                                                                                                                                                                                 | AMPGN2–0: ADC Internal Amplifier Gain<br>000: Gain = 1 |        |      |      |        |        |        |              |

|                                                                                                                                                                                                                                                                                                                                                                         | 001: Gain = 2                                          |        |      |      |        |        |        |              |

|                                                                                                                                                                                                                                                                                                                                                                         | 010: Gain :                                            | -      |      |      |        |        |        |              |

|                                                                                                                                                                                                                                                                                                                                                                         | 011: Gain = 10x: Gain =                                |        |      |      |        |        |        |              |

|                                                                                                                                                                                                                                                                                                                                                                         | 1x: Gain =                                             | -      |      |      |        |        |        |              |

|                                                                                                                                                                                                                                                                                                                                                                         |                                                        |        |      |      |        |        |        |              |

## SFR Definition 6.2. ADC0CF: ADC Configuration ('F220/1/6 and 'F206)

## 8. Comparators

The MCU has two on-board voltage comparators as shown in Figure 8.1. The inputs of each Comparator are available at the package pins. The output of each comparator is optionally available at port1 by configuring (see Section 14). When assigned to package pins, each comparator output can be programmed to operate in open drain or push-pull modes (see section 14.2).

The hysteresis of each comparator is software-programmable via its respective Comparator Control Register (CPT0CN, CPT1CN). The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive-going and negative-going symmetry of this hysteresis around the threshold voltage. The output of the comparator can be polled in software, or can be used as an interrupt source. Each comparator can be individually enabled or disabled (shutdown). When disabled, the comparator output (if assigned to a Port I/O pin via the Port1 MUX) defaults to the logic low state and its interrupt capability is suspended. Comparator inputs can be externally driven from -0.25 V to (V<sub>DD</sub>) + 0.25 V without damage or upset.

The Comparator 0 hysteresis is programmed using bits 3–0 in the Comparator 0 Control Register CPT0CN (shown in SFR Definition 8.1). The amount of negative hysteresis voltage is determined by the settings of the CP0HYN bits. As shown in Figure 8.2, settings of 10, 4 or 2 mV of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CP0HYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see Section 9.4). The CP0FIF flag is set upon a Comparator 0 falling-edge interrupt, and the CP0RIF flag is set upon the Comparator 0 rising-edge interrupt. Once set, these bits remain set until cleared by the user software. The Output State of Comparator 0 can be obtained at any time by reading the CP0OUT bit. Comparator 0 is enabled by setting the CP0EN bit, and is disabled by clearing this bit. Note there is a 20 mS power on time between setting CP0EN and the output stabilizing. Comparator 0 can also be programmed as a reset source. For details, see Section 11. The operation of Comparator 1 is identical to that of Comparator 0, except the Comparator 1 is controlled by the CPT1CN Register (SFR Definition 8.2). Also, Comparator 1 can not be programmed as a reset source. The complete electrical specifications for the Comparators are given in Table 8.1.

# Table 8.1. Comparator Electrical Characteristics $V_{DD}$ = 3.0 V, -40 to +85 ×C unless otherwise specified.

| Parameter                                         | Conditions                                | Min   | Тур      | Max                          | Units |

|---------------------------------------------------|-------------------------------------------|-------|----------|------------------------------|-------|

| Response Time1*                                   | (CP+) - (CP-) = 100 mV                    | _     | 4        | _                            | μs    |

| Response Time2*                                   | (CP+) - (CP-) = 10 mV                     | _     | 12       | —                            | μs    |

| Common Mode Rejection<br>Ratio                    |                                           | _     | 1.5      | 4                            | mV/V  |

| Positive Hysteresis1                              | CPnHYP1-0 = 00                            |       | 0        | 1                            | mV    |

| Positive Hysteresis2                              | CPnHYP1-0 = 01                            | 2     | 4.5      | 7                            | mV    |

| Positive Hysteresis3                              | CPnHYP1-0 = 10                            | 4     | 9        | 15                           | mV    |

| Positive Hysteresis4                              | CPnHYP1-0 = 11                            | 10    | 17       | 25                           | mV    |

| Negative Hysteresis1                              | CPnHYN1-0 = 00                            | —     | 0        | 1                            | mV    |

| Negative Hysteresis2                              | CPnHYN1-0 = 01                            | 2     | 4.5      | 7                            | mV    |

| Negative Hysteresis3                              | CPnHYN1-0 = 10                            | 4     | 9        | 15                           | mV    |

| Negative Hysteresis4                              | CPnHYN1-0 = 11                            | 10    | 17       | 25                           | mV    |

| Inverting or Non-inverting<br>Input Voltage Range |                                           | -0.25 |          | (V <sub>DD</sub> )<br>+ 0.25 | V     |

| Input Capacitance                                 |                                           | _     | 7        | —                            | pF    |

| Input Bias Current                                |                                           | -5    | 0.001    | +5                           | nA    |

| Input Offset Voltage                              |                                           | -10   | —        | +10                          | mV    |

| POWER SUPPLY                                      |                                           |       | 1        |                              |       |

| Power-up Time                                     | CPnEN from 0 to 1                         | _     | 20       | —                            | μs    |

| Power Supply Rejection                            |                                           | —     | 0.1      | 1                            | mV/V  |

| Supply Current                                    | Operating Mode<br>(each comparator) at DC | _     | 1.5      | 4                            | μΑ    |

| *Note: CPnHYP1-0 = CPnHYN                         | V1-0 = 00.                                | I     | <u>ı</u> |                              |       |

#### Notes on Registers, Operands and Addressing Modes:

Rn - Register R0-R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through register R0–R1

**rel -** 8-bit, signed (two's compliment) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00– 0x7F) or an SFR (0x80–0xFF).

#data - 8-bit constant

#data 16 - 16-bit constant

bit - Direct-addressed bit in Data RAM or SFR.

**addr 11 -** 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr 16 -** 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

#### 9.2.5. Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP, 0x81) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

The MCU also has built-in hardware for a stack record. The stack record is a 32-bit shift register, where each Push or increment SP pushes one record bit onto the register, and each Call pushes two record bits onto the register. (A Pop or decrement SP pops one record bit, and a Return pops two record bits, also.) The stack record circuitry can also detect an overflow or underflow on the 32-bit shift register, and can notify the emulator software even with the MCU running full-speed debug.

#### 9.3.1. Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should be set to logic 0. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the datasheet associated with their corresponding system function.

#### SFR Definition 9.1. SP: Stack Pointer

| R/W  | R/W                                       | R/W          | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value<br>00000111 |

|------|-------------------------------------------|--------------|------|------|------|------|------|-------------------------|

| Bit7 | Bit6                                      | Bit5         | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0x81    |

|      | SP: Stack F<br>The stack p<br>before ever | ointer holds |      |      |      |      |      | incremented             |

#### SFR Definition 9.2. DPL: Data Pointer Low Byte

| R/W       | R/W                                                                                                                                                  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value<br>00000111 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|-------------------------|

| Bit7      | Bit6                                                                                                                                                 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0x81    |

| Bits 7–0: | 0x81<br>Bits 7–0: DPL: Data Pointer Low.<br>The DPL register is the low byte of the 16-bit DPTR. DPTR is used to access indirectly<br>addressed RAM. |      |      |      |      |      |      |                         |

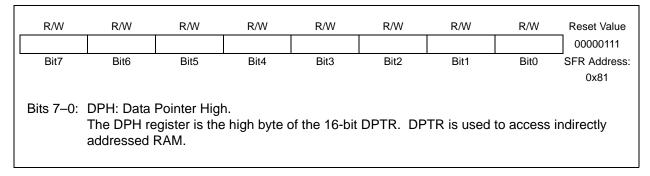

#### SFR Definition 9.3. DPH: Data Pointer High Byte

| R/W     | R/\                                                                                                                                                                                                                                                                                                                | N                                                                                                                                      | R/W   | R/W                       | R/W                              | R/W          | R/W          | R                            | Reset Value          |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------|----------------------------------|--------------|--------------|------------------------------|----------------------|

| CY      | A                                                                                                                                                                                                                                                                                                                  | C                                                                                                                                      | F0    | RS1                       | RS0                              | OV           | F1           | PARITY                       | 00000000             |

| Bit7    | Bit                                                                                                                                                                                                                                                                                                                | 6                                                                                                                                      | Bit5  | Bit4                      | Bit3                             | Bit2         | Bit1         | Bit0<br>(bit<br>addressable) | SFR Address:<br>0xD0 |

| Bit7:   | This b                                                                                                                                                                                                                                                                                                             |                                                                                                                                        |       |                           | etic operatio<br>all other aritl |              |              | ldition) or a                | borrow               |

| Bit6:   | AC: Auxiliary Carry Flag.<br>This bit is set when the last arithmetic operation results in a carry into (addition) or a borrow<br>from (subtraction) the high order nibble. It is cleared to 0 by all other arithmetic operations.                                                                                 |                                                                                                                                        |       |                           |                                  |              |              |                              |                      |

| Bit5:   |                                                                                                                                                                                                                                                                                                                    | er Flag 0<br>a bit-add                                                                                                                 |       | le, general-              | purpose flag                     | for use ur   | nder softwar | e control.                   |                      |

| Bits4–3 |                                                                                                                                                                                                                                                                                                                    |                                                                                                                                        |       | nk Select.<br>register ba | ank is used o                    | luring regis | ster accesse | es.                          |                      |

|         | RS1                                                                                                                                                                                                                                                                                                                | RS0                                                                                                                                    | Regis | ster Bank                 | Address                          |              |              |                              |                      |

|         | 0                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                      |       | 0                         | 0x00–0x0                         | 7            |              |                              |                      |

|         | 0                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                      |       | 1                         | 0x08–0x0                         | F            |              |                              |                      |

|         | 1                                                                                                                                                                                                                                                                                                                  | 0                                                                                                                                      |       | 2                         | 0x10–0x1                         | 7            |              |                              |                      |

|         | 1                                                                                                                                                                                                                                                                                                                  | 1                                                                                                                                      |       | 3                         | 0x18–0x1                         | F            |              |                              |                      |

| Bit2:   | <ul> <li>Note: Any instruction which changes the RS1–RS0 bits must not be immediately followed by the "MOV Rn, A" instruction.</li> <li>Bit2: OV: Overflow Flag.<br/>This bit is set to 1 under the following circumstances:</li> <li>•An ADD, ADDC, or SUBB instruction causes a sign-change overflow.</li> </ul> |                                                                                                                                        |       |                           |                                  |              |              |                              |                      |

|         | <ul> <li>A MUL instruction results in an overflow (result is greater than 255).</li> <li>A DIV instruction causes a divide-by-zero condition.<br/>The OV bit is cleared to 0 by the ADD, ADDC, SUBB, MUL, and DIV instructions in all other cases.</li> </ul>                                                      |                                                                                                                                        |       |                           |                                  |              |              |                              |                      |

| Bit1:   |                                                                                                                                                                                                                                                                                                                    | F1: User Flag 1.<br>This is a bit-addressable, general purpose flag for use under software control.                                    |       |                           |                                  |              |              |                              |                      |

| Bit0:   | This b                                                                                                                                                                                                                                                                                                             | PARITY: Parity Flag.<br>This bit is set to 1 if the sum of the eight bits in the accumulator is odd and cleared if the sum<br>is even. |       |                           |                                  |              |              |                              |                      |

# C8051F2xx

#### 9.4. Interrupt Handler

The CIP-51 includes an extended interrupt system supporting up to 22 interrupt sources with two priority levels. The allocation of interrupt sources between on-chip peripherals and external inputs pins varies according to the specific version of the device. Each interrupt source has one or more associated interrupt-pending flag(s) located in an SFR. When a peripheral or external source meets a valid interrupt condition, the associated interrupt-pending flag is set to logic 1.

If interrupts are enabled for the source, an interrupt request is generated when the interrupt-pending flag is set. As soon as execution of the current instruction is complete, the CPU generates an LCALL to a predetermined address to begin execution of an interrupt service routine (ISR). Each ISR must end with an RETI instruction, which returns program execution to the next instruction that would have been executed if the interrupt request had not occurred. If interrupts are not enabled, the interrupt-pending flag is ignored by the hardware and program execution continues as normal. (The interrupt-pending flag is set to logic 1 regardless of the interrupt's enable/disable state.)

Each interrupt source can be individually enabled or disabled through the use of an associated interrupt enable bit in an SFR (IE–EIE2). However, interrupts must first be globally enabled by setting the EA bit (IE.7) to logic 1 before the individual interrupt enables are recognized. Setting the EA bit to logic 0 disables all interrupt sources regardless of the individual interrupt-enable settings.

Some interrupt-pending flags are automatically cleared by the hardware when the CPU vectors to the ISR. However, most are not cleared by the hardware and must be cleared by software before returning from the ISR. If an interrupt-pending flag remains set after the CPU completes the return-from-interrupt (RETI) instruction, a new interrupt request will be generated immediately and the CPU will re-enter the ISR after the completion of the next instruction.

#### 9.4.1. MCU Interrupt Sources and Vectors

The MCU allocates 9 interrupt sources to on-chip peripherals. Software can simulate an interrupt by setting any interrupt-pending flag to logic 1. If interrupts are enabled for the flag, an interrupt request will be generated and the CPU will vector to the ISR address associated with the interrupt-pending flag. The MCU interrupt sources, associated vector addresses, priority order and control bits are summarized in Table 9.4. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

#### 9.4.2. External Interrupts

The two external interrupt sources (/INT0 and /INT1) are configurable as active-low level-sensitive or active-low edge-sensitive inputs depending on the setting of IT0 (TCON.0) and IT1 (TCON.2). IE0 (TCON.1) and IE1 (TCON.3) serve as the interrupt-pending flag for the /INT0 and /INT1 external interrupts, respectively. If an /INT0 or /INT1 external interrupt is configured as edge-sensitive, the corresponding interrupt-pending flag is automatically cleared by the hardware when the CPU vectors to the ISR. When configured as level sensitive, the interrupt-pending flag follows the state of the external interrupt's input pin. The external interrupt source must hold the input active until the interrupt request is recognized. It must then deactivate the interrupt request before execution of the ISR completes or another interrupt request will be generated.

#### 9.4.3. Software Controlled Interrupts

The C8051F2xx family of devices features four Software Controlled Interrupts controlled by flags located in the Software Controlled Interrupt Flag Register (SWCINT). See SFR Definition 9.7. When a logic '1' is written to a Software-Controlled Interrupt Flag, the CIP-51 will jump to an associated interrupt service vector (see Table 9.4, "Interrupt Summary," on page 75). These interrupt flags must be cleared by software.

#### 12.4. External Reset

The external RST pin provides a means for external circuitry to force the CIP-51 into a reset state. Asserting an active-low signal on the RST pin will cause the CIP-51 to enter the reset state. Although there is a weak pull-up, it may be desirable to provide an external pull-up and/or decoupling of the RST pin to avoid erroneous noise-induced resets. The CIP-51 will remain in reset until at least 12 clock cycles after the active-low RST signal is removed. The PINRSF flag (RSTSRC.0) is set on exit from an external reset. The RST pin is 5 V tolerant.

#### 12.5. Missing Clock Detector Reset

The Missing Clock Detector is essentially a one-shot circuit that is triggered by the MCU system clock. If the system clock goes away for more than 100msec, the one-shot will time out and generate a reset. After a Missing Clock Detector reset, the MCDRSF flag (RSTSRC.2) will be set, signifying the MSD as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset. Setting the MSCLKE bit in the OSCICN register (see SFR Definition 13.1) enables the Missing Clock Detector.

#### 12.6. Comparator 0 Reset

Comparator 0 can be configured as a reset input by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator 0 should be enabled using CPT0CN.7 (see SFR Definition 8.1) prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. When configured as a reset, if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0–), the MCU is put into the reset state. After a Comparator 0 Reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator 0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

#### 12.7. Watchdog Timer Reset

The MCU includes a programmable Watchdog Timer (WDT) running off the system clock. The WDT will force the MCU into the reset state when the watchdog timer overflows. To prevent the reset, the WDT must be restarted by application software before the overflow occurs. If the system experiences a software/hardware malfunction preventing the software from restarting the WDT, the WDT will overflow and cause a reset. This should prevent the system from running out of control.

The WDT is automatically enabled and started with the default maximum time interval on exit from all resets. If desired, the WDT can be disabled by system software or locked 'on' to prevent accidental disabling. Once locked, the WDT cannot be disabled until the next system reset. The state of the RST pin is unaffected by this reset.

#### 12.7.1. Watchdog Usage

The WDT consists of a 21-bit timer running from the programmed system clock. The timer measures the period between specific writes to its control register. If this period exceeds the programmed limit, a WDT reset is generated. The WDT can be enabled and disabled as needed in software, or can be permanently enabled if desired. Watchdog features are controlled via the Watchdog Timer Control Register (WDTCN) shown in SFR Definition 12.1.

#### Enable/Reset WDT

The watchdog timer is both enabled and reset by writing 0xA5 to the WDTCN register. The user's application software should include periodic writes of 0xA5 to WDTCN as needed to prevent a watchdog timer overflow. The WDT is enabled and reset as a result of any system reset.

| SFR Definition 13.2 | . OSCXCN: External | <b>Oscillator Control</b> |

|---------------------|--------------------|---------------------------|

|---------------------|--------------------|---------------------------|

| R        | R/W                                                                                                                                                                                                                                                                                                                                                                          | R/W                                                          | R/W         | R/W          | R/W          | R/W     | R/W             | Reset Value  |  |  |  |  |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------|--------------|--------------|---------|-----------------|--------------|--|--|--|--|--|

| XTLVLD   |                                                                                                                                                                                                                                                                                                                                                                              |                                                              |             |              | XFCN2        | XFCN1   | XFCN0           | 00110000     |  |  |  |  |  |

| Bit7     | Bit6                                                                                                                                                                                                                                                                                                                                                                         |                                                              | Bit4        | Bit3         | Bit2         | Bit1    | Bit0            | SFR Address: |  |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                              |                                                              |             |              |              |         |                 | 0xB1         |  |  |  |  |  |

| Bit7:    | XTLVLD: Crystal Oscillator Valid Flag<br>(Valid only when XOSCMD = 1xx.)<br>0: Crystal Oscillator is unused or not yet stable<br>1: Crystal Oscillator is running and stable                                                                                                                                                                                                 |                                                              |             |              |              |         |                 |              |  |  |  |  |  |

| Bits6–4: | <ul> <li>Bits6–4: XOSCMD2–0: External Oscillator Mode Bits</li> <li>00x: Off. XTAL1 pin is grounded internally.</li> <li>010: System Clock from External CMOS Clock on XTAL1 pin.</li> <li>011: System Clock from External CMOS Clock on XTAL1 pin divided by 2.</li> <li>10x: RC/C Oscillator Mode with divide by 2 stage.</li> <li>110: Crystal Oscillator Mode</li> </ul> |                                                              |             |              |              |         |                 |              |  |  |  |  |  |

| Bit3:    | RESER                                                                                                                                                                                                                                                                                                                                                                        | ystal Oscillator N<br>VED. Read = u                          | ndefined, W | rite = don't | care         |         |                 |              |  |  |  |  |  |

| Bits2–0: |                                                                                                                                                                                                                                                                                                                                                                              | <ul><li>-0: External Osc</li><li>1: see table belo</li></ul> | •           | iency Cont   | rol Bits     |         |                 |              |  |  |  |  |  |

|          | XFCN                                                                                                                                                                                                                                                                                                                                                                         | Crystal (XOSC                                                | MD = 11x)   | RC (XO       | SCMD = 10    | x) C (X | OSCMD =         | 10x)         |  |  |  |  |  |

|          | 000                                                                                                                                                                                                                                                                                                                                                                          | f ≤ 12.5                                                     | kHz         | f≤           | 25 kHz       | K       | K Factor = 0.44 |              |  |  |  |  |  |

|          | 001                                                                                                                                                                                                                                                                                                                                                                          | 12.5 kHz < f ≤                                               | 30.3 kHz    | 25 kHz       | < f ≤ 50 kH  | z K     | K Factor = 1.4  |              |  |  |  |  |  |

|          | 010                                                                                                                                                                                                                                                                                                                                                                          | 30.35 kHz < f                                                | ≤ 93.8 kHz  | 50 kHz       | < f ≤ 100 kł | lz K    | Factor = 4      | .4           |  |  |  |  |  |

|          | 011                                                                                                                                                                                                                                                                                                                                                                          | 93.8 kHz < f ≤                                               | 26 7kHz     | 100 kHz      | < f ≤ 200 k  | Hz K    | Factor = 1      | 13           |  |  |  |  |  |

|          | 100                                                                                                                                                                                                                                                                                                                                                                          | 267 kHz < f ≤                                                | 722 kHz     | 200 kHz      | < f ≤ 400 k  | Hz K    | Factor = 3      | 38           |  |  |  |  |  |

|          | 101                                                                                                                                                                                                                                                                                                                                                                          | 722 kHz < f ≤                                                | 2.23 MHz    | 400 kHz      | < f ≤ 800 k  | Hz K    | Factor = 1      | 00           |  |  |  |  |  |

|          | 110                                                                                                                                                                                                                                                                                                                                                                          | 2.23 MHz < f ≤                                               | 6.74 MHz    | 800 kHz      | < f ≤ 1.6 M  | Hz K    | Factor = 4      | 20           |  |  |  |  |  |

|          | 111                                                                                                                                                                                                                                                                                                                                                                          | f > 6.74                                                     | MHz         | 1.6 MHz      | < f ≤ 3.2 M  | Hz K I  | Factor = 14     | 400          |  |  |  |  |  |

|          | Choose                                                                                                                                                                                                                                                                                                                                                                       | (Circuit from Fig<br>XFCN value to<br>t from Figure 13       | match the c | rystal frequ | iency.       | 1x)     |                 |              |  |  |  |  |  |

|          | •                                                                                                                                                                                                                                                                                                                                                                            | oscillation frequ                                            | •           |              | - 107)       |         |                 |              |  |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                              | (10 <sup>3</sup> ) / (R x C), \                              |             |              |              |         |                 |              |  |  |  |  |  |

|          | f = frequ                                                                                                                                                                                                                                                                                                                                                                    | ency of oscillati                                            | on in MHz   |              |              |         |                 |              |  |  |  |  |  |

|          |                                                                                                                                                                                                                                                                                                                                                                              | acitor value in p                                            |             |              |              |         |                 |              |  |  |  |  |  |

|          | K = Pul                                                                                                                                                                                                                                                                                                                                                                      | -up resistor valu                                            | e in kΩ     |              |              |         |                 |              |  |  |  |  |  |

| C MODE   | C MODE (Circuit from Figure 13.1, Option 3; XOSCMD = 10x)<br>Choose K Factor (KF) for the oscillation frequency desired:<br>f = KF / (C x AV+), where<br>f = frequency of oscillation in MHz<br>C = capacitor value on XTAL1, XTAL2 pins in pF<br>V <sub>DD</sub> = Power supply voltage on MCU in volts                                                                     |                                                              |             |              |              |         |                 |              |  |  |  |  |  |

|          | v <sub>DD</sub> = r                                                                                                                                                                                                                                                                                                                                                          |                                                              | age on MC   |              |              |         |                 |              |  |  |  |  |  |

#### 14.2. General Purpose Port I/O

Each I/O port is accessed through a corresponding special function register (SFR) that is both byte addressable and bit addressable. When writing to a port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the port's input pins are returned regardless of the PRTnMX settings (i.e., even when the pin is assigned to another signal by the MUX, the Port Register can always still read its corresponding Port I/O pin), provided its pin is configured for digital input mode. The exception to this is the execution of the *read-modify-write* instructions. The *read-modify-write* instructions when operating on a port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a port SFR. For these instructions, the value of the register (not the pin) is read, modified, and written back to the SFR.

| R/W      | R/W                                      | R/W                                                     | R/W                           | R/W                                   | R/W         | R/W       | R/W  | Reset Value  |  |  |  |

|----------|------------------------------------------|---------------------------------------------------------|-------------------------------|---------------------------------------|-------------|-----------|------|--------------|--|--|--|

| P0.7     | P0.6                                     | P0.5                                                    | P0.4                          | P0.3                                  | P0.2        | P0.1      | P0.0 | 11111111     |  |  |  |

| Bit7     | Bit6                                     | Bit5                                                    | Bit4                          | Bit3                                  | Bit2        | Bit1      | Bit0 | SFR Address: |  |  |  |

|          |                                          | (bit addressable) 0x                                    |                               |                                       |             |           |      |              |  |  |  |

| Bits7–0: | (Write - Ou<br>0: Logic Lo<br>1: Logic H | ow Output.<br>igh Output<br>gardless o<br>n is logic lo | (high impe<br>f PRT0MX,<br>w. | ins per PRT<br>dance if co<br>PRT1MX, | rresponding | g PRT0CF. |      | sters)       |  |  |  |

#### SFR Definition 14.4. P0: Port0 Register

### SFR Definition 14.5. PRT0CF: Port0 Configuration Register

| R/W      | R/W         | R/W          | R/W          | R/W          | R/W          | R/W          | R/W  | Reset Value |

|----------|-------------|--------------|--------------|--------------|--------------|--------------|------|-------------|

|          |             |              |              |              |              |              |      | 00000000    |

| Bit7     | Bit6        | Bit5         | Bit4         | Bit3         | Bit2         | Bit1         | Bit0 | SFR Address |

|          |             |              |              |              |              |              |      | 0xA4        |

| Bits7–0: | PRT0CF.[7:  | 0]: Output ( | Configuratio | n Bits for P | ).7–P0.0 (re | espectively) |      |             |

|          | 0: Correspo |              | •            |              | · ·          | , <b>,</b> , |      |             |

|          | •           |              |              | de is Push-  | <b>.</b>     |              |      |             |

#### SFR Definition 14.12. P2MODE: Port2 Digital/Analog Input Mode

| R/W                                                                                                                                                                                          | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--------------|--|--|

|                                                                                                                                                                                              |      |      |      |      |      |      |      | 11111111     |  |  |

| Bit7                                                                                                                                                                                         | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |  |  |

|                                                                                                                                                                                              |      |      |      |      |      |      |      | 0xF3         |  |  |

| 0xF3<br>Bits7–0: Port2 Digital/Analog Output Mode<br>0: Corresponding Port2 pin Digital Input disabled. (For analog use, i.e., ADC).<br>1: Corresponding Port2 pin Digital Input is enabled. |      |      |      |      |      |      |      |              |  |  |

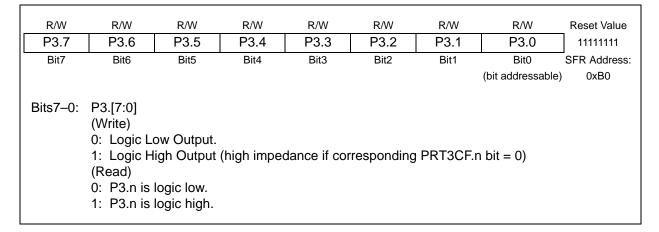

#### SFR Definition 14.13. P3: Port3 Register\*

#### SFR Definition 14.14. PRT3CF: Port3 Configuration Register\*

| R/W      | R/W                                      | R/W         | R/W         | R/W         | R/W    | R/W          | R/W  | Reset Value<br>00000000 |

|----------|------------------------------------------|-------------|-------------|-------------|--------|--------------|------|-------------------------|

| Bit7     | Bit6                                     | Bit5        | Bit4        | Bit3        | Bit2   | Bit1         | Bit0 | SFR Address:<br>0xA7    |

| Bits7–0: | PRT3CF.[7:<br>0: Correspo<br>1: Correspo | onding P3.r | n Output Mo | ode is Open | Drain. | espectively) |      |                         |

#### SFR Definition 16.2. SCON: Serial Port Control

| R/W    | R/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | W                                                                         | R/W                                                                                    | R/W                                                                                    | R/W                                                             | R/W                                           | R/W                           | R/W                                              | Reset Value            |  |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------|-------------------------------|--------------------------------------------------|------------------------|--|--|

| SMC    | ) SN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | И1                                                                        | SM2 RE                                                                                 |                                                                                        | TB8                                                             | RB8                                           | TI                            | RI                                               | 00000000               |  |  |