# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SPI, UART/USART                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                |

| Number of I/O              | 32                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 × 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 32x8b                                                       |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-TQFP                                                         |

| Supplier Device Package    | 48-TQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f220-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1. | System Overview                            | 11 |

|----|--------------------------------------------|----|

|    | 1.1. CIP-51TM Microcontroller Core         | 15 |

|    | 1.1.1. Fully 8051 Compatible               | 15 |

|    | 1.1.2. Improved Throughput                 | 15 |

|    | 1.1.3. Additional Features                 |    |

|    | 1.2. On-Board Memory                       | 17 |

|    | 1.3. JTAG                                  | 18 |

|    | 1.4. Digital/Analog Configurable I/O       | 19 |

|    | 1.5. Serial Ports                          | 20 |

|    | 1.6. Analog to Digital Converter           | 20 |

|    | 1.7. Comparators                           |    |

| 2. | Absolute Maximum Ratings                   | 23 |

| 3. | Global DC Electrical Characteristics       | 24 |

| 4. | Pinout and Package Definitions             | 25 |

| 5. | ADC (8-Bit, C8051F220/1/6 Only)            | 32 |

|    | 5.1. Analog Multiplexer and PGA            | 32 |

|    | 5.2. ADC Modes of Operation                |    |

|    | 5.3. ADC Programmable Window Detector      |    |

| 6. | ADC (12-Bit, C8051F206 Only)               |    |

|    | 6.1. Analog Multiplexer and PGA            |    |

|    | 6.2. ADC Modes of Operation                | 41 |

|    | 6.3. ADC Programmable Window Detector      | 46 |

| 7. | Voltage Reference (C8051F206/220/221/226)  |    |

| 8. |                                            |    |

| 9. | CIP-51 Microcontroller                     |    |

|    | 9.1. Instruction Set                       |    |

|    | 9.1.1. Instruction and CPU Timing          |    |

|    | 9.1.2. MOVX Instruction and Program Memory |    |

|    | 9.2. Memory Organization                   |    |

|    | 9.2.1. Program Memory                      |    |

|    | 9.2.2. Data Memory                         |    |

|    | 9.2.3. General Purpose Registers           |    |

|    | 9.2.4. Bit Addressable Locations           |    |

|    | 9.2.5. Stack                               |    |

|    | 9.3. Special Function Registers            |    |

|    | 9.3.1. Register Descriptions               |    |

|    | 9.4. Interrupt Handler                     |    |

|    | 9.4.1. MCU Interrupt Sources and Vectors   |    |

|    | 9.4.2. External Interrupts                 |    |

|    | 9.4.3. Software Controlled Interrupts      |    |

|    | 9.4.4. Interrupt Priorities                |    |

|    | 9.4.5. Interrupt Latency                   |    |

|    | 9.4.6. Interrupt Register Descriptions     | 17 |

## C8051F2xx

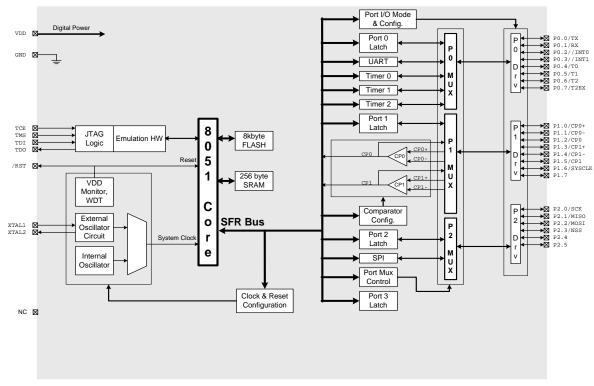

Figure 1.4. C8051F231 Block Diagram (32 LQFP)

### 1.1. CIP-51<sup>TM</sup> Microcontroller Core

#### 1.1.1. Fully 8051 Compatible

The C8051F206, C8051F220/1/6 and C8051F230/1/6 utilize Silcon Labs' proprietary CIP-51 microcontroller core. The CIP-51 is fully compatible with the MCS-51<sup>TM</sup> instruction set. Standard 803x/805x assemblers and compilers can be used to develop software. The core contains the peripherals included with a standard 8052, including three 16-bit counter/timers, a full-duplex UART, 256 bytes of internal RAM, an optional 1024 bytes of XRAM, 128 byte Special Function Register (SFR) address space, and four bytewide I/O Ports.

#### 1.1.2. Improved Throughput

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute with a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with only four instructions taking more than four system clock cycles.

The CIP-51 has a total of 109 instructions. The number of instructions versus the system clock cycles to execute them is as follows:

| Instructions      | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

|-------------------|----|----|-----|----|-----|---|-----|---|---|

| Clocks to Execute | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

### 2. Absolute Maximum Ratings

### Table 2.1. Absolute Maximum Ratings<sup>\*</sup>

| Parameter                                                                                                                                                                                                                                                                                                                                                                                              | Conditions | Min  | Тур | Max                      | Units |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|-----|--------------------------|-------|--|--|--|--|

| Ambient Temperature under Bias                                                                                                                                                                                                                                                                                                                                                                         |            | -55  |     | 125                      | °C    |  |  |  |  |

| Storage Temperature                                                                                                                                                                                                                                                                                                                                                                                    |            | -65  |     | 150                      | °C    |  |  |  |  |

| Voltage on any Pin (except V <sub>DD</sub> and Port I/O) with respect to DGND                                                                                                                                                                                                                                                                                                                          |            | -0.3 | _   | V <sub>DD</sub> +<br>0.3 | V     |  |  |  |  |

| Voltage on any Port I/O Pin or RST pins with respect to DGND                                                                                                                                                                                                                                                                                                                                           |            | -0.3 | —   | 5.8                      | V     |  |  |  |  |

| Voltage on V <sub>DD</sub> with respect to DGND                                                                                                                                                                                                                                                                                                                                                        |            | -0.3 |     | 4.2                      | V     |  |  |  |  |

| Total Power Dissipation                                                                                                                                                                                                                                                                                                                                                                                |            | —    | 1.0 | 800                      | W     |  |  |  |  |

| Maximum Output Current Sunk by any Port pin                                                                                                                                                                                                                                                                                                                                                            |            | —    | _   | 200                      | mA    |  |  |  |  |

| Maximum Output Current Sunk by any other I/O pin                                                                                                                                                                                                                                                                                                                                                       |            | —    |     | 25                       | mA    |  |  |  |  |

| Maximum Output Current Sourced by any Port pin                                                                                                                                                                                                                                                                                                                                                         |            | —    |     | 200                      | mA    |  |  |  |  |

| Maximum Output Current Sourced by any other I/O pin                                                                                                                                                                                                                                                                                                                                                    |            | —    |     | 25                       | mA    |  |  |  |  |

| *Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.<br>This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. |            |      |     |                          |       |  |  |  |  |

| Name | <sup>6</sup> F206,<br>F220,<br>226,<br>230,<br>236 | ʻF221,<br>231 | Туре  | Description                                                   |

|------|----------------------------------------------------|---------------|-------|---------------------------------------------------------------|

|      | 48-Pin                                             | 32-Pin        |       |                                                               |

| P2.7 | 18                                                 |               | D I/O | Port2 Bit7. (See the Port I/O Sub-System section for complete |

|      |                                                    |               | A In  | description).                                                 |

| P3.0 | 44                                                 |               | D I/O | Port3 Bit0. (See the Port I/O Sub-System section for complete |

|      |                                                    |               | A In  | description).                                                 |

| P3.1 | 43                                                 |               | D I/O | Port3 Bit1. (See the Port I/O Sub-System section for complete |

|      |                                                    |               | A In  | description).                                                 |

| P3.2 | 42                                                 |               | D I/O | Port3 Bit2. (See the Port I/O Sub-System section for complete |

|      |                                                    |               | A In  | description).                                                 |

| P3.3 | 41                                                 |               | D I/O | Port3 Bit3. (See the Port I/O Sub-System section for complete |

|      |                                                    |               | A In  | description).                                                 |

| P3.4 | 30                                                 |               | D I/O | Port3 Bit4. (See the Port I/O Sub-System section for complete |

|      |                                                    |               | A In  | description).                                                 |

| P3.5 | 29                                                 |               | D I/O | Port3 Bit5. (See the Port I/O Sub-System section for complete |

|      |                                                    |               | A In  | description).                                                 |

| P3.6 | 20                                                 |               | D I/O | Port3 Bit6. (See the Port I/O Sub-System section for complete |

|      |                                                    |               | A In  | description).                                                 |

| P3.7 | 19                                                 |               | D I/O | Port3 Bit7. (See the Port I/O Sub-System section for complete |

|      |                                                    |               | A In  | description).                                                 |

Table 4.1. Pin Definitions (Continued)

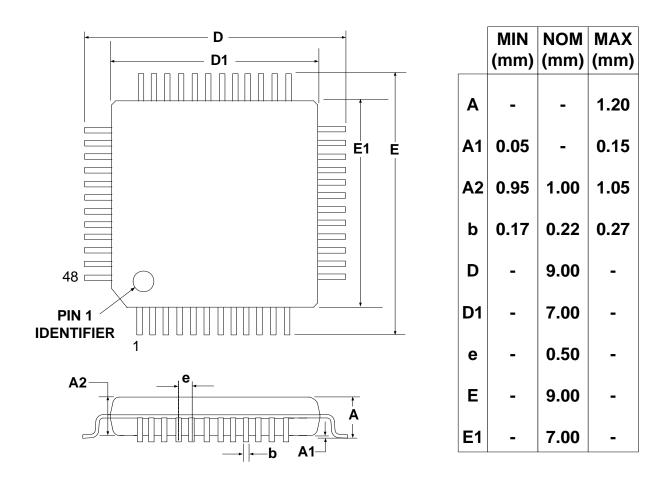

# C8051F2xx

Figure 4.3. TQFP-48 Package Drawing

| R/W<br>MSB                            | R/W    | R/W        | R/W    | R/W  | R/W  | R/W  | R/W<br>LSB | Reset Value<br>00000000 |  |  |  |  |

|---------------------------------------|--------|------------|--------|------|------|------|------------|-------------------------|--|--|--|--|

| Bit7                                  | Bit6   | Bit5       | Bit4   | Bit3 | Bit2 | Bit1 | Bit0       | SFR Address:<br>0xBF    |  |  |  |  |

| Bits7–0: ADC Data Word Bits           |        |            |        |      |      |      |            |                         |  |  |  |  |

| EXAMPLE: ADC Data Word Conversion Map |        |            |        |      |      |      |            |                         |  |  |  |  |

|                                       | A      | AIN – GND( | Volts) |      | ADC  |      |            |                         |  |  |  |  |

|                                       |        | REF x (255 | /256)  |      | 0xF  | F    |            |                         |  |  |  |  |

|                                       |        | REF x 2    | /2     |      | 0x8  | 30   |            |                         |  |  |  |  |

|                                       |        | REF x (127 | /256)  |      | 0x7F |      |            |                         |  |  |  |  |

|                                       | 0 0x00 |            |        |      |      |      |            |                         |  |  |  |  |

|                                       | L      |            |        |      |      |      |            |                         |  |  |  |  |

### SFR Definition 5.4. ADC0H: ADC Data Word ('F220/1/6 and 'F206)

#### 5.3. ADC Programmable Window Detector

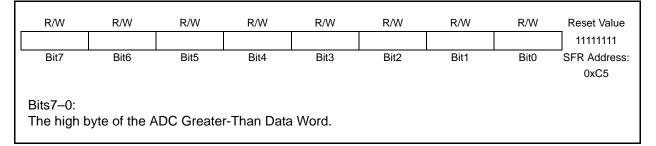

The ADC programmable window detector is very useful in many applications. It continuously compares the ADC output to user-programmed limits and notifies the system when an out-of-band condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (ADWINT in ADCOCN) can also be used in polled mode. The high and low bytes of the reference words are loaded into the ADC Greater-Than and ADC Less-Than registers (ADC0GTH and ADC0LTH).

#### SFR Definition 5.5. ADC0GTH: ADC Greater-Than Data ('F220/1/6 and 'F206)

### SFR Definition 5.6. ADC0LTH: ADC Less-Than Data Byte ('F220/1/6 and 'F206)

| R/W                            | R/W  | R/W  | R/W                | R/W  | R/W  | R/W  | R/W  | Reset Value<br>00000000 |

|--------------------------------|------|------|--------------------|------|------|------|------|-------------------------|

| Bit7<br>Bits7–0:<br>The high b | Bit6 | Bit5 | Bit4<br>Han Data W | Bit3 | Bit2 | Bit1 | BitO | SFR Address:<br>0xC7    |

### Table 5.1. 8-Bit ADC Electrical Characteristics

VDD = 3.0 V, VREF = 2.40 V, PGA Gain = 1, -40 to +85 ×C unless otherwise specified.

| Parameter                        | Conditions                         | Min       | Тур     | Max      | Units  |

|----------------------------------|------------------------------------|-----------|---------|----------|--------|

| DC Accuracy                      |                                    | •         |         |          | •      |

| Resolution                       |                                    |           | 8       | —        | bits   |

| Integral Nonlinearity            |                                    |           | —       | ±1/2     | LSB    |

| Differential Nonlinearity        | Guaranteed Monotonic               | _         | —       | ±1/2     | LSB    |

| Offset Error                     |                                    | ±2        | —       | ±1/2     | LSB    |

| Gain Error                       |                                    | ±2        | —       | ±1/2     | LSB    |

| Offset Temperature Coefficient   |                                    |           | ±0.25   | _        | ppm/°C |

| Dynamic Performance (10 kHz sine | wave input, 0 to –1 dB of full     | scale, 10 | 0 ksps) |          |        |

| Signal-to-Noise Plus Distortion  |                                    | 49.5      | —       | _        | dB     |

| Total Harmonic Distortion        | Up to the 5 <sup>th</sup> harmonic | -60       | -65     | _        | dB     |

| Spurious-Free Dynamic Range      |                                    |           | -65     | _        | dB     |

| Conversion Rate                  |                                    | •         |         |          | •      |

| Conversion Time in SAR Clocks    |                                    | 16        | —       | —        | clocks |

| SAR Clock Frequency              |                                    |           | —       | 2.5      | MHz    |

| Track/Hold Acquisition Time      |                                    | 1.5       | —       | _        | μs     |

| Throughput Rate                  |                                    | _         | —       | 100      | ksps   |

| Analog Inputs                    | ·                                  |           |         |          |        |

| Input Voltage Range              |                                    | 0         | —       | $V_{DD}$ | V      |

| Input Capacitance                |                                    |           | 10      | _        | pF     |

| Power Specifications             |                                    |           |         |          |        |

| Power Supply Current             | Operating Mode, 100 ksps           |           | 0.45    | 1.0      | mA     |

| Power Supply Current in Shutdown |                                    |           | 0.1     | 1        | μA     |

| Power Supply Rejection           |                                    |           | ±0.3    |          | mV/V   |

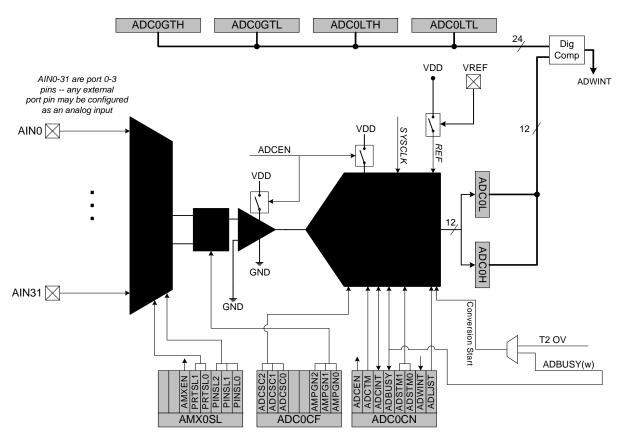

### 6. ADC (12-Bit, C8051F206 Only)

#### Description

The ADC subsystem for the C8051F206 consists of configurable analog multiplexer (AMUX), a programmable gain amplifier (PGA), and a 100ksps, 12-bit successive-approximation-register ADC with integrated track-and-hold and programmable window detector (see Figure 6.1). The AMUX, PGA, Data Conversion Modes, and Window Detector are all configurable under software control via the Special Function Register's shown in Figure 6.1. The ADC subsystem (ADC, track-and-hold and PGA) is enabled only when the ADCEN bit in the ADC Control register (ADC0CN, Figure 6.5) is set to 1. The ADC subsystem is in low power shutdown when this bit is 0.

Figure 6.1. 12-Bit ADC Functional Block Diagram

#### 6.1. Analog Multiplexer and PGA

Any external port pin (ports 0-3) may be selected via software. The AMX0SL SFR is used to select the desired analog input pin. (See SFR Definition 5.1). When the AMUX is enabled, the user selects which port is to be used (bits PRTSL0–1), and then the pin in the selected port (bits PINSL0–2) to be the analog input.

The PGA amplifies the AMUX output signal by an amount determined by the states of the AMPGN2–0 bits in the ADC Configuration register, ADC0CF (SFR Definition 5.2). The PGA can be software-programmed for gains of 0.5, 1, 2, 4, 8 or 16. It defaults to a gain of 1 on reset.

| Interrupt Source                | Interrupt<br>Vector | Priority<br>Order | Interrupt-Pending Flag | Enable            |

|---------------------------------|---------------------|-------------------|------------------------|-------------------|

| ADC0 End of Conversion          | 0x007B              | 15                | ADCINT (ADC0CN.5)      | EADC0 (EIE2.1)    |

| Software Controlled Interrupt 0 | 0x0083              | 16                | SCI0 (SWCINT.4)        | ESCI0 (EIE2.2)    |

| Software Controlled Interrupt 1 | 0x008B              | 17                | SCI1 (SWCINT.5)        | ESCI1 (EIE2.3)    |

| Software Controlled Interrupt 2 | 0x0093              | 18                | SCI2 (SWCINT.6)        | ESCI2 (EIE2.4)    |

| Software Controlled Interrupt 3 | 0x009B              | 19                | SCI3 (SWCINT.7)        | ESCI3 (EIE2.5)    |

| Unused Interrupt Location       | 0x00A3              | 20                | None                   | Reserved (EIE2.6) |

| External Crystal OSC Ready      | 0x00AB              | 21                | XTLVLD (OSCXCN.7)      | EXVLD (EIE2.7)    |

Table 9.4. Interrupt Summary (Continued)

#### 9.4.4. Interrupt Priorities

Each interrupt source can be individually programmed to one of two priority levels: low or high. A low priority interrupt service routine can be preempted by a high priority interrupt. A high priority interrupt cannot be preempted. Each interrupt has an associated interrupt priority bit in an SFR (IP–EIP2) used to configure its priority level. Low priority is the default. If two interrupts are recognized simultaneously, the interrupt with the higher priority is serviced first. If both interrupts have the same priority level, a fixed priority order is used to arbitrate.

#### 9.4.5. Interrupt Latency

Interrupt response time depends on the state of the CPU when the interrupt occurs. Pending interrupts are sampled and priority decoded each system clock cycle. Therefore, the fastest possible response time is 5 system clock cycles: 1 clock cycle to detect the interrupt and 4 clock cycles to complete the LCALL to the ISR. If an interrupt is pending when a RETI is executed, a single instruction is executed before an LCALL is made to service the pending interrupt. Therefore, the maximum response time for an interrupt (when no other interrupt is currently being serviced or the new interrupt is of greater priority) occurs when the CPU is performing an RETI instruction followed by a DIV as the next instruction. In this case, the response time is 18 system clock cycles: 1 clock cycle to detect the interrupt, 5 clock cycles to execute the RETI, 8 clock cycles to complete the DIV instruction and 4 clock cycles to execute the LCALL to the ISR. NOTE: If a Flash write or erase is performed, the MCU is stalled during the operation and interrupts will not be serviced until the operation is complete. If the CPU is executing an ISR for an interrupt with equal or higher priority, the new interrupt will not be serviced until the current ISR completes, including the RETI and following instruction.

### 11. On-Chip XRAM (C8051F206/226/236)

The C8051F206/226/236 features 1024 Bytes of RAM mapped into the external data memory space. All address locations may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using indirect MOVX addressing mode. If the MOVX instruction is used with an 8-bit operand (such as @R1), then the high byte is the External Memory Interface Control Register (EMI0CN, shown in SFR Definition 11.1). Addressing using 8 bits will map to one of four 256-byte pages, and these pages are selected by setting the PGSEL bits in the EMI0CN register.

NOTE: The MOVX instruction is also used for write to the Flash memory. Please see section 10 for details. The MOVX instruction will access XRAM by default.

For any of the addressing modes, the upper 6 bits of the 16-bit external data memory address word are "don't cares". As a result, the 1024-byte RAM is mapped modulo style ("wrap around") over the entire 64k of possible address values. For example, the XRAM byte at address 0x0000 is also at address 0x0400, 0x0800, 0x0C00, 0x1000, etc. This feature is useful when doing a linear memory fill, as the address pointer does not have to be reset when reaching the RAM block boundary.

### SFR Definition 11.1. EMI0CN: External Memory Interface Control

| R          | R                                                                                    | R    | R    | R    | R    | R/W    | R/W    | Reset Value  |  |  |  |  |

|------------|--------------------------------------------------------------------------------------|------|------|------|------|--------|--------|--------------|--|--|--|--|

| -          | -                                                                                    | -    | -    | -    | -    | PGSEL1 | PGSEL0 | 00000000     |  |  |  |  |

| Bit7       | Bit6                                                                                 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1   | Bit0   | SFR Address: |  |  |  |  |

|            |                                                                                      |      |      |      |      |        |        | 0xAF         |  |  |  |  |

| Bits1–0: > | Bit7     Bit6     Bit5     Bit4     Bit3     Bit2     Bit1     Bit0     SFR Address: |      |      |      |      |        |        |              |  |  |  |  |

### SFR Definition 12.2. RSTSRC: Reset Source

|          | R              | R/W                              | R/W          | R                 | R           | R/W          | R           | Reset Value  |  |  |  |  |  |

|----------|----------------|----------------------------------|--------------|-------------------|-------------|--------------|-------------|--------------|--|--|--|--|--|

| -        |                | CORSEF                           | SWRSEF       | WDTRSF            | MCDRSF      | PORSF        | PINRSF      | xxxxxxxx     |  |  |  |  |  |

| Bit7     | Bit6           | Bit5                             | Bit4         | Bit3              | Bit2        | Bit1         | Bit0        | SFR Address: |  |  |  |  |  |

|          |                |                                  |              |                   |             |              |             | 0xEF         |  |  |  |  |  |

|          |                |                                  |              |                   |             |              |             |              |  |  |  |  |  |

| (Note: D | Do not use rea | ad-modify-wr                     | ite operatio | ons on this I     | egister.)   |              |             |              |  |  |  |  |  |

| Bit7:    | RESERVE        | D.                               |              |                   |             |              |             |              |  |  |  |  |  |

| Bit6:    |                | Read only 0                      |              |                   |             |              |             |              |  |  |  |  |  |

| Bit5:    |                | Comparator C                     | Reset Ena    | able and Fla      | ag          |              |             |              |  |  |  |  |  |

|          | Write          |                                  |              |                   |             |              |             |              |  |  |  |  |  |

|          |                | ator 0 is not                    |              |                   |             |              |             |              |  |  |  |  |  |

|          | •              | ator 0 is a re                   | set source   | (active low)      |             |              |             |              |  |  |  |  |  |

|          | Read           |                                  |              |                   |             |              |             |              |  |  |  |  |  |

|          |                | alue read fro                    | om CORSE     | F IS NOT DET      | ned if Comp | parator u na | is not been | enabled as   |  |  |  |  |  |

|          | a reset sou    |                                  | waa not fr   |                   | ator 0      |              |             |              |  |  |  |  |  |

|          |                | of prior reset<br>of prior reset |              |                   |             |              |             |              |  |  |  |  |  |

| Bit4:    |                | oftware Rese                     |              | •                 | 0           |              |             |              |  |  |  |  |  |

| DIL4.    | Write          | Sitware itese                    |              | uriay             |             |              |             |              |  |  |  |  |  |

|          | 0: No Effect   | rt                               |              |                   |             |              |             |              |  |  |  |  |  |

|          |                | an internal re                   | set. RST c   | in is not aff     | ected.      |              |             |              |  |  |  |  |  |

| Read     |                |                                  |              |                   |             |              |             |              |  |  |  |  |  |

|          | 0: Prior res   | set source wa                    | as not from  | write to the      | SWRSF bi    | it.          |             |              |  |  |  |  |  |

|          | 1: Prior res   | set source wa                    | as from wri  | te to the SV      | VRSF bit.   |              |             |              |  |  |  |  |  |

| Bit3:    | WDTRSF: \      | Watchdog Ti                      | mer Reset    | Flag (Read        | only)       |              |             |              |  |  |  |  |  |

|          | 0: Source of   | of prior reset                   | was not fr   | om WDT tin        | neout.      |              |             |              |  |  |  |  |  |

|          |                | of prior reset                   |              |                   |             |              |             |              |  |  |  |  |  |

| Bit2:    |                | Missing Cloc                     |              |                   |             |              |             |              |  |  |  |  |  |

|          |                | of prior reset                   |              |                   |             |              | t.          |              |  |  |  |  |  |

|          |                | of prior reset                   |              |                   | ck Detector | timeout.     |             |              |  |  |  |  |  |

| Bit1:    |                | wer-On Res                       | et Force a   | nd Flag           |             |              |             |              |  |  |  |  |  |

|          | Write          |                                  |              |                   |             |              |             |              |  |  |  |  |  |

|          | 0: No effec    |                                  |              |                   |             |              |             |              |  |  |  |  |  |

| Dood     | 1: Forces a    | a Power-On                       | Reset. RS    | i is ariven lo    | JW.         |              |             |              |  |  |  |  |  |

| Read     | 0. Source      | of prior roact                   | was not fr   |                   |             |              |             |              |  |  |  |  |  |

|          |                | of prior reset<br>of prior reset |              |                   |             |              |             |              |  |  |  |  |  |

| Bit0:    |                | W Pin Reset                      |              |                   |             |              |             |              |  |  |  |  |  |

|          |                | of prior reset                   |              | om <u>RST</u> nin |             |              |             |              |  |  |  |  |  |

|          |                | of prior reset                   |              |                   | •           |              |             |              |  |  |  |  |  |

|          | 1. 000100 0    |                                  |              |                   |             |              |             |              |  |  |  |  |  |

|          |                |                                  |              |                   |             |              |             |              |  |  |  |  |  |

| R/W      | R/W                                                                                                                                                | R/W                                             | R/W   | R/W         | R/W          | R/W          | R/W      | Reset Value  |  |  |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------|-------------|--------------|--------------|----------|--------------|--|--|--|--|--|--|

| MSCLKE   | -                                                                                                                                                  | -                                               | IFRDY | CLKSL       | IOSCEN       | IFCN1        | IFCN0    | 00000100     |  |  |  |  |  |  |

| Bit7     | Bit6                                                                                                                                               | Bit5                                            | Bit4  | Bit3        | Bit2         | Bit1         | Bit0     | SFR Address: |  |  |  |  |  |  |

|          |                                                                                                                                                    |                                                 |       |             |              |              |          | 0xB2         |  |  |  |  |  |  |

| Bit7:    | <ol> <li>0: Missing Clock Detector Disabled</li> <li>1: Missing Clock Detector Enabled; triggers a reset if a missing clock is detected</li> </ol> |                                                 |       |             |              |              |          |              |  |  |  |  |  |  |

| Bits6–5: |                                                                                                                                                    |                                                 |       |             |              |              |          |              |  |  |  |  |  |  |

| Bit4:    |                                                                                                                                                    | IFRDY: Internal Oscillator Frequency Ready Flag |       |             |              |              |          |              |  |  |  |  |  |  |

|          | 0: Internal                                                                                                                                        |                                                 |       | •           |              |              |          | 5.           |  |  |  |  |  |  |

| Dire     |                                                                                                                                                    |                                                 |       | • •         | eed specifie | ed by the IF | CN bits. |              |  |  |  |  |  |  |

| Bit3:    | CLKSL: Sys                                                                                                                                         |                                                 |       |             |              |              |          |              |  |  |  |  |  |  |

|          | 0: Uses Int                                                                                                                                        |                                                 |       |             |              |              |          |              |  |  |  |  |  |  |

| Bit2:    | 1: Uses Ex<br>IOSCEN: In                                                                                                                           |                                                 |       |             |              |              |          |              |  |  |  |  |  |  |

| DILZ.    | 0: Internal                                                                                                                                        |                                                 |       |             |              |              |          |              |  |  |  |  |  |  |

|          | 1: Internal                                                                                                                                        |                                                 |       |             |              |              |          |              |  |  |  |  |  |  |

| Bits1–0: | IFCN1-0: In                                                                                                                                        |                                                 |       | ancy Contro | l Rits       |              |          |              |  |  |  |  |  |  |

| Ditor 0. | 00: Interna                                                                                                                                        |                                                 |       | •           |              |              |          |              |  |  |  |  |  |  |

|          | 01: Interna                                                                                                                                        |                                                 |       |             |              |              |          |              |  |  |  |  |  |  |

|          | 10: Interna                                                                                                                                        |                                                 |       |             |              |              |          |              |  |  |  |  |  |  |

|          | 11: Internal Oscillator typical frequency is 16 MHz.                                                                                               |                                                 |       |             |              |              |          |              |  |  |  |  |  |  |

|          |                                                                                                                                                    |                                                 | ··· · | -           |              |              |          |              |  |  |  |  |  |  |

### SFR Definition 13.1. OSCICN: Internal Oscillator Control

### **Table 13.1. Internal Oscillator Electrical Characteristics**

-40 to +85 ×C unless otherwise specified.

| Parameter                                                        | Conditions        | Min | Тур | Max | Units  |

|------------------------------------------------------------------|-------------------|-----|-----|-----|--------|

| Internal Oscillator Frequency                                    | OSCICN.[1:0] = 00 | 1.5 | 2.0 | 2.5 | MHz    |

|                                                                  | OSCICN.[1:0] = 01 | 3.0 | 4.0 | 5.0 |        |

|                                                                  | OSCICN.[1:0] = 10 | 6.0 | 8.0 | 10  |        |

|                                                                  | OSCICN.[1:0] = 11 | 12  | 16  | 20  |        |

| Internal Oscillator Current Consumption                          | OSCICN.2 = 1      | —   | 200 | _   | μA     |

| Internal Oscillator Temperature Stability                        |                   | —   | 4   | _   | ppm/°C |

| Internal Oscillator Power Supply (V <sub>DD</sub> )<br>Stability |                   | _   | 6.4 | _   | %/V    |

| SFR Definition 13.2 | . OSCXCN: External | <b>Oscillator Control</b> |

|---------------------|--------------------|---------------------------|

|---------------------|--------------------|---------------------------|

| R                 | R/W                                                                                                                                                                                                                                                                                                               | R/W                                                    | R/W             | R/W          | R/W                      | R/W      | R/W               | Reset Value  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------|--------------|--------------------------|----------|-------------------|--------------|--|--|--|--|

| XTLVLD            |                                                                                                                                                                                                                                                                                                                   |                                                        |                 |              | XFCN2                    | XFCN1    | XFCN0             | 00110000     |  |  |  |  |

| Bit7              | Bit6                                                                                                                                                                                                                                                                                                              |                                                        | Bit4            | Bit3         | Bit2                     | Bit1     | Bit0              | SFR Address: |  |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                   |                                                        |                 |              |                          |          |                   | 0xB1         |  |  |  |  |

| Bit7:             | (Valid only when XOSCMD = 1xx.)<br>0: Crystal Oscillator is unused or not yet stable                                                                                                                                                                                                                              |                                                        |                 |              |                          |          |                   |              |  |  |  |  |

| Bits6–4:          | <ul> <li>00x: Off. XTAL1 pin is grounded internally.</li> <li>010: System Clock from External CMOS Clock on XTAL1 pin.</li> <li>011: System Clock from External CMOS Clock on XTAL1 pin divided by 2.</li> <li>10x: RC/C Oscillator Mode with divide by 2 stage.</li> <li>110: Crystal Oscillator Mode</li> </ul> |                                                        |                 |              |                          |          |                   |              |  |  |  |  |

| D:+0.             |                                                                                                                                                                                                                                                                                                                   | ystal Oscillator N                                     |                 | •            | -                        |          |                   |              |  |  |  |  |

| Bit3:<br>Bits2–0: |                                                                                                                                                                                                                                                                                                                   | VED. Read = u<br>-0: External Osc                      |                 |              |                          |          |                   |              |  |  |  |  |

| Dit32-0.          |                                                                                                                                                                                                                                                                                                                   | 1: see table belo                                      | •               |              |                          |          |                   |              |  |  |  |  |

|                   | XFCN                                                                                                                                                                                                                                                                                                              | Crystal (XOSC                                          |                 | RC (XO       | SCMD = 10                | )x) C (X | OSCMD =           | 10x)         |  |  |  |  |

|                   | 000                                                                                                                                                                                                                                                                                                               | f ≤ 12.5                                               |                 | -            | 25 kHz                   |          | K Factor = $0.44$ |              |  |  |  |  |

|                   | 001                                                                                                                                                                                                                                                                                                               | 12.5 kHz < f ≤                                         |                 |              | < f ≤ 50 kH              |          | K Factor = $1.4$  |              |  |  |  |  |

|                   | 010                                                                                                                                                                                                                                                                                                               | 30.35 kHz < f s                                        |                 | -            | $< f \le 100 \text{ kH}$ |          | K Factor = 4.4    |              |  |  |  |  |

|                   | 011                                                                                                                                                                                                                                                                                                               | 93.8 kHz < f ≤                                         |                 |              | < f ≤ 200 k              |          | K Factor = 13     |              |  |  |  |  |

|                   | 100                                                                                                                                                                                                                                                                                                               | 267 kHz < f ≤                                          |                 |              | < f ≤ 400 k              |          | Factor = 3        |              |  |  |  |  |

|                   | 101                                                                                                                                                                                                                                                                                                               | 722 kHz < f ≤                                          | 2.23 MHz        | 400 kHz      | < f ≤ 800 k              | Hz K     | Factor = 1        | 00           |  |  |  |  |

|                   | 110                                                                                                                                                                                                                                                                                                               | 2.23 MHz < f ≤                                         | 6.74 MHz        | 800 kHz      | < f ≤ 1.6 M              | Hz K     | Factor = 4        | 20           |  |  |  |  |

|                   | 111                                                                                                                                                                                                                                                                                                               | f > 6.74                                               | MHz             | 1.6 MHz      | < f ≤ 3.2 M              | Hz K     | Factor = 14       | 400          |  |  |  |  |

|                   | Choose                                                                                                                                                                                                                                                                                                            | (Circuit from Fig<br>XFCN value to<br>t from Figure 13 | match the c     | rystal frequ | iency.                   | 1x)      |                   |              |  |  |  |  |

|                   | •                                                                                                                                                                                                                                                                                                                 | oscillation frequ                                      | •               |              | - 100                    |          |                   |              |  |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                   | (10 <sup>3</sup> ) / (R x C), v                        |                 | -            |                          |          |                   |              |  |  |  |  |

|                   | f = frequ                                                                                                                                                                                                                                                                                                         | ency of oscillati                                      | on in MHz       |              |                          |          |                   |              |  |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                   | acitor value in p                                      |                 |              |                          |          |                   |              |  |  |  |  |

|                   | R = Pul                                                                                                                                                                                                                                                                                                           | -up resistor valu                                      | e in k $\Omega$ |              |                          |          |                   |              |  |  |  |  |

| C MODE            | <pre>C MODE (Circuit from Figure 13.1, Option 3; XOSCMD = 10x)<br/>Choose K Factor (KF) for the oscillation frequency desired:<br/>f = KF / (C x AV+), where<br/>f = frequency of oscillation in MHz<br/>C = capacitor value on XTAL1, XTAL2 pins in pF</pre>                                                     |                                                        |                 |              |                          |          |                   |              |  |  |  |  |

|                   | $V_{DD} = F$                                                                                                                                                                                                                                                                                                      | ower supply vol                                        | tage on MC      | U in volts   |                          |          |                   |              |  |  |  |  |

### SFR Definition 14.2. PRT1MX: Port I/O MUX Register 1

| R         | R/W                              | R             | R             | R           | R    | R/W    | R/W    | Reset Value  |  |  |  |

|-----------|----------------------------------|---------------|---------------|-------------|------|--------|--------|--------------|--|--|--|

| -         | SYSCKE                           | -             | -             | -           | -    | CP10EN | CP00EN | 00000000     |  |  |  |

| Bit7      | Bit6                             | Bit5          | Bit4          | Bit3        | Bit2 | Bit1   | Bit0   | SFR Address: |  |  |  |

|           |                                  |               |               |             |      |        |        | 0xE2         |  |  |  |

|           |                                  |               |               |             |      |        |        |              |  |  |  |

| Bit7:     | UNUSED. Read = 0.                |               |               |             |      |        |        |              |  |  |  |

| Bit6:     | SYSCKE: SYSCLK Output Enable Bit |               |               |             |      |        |        |              |  |  |  |

|           | 0: SYSCLK                        | unavailable   | e at the port | t pin.      |      |        |        |              |  |  |  |

|           | 1: SYSCLK                        | output rout   | ed to pin P   | 1.6         |      |        |        |              |  |  |  |

| Bits 5-2: | UNUSED. F                        | Read = 0000   | 0b, Write =   | don't care. |      |        |        |              |  |  |  |

| Bit1:     | CP10EN: C                        | Comparator    | 1 Output E    | nable bit.  |      |        |        |              |  |  |  |

|           | 0: CP1 una                       | available at  | Port pin.     |             |      |        |        |              |  |  |  |

|           | 1: CP1 rou                       | ted to Port I | Pin P1.5.     |             |      |        |        |              |  |  |  |

| Bit0:     | CP0OEN: C                        | Comparator    | 0 Output E    | nable Bit   |      |        |        |              |  |  |  |

|           | 0: CP0 una                       |               | •             |             |      |        |        |              |  |  |  |

|           | 1: CP0 rou                       |               |               |             |      |        |        |              |  |  |  |

|           |                                  |               |               |             |      |        |        |              |  |  |  |

### SFR Definition 14.3. PRT2MX: Port I/O MUX Register 2

| R/W    | R/W          | R/W           | R/W           | R/W         | R/W         | R/W          | R/W          | Reset Value  |

|--------|--------------|---------------|---------------|-------------|-------------|--------------|--------------|--------------|

| GWPUD  | P3WPUD       | P2WPUD        | P1WPUD        | P0WPUD      | -           | -            | SPI00EN      | 00000000     |

| Bit7   | Bit6         | Bit5          | Bit4          | Bit3        | Bit2        | Bit1         | Bit0         | SFR Address: |

|        |              |               |               |             |             |              |              | 0xE3         |

| D:4 7. |              | lahal Darit L |               |             |             |              |              |              |

| Bit 7: | GWPUD: G     |               |               | •           | ie Bit      |              |              |              |

|        | 0: Weak Pu   | •             | •             |             |             |              |              |              |

| 1      | 1: Weak Pu   | •             | •             |             | res)        |              |              |              |

| Bit 6: | P3WPUD: F    |               |               |             |             |              |              |              |

|        | 0: Weak Pu   | ull-ups Enat  | oled for port | : 3         |             |              |              |              |

|        | 1: Weak Pu   | ull-ups Disa  | bled for por  | t 3         |             |              |              |              |

| Bit 5: | P2WPUD: F    | Port 2 Weak   | k Pull-up Dis | sable Bit   |             |              |              |              |

|        | 0: Weak Pu   | ull-ups Enat  | oled for port | 2.          |             |              |              |              |

|        | 1: Weak Pu   | JII-ups Disa  | bled for por  | t 2         |             |              |              |              |

| Bit 4: | P1WPUD: F    | •             |               |             |             |              |              |              |

|        | 0: Weak Pu   |               |               |             |             |              |              |              |

|        | 1: Weak Pu   |               |               |             |             |              |              |              |

| Bit 3: | POWPUD: F    | •             |               |             |             |              |              |              |

| Dit 5. | 0: Weak Pu   |               |               |             |             |              |              |              |

|        |              | •             |               |             |             |              |              |              |

|        | 1: Weak Pu   | •             |               |             |             |              |              |              |

|        | UNUSED. F    |               |               |             |             |              |              |              |

| Bit 0: | SPI0OEN: S   |               |               |             |             |              |              |              |

|        | 0: SPI I/O u |               |               |             |             |              |              |              |

|        | 1: SCK, MIS  | SO, MOSI, I   | NSS routed    | to pins P2. | 0, P2.1, P2 | .2, and P2.3 | 3 respective | ely.         |

|        |              |               |               |             |             |              |              |              |

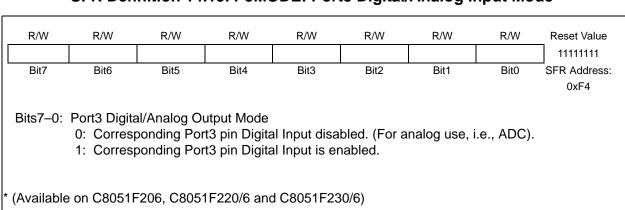

### SFR Definition 14.15. P3MODE: Port3 Digital/Analog Input Mode\*

### Table 14.1. Port I/O DC Electrical Characteristics

| Parameter             | Conditions                                          | Min                      | Тур                      | Max                      | Units |

|-----------------------|-----------------------------------------------------|--------------------------|--------------------------|--------------------------|-------|

|                       | I <sub>OH</sub> = −10 uA, Port I/O push-pull        | V <sub>DD</sub> –        |                          |                          |       |

| Output High Voltage   | I <sub>OH</sub> = −3 mA, Port I/O push-pull         | 0.1<br>V <sub>DD</sub> – |                          |                          | V     |

|                       | I <sub>OH</sub> = −10 mA, Port I/O push-pull        | 0.7                      | V <sub>DD</sub> –<br>0.8 |                          |       |

| Output Low Voltage    | I <sub>OL</sub> = 10 uA<br>I <sub>OL</sub> = 8.5 mA |                          |                          | 0.1                      | V     |

|                       | $I_{OL} = 25 \text{ mA}$                            |                          | 1.0                      | 0.6                      | v     |

| Input High Voltage    |                                                     | 0.7 x<br>V <sub>DD</sub> |                          |                          | V     |

| Input Low Voltage     |                                                     |                          |                          | 0.3 x<br>V <sub>DD</sub> | V     |

|                       | DGND < Port Pin < V <sub>DD</sub> , Pin Tri-state   |                          |                          |                          | A     |

| Input Leakage Current | Weak Pull-up Off<br>Weak Pull-up On                 |                          | 30                       | ±1                       | μA    |

| Capacitive Loading    |                                                     |                          | 3                        |                          | pF    |

$V_{DD}$  = 2.7 to 3.6 V, -40 to +85 °C unless otherwise specified.

| R/W   | R/W                      | R/W                          | R/W          | R/W           | R/W           | R/W             | R/W          | Reset Value                                         |

|-------|--------------------------|------------------------------|--------------|---------------|---------------|-----------------|--------------|-----------------------------------------------------|

| TF1   | TR1                      | TF0                          | TR0          | IE1           | IT1           | IE0             | IT0          | 00000000                                            |

| Bit7  | Bit6                     | Bit5                         | Bit4         | Bit3          | Bit2          | Bit1            | Bit0         | SFR Address:<br>0x88                                |

| Bit7: | TF1: Timer               |                              |              | orflowe Th    | is flog con l | a cleared b     | w coftwor    | e but is auto-                                      |

|       |                          | eared when                   | the CPU v    |               |               | terrupt servi   |              |                                                     |

|       | 1: Timer 1               |                              |              |               |               |                 |              |                                                     |

| Bit6: | TR1: Timer               |                              |              |               |               |                 |              |                                                     |

| Bito. | 0: Timer 1               |                              |              |               |               |                 |              |                                                     |

|       | 1: Timer 1               |                              |              |               |               |                 |              |                                                     |

| Bit5: | TF0: Timer               | 0 Overflow                   | Flag.        |               |               |                 |              |                                                     |

|       |                          |                              |              |               |               |                 |              | e but is auto-                                      |

|       |                          |                              |              | ectors to th  | e Timer 0 in  | terrupt serv    | ice routine  | ).                                                  |

|       | 0: No Time               |                              |              |               |               |                 |              |                                                     |

| D:44  | 1: Timer 0               |                              |              |               |               |                 |              |                                                     |

| Bit4: | TR0: Timer               |                              | trol.        |               |               |                 |              |                                                     |

|       | 0: Timer 0<br>1: Timer 0 |                              |              |               |               |                 |              |                                                     |

| Bit3: | IE1: Extern              |                              | 1            |               |               |                 |              |                                                     |

| Dito. |                          |                              |              | an edge/lev   | el of type de | efined by IT    | 1 is detect  | ed. It can be                                       |

|       |                          |                              |              |               |               |                 |              | External Inter-                                     |

|       |                          |                              |              |               |               |                 |              | l's logic level                                     |

|       | when IT1 =               | 0.                           |              | Ū             |               |                 |              | Ū                                                   |

| Bit2: | IT1: Interru             |                              |              |               |               |                 |              |                                                     |

|       | This bit sele            | ects whethe                  | r the config | ured /INT1    | signal will d | etect falling   | edge or a    | ctive-low                                           |

|       | level-sensit             |                              |              |               |               |                 |              |                                                     |

|       | 0: /INT1 is              |                              |              |               |               |                 |              |                                                     |

| DIA   | 1: /INT1 is              | 0 00                         |              |               |               |                 |              |                                                     |

| Bit1: | IE0: Extern              |                              |              | on odro/los   | امم مراجع     | afin a d by IT( | ) ia dataat  | ad Itaan ba                                         |

|       | cleared by               | software bu<br>ce routine if | t is automa  | tically clear | ed when the   | e CPU vecto     | ors to the E | ed. It can be<br>External Inter-<br>I's logic level |

| Bit0: | IT0: Interru             |                              |              |               |               |                 |              |                                                     |

|       | level-sensit             | ive interrup <sup>-</sup>    | ts.          | ured /INT0    | signal will d | etect falling   | edge or a    | ctive-low                                           |

|       | 0: /INT0 is              |                              |              |               |               |                 |              |                                                     |

|       | 1: /INT0 is              | edge trigge                  | red.         |               |               |                 |              |                                                     |

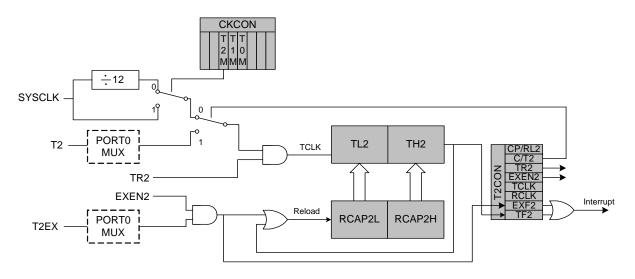

### 17.2. Timer 2

Timer 2 is a 16-bit counter/timer formed by the two 8-bit SFR's: TL2 (low byte) and TH2 (high byte). As with Timers 0 and 1, Timer 2 can use either the system clock or transitions on an external input pin as its clock source. The Counter/Timer Select bit C/T2 bit (T2CON.1) selects the clock source for Timer 2. Clearing C/T2 selects the system clock as the input for the timer (divided by either one or twelve as specified by the Timer Clock Select bit T2M in CKCON). When C/T2 is set to 1, high-to-low transitions at the T2 input pin increment the counter/timer register. (Refer to Section 14 for information on selecting and configuring external I/O pins.) Timer 2 can also be used to start an ADC Data Conversion (see section 5).

Timer 2 offers capabilities not found in Timer 0 and Timer 1. It operates in one of three modes: 16-bit Counter/Timer with Capture, 16-bit Counter/Timer with Auto-Reload or Baud Rate Generator Mode. Timer 2's operating mode is selected by setting configuration bits in the Timer 2 Control (T2CON) register. Below is a summary of the Timer 2 operating modes and the T2CON bits used to configure the counter/timer. Detailed descriptions of each mode follow.

| RCLK | TCLK | CP/RL2 | TR2 | Mode                                  |

|------|------|--------|-----|---------------------------------------|

| 0    | 0    | 1      | 1   | 16-bit Counter/Timer with Capture     |

| 0    | 0    | 0      | 1   | 16-bit Counter/Timer with Auto-Reload |

| 0    | 1    | Х      | 1   | Baud Rate Generator for TX            |

| 1    | 0    | Х      | 1   | Baud Rate Generator for RX            |

| 1    | 1    | Х      | 1   | Baud Rate Generator for TX and RX     |

| Х    | Х    | Х      | 0   | Off                                   |

#### 17.2.2. Mode 1: 16-bit Counter/Timer with Auto-Reload

The Counter/Timer with Auto-Reload mode sets the TF2 timer overflow flag when the counter/timer register overflows from 0xFFFF to 0x0000. An interrupt is generated if enabled. On overflow, the 16-bit value held in the two capture registers (RCAP2H, RCAP2L) is automatically loaded into the counter/timer register and the timer is restarted.

Counter/Timer with Auto-Reload mode is selected by clearing the CP/RL2 bit. Setting TR2 to logic 1 enables and starts the timer. Timer 2 can use either the system clock or transitions on an external input pin as its clock source, as specified by the C/T2 bit. If EXEN2 is set to logic 1, a high-to-low transition on T2EX will also cause Timer 2 to be reloaded. If EXEN2 is cleared, transitions on T2EX will be ignored.

Figure 17.5. T2 Mode 1 Block Diagram

|                                                                                                                                                                                                                                                                                                                | _                                                                                                                                                                                                                                                                                                |                                                                                             |                                                    |                                            |                       |                          |                             | Reset Value              |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------|-----------------------|--------------------------|-----------------------------|--------------------------|--|--|--|--|