Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SPI, UART/USART                                                |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                               |

| Number of I/O              | 22                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 22x8b                                                      |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 32-LQFP                                                        |

| Supplier Device Package    | 32-LQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f221-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 9.5. Power Management Modes                            | 83  |

|--------------------------------------------------------|-----|

| 9.5.1. Idle Mode                                       |     |

| 9.5.2. Stop Mode                                       |     |

| 10. Flash Memory                                       |     |

| 10.1.Programming The Flash Memory                      |     |

| 10.2.Security Options                                  |     |

| 11. On-Chip XRAM (C8051F206/226/236)                   |     |

| 12. Reset Sources                                      |     |

| 12.1.Power-on Reset                                    |     |

| 12.2.Software Forced Reset                             |     |

| 12.3.Power-fail Reset                                  |     |

| 12.4.External Reset                                    |     |

| 12.5.Missing Clock Detector Reset                      |     |

| 12.6.Comparator 0 Reset                                |     |

| 12.7.Watchdog Timer Reset                              |     |

| 12.7.1.Watchdog Usage                                  |     |

| 13. Oscillator                                         |     |

| 13.1.External Crystal Example                          |     |

| 13.2.External RC Example                               |     |

| 13.3.External Capacitor Example                        |     |

| 14. Port Input/Output                                  |     |

| 14.1.Port I/O Initialization                           |     |

| 14.2.General Purpose Port I/O                          | 105 |

| 15. Serial Peripheral Interface Bus                    |     |

| 15.1.Signal Descriptions                               |     |

| 15.1.1.Master Out, Slave In                            |     |

| 15.1.2.Master In, Slave Out                            |     |

| 15.1.3.Serial Clock                                    |     |

| 15.1.4.Slave Select                                    |     |

| 15.2.Serial Clock Timing                               |     |

| 15.3.SPI Special Function Registers                    |     |

| 16.UART                                                |     |

| 16.1.UART Operational Modes                            |     |

| 16.1.1.Mode 0: Synchronous Mode                        |     |

| 16.1.2.Mode 1: 8-Bit UART, Variable Baud Rate          |     |

| 16.1.3.Mode 2: 9-Bit UART, Fixed Baud Rate             |     |

| 16.1.4.Mode 3: 9-Bit UART, Variable Baud Rate          |     |

| 16.2.Multiprocessor Communications                     |     |

| 17. Timers                                             |     |

| 17.1.Timer 0 and Timer 1                               |     |

| 17.1.1.Mode 0: 13-bit Counter/Timer                    |     |

| 17.1.2.Mode 1: 16-bit Counter/Timer                    |     |

| 17.1.3.Mode 2: 8-bit Counter/Timer with Auto-Reload    |     |

| 17.1.4.Mode 3: Two 8-bit Counter/Timers (Timer 0 Only) |     |

|                                                        |     |

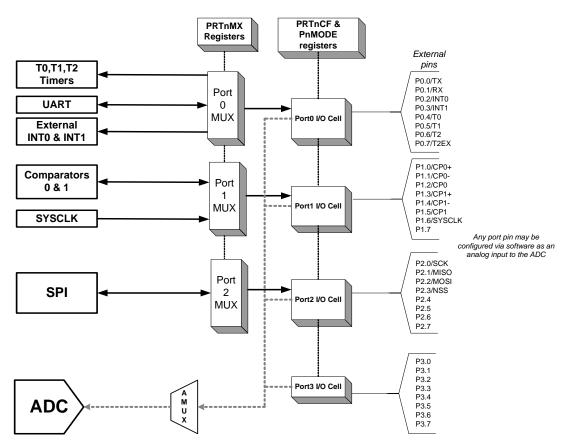

# 1. System Overview

The C8051F2xx is a family of fully integrated, mixed-signal System on a Chip MCU's available with a true 12-bit ('F206) multi-channel ADC, 8-bit multi-channel ADC ('F220/1/6 and 'F206), or without an ADC ('F230/1/6). Each model features an 8051-compatible microcontroller core with 8 kB of Flash memory. There are also UART and SPI serial interfaces implemented in hardware (not "bit-banged" in user software). Products in this family feature 22 or 32 general purpose I/O pins, some of which can be used for assigned digital peripheral interface. Any pins may be configured for use as analog input to the analog-to-digital converter ('F220/1/6 and 'F206 only). (See the Product Selection Guide in Table 1.1 for a quick reference of each MCUs' feature set.)

Other features include an on-board  $V_{DD}$  monitor, WDT, and clock oscillator. On-board Flash memory can be reprogrammed in-circuit, and may also be used for non-volatile data storage. Integrated peripherals can also individually shut down any or all of the peripherals to conserve power. All parts have 256 bytes of SRAM. Also, an additional 1024 bytes of RAM is available in the 'F206/226/236.

On-board JTAG debug support allows non-intrusive (uses no on-chip resources), full speed, in-circuit debug using the production MCU installed in the final application. This debug system supports inspection and modification of memory and registers, setting breakpoints, watchpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional when emulating using JTAG.

Each MCU is specified for 2.7 to 3.6 V operation over the industrial temperature range (-45 to +85 °C) and is available in the 48-pin TFQP and 32-pin LFQP. The Port I/Os are tolerant for input signals up to 5 V.

|           | MIPS (Peak) | Flash Memory | RAM  | SPI          | UART         | Timers (16-bit) | Digital Port I/O's | ADC Resolution (bits) | ADC Max Speed (ksps) | ADC Inputs | Voltage Comparators | Package |

|-----------|-------------|--------------|------|--------------|--------------|-----------------|--------------------|-----------------------|----------------------|------------|---------------------|---------|

| C8051F206 | 25          | 8 k          | 1280 | $\checkmark$ | $\checkmark$ | 3               | 32                 | 12                    | 100                  | 32         | 2                   | 48TQFP  |

| C8051F220 | 25          | 8 k          | 256  | $\checkmark$ | $\checkmark$ | 3               | 32                 | 8                     | 100                  | 32         | 2                   | 48TQFP  |

| C8051F221 | 25          | 8 k          | 256  | $\checkmark$ | $\checkmark$ | 3               | 22                 | 8                     | 100                  | 22         | 2                   | 32LQFP  |

| C8051F226 | 25          | 8 k          | 1280 | $\checkmark$ | $\checkmark$ | 3               | 32                 | 8                     | 100                  | 32         | 2                   | 48TQFP  |

| C8051F230 | 25          | 8 k          | 256  | $\checkmark$ | $\checkmark$ | 3               | 32                 |                       | _                    |            | 2                   | 48TQFP  |

| C8051F231 | 25          | 8 k          | 256  | $\checkmark$ | $\checkmark$ | 3               | 22                 |                       | _                    |            | 2                   | 32LQFP  |

| C8051F236 | 25          | 8 k          | 1280 | $\checkmark$ | $\checkmark$ | 3               | 32                 | _                     |                      |            | 2                   | 48TQFP  |

# Table 1.1. Product Selection Guide

# 4. Pinout and Package Definitions

Table 4.1. Pin Definitions

| Name            | <sup>6</sup> F206,<br>F220,<br>226,<br>230,<br>236<br><b>48-Pin</b> | <sup>'F221,</sup><br>231<br><b>32-Pin</b> | Туре          | Description                                                                                                                                                                                                                                                                            |  |  |  |

|-----------------|---------------------------------------------------------------------|-------------------------------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>DD</sub> | 11,31                                                               | 8                                         |               | Digital Voltage Supply.                                                                                                                                                                                                                                                                |  |  |  |

| GND             | 5,6,8,<br>13,32                                                     | 9                                         |               | Ground. ( <b>Note:</b> Pins 5,6, and 8 on the 48-pin package are not connected (NC), but it is recommended that they be connected to ground.)                                                                                                                                          |  |  |  |

| MONEN           | 12                                                                  |                                           | D In          | Monitor Enable (on 48 pin package ONLY). Enables reset volt-<br>age monitor function when pulled high (logic "1").                                                                                                                                                                     |  |  |  |

| ТСК             | 25                                                                  | 17                                        | D In          | JTAG Test Clock with internal pull-up.                                                                                                                                                                                                                                                 |  |  |  |

| TMS             | 26                                                                  | 18                                        | D In          | JTAG Test-Mode Select with internal pull-up.                                                                                                                                                                                                                                           |  |  |  |

| TDI             | 28                                                                  | 20                                        | D In          | JTAG Test Data Input with internal pull-up. TDI is latched on a rising edge of TCK.                                                                                                                                                                                                    |  |  |  |

| TDO             | 27                                                                  | 19                                        | D Out         | JTAG Test Data Output. Data is shifted out on TDO on the falling edge of TCK. TDO output is a tri-state driver.                                                                                                                                                                        |  |  |  |

| XTAL1           | 9                                                                   | 6                                         | A In          | Crystal Input. This pin is the return for the internal oscillator<br>cuit for a crystal or ceramic resonator. For a precision intern<br>clock, connect a crystal or ceramic resonator from XTAL1 to<br>XTAL2. If overdriven by an external CMOS clock, this becom<br>the system clock. |  |  |  |

| XTAL2           | 10                                                                  | 7                                         | A Out         | Crystal Output. This pin is the excitation driver for a crystal or ceramic resonator.                                                                                                                                                                                                  |  |  |  |

| RST             | 14                                                                  | 10                                        | D I/O         | Chip Reset. Open-drain output of internal Voltage Supply moni-<br>tor. Is driven low when V <sub>DD</sub> is < 2.7V and MONEN=1, or when a<br>'1'is written to PORSF. An external source can force a system<br>reset by driving this pin low.                                          |  |  |  |

| VREF            | 7                                                                   | 5                                         | A I/O         | Voltage Reference. When configured as an input, this pin is the voltage reference for the ADC. Otherwise, V <sub>DD</sub> will be the reference. NOTE: this pin is Not Connected (NC) on 'F230/1/6.                                                                                    |  |  |  |

| CP0+            | 4                                                                   | 4                                         | A In          | Comparator 0 Non-Inverting Input.                                                                                                                                                                                                                                                      |  |  |  |

| CP0-            | 3                                                                   | 3                                         | A In          | Comparator 0 Inverting Input.                                                                                                                                                                                                                                                          |  |  |  |

| CP0             | 2                                                                   | 2                                         | D Out         | Comparator 0 Output                                                                                                                                                                                                                                                                    |  |  |  |

| CP1+            | 1                                                                   | 1                                         | A In          | Comparator 1 Non-Inverting Input.                                                                                                                                                                                                                                                      |  |  |  |

| CP1-            | 48                                                                  | 32                                        | A In          | Comparator 1 Inverting Input.                                                                                                                                                                                                                                                          |  |  |  |

| CP1             | 47                                                                  | 31                                        | D Out         | Comparator 1 Output                                                                                                                                                                                                                                                                    |  |  |  |

| P0.0/TX         | 40                                                                  | 28                                        | D I/O<br>A In | Port0 Bit0. (See the Port I/O Sub-System section for complete description).                                                                                                                                                                                                            |  |  |  |

| P0.1/RX         | 39                                                                  | 27                                        | D I/O<br>A In | Port0 Bit1. (See the Port I/O Sub-System section for complete description).                                                                                                                                                                                                            |  |  |  |

| P0.2/INT0       | 38                                                                  | 26                                        | D I/O<br>A In | Port0 Bit2. (See the Port I/O Sub-System section for complete description).                                                                                                                                                                                                            |  |  |  |

| Name | <sup>6</sup> F206,<br>F220,<br>226,<br>230,<br>236 | ʻF221,<br>231 | Туре  | Description                                                   |  |  |  |  |  |

|------|----------------------------------------------------|---------------|-------|---------------------------------------------------------------|--|--|--|--|--|

|      | 48-Pin                                             | 32-Pin        |       |                                                               |  |  |  |  |  |

| P2.7 | 18                                                 |               | D I/O | Port2 Bit7. (See the Port I/O Sub-System section for complete |  |  |  |  |  |

|      |                                                    |               | A In  | description).                                                 |  |  |  |  |  |

| P3.0 | 44                                                 |               | D I/O | Port3 Bit0. (See the Port I/O Sub-System section for complete |  |  |  |  |  |

|      |                                                    |               | A In  | description).                                                 |  |  |  |  |  |

| P3.1 | 43                                                 |               | D I/O | Port3 Bit1. (See the Port I/O Sub-System section for complete |  |  |  |  |  |

|      |                                                    |               | A In  | description).                                                 |  |  |  |  |  |

| P3.2 | 42                                                 |               | D I/O | Port3 Bit2. (See the Port I/O Sub-System section for complete |  |  |  |  |  |

|      |                                                    |               | A In  | description).                                                 |  |  |  |  |  |

| P3.3 | 41                                                 |               | D I/O | Port3 Bit3. (See the Port I/O Sub-System section for complete |  |  |  |  |  |

|      |                                                    |               | A In  | description).                                                 |  |  |  |  |  |

| P3.4 | 30                                                 |               | D I/O | Port3 Bit4. (See the Port I/O Sub-System section for complete |  |  |  |  |  |

|      |                                                    |               | A In  | description).                                                 |  |  |  |  |  |

| P3.5 | 29                                                 |               | D I/O | Port3 Bit5. (See the Port I/O Sub-System section for complete |  |  |  |  |  |

|      |                                                    |               | A In  | description).                                                 |  |  |  |  |  |

| P3.6 | 20                                                 |               | D I/O | Port3 Bit6. (See the Port I/O Sub-System section for complete |  |  |  |  |  |

|      |                                                    |               | A In  | description).                                                 |  |  |  |  |  |

| P3.7 | 19                                                 |               | D I/O | Port3 Bit7. (See the Port I/O Sub-System section for complete |  |  |  |  |  |

|      |                                                    |               | A In  | description).                                                 |  |  |  |  |  |

Table 4.1. Pin Definitions (Continued)

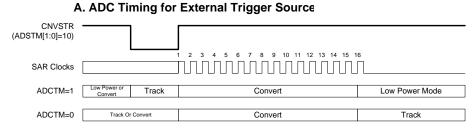

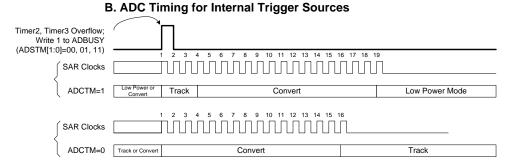

## 6.2. ADC Modes of Operation

The ADC has a maximum conversion speed of 100 ksps. The ADC conversion clock is derived from the system clock. The ADC conversion clock is derived from a divided version of SYSCLK. Divide ratios of 1, 2, 4, 8, or 16 are supported by setting the ADCSC bits in the ADC0CF Register. This is useful to adjust conversion speed to accommodate different system clock speeds.

A conversion can be initiated in one of two ways, depending on the programmed states of the ADC Start of Conversion Mode bits (ADSTM1, ADSTM0) in ADC0CN. Conversions may be initiated by:

- 1. Writing a 1 to the ADBUSY bit of ADC0CN;

- 2. A Timer 2 overflow (i.e. timed continuous conversions).

Writing a 1 to ADBUSY provides software control of the ADC whereby conversions are performed "ondemand". During conversion, the ADBUSY bit is set to 1 and restored to 0 when conversion is complete. The falling edge of ADBUSY triggers an interrupt (when enabled) and sets the ADCINT interrupt flag in the ADC0CN register. Note: When conversions are performed "on-demand", the ADCINT flag, not ADBUSY, should be polled to determine when the conversion has completed. Converted data is available in the ADC data word register, ADC0H.

The ADCTM bit in register ADC0CN controls the ADC track-and-hold mode. In its default state, the ADC input is continuously tracked, except when a conversion is in progress. Setting ADCTM to 1 allows one of two different low power track-and-hold modes to be specified by states of the ADSTM1-0 bits (also in ADC0CN):

- 1. Tracking begins with a write of 1 to ADBUSY and lasts for 3 SAR clocks;

- 2. Tracking starts with an overflow of Timer 2 and lasts for 3 SAR clocks.

Tracking can be disabled (shutdown) when the entire chip is in low power standby or sleep modes.

Figure 6.2. 12-Bit ADC Track and Conversion Example Timing

# 7. Voltage Reference (C8051F206/220/221/226)

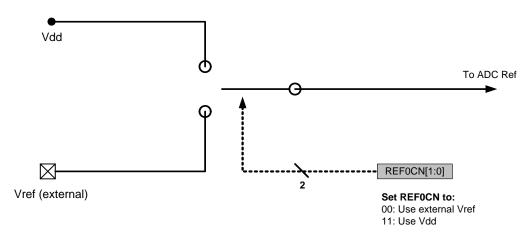

The voltage reference circuit selects between an externally connected reference and the power supply voltage ( $V_{DD}$ ). (See Figure 7.1).

An external reference can be connected to the VREF pin and selected by setting the REF0CN special function register per Figure 7.1. The external reference supply must be between  $V_{DD} - 0.3$  V and 1 V.  $V_{DD}$  may also be selected using REF0CN per SFR Definition 7.1. The electrical specifications for the Voltage Reference are given in Table 7.1.

Figure 7.1. Voltage Reference Functional Block Diagram

| R/W      | R/W                                                                                                | R/W                                    | R/W                            | R/W            | R/W  | R/W    | R/W    | Reset Value          |

|----------|----------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------|----------------|------|--------|--------|----------------------|

| -        | -                                                                                                  | -                                      | -                              | -              | -    | REFSL1 | REFSL0 | 00000000             |

| Bit7     | Bit6                                                                                               | Bit5                                   | Bit4                           | Bit3           | Bit2 | Bit1   | Bit0   | SFR Address:<br>0xD1 |

| Bits7-2: | UNUSED.                                                                                            | Read = 000                             | 000b; Write                    | = don't care   | 9    |        |        |                      |

| Bit1–0:  | REFSL1- R<br>Bits control<br>00: Externa<br>01: Reserve<br>10: Reserve<br>11: V <sub>DD</sub> sele | which refe<br>I VREF sou<br>ed.<br>ed. | rence is sele<br>urce is selec | ected.<br>ted. | on.  |        |        |                      |

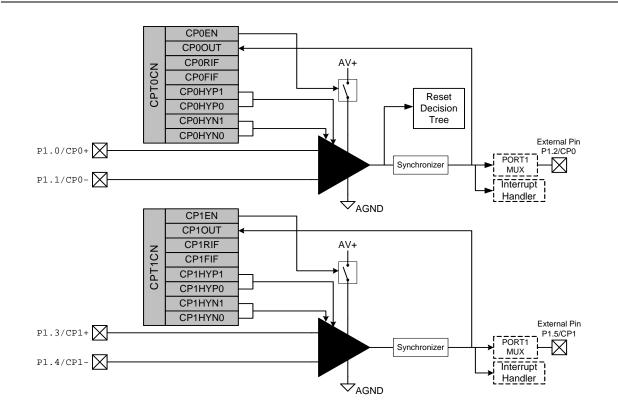

Figure 8.1. Comparator Functional Block Diagram

| Mnemonic           | Description                           | Bytes | Clock<br>Cycles |  |

|--------------------|---------------------------------------|-------|-----------------|--|

| INC @Ri            | Increment indirect RAM                | 1     | 2               |  |

| DEC A              | Decrement A                           | 1     | 1               |  |

| DEC Rn             | Decrement register                    | 1     | 1               |  |

| DEC direct         | Decrement direct byte                 | 2     | 2               |  |

| DEC @Ri            | Decrement indirect RAM                | 1     | 2               |  |

| INC DPTR           | Increment Data Pointer                | 1     | 1               |  |

| MUL AB             | Multiply A and B                      | 1     | 4               |  |

| DIV AB             | Divide A by B                         | 1     | 8               |  |

| DA A               | Decimal Adjust A                      | 1     | 1               |  |

| Logical Operations |                                       |       | - <b>I</b>      |  |

| ANL A,Rn           | AND Register to A                     | 1     | 1               |  |

| ANL A, direct      | AND direct byte to A                  | 2     | 2               |  |

| ANL A,@Ri          | AND indirect RAM to A                 | 1     | 2               |  |

| ANL A,#data        | AND immediate to A                    | 2     | 2               |  |

| ANL direct,A       | AND A to direct byte                  | 2     | 2               |  |

| ANL direct,#data   | AND immediate to direct byte          | 3     | 3               |  |

| ORL A,Rn           | OR Register to A                      | 1     | 1               |  |

| ORL A, direct      | OR direct byte to A                   | 2     | 2               |  |

| ORL A,@Ri          | OR indirect RAM to A                  | 1     | 2               |  |

| ORL A,#data        | OR immediate to A                     | 2     | 2               |  |

| ORL direct,A       | OR A to direct byte                   | 2     | 2               |  |

| ORL direct,#data   | OR immediate to direct byte           | 3     | 3               |  |

| XRL A,Rn           | Exclusive-OR Register to A            | 1     | 1               |  |

| XRL A, direct      | Exclusive-OR direct byte to A         | 2     | 2               |  |

| XRL A,@Ri          | Exclusive-OR indirect RAM to A        | 1     | 2               |  |

| XRL A,#data        | Exclusive-OR immediate to A           | 2     | 2               |  |

| XRL direct,A       | Exclusive-OR A to direct byte         | 2     | 2               |  |

| XRL direct,#data   | Exclusive-OR immediate to direct byte | 3     | 3               |  |

| CLR A              | Clear A                               | 1     | 1               |  |

| CPL A              | Complement A                          | 1     | 1               |  |

| RL A               | Rotate A left                         | 1     | 1               |  |

| RLC A              | Rotate A left through carry           | 1     | 1               |  |

| RR A               | Rotate A right                        | 1     | 1               |  |

| RRC A              | Rotate A right through carry          | 1     | 1               |  |

| SWAP A             | Swap nibbles of A                     | 1     | 1               |  |

| Data Transfer      | 1                                     | I     | 1               |  |

| MOV A,Rn           | Move register to A                    | 1     | 1               |  |

| MOV A, direct      | Move direct byte to A                 | 2     | 2               |  |

| MOV A,@Ri          | Move indirect RAM to A                | 1     | 2               |  |

# Table 9.1. CIP-51 Instruction Set Summary (Continued)

# 11. On-Chip XRAM (C8051F206/226/236)

The C8051F206/226/236 features 1024 Bytes of RAM mapped into the external data memory space. All address locations may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using indirect MOVX addressing mode. If the MOVX instruction is used with an 8-bit operand (such as @R1), then the high byte is the External Memory Interface Control Register (EMI0CN, shown in SFR Definition 11.1). Addressing using 8 bits will map to one of four 256-byte pages, and these pages are selected by setting the PGSEL bits in the EMI0CN register.

NOTE: The MOVX instruction is also used for write to the Flash memory. Please see section 10 for details. The MOVX instruction will access XRAM by default.

For any of the addressing modes, the upper 6 bits of the 16-bit external data memory address word are "don't cares". As a result, the 1024-byte RAM is mapped modulo style ("wrap around") over the entire 64k of possible address values. For example, the XRAM byte at address 0x0000 is also at address 0x0400, 0x0800, 0x0C00, 0x1000, etc. This feature is useful when doing a linear memory fill, as the address pointer does not have to be reset when reaching the RAM block boundary.

## SFR Definition 11.1. EMI0CN: External Memory Interface Control

| R          | R          | R                                                                                                      | R                                                         | R                                                    | R            | R/W          | R/W         | Reset Value  |

|------------|------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------|--------------|--------------|-------------|--------------|

| -          | -          | -                                                                                                      | -                                                         | -                                                    | -            | PGSEL1       | PGSEL0      | 00000000     |

| Bit7       | Bit6       | Bit5                                                                                                   | Bit4                                                      | Bit3                                                 | Bit2         | Bit1         | Bit0        | SFR Address: |

|            |            |                                                                                                        |                                                           |                                                      |              |              |             | 0xAF         |

| Bits1–0: > | when using | Select Bits<br>Page Select<br>an 8-bit MG<br>are "don't of<br>ry address so<br>0x0FF<br>0x1FF<br>0x2FF | PGSEL[1:0<br>et bits provid<br>DVX comma<br>cares", so th | )]<br>de the high h<br>and, effectiv<br>he 1k addres | ely selectin | g a 256-byte | e page of R | AM. The      |

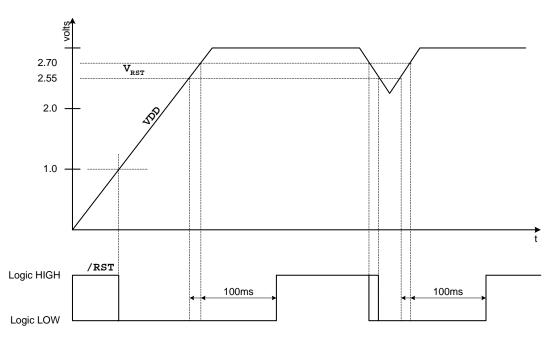

# 12.1. Power-on Reset

The CIP-51 incorporates a power supply monitor that holds the MCU in the reset state until  $V_{DD}$  rises above the VRST level during power-up. (See Figure 12.2 for timing diagram, and refer to Table 12.1 for the Electrical Characteristics of the power supply monitor circuit.) The RST pin is asserted (low) until the end of the 100msec  $V_{DD}$  Monitor timeout in order to allow the  $V_{DD}$  supply to become stable. On 48-pin packages, the  $V_{DD}$  monitor is enabled by pulling the MONEN pin high and is disabled by pulling the MONEN pin low. The MONEN pin should never be left floating. On 32-pin packages, the  $V_{DD}$  monitor is always enabled and cannot be disabled.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. All of the other reset flags in the RSTSRC Register are indeterminate. PORSF is cleared by all other resets. Since all resets cause program execution to begin at the same location (0x0000), software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset.

## 12.2. Software Forced Reset

Writing a 1 to the PORSF bit forces a Power-On Reset as described in Section 12.1.

# 12.3. Power-fail Reset

When the  $V_{DD}$  monitor is enabled, the MONEN pin (not on C8051F221/F231 32 pin parts) is "pulled high", and power-down transition or power irregularity causes  $V_{DD}$  to drop below VRST, the power supply monitor will drive the RST pin low and return the CIP-51 to the reset state (see Figure 12.2). When  $V_{DD}$  returns to a level above VRST, the CIP-51 will leave the reset state in the same manner as that for the power-on reset. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag is set, the data may no longer be valid.

## 12.4. External Reset

The external RST pin provides a means for external circuitry to force the CIP-51 into a reset state. Asserting an active-low signal on the RST pin will cause the CIP-51 to enter the reset state. Although there is a weak pull-up, it may be desirable to provide an external pull-up and/or decoupling of the RST pin to avoid erroneous noise-induced resets. The CIP-51 will remain in reset until at least 12 clock cycles after the active-low RST signal is removed. The PINRSF flag (RSTSRC.0) is set on exit from an external reset. The RST pin is 5 V tolerant.

### 12.5. Missing Clock Detector Reset

The Missing Clock Detector is essentially a one-shot circuit that is triggered by the MCU system clock. If the system clock goes away for more than 100msec, the one-shot will time out and generate a reset. After a Missing Clock Detector reset, the MCDRSF flag (RSTSRC.2) will be set, signifying the MSD as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset. Setting the MSCLKE bit in the OSCICN register (see SFR Definition 13.1) enables the Missing Clock Detector.

#### 12.6. Comparator 0 Reset

Comparator 0 can be configured as a reset input by writing a 1 to the CORSEF flag (RSTSRC.5). Comparator 0 should be enabled using CPT0CN.7 (see SFR Definition 8.1) prior to writing to CORSEF to prevent any turn-on chatter on the output from generating an unwanted reset. When configured as a reset, if the non-inverting input voltage (on CP0+) is less than the inverting input voltage (on CP0–), the MCU is put into the reset state. After a Comparator 0 Reset, the CORSEF flag (RSTSRC.5) will read 1 signifying Comparator 0 as the reset source; otherwise, this bit reads 0. The state of the RST pin is unaffected by this reset.

## 12.7. Watchdog Timer Reset

The MCU includes a programmable Watchdog Timer (WDT) running off the system clock. The WDT will force the MCU into the reset state when the watchdog timer overflows. To prevent the reset, the WDT must be restarted by application software before the overflow occurs. If the system experiences a software/hardware malfunction preventing the software from restarting the WDT, the WDT will overflow and cause a reset. This should prevent the system from running out of control.

The WDT is automatically enabled and started with the default maximum time interval on exit from all resets. If desired, the WDT can be disabled by system software or locked 'on' to prevent accidental disabling. Once locked, the WDT cannot be disabled until the next system reset. The state of the RST pin is unaffected by this reset.

#### 12.7.1. Watchdog Usage

The WDT consists of a 21-bit timer running from the programmed system clock. The timer measures the period between specific writes to its control register. If this period exceeds the programmed limit, a WDT reset is generated. The WDT can be enabled and disabled as needed in software, or can be permanently enabled if desired. Watchdog features are controlled via the Watchdog Timer Control Register (WDTCN) shown in SFR Definition 12.1.

#### Enable/Reset WDT

The watchdog timer is both enabled and reset by writing 0xA5 to the WDTCN register. The user's application software should include periodic writes of 0xA5 to WDTCN as needed to prevent a watchdog timer overflow. The WDT is enabled and reset as a result of any system reset.

| R/W      | R/W                                                                                                                                                                                                    | R/W                                          | R/W   | R/W         | R/W          | R/W          | R/W      | Reset Value |  |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------|-------------|--------------|--------------|----------|-------------|--|--|--|--|--|--|

| MSCLKE   | -                                                                                                                                                                                                      | -                                            | IFRDY | CLKSL       | IOSCEN       | IFCN1        | IFCN0    | 00000100    |  |  |  |  |  |  |

| Bit7     | Bit6                                                                                                                                                                                                   | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Addre |       |             |              |              |          |             |  |  |  |  |  |  |

|          | 0xB2                                                                                                                                                                                                   |                                              |       |             |              |              |          |             |  |  |  |  |  |  |

| Bit7:    | MSCLKE: Missing Clock Enable Bit<br>0: Missing Clock Detector Disabled<br>1: Missing Clock Detector Enabled; triggers a reset if a missing clock is detected<br>UNUSED. Read = 00b, Write = don't care |                                              |       |             |              |              |          |             |  |  |  |  |  |  |

| Bits6–5: |                                                                                                                                                                                                        |                                              |       |             |              |              |          |             |  |  |  |  |  |  |

| Bit4:    | IFRDY: Inte                                                                                                                                                                                            |                                              | •     |             | •            |              |          |             |  |  |  |  |  |  |

|          | 0: Internal                                                                                                                                                                                            |                                              |       | •           |              |              |          | 5.          |  |  |  |  |  |  |

| Dire     |                                                                                                                                                                                                        |                                              |       | • •         | eed specifie | ed by the IF | CN bits. |             |  |  |  |  |  |  |

| Bit3:    | CLKSL: Sys                                                                                                                                                                                             |                                              |       |             |              |              |          |             |  |  |  |  |  |  |

|          | 0: Uses Int                                                                                                                                                                                            |                                              |       |             |              |              |          |             |  |  |  |  |  |  |

| Bit2:    | 1: Uses Ex<br>IOSCEN: In                                                                                                                                                                               |                                              |       |             |              |              |          |             |  |  |  |  |  |  |

| DILZ.    | 0: Internal                                                                                                                                                                                            |                                              |       |             |              |              |          |             |  |  |  |  |  |  |

|          | 1: Internal                                                                                                                                                                                            |                                              |       |             |              |              |          |             |  |  |  |  |  |  |

| Bits1–0: | IFCN1-0: In                                                                                                                                                                                            |                                              |       | ancy Contro | l Rits       |              |          |             |  |  |  |  |  |  |

| Ditor 0. | 00: Interna                                                                                                                                                                                            |                                              |       | •           |              |              |          |             |  |  |  |  |  |  |

|          | 01: Interna                                                                                                                                                                                            |                                              |       |             |              |              |          |             |  |  |  |  |  |  |

|          | 10: Interna                                                                                                                                                                                            |                                              |       |             |              |              |          |             |  |  |  |  |  |  |

|          | 11: Internal Oscillator typical frequency is 16 MHz.                                                                                                                                                   |                                              |       |             |              |              |          |             |  |  |  |  |  |  |

|          |                                                                                                                                                                                                        |                                              | ··· · | -           |              |              |          |             |  |  |  |  |  |  |

# SFR Definition 13.1. OSCICN: Internal Oscillator Control

# **Table 13.1. Internal Oscillator Electrical Characteristics**

-40 to +85 ×C unless otherwise specified.

| Parameter                                                        | Conditions        | Min | Тур | Max | Units  |

|------------------------------------------------------------------|-------------------|-----|-----|-----|--------|

| Internal Oscillator Frequency                                    | OSCICN.[1:0] = 00 | 1.5 | 2.0 | 2.5 | MHz    |

|                                                                  | OSCICN.[1:0] = 01 | 3.0 | 4.0 | 5.0 |        |

|                                                                  | OSCICN.[1:0] = 10 | 6.0 | 8.0 | 10  |        |

|                                                                  | OSCICN.[1:0] = 11 | 12  | 16  | 20  |        |

| Internal Oscillator Current Consumption                          | OSCICN.2 = 1      | —   | 200 | _   | μA     |

| Internal Oscillator Temperature Stability                        |                   | —   | 4   | _   | ppm/°C |

| Internal Oscillator Power Supply (V <sub>DD</sub> )<br>Stability |                   | _   | 6.4 | _   | %/V    |

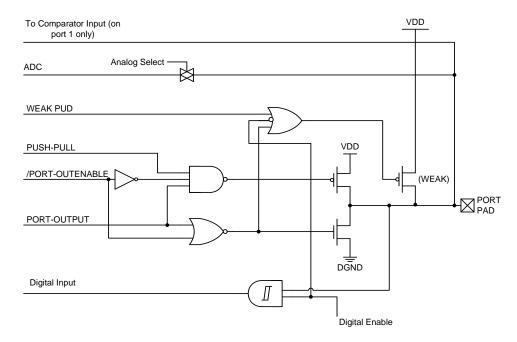

Figure 14.1. Port I/O Functional Block Diagram

| R/W    | R/W                                            | R/W                    | R/W     | R/W     | R/W       | R | R/W    | Reset Value |  |  |  |  |  |

|--------|------------------------------------------------|------------------------|---------|---------|-----------|---|--------|-------------|--|--|--|--|--|

| T2EXE  | T2E                                            | T1E                    | T0E     | INT1E   | INT0E     | - | UARTEN | 00000000    |  |  |  |  |  |

| Bit7   | Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0 SFR Address |                        |         |         |           |   |        |             |  |  |  |  |  |

|        | 0xE1                                           |                        |         |         |           |   |        |             |  |  |  |  |  |

|        |                                                |                        |         |         |           |   |        |             |  |  |  |  |  |

| Bit7:  |                                                | T2EXE: T2EX Enable Bit |         |         |           |   |        |             |  |  |  |  |  |

|        | 0: T2EX ur                                     |                        | •       |         |           |   |        |             |  |  |  |  |  |

| Dire   | 1: T2EX ro                                     |                        | t Pin.  |         |           |   |        |             |  |  |  |  |  |

| Bit6:  | T2E: T2 En                                     |                        |         |         |           |   |        |             |  |  |  |  |  |

|        | 0: T2 unav                                     |                        | •       |         |           |   |        |             |  |  |  |  |  |

| Dite   | 1: T2 route                                    |                        | n.      |         |           |   |        |             |  |  |  |  |  |

| Bit5:  | T1E: T1 En                                     |                        | t :     |         |           |   |        |             |  |  |  |  |  |

|        | 0: T1 unav<br>1: T1 route                      |                        |         |         |           |   |        |             |  |  |  |  |  |

| Bit4:  | TOE: TO En                                     |                        | n.      |         |           |   |        |             |  |  |  |  |  |

| ЫЦ4.   |                                                |                        | ort nin |         |           |   |        |             |  |  |  |  |  |

|        | 0: T0 unava<br>1: T0 route                     |                        | •       |         |           |   |        |             |  |  |  |  |  |

| Bit3:  | INT1E: /INT                                    |                        |         |         |           |   |        |             |  |  |  |  |  |

| DII.3. | 0: /INT1 un                                    |                        |         |         |           |   |        |             |  |  |  |  |  |

|        | 1: /INT1 ro                                    |                        | •       |         |           |   |        |             |  |  |  |  |  |

| Bit2:  | INTOE: /INT                                    |                        | •       |         |           |   |        |             |  |  |  |  |  |

| DILZ.  | 0: /INT0 un                                    |                        |         |         |           |   |        |             |  |  |  |  |  |

|        | 1: /INT0 ro                                    |                        |         |         |           |   |        |             |  |  |  |  |  |

| Bit1:  | UNUSED.                                        |                        |         | t care. |           |   |        |             |  |  |  |  |  |

| Bit0:  | UARTEN: L                                      |                        |         |         |           |   |        |             |  |  |  |  |  |

|        | 0: UART I/C                                    |                        |         | ns.     |           |   |        |             |  |  |  |  |  |

|        | 1: TX, RX r                                    |                        |         |         | ectively. |   |        |             |  |  |  |  |  |

|        | ,                                              |                        |         | ,       | - 1       |   |        |             |  |  |  |  |  |

|        |                                                |                        |         |         |           |   |        |             |  |  |  |  |  |

# SFR Definition 14.1. PRT0MX: Port I/O MUX Register 0

# 14.2. General Purpose Port I/O

Each I/O port is accessed through a corresponding special function register (SFR) that is both byte addressable and bit addressable. When writing to a port, the value written to the SFR is latched to maintain the output data value at each pin. When reading, the logic levels of the port's input pins are returned regardless of the PRTnMX settings (i.e., even when the pin is assigned to another signal by the MUX, the Port Register can always still read its corresponding Port I/O pin), provided its pin is configured for digital input mode. The exception to this is the execution of the *read-modify-write* instructions. The *read-modify-write* instructions when operating on a port SFR are the following: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ and MOV, CLR or SETB, when the destination is an individual bit in a port SFR. For these instructions, the value of the register (not the pin) is read, modified, and written back to the SFR.

| R/W                                                                                                                                                                                                                                                                                                                                                                                              | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W               | Reset Value  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|-------------------|--------------|--|

| P0.7                                                                                                                                                                                                                                                                                                                                                                                             | P0.6 | P0.5 | P0.4 | P0.3 | P0.2 | P0.1 | P0.0              | 11111111     |  |

| Bit7                                                                                                                                                                                                                                                                                                                                                                                             | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0              | SFR Address: |  |

|                                                                                                                                                                                                                                                                                                                                                                                                  |      |      |      |      |      |      | (bit addressable) | 0x80         |  |

| <ul> <li>Bits7–0: P0.[7:0]</li> <li>(Write - Output appears on I/O pins per PRT0MX, PRT1MX, and PRT2MX Registers)</li> <li>0: Logic Low Output.</li> <li>1: Logic High Output (high impedance if corresponding PRT0CF.n bit = 0)</li> <li>(Read - Regardless of PRT0MX, PRT1MX, and PRT2MX Register settings).</li> <li>0: P0.n pin is logic low.</li> <li>1: P0.n pin is logic high.</li> </ul> |      |      |      |      |      |      |                   |              |  |

# SFR Definition 14.4. P0: Port0 Register

# SFR Definition 14.5. PRT0CF: Port0 Configuration Register

| R/W      | R/W                                              | R/W          | R/W          | R/W          | R/W          | R/W          | R/W  | Reset Value |  |  |

|----------|--------------------------------------------------|--------------|--------------|--------------|--------------|--------------|------|-------------|--|--|

|          |                                                  |              |              |              |              |              |      | 00000000    |  |  |

| Bit7     | Bit6                                             | Bit5         | Bit4         | Bit3         | Bit2         | Bit1         | Bit0 | SFR Address |  |  |

|          |                                                  |              |              |              |              |              |      | 0xA4        |  |  |

| Bits7–0: | PRT0CF.[7:                                       | 0]: Output ( | Configuratio | n Bits for P | ).7–P0.0 (re | espectively) |      |             |  |  |

|          | 0: Corresponding P0.n Output mode is Open-Drain. |              |              |              |              |              |      |             |  |  |

|          |                                                  |              | •            | de is Push-  |              |              |      |             |  |  |

| SFR Definition | 15.2. | SPI0CN: | SPI | Control |

|----------------|-------|---------|-----|---------|

|----------------|-------|---------|-----|---------|

| R/W   | R/W                                                                                                                                                                                                                                                                                                                                                           | R/W                                                                                                                                                                                                                                                            | R/W         | R     | R      | R/W   | R/W   | Reset Value          |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|--------|-------|-------|----------------------|--|--|--|--|

| SPIF  | WCOL                                                                                                                                                                                                                                                                                                                                                          | MODF                                                                                                                                                                                                                                                           | RXOVRN      | TXBSY | SLVSEL | MSTEN | SPIEN | 00000000             |  |  |  |  |

| Bit7  | Bit6                                                                                                                                                                                                                                                                                                                                                          | Bit5                                                                                                                                                                                                                                                           | Bit4        | Bit3  | Bit2   | Bit1  | Bit0  | SFR Address:<br>0xF8 |  |  |  |  |

| Bit7: | SPIF: SPI Interrupt Flag.<br>This bit is set to logic 1 by hardware at the end of a data transfer. If interrupts are enabled, setting this bit causes the CPU to vector to the SPI0 interrupt service routine. This bit is not automatically cleared by hardware. It must be cleared by software.                                                             |                                                                                                                                                                                                                                                                |             |       |        |       |       |                      |  |  |  |  |

| Bit6: | WCOL: Write Collision Flag.<br>This bit is set to logic 1 by hardware (and generates a SPI interrupt) to indicate a write to the<br>SPI data register was attempted while a data transfer was in progress. It is cleared by soft-<br>ware.                                                                                                                    |                                                                                                                                                                                                                                                                |             |       |        |       |       |                      |  |  |  |  |

| Bit5: | This bit is s collision is a                                                                                                                                                                                                                                                                                                                                  | MODF: Mode Fault Flag.<br>This bit is set to logic 1 by hardware (and generates a SPI interrupt) when a master mode<br>collision is detected (NSS is low and MSTEN = 1). This bit is not automatically cleared by<br>hardware. It must be cleared by software. |             |       |        |       |       |                      |  |  |  |  |

| Bit4: | RXOVRN: Receive Overrun Flag.<br>This bit is set to logic 1 by hardware (and generates a SPI interrupt) when the receive buffer<br>still holds unread data from a previous transfer and the last bit of the current transfer is<br>shifted into the SPI shift register. This bit is not automatically cleared by hardware. It must<br>be cleared by software. |                                                                                                                                                                                                                                                                |             |       |        |       |       |                      |  |  |  |  |

| Bit3: | This bit is s                                                                                                                                                                                                                                                                                                                                                 | TXBSY: Transmit Busy Flag.<br>This bit is set to logic 1 by hardware while a master mode transfer is in progress. It is cleared by hardware at the end of the transfer.                                                                                        |             |       |        |       |       |                      |  |  |  |  |

| Bit2: | SLVSEL: Slave Selected Flag.<br>This bit is set to logic 1 whenever the NSS pin is low indicating it is enabled as a slave. It is<br>cleared to logic 0 when NSS is high (slave disabled).                                                                                                                                                                    |                                                                                                                                                                                                                                                                |             |       |        |       |       |                      |  |  |  |  |

| Bit1: | MSTEN: Master Mode Enable.<br>0: Disable master mode. Operate in slave mode.<br>1: Enable master mode. Operate as a master.                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                |             |       |        |       |       |                      |  |  |  |  |

| Bit0: | SPIEN: SP<br>This bit ena<br>0: SPI disal<br>1: SPI enab                                                                                                                                                                                                                                                                                                      | ables/disable<br>bled.                                                                                                                                                                                                                                         | es the SPI. |       |        |       |       |                      |  |  |  |  |

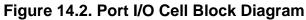

#### 16.1.3. Mode 2: 9-Bit UART, Fixed Baud Rate

Mode 2 provides asynchronous, full-duplex communication using a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit (see timing diagram in Figure 16.6). On transmit, the ninth data bit is determined by the value in TB8 (SCON.3). It can be assigned the value of the parity flag P in the PSW or used in multiprocessor communications. On receive, the ninth data bit goes into RB8 (SCON.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF register. The TI Transmit Interrupt Flag (SCON.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN Receive Enable bit (SCON.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF receive register if the following conditions are met: RI must be logic 0, and if SM2 is logic 1, the 9th bit must be logic 1.

If these conditions are met, the eight bits of data is stored in SBUF, the ninth bit is stored in RB8 and the RI flag is set. If these conditions are not met, SBUF and RB8 will not be loaded and the RI flag will not be set. An interrupt will occur if enabled when either TI or RI are set.

The baud rate in Mode 2 is a direct function of the system clock frequency as follows:

#### Mode 2 Baud Rate = 2SMOD x (SYSCLK / 64).

The SMOD bit (PCON.7) selects whether to divide SYSCLK by 32 or 64. In the formula, 2 is raised to the power SMOD, resulting in a baud rate of either 1/32 or 1/64 of the system clock frequency. On reset, the SMOD bit is logic 0, thus selecting the lower speed baud rate by default.

## Figure 16.6. UART Modes 2 and 3 Timing Diagram

#### 16.1.4. Mode 3: 9-Bit UART, Variable Baud Rate

Mode 3 is the same as Mode 2 in all respects except the baud rate is variable. The baud rate is determined in the same manner as for Mode 1. Mode 3 operation transmits 11 bits: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. Timer 1 or Timer 2 overflows generate the baud rate just as with Mode 1. In summary, Mode 3 transmits using the same protocol as Mode 2 but with Mode 1 baud rate generation.

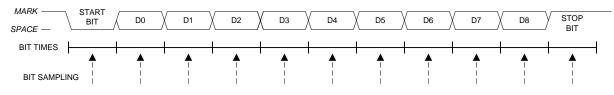

#### 17.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. The TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0. Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0.

Figure 17.2. T0 Mode 2 Block Diagram

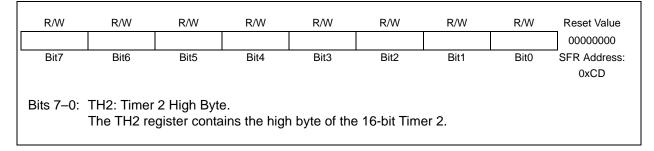

# SFR Definition 17.8. T2CON: Timer 2 Control

| R/W   | R/W                                                                                                                                            | R/W                                                                                                                                                                                              | R/W          | R/W             | R/W          | R/W          | R/W                               | Reset Value   |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|--------------|--------------|-----------------------------------|---------------|--|--|--|--|

| TF2   | EXF2                                                                                                                                           | RCLK                                                                                                                                                                                             | TCLK         | EXEN2           | TR2          | C/T2         | CP/RL2                            | 00000000      |  |  |  |  |

| Bit7  | Bit6                                                                                                                                           | Bit5                                                                                                                                                                                             | Bit4         | Bit3            | Bit2         | Bit1         | Bit0                              | SFR Address:  |  |  |  |  |

|       |                                                                                                                                                |                                                                                                                                                                                                  |              |                 |              |              | (bit addressable                  | e) 0xC8       |  |  |  |  |

|       |                                                                                                                                                |                                                                                                                                                                                                  |              |                 |              |              |                                   |               |  |  |  |  |

| Bit7: |                                                                                                                                                | r 2 Overflow                                                                                                                                                                                     |              |                 |              |              |                                   |               |  |  |  |  |

|       |                                                                                                                                                |                                                                                                                                                                                                  |              |                 |              |              | When the T                        |               |  |  |  |  |

|       | •                                                                                                                                              |                                                                                                                                                                                                  |              |                 |              |              | ner 2 interrupt                   |               |  |  |  |  |

|       | tine. This bit is not automatically cleared by hardware and must be cleared by softw<br>TF2 will not be set when RCLK and/or TCLK are logic 1. |                                                                                                                                                                                                  |              |                 |              |              |                                   |               |  |  |  |  |

| Bit6: |                                                                                                                                                | er 2 Externa                                                                                                                                                                                     |              | anu/or tolr     | are logic    | 1.           |                                   |               |  |  |  |  |

| Dito. |                                                                                                                                                |                                                                                                                                                                                                  | 0            | anture or re    | load is cau  | sed by a hid | gh-to-low tran                    | sition on the |  |  |  |  |

|       |                                                                                                                                                |                                                                                                                                                                                                  |              |                 |              |              | is enabled, se                    |               |  |  |  |  |

|       |                                                                                                                                                |                                                                                                                                                                                                  |              |                 |              |              | This bit is no                    |               |  |  |  |  |

|       |                                                                                                                                                |                                                                                                                                                                                                  |              | nust be clear   | •            |              |                                   |               |  |  |  |  |

| Bit5: |                                                                                                                                                | ceive Clock                                                                                                                                                                                      |              |                 |              |              |                                   |               |  |  |  |  |

|       |                                                                                                                                                |                                                                                                                                                                                                  |              | he UART's r     | eceive cloo  | ck in modes  | s 1 or 3.                         |               |  |  |  |  |