Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                             |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SPI, UART/USART                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                |

| Number of I/O              | 22                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 22x8b                                                       |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 32-LQFP                                                         |

| Supplier Device Package    | 32-LQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f221-gqr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

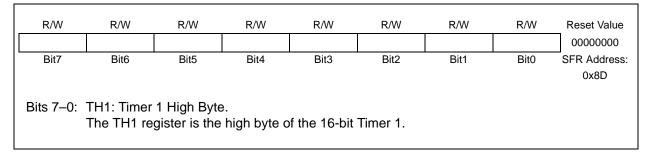

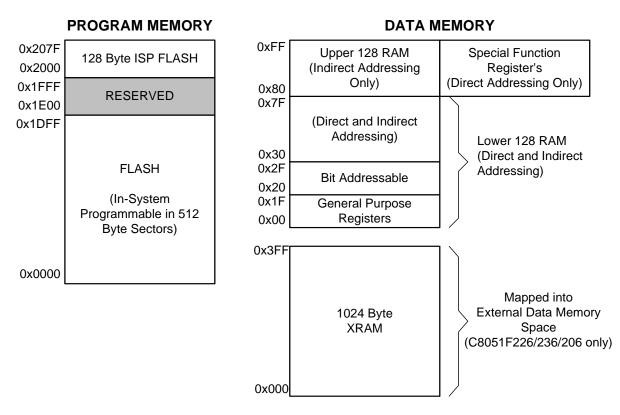

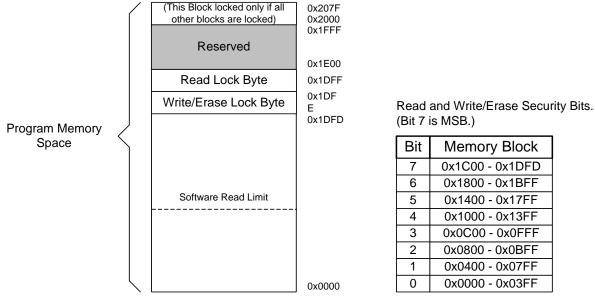

Figure 1.7. On-Board Memory Map

#### 1.3. JTAG

The C8051F2xx have on-chip JTAG and debug logic that provide non-intrusive, full speed, in-circuit debug using the production part installed in the end application using the four-pin JTAG I/F. The C8051F2xxDK is a development kit with all the hardware and software necessary to develop application code and perform in-circuit debug with the C8051F2xx. The kit includes software with a developer's studio and debugger, an integrated 8051 assembler, and an RS-232 to JTAG interface module referred to as the EC. It also has a target application board with a C8051F2xx installed and large prototyping area, plus the RS-232 and JTAG cables, and wall-mount power supply. The Development Kit requires a Windows OS (Windows 95 or later) computer with one available RS-232 serial port. As shown in Figure 1.8, the PC is connected via RS-232 to the EC. A six-inch ribbon cable connects the EC to the user's application board. It requires roughly 20 mA at 2.7–3.6 V. For applications where there is not sufficient power available from the target board, the provided power supply can be connected directly to the EC.

This is a vastly superior configuration for developing and debugging embedded applications compared to standard MCU Emulators, which use on-board "ICE Chips" and target cables and require the MCU in the application board to be socketed. Silicon Labs' debug environment both increases ease of use, and preserves the performance of the precision analog peripherals.

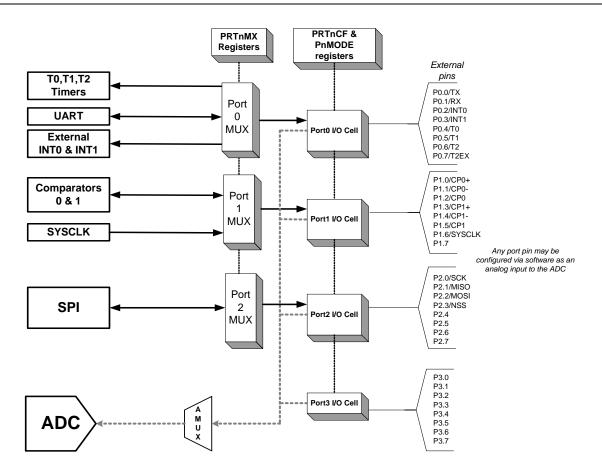

Figure 1.9. Port I/O Functional Block Diagram

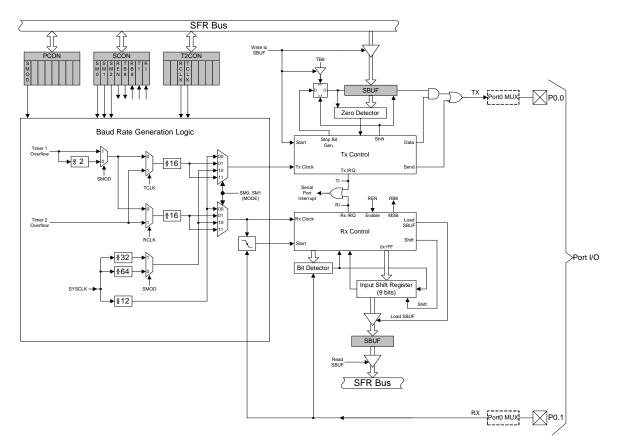

#### 1.5. Serial Ports

The C8051F206, C8051F220/1/6 and C8051F230/1/6 include a Full-Duplex UART and SPI Bus. Each of the serial buses is fully implemented in hardware and makes extensive use of the CIP-51's interrupts, thus requiring very little intervention by the CPU. The serial buses do not have to "share" resources such as timers, interrupts, or Port I/O, so both of the serial buses may be used simultaneously. (You may use Timer1, Timer 2, or SYSCLK to generate baud rates for UART).

#### 1.6. Analog to Digital Converter

The C8051F220/1/6 has an on-chip 8-bit SAR ADC and the C8051F206 has a 12-bit SAR ADC with a programmable gain amplifier. With a maximum throughput of 100ksps, the ADC offers true 8-bit with an INL of  $\pm$ 1/4 LSB, and or 12-bit accuracy with  $\pm$ 2 LSB. The voltage reference can be the power supply (V<sub>DD</sub>), or an external reference voltage (VREF). Also, the system controller can place the ADC into a power-saving shutdown mode when not in use. A programmable gain amplifier follows the analog multiplexer. The gain can be set in software from 0.5 to 16 in powers of 2.

Conversions can be initiated in two ways; a software command or an overflow on Timer 2. This flexibility allows the start of conversion to be triggered by software events, or convert continuously. A completed conversion causes an interrupt, or a status bit can be polled in software to determine the end of conversion. The resulting 8-bit data word is latched into an SFR upon completion of a conversion.

## Table 5.1. 8-Bit ADC Electrical Characteristics

VDD = 3.0 V, VREF = 2.40 V, PGA Gain = 1, -40 to +85 ×C unless otherwise specified.

| Parameter                        | Conditions                         | Min       | Тур     | Max             | Units  |

|----------------------------------|------------------------------------|-----------|---------|-----------------|--------|

| DC Accuracy                      |                                    | •         |         |                 | •      |

| Resolution                       |                                    |           | 8       | —               | bits   |

| Integral Nonlinearity            |                                    |           | —       | ±1/2            | LSB    |

| Differential Nonlinearity        | Guaranteed Monotonic               | _         | —       | ±1/2            | LSB    |

| Offset Error                     |                                    | ±2        | —       | ±1/2            | LSB    |

| Gain Error                       |                                    | ±2        | —       | ±1/2            | LSB    |

| Offset Temperature Coefficient   |                                    |           | ±0.25   | _               | ppm/°C |

| Dynamic Performance (10 kHz sine | wave input, 0 to –1 dB of full     | scale, 10 | 0 ksps) |                 |        |

| Signal-to-Noise Plus Distortion  |                                    | 49.5      | —       | _               | dB     |

| Total Harmonic Distortion        | Up to the 5 <sup>th</sup> harmonic | -60       | -65     | _               | dB     |

| Spurious-Free Dynamic Range      |                                    |           | -65     | _               | dB     |

| Conversion Rate                  |                                    | •         |         |                 | •      |

| Conversion Time in SAR Clocks    |                                    | 16        | —       | —               | clocks |

| SAR Clock Frequency              |                                    |           | —       | 2.5             | MHz    |

| Track/Hold Acquisition Time      |                                    | 1.5       | —       | _               | μs     |

| Throughput Rate                  |                                    | _         | —       | 100             | ksps   |

| Analog Inputs                    | ·                                  |           |         |                 |        |

| Input Voltage Range              |                                    | 0         | —       | V <sub>DD</sub> | V      |

| Input Capacitance                |                                    |           | 10      | _               | pF     |

| Power Specifications             |                                    |           |         |                 |        |

| Power Supply Current             | Operating Mode, 100 ksps           |           | 0.45    | 1.0             | mA     |

| Power Supply Current in Shutdown |                                    |           | 0.1     | 1               | μA     |

| Power Supply Rejection           |                                    |           | ±0.3    |                 | mV/V   |

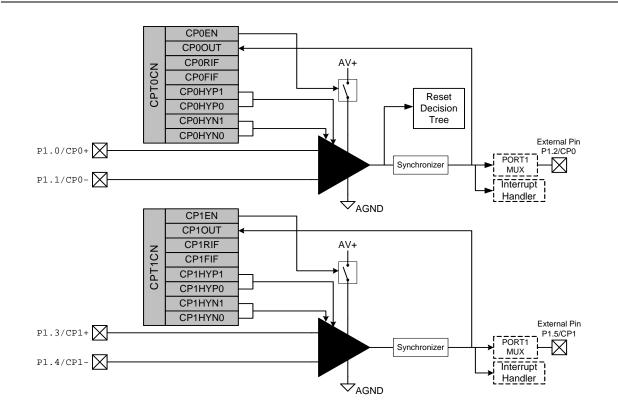

Figure 8.1. Comparator Functional Block Diagram

## Table 9.3. Special Function Registers

#### SFR's are listed in alphabetical order.

| Address | Register             | Description                            | Page No. |

|---------|----------------------|----------------------------------------|----------|

| 0xE0    | ACC                  | Accumulator                            | 73       |

| 0xBC    | ADC0CF               | ADC Configuration                      | 35       |

| 0xE8    | ADC0CN               | ADC Control                            | 36       |

| 0xC5    | ADC0GTH <sup>1</sup> | ADC Greater-Than Data Word (High Byte) | 37       |

| 0xC4    | ADC0GTL <sup>4</sup> | ADC Greater-Than Data Word (Low Byte)  | 46       |

| 0xBF    | ADC0H <sup>1</sup>   | ADC Data Word (High Byte)              | 37       |

| 0xBE    | ADC0L <sup>4</sup>   | ADC Data Word (Low Byte)               | 45       |

| 0xC7    | ADC0LTH <sup>1</sup> | ADC Less-Than Data Word (High Byte)    | 46       |

| 0xCE    | ADC0LTL <sup>4</sup> | ADC Less-Than Data Word (Low Byte)     | 47       |

| 0xBB    | AMX0SL               | ADC MUX Channel Selection              | 34       |

| 0xF0    | В                    | B Register                             | 73       |

| 0x8E    | CKCON                | Clock Control                          | 131      |

| 0x9E    | CPT0CN               | Comparator 0 Control                   | 55       |

| 0x9F    | CPT1CN               | Comparator 1 Control                   | 56       |

| 0x83    | DPH                  | Data Pointer (High Byte)               | 71       |

| 0x82    | DPL                  | Data Pointer (Low Byte)                | 71       |

| 0xE6    | EIE1                 | Extended Interrupt Enable 1            | 79       |

| 0xE7    | EIE2                 | Extended Interrupt Enable 2            | 80       |

| 0xF6    | EIP1                 | External Interrupt Priority 1          | 81       |

| 0xF7    | EIP2                 | External Interrupt Priority 2          | 82       |

| 0xAF    | EMI0CN <sup>3</sup>  | External Memory Interface Control      | 90       |

| 0xB7    | FLACL                | Flash Memory Read Limit                | 89       |

| 0xB6    | FLSCL                | Flash Memory Timing Prescaler          | 89       |

| 0xA8    | IE                   | Interrupt Enable                       | 77       |

| 0xB8    | IP                   | Interrupt Priority Control             | 78       |

| 0xB2    | OSCICN               | Internal Oscillator Control            | 98       |

| 0xB1    | OSCXCN               | External Oscillator Control            | 99       |

| 0x80    | P0                   | Port 0 Latch                           | 105      |

| 0x90    | P1                   | Port 1 Latch                           | 106      |

| 0xA0    | P2                   | Port 2 Latch                           | 107      |

| 0xB0    | P3                   | Port 3 Latch                           | 108      |

| 0xF1    | P0MODE               | Port0 Digital/Analog Output Mode       | 106      |

| 0xF2    | P1MODE               | Port1 Digital/Analog Output Mode       | 107      |

| 0xF3    | P2MODE               | Port2 Digital/Analog Output Mode       | 108      |

| 0xF4    | P3MODE <sup>2</sup>  | Port3 Digital/Analog Output Mode       | 109      |

| 0x87    | PCON                 | Power Control                          | 84       |

#### 9.4.6. Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described below. Refer to the datasheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

#### SFR Definition 9.8. IE: Interrupt Enable

| R/W      | R/W                                      | R/W                            | R/W         | R/W            | R/W           | R/W            | R/W             | Reset Value  |

|----------|------------------------------------------|--------------------------------|-------------|----------------|---------------|----------------|-----------------|--------------|

| EA       | -                                        | ET2                            | ES          | ET1            | EX1           | ET0            | EX0             | 00000000     |

| Bit7     | Bit6                                     | Bit5                           | Bit4        | Bit3           | Bit2          | Bit1           | Bit0            | SFR Address  |

|          |                                          |                                |             |                |               | (              | bit addressable | e) 0xA8      |

| Bit7:    |                                          | e All Interru                  |             |                |               |                |                 |              |

|          | -                                        | bally enable                   | es/disables | s all interrup | ots. It overr | ides the indiv | vidual interro  | upt mask set |

|          | tings.                                   | all interrupt                  | courcoc     |                |               |                |                 |              |

|          |                                          | each interru                   |             | ng to its ind  | ividual mas   | k setting.     |                 |              |

| Dire     |                                          |                                |             |                |               | Ū              |                 |              |

| Bit6:    | UNUSED.                                  | Read = $0,$                    | Write = do  | n't care.      |               |                |                 |              |

| Bit5:    |                                          | le Timer 2 l                   |             |                |               |                |                 |              |

|          |                                          | ts the maski                   |             |                | rrupt.        |                |                 |              |

|          |                                          | all Timer 2                    |             |                | he TF2 flag   | (T2CON.7)      |                 |              |

|          |                                          | interrupt iet                  |             | icrated by t   | no ni z nay   | (1200N.7)      |                 |              |

| Bit4:    |                                          | e Serial Por                   | · · ·       |                | , .           |                |                 |              |

|          |                                          | ts the maski                   |             | Serial Port (  | UART) inte    | errupt.        |                 |              |

|          |                                          | all UART ir                    |             | erated by t    | he R1 flag    | (SCON.0) or    | T1 flag (SC     | ON.1).       |

|          |                                          | -                              |             | ,              | 0             | · · · · ·      | 5.              | ,            |

| Bit3:    |                                          | le Timer 1 l<br>ts the maski   |             | Fimor 1 into   | rrupt         |                |                 |              |

|          |                                          | all Timer 1                    |             |                | nupi.         |                |                 |              |

|          |                                          | interrupt ree                  |             |                | he TF1 flag   | (TCON.7).      |                 |              |

| Bit2:    | EX1: Enab                                | le External                    | Interrunt 1 |                |               |                |                 |              |

| DILL.    |                                          | ts the maski                   |             |                | ot 1.         |                |                 |              |

|          |                                          | external int                   | •           |                |               |                |                 |              |

|          | 1: Enable                                | interrupt ree                  | quests ger  | erated by t    | he /INT1 pi   | n.             |                 |              |

| Bit1:    | ET0: Enab                                | le Timer 0 l                   | nterrupt.   |                |               |                |                 |              |

| 0 F' '   |                                          | ts the mask                    | •           | Fimer 0 inte   | rrupt.        |                |                 |              |

| U: Disat | ole all Timer (<br>1 <sup>.</sup> Enable | 0 interrupts.<br>interrupt ree |             | erated by t    | he TF0 flag   |                |                 |              |

|          |                                          | interrupt ret                  | 140010 901  |                |               |                |                 |              |

| Bit0:    |                                          | le External                    | •           |                |               |                |                 |              |

|          |                                          | ts the maski<br>external int   |             | rnal interrup  | ot 0.         |                |                 |              |

|          |                                          | interrupt re                   |             | erated by t    | he /INT0 pi   | n.             |                 |              |

|          |                                          |                                |             | / -            |               |                |                 |              |

#### 9.5. Power Management Modes

The CIP-51 core has two software programmable power management modes: Idle and Stop. Idle mode halts the CPU while leaving the external peripherals and internal clocks active. In Stop mode, the CPU is halted, all interrupts and timers (except the Missing Clock Detector) are inactive, and the system clock is stopped. Since clocks are running in Idle mode, power consumption is dependent upon the system clock frequency and the number of peripherals left in active mode before entering Idle. Stop mode consumes the least power. SFR Definition 9.14 describes the Power Control Register (PCON) used to control the CIP-51's power management modes.

Although the CIP-51 has Idle and Stop modes built in (as with any standard 8051 architecture), power management of the entire MCU is better accomplished by enabling/disabling individual peripherals as needed. Each analog peripheral can be disabled when not in use and put into low power mode. Turning off the active oscillator saves even more power, but requires a reset to restart the MCU.

#### 9.5.1. Idle Mode

Setting the Idle Mode Select bit (PCON.0) causes the CIP-51 to halt the CPU and enter Idle mode as soon as the instruction that sets the bit completes. All internal registers and memory maintain their original data. All analog and digital peripherals can remain active during Idle mode.

Idle mode is terminated when an enabled interrupt or RST is asserted. The assertion of an enabled interrupt will cause the Idle Mode Selection bit (PCON.0) to be cleared and the CPU will resume operation. The pending interrupt will be serviced and the next instruction to be executed after the return from interrupt (RETI) will be the instruction immediately following the one that set the Idle Mode Select bit. If Idle mode is terminated by an internal or external reset, the CIP-51 performs a normal reset sequence and begins program execution at address 0x0000.

Note: If the instruction following the write of the IDLE bit is a single-byte instruction and an interrupt occurs during the execution phase of the instruction that sets the IDLE bit, the CPU may not wake from Idle mode when a future interrupt occurs. Any instructions that set the IDLE bit should be followed by an instruction that has 2 or more op-code bytes, for example:

| // in 'C':<br>PCON  = 0x01;<br>PCON = PCON;        | // set IDLE bit<br>// followed by a 3-cycle dummy instruction |

|----------------------------------------------------|---------------------------------------------------------------|

| ; in assembly:<br>ORL PCON, #01h<br>MOV PCON, PCON | ; set IDLE bit<br>; followed by a 3-cycle dummy instruction   |

If enabled, the WDT will eventually cause an internal watchdog reset and thereby terminate the Idle mode. This feature protects the system from an unintended permanent shutdown in the event of an inadvertent write to the PCON register. If this behavior is not desired, the WDT may be disabled by software prior to entering the Idle mode if the WDT was initially configured to allow this operation. This provides the opportunity for additional power savings, allowing the system to remain in the Idle mode indefinitely, waiting for an external stimulus to wake up the system. Refer to Section 12.7 Watchdog Timer for more information on the use and configuration of the WDT.

#### 9.5.2. Stop Mode

Setting the Stop Mode Select bit (PCON.1) causes the CIP-51 to enter Stop mode as soon as the instruction that sets the bit completes. In Stop mode, the CPU and oscillators are stopped, effectively shutting

down all digital peripherals. Each analog peripheral must be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to sleep for longer than the MCD timeout of  $100\mu$ sec.

| R/W                                                                                                                                                                                                                                                                                                   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--------------|

| SMOD                                                                                                                                                                                                                                                                                                  | GF4  | GF3  | GF2  | GF1  | GF0  | STOP | IDLE | 00000000     |

| Bit7                                                                                                                                                                                                                                                                                                  | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|                                                                                                                                                                                                                                                                                                       |      |      |      |      |      |      |      | 0x87         |

| <ul> <li>Bit7: SMOD: Serial Port Baud Rate Doubler Enable.</li> <li>0: Serial Port baud rate is that defined by Serial Port Mode in SCON.</li> <li>1: Serial Port baud rate is double that defined by Serial Port Mode in SCON.</li> </ul>                                                            |      |      |      |      |      |      |      |              |

| Bits6–2: GF4–GF0: General Purpose Flags 4–0.<br>These are general purpose flags for use under software control.                                                                                                                                                                                       |      |      |      |      |      |      |      |              |

| <ul> <li>Bit1: STOP: Stop Mode Select.</li> <li>Setting this bit will place the CIP-51 in Stop mode. This bit will always be read as 0.</li> <li>1: Goes into power down mode. (Turns off internal oscillator).</li> </ul>                                                                            |      |      |      |      |      |      |      |              |

| <ul> <li>Bit0: IDLE: Idle Mode Select.</li> <li>Setting this bit will place the CIP-51 in Idle mode. This bit will always be read as 0.</li> <li>1: Goes into idle mode. (Shuts off clock to CPU, but clock to Timers, Interrupts, Serial Ports, and Analog Peripherals are still active.)</li> </ul> |      |      |      |      |      |      |      |              |

#### SFR Definition 9.14. PCON: Power Control Register

Flash Read Lock Byte

Bits7–0: Each bit locks a corresponding block of memory. (Bit 7 is MSB.)

0: Read operations are locked (disabled) for corresponding block across the JTAG interface.

1: Read operations are unlocked (enabled) for corresponding block across the JTAG interface.

Flash Write/Erase Lock Byte

Bits7–0: Each bit locks a corresponding block of memory.

0: Write/Erase operations are locked (disabled) for corresponding block across the JTAG interface.

1: Write/Erase operations are unlocked (enabled) for corresponding block across the JTAG interface.

Flash Access Limit Register (FLACL)

The content of this register is used as the high byte of the 16-bit software read limit address. The 16-bit read limit address value is calculated as 0xNN00 where NN is replaced by content of this register on reset. Software running at or above this address is prohibited from using the MOVX and MOVC instructions to read, write, or erase, locations below this address. Any attempts to read locations below this limit will return the value 0x00.

#### Figure 10.1. Flash Program Memory Security Bytes

The lock bits can always be read and cleared to logic 0 regardless of the security setting applied to the block containing the security bytes. This allows additional blocks to be protected after the block containing the security bytes has been locked. However, the only means of removing a lock once set is to erase the entire program memory space by performing a JTAG erase operation. NOTE: Erasing the Flash memory block containing the security bytes will automatically initiate erasure of the entire program memory space (except for the reserved area). This erasure can only be performed via the JTAG. If a non-security byte in the 0x1C00–0x1DFF page is written to in order to perform an erasure of that page, then that page including the security bytes will be erased.

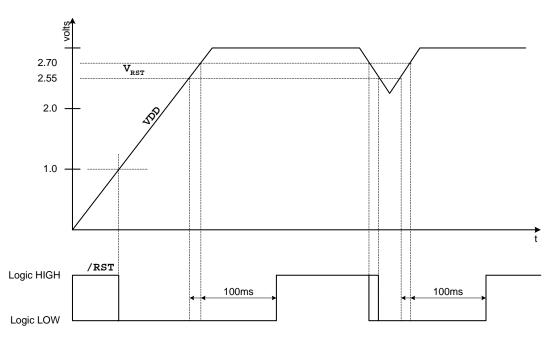

#### 12.1. Power-on Reset

The CIP-51 incorporates a power supply monitor that holds the MCU in the reset state until  $V_{DD}$  rises above the VRST level during power-up. (See Figure 12.2 for timing diagram, and refer to Table 12.1 for the Electrical Characteristics of the power supply monitor circuit.) The RST pin is asserted (low) until the end of the 100msec  $V_{DD}$  Monitor timeout in order to allow the  $V_{DD}$  supply to become stable. On 48-pin packages, the  $V_{DD}$  monitor is enabled by pulling the MONEN pin high and is disabled by pulling the MONEN pin low. The MONEN pin should never be left floating. On 32-pin packages, the  $V_{DD}$  monitor is always enabled and cannot be disabled.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic 1. All of the other reset flags in the RSTSRC Register are indeterminate. PORSF is cleared by all other resets. Since all resets cause program execution to begin at the same location (0x0000), software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset.

#### 12.2. Software Forced Reset

Writing a 1 to the PORSF bit forces a Power-On Reset as described in Section 12.1.

#### 12.3. Power-fail Reset

When the  $V_{DD}$  monitor is enabled, the MONEN pin (not on C8051F221/F231 32 pin parts) is "pulled high", and power-down transition or power irregularity causes  $V_{DD}$  to drop below VRST, the power supply monitor will drive the RST pin low and return the CIP-51 to the reset state (see Figure 12.2). When  $V_{DD}$  returns to a level above VRST, the CIP-51 will leave the reset state in the same manner as that for the power-on reset. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag is set, the data may no longer be valid.

### SFR Definition 14.2. PRT1MX: Port I/O MUX Register 1

| R         | R/W                                                 | R    | R    | R    | R    | R/W    | R/W    | Reset Value  |  |

|-----------|-----------------------------------------------------|------|------|------|------|--------|--------|--------------|--|

| -         | SYSCKE                                              | -    | -    | -    | -    | CP10EN | CP00EN | 00000000     |  |

| Bit7      | Bit6                                                | Bit5 | Bit4 | Bit3 | Bit2 | Bit1   | Bit0   | SFR Address: |  |

|           |                                                     |      |      |      |      |        |        | 0xE2         |  |

|           |                                                     |      |      |      |      |        |        |              |  |

| Bit7:     | UNUSED. Read = 0.                                   |      |      |      |      |        |        |              |  |

| Bit6:     | SYSCKE: SYSCLK Output Enable Bit                    |      |      |      |      |        |        |              |  |

|           | 0: SYSCLK unavailable at the port pin.              |      |      |      |      |        |        |              |  |

|           | 1: SYSCLK output routed to pin P1.6                 |      |      |      |      |        |        |              |  |

| Bits 5-2: | Bits 5–2: UNUSED. Read = 0000b, Write = don't care. |      |      |      |      |        |        |              |  |

| Bit1:     | CP10EN: Comparator 1 Output Enable bit.             |      |      |      |      |        |        |              |  |

|           | 0: CP1 unavailable at Port pin.                     |      |      |      |      |        |        |              |  |

|           | 1: CP1 routed to Port Pin P1.5.                     |      |      |      |      |        |        |              |  |

| Bit0:     | CP00EN: Comparator 0 Output Enable Bit              |      |      |      |      |        |        |              |  |

|           | 0: CP0 unavailable at port pin.                     |      |      |      |      |        |        |              |  |

|           | 1: CP0 rou                                          |      |      |      |      |        |        |              |  |

|           |                                                     | ···· |      |      |      |        |        |              |  |

## SFR Definition 14.3. PRT2MX: Port I/O MUX Register 2

| R/W    | R/W                                                                         | R/W           | R/W           | R/W         | R/W         | R/W          | R/W          | Reset Value  |  |  |

|--------|-----------------------------------------------------------------------------|---------------|---------------|-------------|-------------|--------------|--------------|--------------|--|--|

| GWPUD  | P3WPUD                                                                      | P2WPUD        | P1WPUD        | P0WPUD      | -           | -            | SPI00EN      | 00000000     |  |  |

| Bit7   | Bit6                                                                        | Bit5          | Bit4          | Bit3        | Bit2        | Bit1         | Bit0         | SFR Address: |  |  |

|        |                                                                             |               |               |             |             |              |              | 0xE3         |  |  |

| D:4 7. |                                                                             | lahal Darit L |               |             |             |              |              |              |  |  |

| BIT 7: | Bit 7: GWPUD: Global Port I/O Weak Pull-up Disable Bit                      |               |               |             |             |              |              |              |  |  |

|        | 0: Weak Pu                                                                  | •             | •             |             |             |              |              |              |  |  |

| 1      | 1: Weak Pu                                                                  | •             | •             |             | res)        |              |              |              |  |  |

| Bit 6: | P3WPUD: F                                                                   |               |               |             |             |              |              |              |  |  |

|        | 0: Weak Pu                                                                  | ull-ups Enat  | oled for port | : 3         |             |              |              |              |  |  |

|        | 1: Weak Pull-ups Disabled for port 3                                        |               |               |             |             |              |              |              |  |  |

| Bit 5: |                                                                             |               |               |             |             |              |              |              |  |  |

|        | 0: Weak Pull-ups Enabled for port 2.                                        |               |               |             |             |              |              |              |  |  |

|        | 1: Weak Pu                                                                  | JII-ups Disa  | bled for por  | t 2         |             |              |              |              |  |  |

| Bit 4: |                                                                             |               |               |             |             |              |              |              |  |  |

|        | 0: Weak Pu                                                                  |               |               |             |             |              |              |              |  |  |

|        | 1: Weak Pu                                                                  |               |               |             |             |              |              |              |  |  |

| Bit 3: | POWPUD: F                                                                   | •             |               |             |             |              |              |              |  |  |

| Dit 5. |                                                                             |               |               |             |             |              |              |              |  |  |

|        | 0: Weak Pull-ups Enabled for port 0<br>1: Weak Pull-ups Disabled for port 0 |               |               |             |             |              |              |              |  |  |

|        |                                                                             | •             |               |             |             |              |              |              |  |  |

|        | UNUSED. F                                                                   |               |               |             |             |              |              |              |  |  |

| Bit 0: | Bit 0: SPI00EN: SPI Bus I/O Enable Bit.                                     |               |               |             |             |              |              |              |  |  |

|        | 0: SPI I/O u                                                                |               |               |             |             |              |              |              |  |  |

|        | 1: SCK, MIS                                                                 | SO, MOSI, I   | NSS routed    | to pins P2. | 0, P2.1, P2 | .2, and P2.3 | 3 respective | ely.         |  |  |

|        |                                                                             |               |               |             |             |              |              |              |  |  |

### SFR Definition 14.12. P2MODE: Port2 Digital/Analog Input Mode

| R/W      | R/W  | R/W         | R/W           | R/W                             | R/W  | R/W          | R/W        | Reset Value  |

|----------|------|-------------|---------------|---------------------------------|------|--------------|------------|--------------|

|          |      |             |               |                                 |      |              |            | 11111111     |

| Bit7     | Bit6 | Bit5        | Bit4          | Bit3                            | Bit2 | Bit1         | Bit0       | SFR Address: |

|          |      |             |               |                                 |      |              |            | 0xF3         |

| Bits7–0: |      | ponding Por | t2 pin Digita | al Input disa<br>al Input is er | •    | nalog use, i | i.e., ADC) |              |

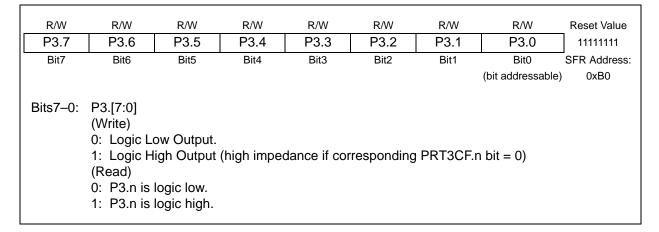

#### SFR Definition 14.13. P3: Port3 Register\*

### SFR Definition 14.14. PRT3CF: Port3 Configuration Register\*

| R/W      | R/W                                      | R/W         | R/W         | R/W         | R/W     | R/W          | R/W  | Reset Value<br>00000000 |

|----------|------------------------------------------|-------------|-------------|-------------|---------|--------------|------|-------------------------|

| Bit7     | Bit6                                     | Bit5        | Bit4        | Bit3        | Bit2    | Bit1         | Bit0 | SFR Address:<br>0xA7    |

| Bits7–0: | PRT3CF.[7:<br>0: Correspo<br>1: Correspo | onding P3.r | n Output Mo | ode is Open | -Drain. | espectively) |      |                         |

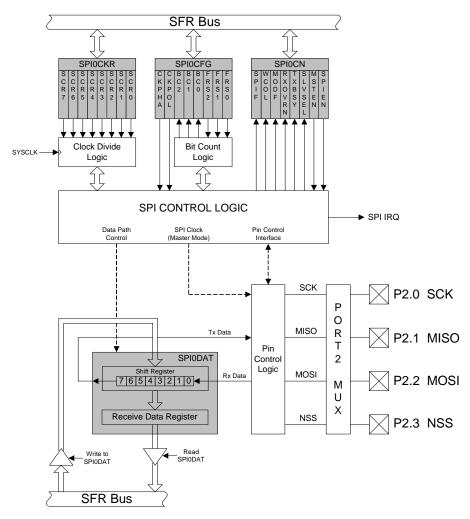

## 15. Serial Peripheral Interface Bus

The Serial Peripheral Interface (SPI) provides access to a four-wire, full-duplex, serial bus. SPI supports the connection of multiple slave devices to a master device on the same bus. A separate slave-select signal (NSS) is used to select a slave device and enable a data transfer between the master and the selected slave. Multiple masters on the same bus are also supported. Collision detection is provided when two or more masters attempt a data transfer at the same time. The SPI can operate as either a master or a slave. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency.

When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS, and the serial input data synchronously with the system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less that 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of ¼ the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the system clock.

| This bit cor<br>0: Data sar<br>1: Data sar<br>1: Data sar<br>Bit6: CKPOL: SI<br>This bit cor<br>0: SCK line<br>1: SCK line<br>1: SCK line<br>Bits5–3: BC2–BC0:<br>Indicates w<br>BC2–BC0:<br>Indicates w<br>BC<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>Bits2–0: SPIFRS2–<br>These three<br>data transfe<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | mpled on secor<br>PI Clock Polarit<br>ntrols the SPI c<br>e low in idle stat                                                                   | ock phase.<br>Ige of SCK period.<br>d edge of SCK per                  | R/W<br>SPIFRS2<br>Bit2 | R/W<br>SPIFRS1<br>Bit1 | R/W<br>SPIFRS0<br>Bit0 | Reset Value<br>00000111<br>SFR Address:<br>0x9A |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------|------------------------|------------------------|-------------------------------------------------|

| Bit7     Bit6       Bit7:     CKPHA: SI<br>This bit cor<br>0: Data sar<br>1: Data sar<br>1: Data sar       Bit6:     CKPOL: SI<br>This bit cor<br>0: SCK line<br>1: SCK line<br>1: SCK line       Bits5–3:     BC2–BC0:<br>Indicates w       Bits5–3:     BC2–BC0:<br>Indicates w       0     0       0     0       0     0       1     1       1     1       Bits2–0:     SPIFRS2–<br>These three<br>data transfe       0     SI       0     0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Bit5<br>PI Clock Phase<br>ntrols the SPI c<br>mpled on first e<br>mpled on secor<br>PI Clock Polarit<br>ntrols the SPI c<br>e low in idle stat | Bit4 Bit3<br>Dock phase.<br>Ige of SCK period.<br>d edge of SCK per    | Bit2                   |                        |                        | SFR Address:                                    |

| Bit7: CKPHA: SI<br>This bit cor<br>0: Data sar<br>1: Data sar<br>Bit6: CKPOL: SI<br>This bit cor<br>0: SCK line<br>1: SCK line<br>Bits5–3: BC2–BC0:<br>Indicates w<br>Bits5–3: BC2–BC0:<br>Indicates w<br>Bits2–0: SPIFRS2–<br>These three<br>data transfe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PI Clock Phase<br>ntrols the SPI c<br>mpled on first e<br>mpled on secor<br>PI Clock Polarit<br>ntrols the SPI c<br>e low in idle stat         | ock phase.<br>Ige of SCK period.<br>d edge of SCK per                  |                        | Bit1                   | Bit0                   |                                                 |

| This bit cor<br>0: Data sar<br>1: Data sar<br>Bit6: CKPOL: SI<br>This bit cor<br>0: SCK line<br>1: SCK line<br>Bits5–3: BC2–BC0:<br>Indicates w<br>BC<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>Bits2–0: SPIFRS2–<br>These three<br>data transfe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ntrols the SPI c<br>mpled on first e<br>mpled on secor<br>PI Clock Polarit<br>ntrols the SPI c<br>e low in idle stat                           | ock phase.<br>Ige of SCK period.<br>d edge of SCK per                  | iod.                   |                        |                        |                                                 |

| This bit cor<br>0: SCK line<br>1: SCK line<br>Bits5–3: BC2–BC0:<br>Indicates w<br>BC<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>Bits2–0: SPIFRS2–<br>These three<br>data transfe<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ntrols the SPI c<br>e low in idle stat                                                                                                         | Ι.                                                                     |                        |                        |                        |                                                 |

| Indicates w<br>BC<br>0<br>0<br>0<br>0<br>1<br>1<br>1<br>1<br>Bits2–0: SPIFRS2–<br>These three<br>data transfe<br>0<br>SI<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | e high in idle sta                                                                                                                             | ock polarity.<br>e.                                                    |                        |                        |                        |                                                 |

| 0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>Bits2–0: SPIFRS2–<br>These three<br>data transfer<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                | o 8 bits of the SPI                                                    | word have b            | een transm             | itted.                 |                                                 |

| 0<br>0<br>0<br>1<br>1<br>1<br>1<br>Bits2–0: SPIFRS2–<br>These three<br>data transfe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2–BC0                                                                                                                                          | Bit Transmitte                                                         | ł                      |                        |                        |                                                 |

| 0<br>0<br>1<br>1<br>1<br>1<br>Bits2–0: SPIFRS2–<br>These three<br>data transfer<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0 0                                                                                                                                            | Bit 0 (LSB)                                                            |                        |                        |                        |                                                 |

| 0<br>1<br>1<br>1<br>1<br>Bits2–0: SPIFRS2–<br>These three<br>data transfe<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0 1                                                                                                                                            | Bit 1                                                                  |                        |                        |                        |                                                 |

| 1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 <t< td=""><td>1 0</td><td>Bit 2</td><td>_</td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1 0                                                                                                                                            | Bit 2                                                                  | _                      |                        |                        |                                                 |

| 1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 <t< td=""><td>1 1</td><td>Bit 3</td><td>_</td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1 1                                                                                                                                            | Bit 3                                                                  | _                      |                        |                        |                                                 |

| 1       1       Bits2–0:     SPIFRS2–       These three data transfe       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 0                                                                                                                                            | Bit 4                                                                  | _                      |                        |                        |                                                 |

| 1<br>Bits2–0: SPIFRS2–<br>These three<br>data transfe<br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 1                                                                                                                                            | Bit 5                                                                  | _                      |                        |                        |                                                 |