Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Not For New Designs                                            |

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SPI, UART/USART                                                |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                               |

| Number of I/O              | 32                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1.25K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 32x8b                                                      |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f226-gq |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 17.2.Timer 2                                         | 133 |

|------------------------------------------------------|-----|

| 17.2.1.Mode 0: 16-bit Counter/Timer with Capture     | 134 |

| 17.2.2.Mode 1: 16-bit Counter/Timer with Auto-Reload | 135 |

| 17.2.3.Mode 2: Baud Rate Generator                   | 136 |

| 18. JTAG                                             | 139 |

| 18.1.Flash Programming Commands                      | 140 |

| 18.2.Boundary Scan Bypass and ID Code                | 143 |

| 18.2.1.BYPASS Instruction                            | 143 |

| 18.2.2.IDCODE Instruction                            | 143 |

| 18.3.Debug Support                                   | 143 |

| Contact Information                                  | 111 |

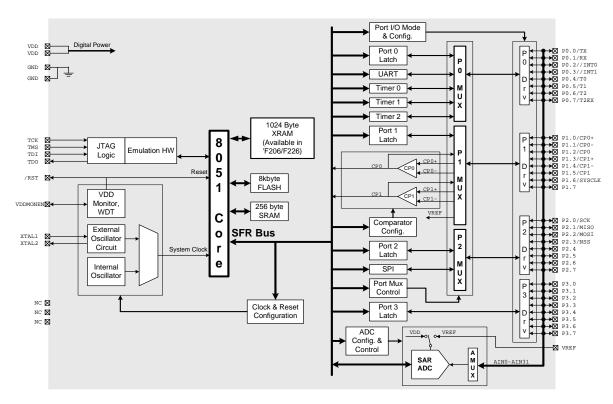

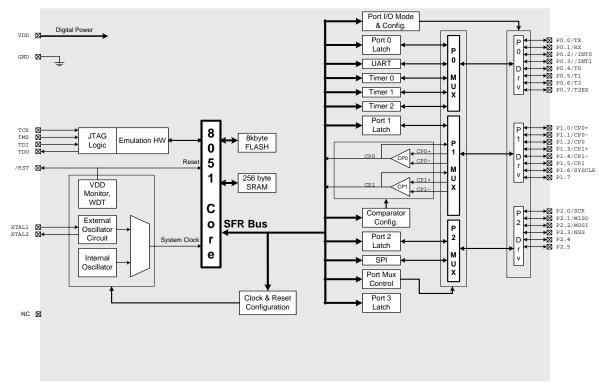

## 1. System Overview

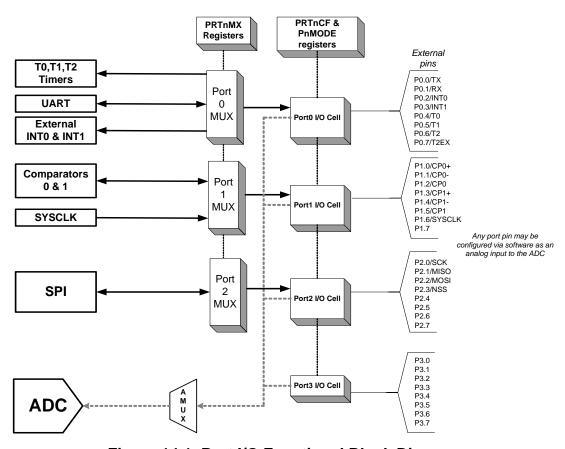

The C8051F2xx is a family of fully integrated, mixed-signal System on a Chip MCU's available with a true 12-bit ('F206) multi-channel ADC, 8-bit multi-channel ADC ('F220/1/6 and 'F206), or without an ADC ('F230/1/6). Each model features an 8051-compatible microcontroller core with 8 kB of Flash memory. There are also UART and SPI serial interfaces implemented in hardware (not "bit-banged" in user software). Products in this family feature 22 or 32 general purpose I/O pins, some of which can be used for assigned digital peripheral interface. Any pins may be configured for use as analog input to the analog-to-digital converter ('F220/1/6 and 'F206 only). (See the Product Selection Guide in Table 1.1 for a quick reference of each MCUs' feature set.)

Other features include an on-board  $V_{DD}$  monitor, WDT, and clock oscillator. On-board Flash memory can be reprogrammed in-circuit, and may also be used for non-volatile data storage. Integrated peripherals can also individually shut down any or all of the peripherals to conserve power. All parts have 256 bytes of SRAM. Also, an additional 1024 bytes of RAM is available in the 'F206/226/236.

On-board JTAG debug support allows non-intrusive (uses no on-chip resources), full speed, in-circuit debug using the production MCU installed in the final application. This debug system supports inspection and modification of memory and registers, setting breakpoints, watchpoints, single stepping, run and halt commands. All analog and digital peripherals are fully functional when emulating using JTAG.

Each MCU is specified for 2.7 to 3.6 V operation over the industrial temperature range (-45 to +85 °C) and is available in the 48-pin TFQP and 32-pin LFQP. The Port I/Os are tolerant for input signals up to 5 V.

**Table 1.1. Product Selection Guide**

|           | MIPS (Peak) | Flash Memory | RAM  | SPI      | UART     | Timers (16-bit) | Digital Port I/O's | ADC Resolution (bits) | ADC Max Speed (ksps) | ADC Inputs | Voltage Comparators | Package |

|-----------|-------------|--------------|------|----------|----------|-----------------|--------------------|-----------------------|----------------------|------------|---------------------|---------|

| C8051F206 | 25          | 8 k          | 1280 | <b>√</b> | <b>✓</b> | 3               | 32                 | 12                    | 100                  | 32         | 2                   | 48TQFP  |

| C8051F220 | 25          | 8 k          | 256  | <b>√</b> | <b>✓</b> | 3               | 32                 | 8                     | 100                  | 32         | 2                   | 48TQFP  |

| C8051F221 | 25          | 8 k          | 256  | ✓        | <b>✓</b> | 3               | 22                 | 8                     | 100                  | 22         | 2                   | 32LQFP  |

| C8051F226 | 25          | 8 k          | 1280 | ✓        | <b>✓</b> | 3               | 32                 | 8                     | 100                  | 32         | 2                   | 48TQFP  |

| C8051F230 | 25          | 8 k          | 256  | <b>√</b> | <b>✓</b> | 3               | 32                 | _                     | _                    | _          | 2                   | 48TQFP  |

| C8051F231 | 25          | 8 k          | 256  | ✓        | <b>✓</b> | 3               | 22                 | _                     | _                    | _          | 2                   | 32LQFP  |

| C8051F236 | 25          | 8 k          | 1280 | <b>√</b> | <b>√</b> | 3               | 32                 | _                     | _                    | _          | 2                   | 48TQFP  |

Figure 1.1. C8051F206, C8051F220 and C8051F226 Block Diagram (48 TQFP)

Figure 1.4. C8051F231 Block Diagram (32 LQFP)

## 1.1. CIP-51<sup>TM</sup> Microcontroller Core

#### 1.1.1. Fully 8051 Compatible

The C8051F206, C8051F220/1/6 and C8051F230/1/6 utilize Silcon Labs' proprietary CIP-51 microcontroller core. The CIP-51 is fully compatible with the MCS-51<sup>TM</sup> instruction set. Standard 803x/805x assemblers and compilers can be used to develop software. The core contains the peripherals included with a standard 8052, including three 16-bit counter/timers, a full-duplex UART, 256 bytes of internal RAM, an optional 1024 bytes of XRAM, 128 byte Special Function Register (SFR) address space, and four byte-wide I/O Ports.

#### 1.1.2. Improved Throughput

The CIP-51 employs a pipelined architecture that greatly increases its instruction throughput over the standard 8051 architecture. In a standard 8051, all instructions except for MUL and DIV take 12 or 24 system clock cycles to execute with a maximum system clock of 12 MHz. By contrast, the CIP-51 core executes 70% of its instructions in one or two system clock cycles, with only four instructions taking more than four system clock cycles.

The CIP-51 has a total of 109 instructions. The number of instructions versus the system clock cycles to execute them is as follows:

| Instructions      | 26 | 50 | 5   | 14 | 7   | 3 | 1   | 2 | 1 |

|-------------------|----|----|-----|----|-----|---|-----|---|---|

| Clocks to Execute | 1  | 2  | 2/3 | 3  | 3/4 | 4 | 4/5 | 5 | 8 |

### SFR Definition 5.2. ADC0CF: ADC Configuration Register

| R/W    | R/W    | R/W    | R/W  | R/W  | R/W    | R/W    | R/W    | Reset Value  |

|--------|--------|--------|------|------|--------|--------|--------|--------------|

| ADCSC2 | ADCSC1 | ADCSC0 | -    | -    | AMPGN2 | AMPGN1 | AMPGN0 | 01100000     |

| Bit7   | Bit6   | Bit5   | Bit4 | Bit3 | Bit2   | Bit1   | Bit0   | SFR Address: |

|        |        |        |      |      |        |        |        | 0xBC         |

Bits7-5: ADCSC2-0: ADC SAR Conversion Clock Period Bits

000: SAR Conversion Clock = 1 System Clock

001: SAR Conversion Clock = 2 System Clocks

010: SAR Conversion Clock = 4 System Clocks

011: SAR Conversion Clock = 8 System Clocks

1xx: SAR Conversion Clock = 16 Systems Clocks

NOTE: SAR conversion clock should be less than or equal to 2MHz.

Bits4–3: UNUSED. Read = 00b; Write = don't care Bits2–0: AMPGN2–0: ADC Internal Amplifier Gain

000: Gain = 1 001: Gain = 2 010: Gain = 4 011: Gain = 8 10x: Gain = 16 11x: Gain = 0.5

### SFR Definition 6.3. ADC0CN: ADC Control ('F220/1/6 and 'F206)

| R/W   | R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W               | Reset Value  |

|-------|-------|--------|--------|--------|--------|--------|-------------------|--------------|

| ADCEN | ADCTM | ADCINT | ADBUSY | ADSTM1 | ADSTM0 | ADWINT | ADLJST            | 00000000     |

| Bit7  | Bit6  | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0              | SFR Address: |

|       |       |        |        |        |        |        | (bit addressable) | 0xE8         |

Bit7: ADCEN: ADC Enable Bit

0: ADC Disabled. ADC is in low power shutdown.

1: ADC Enabled. ADC is active and ready for data conversions.

Bit6: ADCTM: ADC Track Mode Bit

0: When the ADC is enabled, tracking is continuous unless a conversion is in process

1: Tracking Defined by ADSTM1-0 bits

ADSTM1-0:

00: Tracking starts with the write of 1 to ADBUSY and lasts for 3 SAR clocks

01: RESERVED 10: RESERVED

11: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks

Bit5: ADCINT: ADC Conversion Complete Interrupt Flag (cleared by software).

0: ADC has not completed a data conversion since the last time this flag was cleared

1: ADC has completed a data conversion

Bit4: ADBUSY: ADC Busy Bit

Read

0: ADC Conversion complete or no valid data has been converted since a reset. The falling edge of ADBUSY generates an interrupt when enabled.

1: ADC Busy converting data

Write

0: No effect

1: Starts ADC Conversion if ADSTM1-0 = 00b

Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits

00: ADC conversion started upon a write of 1 to ADBUSY

01: RESERVED 10: RESERVED

11: ADC conversions initiated on overflows of Timer 2

Bit1: ADWINT: ADC Window Compare Interrupt Flag

0: ADC Window Comparison Data match has not occurred

1: ADC Window Comparison Data match occurred

Bit0: ADLJST: ADC Left Justify Data Bit

0: Data in ADC0H:ADC0L registers are right justified.

1: Data in ADC0H:ADC0L registers are left justified.

Table 9.1. CIP-51 Instruction Set Summary (Continued)

| Mnemonic                    | Description                                | Bytes | Clock<br>Cycles |

|-----------------------------|--------------------------------------------|-------|-----------------|

| MOV A,#data                 | Move immediate to A                        | 2     | 2               |

| MOV Rn,A                    | Move A to register                         | 1     | 1               |

| MOV Rn,direct               | Move direct byte to register               | 2     | 2               |

| MOV Rn,#data                | Move immediate to register                 | 2     | 2               |

| MOV direct,A                | Move A to direct byte                      | 2     | 2               |

| MOV direct,Rn               | Move register to direct byte               | 2     | 2               |

| MOV direct, direct          | Move direct byte to direct                 | 3     | 3               |

| MOV direct,@Ri              | Move indirect RAM to direct byte           | 2     | 2               |

| MOV direct,#data            | Move immediate to direct byte              | 3     | 3               |

| MOV @Ri,A                   | Move A to indirect RAM                     | 1     | 2               |

| MOV @Ri,direct              | Move direct byte to indirect RAM           | 2     | 2               |

| MOV @Ri,#data               | Move immediate to indirect RAM             | 2     | 2               |

| MOV DPTR,#data16            | Load data pointer with 16-bit constant     | 3     | 3               |

| MOVC A,@A+DPTR              | Move code byte relative DPTR to A          | 1     | 3               |

| MOVC A,@A+PC                | Move code byte relative PC to A            | 1     | 3               |

| MOVX A,@Ri                  | Move external data (8-bit address) to A    | 1     | 3               |

| MOVX @Ri,A                  | Move A to external data (8-bit address)    | 1     | 3               |

| MOVX A,@DPTR                | Move external data (16-bit address) to A   | 1     | 3               |

| MOVX @DPTR,A                | Move A to external data (16-bit address)   | 1     | 3               |

| PUSH direct                 | Push direct byte onto stack                | 2     | 2               |

| POP direct                  | Pop direct byte from stack                 | 2     | 2               |

| XCH A,Rn                    | Exchange register with A                   | 1     | 1               |

| XCH A,direct                | Exchange direct byte with A                | 2     | 2               |

| XCH A,@Ri                   | Exchange indirect RAM with A               | 1     | 2               |

| XCHD A,@Ri                  | Exchange low nibble of indirect RAM with A | 1     | 2               |

| <b>Boolean Manipulation</b> |                                            | •     | ·               |

| CLR C                       | Clear carry                                | 1     | 1               |

| CLR bit                     | Clear direct bit                           | 2     | 2               |

| SETB C                      | Set carry                                  | 1     | 1               |

| SETB bit                    | Set direct bit                             | 2     | 2               |

| CPL C                       | Complement carry                           | 1     | 1               |

| CPL bit                     | Complement direct bit                      | 2     | 2               |

| ANL C,bit                   | AND direct bit to carry                    | 2     | 2               |

| ANL C,/bit                  | AND complement of direct bit to carry      | 2     | 2               |

| ORL C,bit                   | OR direct bit to carry                     | 2     | 2               |

| ORL C,/bit                  | OR complement of direct bit to carry       | 2     | 2               |

| MOV C,bit                   | Move direct bit to carry                   | 2     | 2               |

| MOV bit,C                   | Move carry to direct bit                   | 2     | 2               |

| JC rel                      | Jump if carry is set                       | 2     | 2/3             |

### 9.2. Memory Organization

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. There are 256 bytes of internal data memory and 8 kB of internal program memory address space implemented within the CIP-51. The CIP-51 memory organization is shown in Figure 9.2.

### 9.2.1. Program Memory

The CIP-51 has a 8 kB program memory space. The MCU implements 8320 bytes of this program memory space as in-system, reprogrammable Flash memory, organized in a contiguous block from addresses 0x0000 to 0x207F. Note: 512 bytes (0x1E00 – 0x1FFF) of this memory are reserved for factory use and are not available for user program storage.

Program memory is normally assumed to be read-only. However, the CIP-51 can write to program memory by setting the Program Store Write Enable bit (PSCTL.0) and using the MOVX instruction. This feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. Refer to Section 10 Flash Memory for further details.

#### 9.2.2. Data Memory

The CIP-51 implements 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct bit addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F will access the upper 128 bytes of data memory. Figure 9.2 illustrates the data memory organization of the CIP-51.

Additionally, the C8051F206/226/236 feature 1024 Bytes of RAM mapped in the external data memory space. All address locations may be accessed using the MOVX instruction. (Please see Section 11).

### 9.3.1. Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should be set to logic 0. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic 0, selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the datasheet associated with their corresponding system function.

### SFR Definition 9.1. SP: Stack Pointer

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 00000111     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0x81         |

Bits 7-0: SP: Stack Pointer.

The stack pointer holds the location of the top of the stack. The stack pointer is incremented before every PUSH operation. The SP register defaults to 0x07 after reset.

### SFR Definition 9.2. DPL: Data Pointer Low Byte

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 00000111     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0x81         |

Bits 7-0: DPL: Data Pointer Low.

The DPL register is the low byte of the 16-bit DPTR. DPTR is used to access indirectly addressed RAM.

## SFR Definition 9.3. DPH: Data Pointer High Byte

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 00000111     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0x81         |

Bits 7-0: DPH: Data Pointer High.

The DPH register is the high byte of the 16-bit DPTR. DPTR is used to access indirectly addressed RAM.

down all digital peripherals. Each analog peripheral must be shut down individually prior to entering Stop Mode. Stop mode can only be terminated by an internal or external reset. On reset, the CIP-51 performs the normal reset sequence and begins program execution at address 0x0000.

If enabled, the Missing Clock Detector will cause an internal reset and thereby terminate the Stop mode. The Missing Clock Detector should be disabled if the CPU is to be put to sleep for longer than the MCD timeout of 100µsec.

### SFR Definition 9.14. PCON: Power Control Register

|   | R/W  | Reset Value  |

|---|------|------|------|------|------|------|------|------|--------------|

|   | SMOD | GF4  | GF3  | GF2  | GF1  | GF0  | STOP | IDLE | 00000000     |

|   | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

| ı |      |      |      |      |      |      |      |      | 0x87         |

Bit7: SMOD: Serial Port Baud Rate Doubler Enable.

0: Serial Port baud rate is that defined by Serial Port Mode in SCON.

1: Serial Port baud rate is double that defined by Serial Port Mode in SCON.

Bits6-2: GF4-GF0: General Purpose Flags 4-0.

These are general purpose flags for use under software control.

Bit1: STOP: Stop Mode Select.

Setting this bit will place the CIP-51 in Stop mode. This bit will always be read as 0.

1: Goes into power down mode. (Turns off internal oscillator).

Bit0: IDLE: Idle Mode Select.

Setting this bit will place the CIP-51 in Idle mode. This bit will always be read as 0.

1: Goes into idle mode. (Shuts off clock to CPU, but clock to Timers, Interrupts, Serial

Ports, and Analog Peripherals are still active.)

## 10. Flash Memory

This MCU includes 8 k + 128 bytes of on-chip, re-programmable Flash memory for program code and non-volatile data storage. The Flash memory can be programmed in-system, a single byte at a time, through the JTAG interface or by software using the MOVX instruction. Once cleared to 0, a Flash bit must be erased to set it back to 1. The bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution. Data polling to determine the end of the write/erase operation is not required. The Flash memory is designed to withstand at least 20,000 write/erase cycles. Refer to Table 10.1 for the electrical characteristics of the Flash memory.

### 10.1. Programming The Flash Memory

The simplest means of programming the Flash memory is through the JTAG interface using programming tools provided by Silicon Labs or a third party vendor. This is the only means for programming a non-initialized device. For details on the JTAG commands to program Flash memory, see Section 18.1.

The Flash memory can be programmed by software using the MOVX instruction with the address and data byte to be programmed provided as normal operands. Before writing to Flash memory using MOVX, flash write operations must be enabled by setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1. Writing to Flash remains enabled until the PSWE bit is cleared by software.

To ensure the contents of the Flash contents, it is strongly recommended that the on-chip  $V_{DD}$  monitor be enabled (by tieing the MONEN pin 'high') in any application that writes and/or erases Flash memory from software.

Writes to Flash memory can clear bits but cannot set them. Only an erase operation can set bits in Flash. The byte location to be programmed must be erased before a new value can be written. The 8kbyte Flash memory is organized in 512-byte sectors. The erase operation applies to an entire sector (setting all bytes in the sector to 0xFF). Setting the PSEE Program Store Erase Enable bit (PSCTL.1) and PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 and then using the MOVX command to write a data byte to any byte location within the sector will erase an entire 512-byte sector. The data byte written can be of any value because it is not actually written to the Flash. Flash erasure remains enabled until the PSEE bit is cleared by software. The following sequence illustrates the algorithm for programming the Flash memory by software:

- 1. Disable interrupts.

- 2. Enable Flash Memory write/erase in FLSCL Register using FLASCL bits.

- 3. Set PSEE (PSCTL.1) to enable Flash sector erase.

- 4. Set PSWE (PSCTL.0) to enable Flash writes.

- 5. Use MOVX to write a data byte to any location within the 512-byte sector to be erased.

- 6. Clear PSEE to disable Flash sector erase.

- Use MOVX to write a data byte to the desired byte location within the erased 512-byte sector. Repeat until finished. (Any number of bytes can be written from a single byte to and entire sector.)

- 8. Clear the PSWE bit to disable Flash writes.

Write/Erase timing is automatically controlled by hardware based on the prescaler value held in the Flash Memory Timing Prescaler register (FLSCL). The 4-bit prescaler value FLASCL determines the time interval for write/erase operations. The FLASCL value required for a given system clock is shown in SFR Definition 10.2, along with the formula used to derive the FLASCL values. When FLASCL is set to 1111b, the

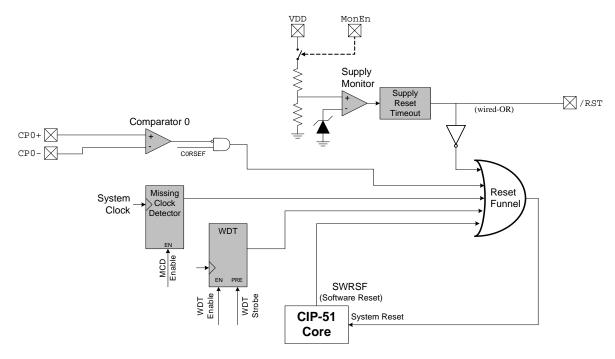

### 12. Reset Sources

The reset circuitry of the MCU allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the CIP-51 halts program execution, forces the external port pins to a known state and initializes the SFRs to their defined reset values. Interrupts and timers are disabled. On exit, the program counter (PC) is reset, and program execution starts at location 0x0000.

All of the SFRs are reset to predefined values. The reset values of the SFR bits are defined in the SFR detailed descriptions. The contents of internal data memory are not changed during a reset and any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost even though the data on the stack are not altered.

The I/O port latches are reset to 0xFF (all logic ones), activating internal weak pull-ups which take the external I/O pins to a high state. The weak pull-ups are enabled during and after the reset. If the source of reset is from the  $V_{DD}$  Monitor or writing a '1' to the PORSF bit, the  $\overline{RST}$  pin is driven low until the end of the  $V_{DD}$  reset timeout.

On exit from the reset state, the MCU uses the internal oscillator running at 2MHz as the system clock by default. Refer to Section 13 for information on selecting and configuring the system clock source. The Watchdog Timer is enabled using its longest timeout interval. (Section 12.7 details the use of the Watchdog Timer.) Once the system clock source is stable, program execution begins at location 0x0000.

There are six sources for putting the MCU into the reset state: power-on/power-fail (V<sub>DD</sub> monitor), external RST pin, software commanded, Comparator 0, Missing Clock Detector, and Watchdog Timer. Each reset source is described below:

Figure 12.1. Reset Sources Diagram

#### **Disable WDT**

Writing 0xDE followed by 0xAD to the WDTCN register disables the WDT. The following code segment illustrates disabling the WDT.

```

; disable all interrupts

CLR

; disable watchdog timer

VOM

WDTCN, #0DEh

VOM

WDTCN, #0ADh

SETB

; re-enable interrupts

```

The writes of 0xDE and 0xAD must occur within 4 clock cycles of each other, or the disable operation is ignored. Interrupts should be disabled during this procedure to avoid delay between the two writes.

#### **Disable WDT Lockout**

Writing 0xFF to WDTCN locks out the disable feature. Once locked out, the disable operation is ignored until the next system reset. Writing 0xFF does not enable or reset the watchdog timer. Applications alays intending to use the watchdog should write 0xFF to WDTCN in their initialization code.

#### **Setting WDT Interval**

WDTCN.[2:0] control the watchdog timeout interval. The interval is given by the following equation:

$$4^{3+WDTCN[2:0]}$$

x  $T_{SYSCLK}$ , (where  $T_{SYSCLK}$  is the system clock period).

For a 2.0 MHz system clock, this provides an interval range of 32msec to 524msec. WDTCN.7 must be written as 0 when setting this interval. Reading WDTCN returns the programmed interval. WDTCN.[2:0] is 111b after a system reset.

## SFR Definition 12.1. WDTCN: Watchdog Timer Control

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | xxxxx111     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | OVEE         |

Bits7-0: WDT Control

Writing 0xA5 both enables and reloads the WDT.

Writing 0xDE followed within 4 clocks by 0xAD disables the WDT.

Writing 0xFF locks out the disable feature.

Bit4: Watchdog Status Bit (when Read)

Reading the WDTCN.[4] bit indicates the Watchdog Timer Status.

0: WDT is inactive 1: WDT is active

Bits2-0: Watchdog Timeout Interval Bits

The WDTCN.[2:0] bits set the Watchdog Timeout Interval. When writing these bits,

WDTCN.7 must be set to 0.

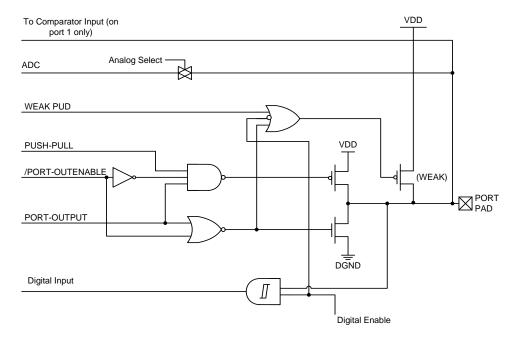

Figure 14.1. Port I/O Functional Block Diagram

Figure 14.2. Port I/O Cell Block Diagram

SILICON LABS

### SFR Definition 15.2. SPI0CN: SPI Control

| R/W  | R/W  | R/W  | R/W    | R     | R      | R/W   | R/W   | Reset Value  |

|------|------|------|--------|-------|--------|-------|-------|--------------|

| SPIF | WCOL | MODF | RXOVRN | TXBSY | SLVSEL | MSTEN | SPIEN | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4   | Bit3  | Bit2   | Bit1  | Bit0  | SFR Address: |

|      |      |      |        |       |        |       |       | 0vE8         |

Bit7: SPIF: SPI Interrupt Flag.

This bit is set to logic 1 by hardware at the end of a data transfer. If interrupts are enabled, setting this bit causes the CPU to vector to the SPI0 interrupt service routine. This bit is not automatically cleared by hardware. It must be cleared by software.

Bit6: WCOL: Write Collision Flag.

This bit is set to logic 1 by hardware (and generates a SPI interrupt) to indicate a write to the SPI data register was attempted while a data transfer was in progress. It is cleared by software.

Bit5: MODF: Mode Fault Flag.

This bit is set to logic 1 by hardware (and generates a SPI interrupt) when a master mode collision is detected (NSS is low and MSTEN = 1). This bit is not automatically cleared by hardware. It must be cleared by software.

Bit4: RXOVRN: Receive Overrun Flag.

This bit is set to logic 1 by hardware (and generates a SPI interrupt) when the receive buffer still holds unread data from a previous transfer and the last bit of the current transfer is shifted into the SPI shift register. This bit is not automatically cleared by hardware. It must be cleared by software.

Bit3: TXBSY: Transmit Busy Flag.

This bit is set to logic 1 by hardware while a master mode transfer is in progress. It is cleared by hardware at the end of the transfer.

Bit2: SLVSEL: Slave Selected Flag.

This bit is set to logic 1 whenever the NSS pin is low indicating it is enabled as a slave. It is cleared to logic 0 when NSS is high (slave disabled).

Bit1: MSTEN: Master Mode Enable.

0: Disable master mode. Operate in slave mode.1: Enable master mode. Operate as a master.

Bit0: SPIEN: SPI Enable.

This bit enables/disables the SPI.

0: SPI disabled.1: SPI enabled.

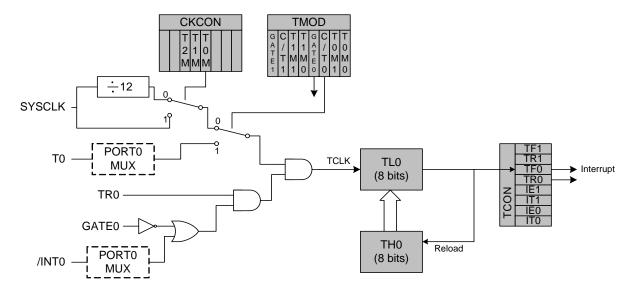

### 17.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. The TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0. Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0.

Figure 17.2. T0 Mode 2 Block Diagram

### SFR Definition 17.8. T2CON: Timer 2 Control

| R/W  | R/W  | R/W  | R/W  | R/W   | R/W  | R/W  | R/W              | Reset Value  |

|------|------|------|------|-------|------|------|------------------|--------------|

| TF2  | EXF2 | RCLK | TCLK | EXEN2 | TR2  | C/T2 | CP/RL2           | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3  | Bit2 | Bit1 | Bit0             | SFR Address: |

|      |      |      |      |       |      |      | (bit addressable | ) 0xC8       |

Bit7: TF2: Timer 2 Overflow Flag.

Set by hardware when Timer 2 overflows from 0xFFFF to 0x0000. When the Timer 2 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 2 interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.

TF2 will not be set when RCLK and/or TCLK are logic 1.

Bit6: EXF2: Timer 2 External Flag.

Set by hardware when either a capture or reload is caused by a high-to-low transition on the T2EX input pin and EXEN2 is logic 1. When the Timer 2 interrupt is enabled, setting this bit causes the CPU to vector to the Timer 2 Interrupt service routine. This bit is not automatically cleared by hardware and must be cleared by software.

Bit5: RCLK: Receive Clock Flag.

Selects which timer is used for the UART's receive clock in modes 1 or 3.

0: Timer 1 overflows used for receive clock.

1: Timer 2 overflows used for receive clock.

Bit4: TCLK: Transmit Clock Flag.

Selects which timer is used for the UART's transmit clock in modes 1 or 3.

0: Timer 1 overflows used for transmit clock.

1: Timer 2 overflows used for transmit clock.

Bit3: EXEN2: Timer 2 External Enable.

Enables high-to-low transitions on T2EX to trigger captures or reloads when Timer 2 is not operating in Baud Rate Generator mode.

0: High-to-low transitions on T2EX ignored.

1: High-to-low transitions on T2EX cause a capture or reload.

Bit2: TR2: Timer 2 Run Control.

This bit enables/disables Timer 2.

0: Timer 2 disabled.

1: Timer 2 enabled.

Bit1: C/T2: Counter/Timer Select.

0: Timer Function: Timer 2 incremented by clock defined by T2M (CKCON.5).

1: Counter Function: Timer 2 incremented by high-to-low transitions on external input pin P0.6/T2.

Bit0: CP/RL2: Capture/Reload Select.

This bit selects whether Timer 2 functions in capture or auto-reload mode. EXEN2 must be logic 1 for high-to-low transitions on T2EX to be recognized and used to trigger captures or reloads. If RCLK or TCLK is set, this bit is ignored and Timer 2 will function in auto-reload mode.

0: Auto-reload on Timer 2 overflow or high-to-low transition at T2EX (EXEN2 = 1).

1: Capture on high-to-low transition at T2EX (EXEN2 = 1).

## SFR Definition 17.9. RCAP2L: Timer 2 Capture Register Low Byte

| R/W  | Reset Value          |

|------|------|------|------|------|------|------|------|----------------------|

|      |      |      |      |      |      |      |      | 00000000             |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xCA |

Bits 7-0: RCAP2L: Timer 2 Capture Register Low Byte.

The RCAP2L register captures the low byte of Timer 2 when Timer 2 is configured in capture mode. When Timer 2 is configured in auto-reload mode, it holds the low byte of the reload value.

### SFR Definition 17.10. RCAP2H: Timer 2 Capture Register High Byte

| R/W  | Reset Value          |

|------|------|------|------|------|------|------|------|----------------------|

|      |      |      |      |      |      |      |      | 00000000             |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xCB |

Bits 7-0: RCAP2H: Timer 2 Capture Register High Byte.

The RCAP2H register captures the high byte of Timer 2 when Timer 2 is configured in capture mode. When Timer 2 is configured in auto-reload mode, it holds the high byte of the reload value.

### SFR Definition 17.11. TL2: Timer 2 Low Byte

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0VCC         |

Bits 7-0: TL2: Timer 2 Low Byte.

The TL2 register contains the low byte of the 16-bit Timer 2.

### SFR Definition 17.12. TH2: Timer 2 High Byte

| R/W  | Reset Value          |

|------|------|------|------|------|------|------|------|----------------------|

|      |      |      |      |      |      |      |      | 00000000             |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xCD |

Bits 7-0: TH2: Timer 2 High Byte.

The TH2 register contains the high byte of the 16-bit Timer 2.

SILICON LABS

### **18. JTAG**

### Description

The MCU has an on-chip JTAG interface and logic to support Flash read and write operations and non-intrusive in-circuit debug. The C8051F2xx may be placed in a JTAG test chain in order to maintain only one JTAG interface in a system for boundary scan of other parts, and still utilize the C8051F2xx debug and Flash programming. However, the C8051F2xx does NOT support boundary scan and will act as BYPASS as specified in IEEE 1149.1.

The JTAG interface is implemented via four dedicated pins on the MCU, which are TCK, TMS, TDI, and TDO. These pins are all 5 volt tolerant.

Through the 16-bit JTAG Instruction Register (IR), five instructions shown in JTAG Register Definition 18.1 can be commanded. These commands can either select the device ID code, or select registers for Flash programming operations. BYPASS is shown to illustrate its default setting. There are four Data Registers associated with the Flash read and write operations on the MCU.

### JTAG Register Definition 18.1. IR: JTAG Instruction

|   |          |      |         |      |  |   |  |    |        |      |  |      | Reset Value |

|---|----------|------|---------|------|--|---|--|----|--------|------|--|------|-------------|

|   |          |      |         |      |  |   |  | Į. |        |      |  |      | 0x0000      |

| - | Bit15    | ,    | ,       | ,    |  | , |  |    |        |      |  | Bit0 | 1           |

|   |          |      |         |      |  |   |  |    |        |      |  |      |             |

|   |          |      |         |      |  |   |  |    |        |      |  |      |             |

| l | ID value |      | <u></u> | 4ion |  |   |  |    | oorin: | lion |  |      |             |

|   | IR value | l in | struct  | tion |  |   |  | De | scrip  | tion |  |      |             |

| IR value | Instruction   | Description                                                                                                                                                                                                               |

|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0004   | IDCODE        | Selects device ID Register                                                                                                                                                                                                |

| 0xFFFF   | BYPASS        | Selects bypass Data Register and is DEFAULT for the device. Note: The device does NOT support boundary scan. However, it may be placed in a scan chain and bypassed in a system of other devices utilizing boundary scan. |

| 0x0082   | Flash Control | Selects FLASHCON Register to control how the interface logic responds to reads and writes to the FLASHDAT Register                                                                                                        |

| 0x0083   | Flash Data    | Selects FLASHDAT Register for reads and writes to the Flash memory                                                                                                                                                        |

| 0x0084   | Flash Address | Selects FLASHADR Register which holds the address of all Flash read, write, and erase operations                                                                                                                          |

| 0x0085   | Flash Scale   | Selects FLASHSCL Register which controls the prescaler used to generate timing signals for Flash operations                                                                                                               |

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific written consent of Silicon Laboratories. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701