# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                            |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SPI, UART/USART                                                |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                               |

| Number of I/O              | 32                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 256 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | -                                                              |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 48-TQFP                                                        |

| Supplier Device Package    | 48-TQFP (7x7)                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f230-gq |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of Figures and Tables

| 1. | System Overview                                                           |    |

|----|---------------------------------------------------------------------------|----|

|    | Table 1.1. Product Selection Guide                                        | 11 |

|    | Figure 1.1. C8051F206, C8051F220 and C8051F226 Block Diagram (48 TQFP)    | 12 |

|    | Figure 1.2. C8051F221 Block Diagram (32 LQFP)                             |    |

|    | Figure 1.3. C8051F230 and C8051F236 Block Diagram (48 TQFP)               | 14 |

|    | Figure 1.4. C8051F231 Block Diagram (32 LQFP)                             | 15 |

|    | Figure 1.5. Comparison of Peak MCU Throughputs                            |    |

|    | Figure 1.6. Comparison of Peak MCU Throughputs                            |    |

|    | Figure 1.7. On-Board Memory Map                                           |    |

|    | Figure 1.8. Degub Environment Diagram                                     | 19 |

|    | Figure 1.9. Port I/O Functional Block Diagram                             |    |

|    | Figure 1.10. ADC Diagram                                                  |    |

|    | Figure 1.11. Comparator Diagram                                           |    |

| 2. | Absolute Maximum Ratings                                                  |    |

|    | Table 2.1. Absolute Maximum Ratings*                                      | 23 |

| 3. | Global DC Electrical Characteristics                                      |    |

|    | Table 3.1. Global DC Electrical Characteristics                           | 24 |

| 4. | Pinout and Package Definitions                                            |    |

|    | Table 4.1. Pin Definitions                                                | 25 |

|    | Figure 4.1. TQFP-48 Pin Diagram                                           | 28 |

|    | Figure 4.2. LQFP-32 Pin Diagram                                           | 29 |

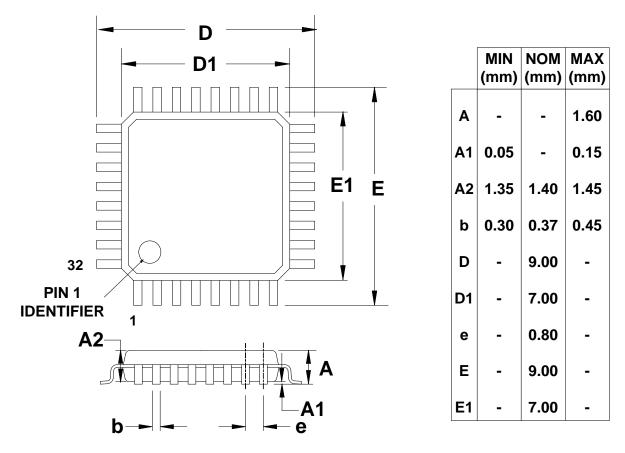

|    | Figure 4.3. TQFP-48 Package Drawing                                       | 30 |

|    | Figure 4.4. LQFP-32 Package Drawing                                       | 31 |

| 5. | ADC (8-Bit, C8051F220/1/6 Only)                                           |    |

|    | Figure 5.1. 8-Bit ADC Functional Block Diagram                            |    |

|    | Figure 5.2. 12-Bit ADC Track and Conversion Example Timing                |    |

|    | Figure 5.3. 8-Bit ADC Window Interrupt Examples                           |    |

|    | Table 5.1.    8-Bit ADC Electrical Characteristics                        | 39 |

| 6. | ADC (12-Bit, C8051F206 Only)                                              |    |

|    | Figure 6.1. 12-Bit ADC Functional Block Diagram                           |    |

|    | Figure 6.2. 12-Bit ADC Track and Conversion Example Timing                |    |

|    | Figure 6.3. 12-Bit ADC Window Interrupt Examples, Right Justified Data    |    |

|    | Figure 6.4. 12-Bit ADC Window Interrupt Examples, Left Justified Data     |    |

|    | Table 6.1.         12-Bit ADC Electrical Characteristics (C8015F206 only) | 49 |

| 7. | Voltage Reference (C8051F206/220/221/226)                                 |    |

|    | Figure 7.1. Voltage Reference Functional Block Diagram                    |    |

| _  | Table 7.1. Reference Electrical Characteristics                           | 51 |

| 8. | Comparators                                                               |    |

|    | Figure 8.1. Comparator Functional Block Diagram                           |    |

|    | Figure 8.2. Comparator Hysteresis Plot                                    |    |

| -  | Table 8.1.   Comparator Electrical Characteristics                        | 57 |

| 9. | CIP-51 Microcontroller                                                    |    |

|    | Figure 9.1. CIP-51 Block Diagram                                          | 58 |

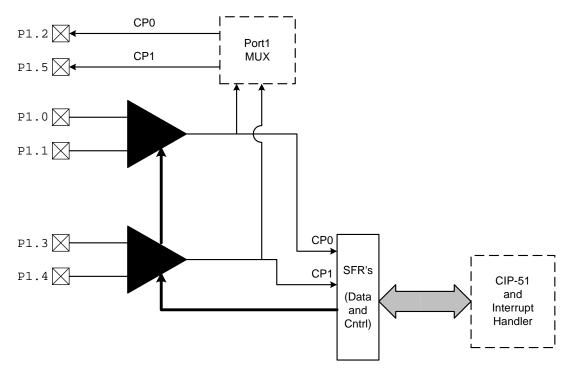

Figure 1.11. Comparator Diagram

## 4. Pinout and Package Definitions

Table 4.1. Pin Definitions

| Name            | <sup>6</sup> F206,<br>F220,<br>226,<br>230,<br>236<br><b>48-Pin</b> | <sup>'F221,</sup><br>231<br><b>32-Pin</b> | Туре          | Description                                                                                                                                                                                                                                                                                     |

|-----------------|---------------------------------------------------------------------|-------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> | 11,31                                                               | 8                                         |               | Digital Voltage Supply.                                                                                                                                                                                                                                                                         |

| GND             | 5,6,8,<br>13,32                                                     | 9                                         |               | Ground. ( <b>Note:</b> Pins 5,6, and 8 on the 48-pin package are not connected (NC), but it is recommended that they be connected to ground.)                                                                                                                                                   |

| MONEN           | 12                                                                  |                                           | D In          | Monitor Enable (on 48 pin package ONLY). Enables reset volt-<br>age monitor function when pulled high (logic "1").                                                                                                                                                                              |

| ТСК             | 25                                                                  | 17                                        | D In          | JTAG Test Clock with internal pull-up.                                                                                                                                                                                                                                                          |

| TMS             | 26                                                                  | 18                                        | D In          | JTAG Test-Mode Select with internal pull-up.                                                                                                                                                                                                                                                    |

| TDI             | 28                                                                  | 20                                        | D In          | JTAG Test Data Input with internal pull-up. TDI is latched on a rising edge of TCK.                                                                                                                                                                                                             |

| TDO             | 27                                                                  | 19                                        | D Out         | JTAG Test Data Output. Data is shifted out on TDO on the falling edge of TCK. TDO output is a tri-state driver.                                                                                                                                                                                 |

| XTAL1           | 9                                                                   | 6                                         | A In          | Crystal Input. This pin is the return for the internal oscillator cir-<br>cuit for a crystal or ceramic resonator. For a precision internal<br>clock, connect a crystal or ceramic resonator from XTAL1 to<br>XTAL2. If overdriven by an external CMOS clock, this becomes<br>the system clock. |

| XTAL2           | 10                                                                  | 7                                         | A Out         | Crystal Output. This pin is the excitation driver for a crystal or ceramic resonator.                                                                                                                                                                                                           |

| RST             | 14                                                                  | 10                                        | D I/O         | Chip Reset. Open-drain output of internal Voltage Supply moni-<br>tor. Is driven low when V <sub>DD</sub> is < 2.7V and MONEN=1, or when a<br>'1'is written to PORSF. An external source can force a system<br>reset by driving this pin low.                                                   |

| VREF            | 7                                                                   | 5                                         | A I/O         | Voltage Reference. When configured as an input, this pin is the voltage reference for the ADC. Otherwise, V <sub>DD</sub> will be the reference. NOTE: this pin is Not Connected (NC) on 'F230/1/6.                                                                                             |

| CP0+            | 4                                                                   | 4                                         | A In          | Comparator 0 Non-Inverting Input.                                                                                                                                                                                                                                                               |

| CP0-            | 3                                                                   | 3                                         | A In          | Comparator 0 Inverting Input.                                                                                                                                                                                                                                                                   |

| CP0             | 2                                                                   | 2                                         | D Out         | Comparator 0 Output                                                                                                                                                                                                                                                                             |

| CP1+            | 1                                                                   | 1                                         | A In          | Comparator 1 Non-Inverting Input.                                                                                                                                                                                                                                                               |

| CP1-            | 48                                                                  | 32                                        | A In          | Comparator 1 Inverting Input.                                                                                                                                                                                                                                                                   |

| CP1             | 47                                                                  | 31                                        | D Out         | Comparator 1 Output                                                                                                                                                                                                                                                                             |

| P0.0/TX         | 40                                                                  | 28                                        | D I/O<br>A In | Port0 Bit0. (See the Port I/O Sub-System section for complete description).                                                                                                                                                                                                                     |

| P0.1/RX         | 39                                                                  | 27                                        | D I/O<br>A In | Port0 Bit1. (See the Port I/O Sub-System section for complete description).                                                                                                                                                                                                                     |

| P0.2/INT0       | 38                                                                  | 26                                        | D I/O<br>A In | Port0 Bit2. (See the Port I/O Sub-System section for complete description).                                                                                                                                                                                                                     |

Figure 4.4. LQFP-32 Package Drawing

| Input Voltage<br>(Analog Input - GND) | ADC Data<br>Word       |                                         | Input Voltage<br>(Analog Input - GND)                          | ADC Data<br>Word |                 |

|---------------------------------------|------------------------|-----------------------------------------|----------------------------------------------------------------|------------------|-----------------|

| REF x (255/256)                       | 0xFF                   |                                         | REF x (255/256)                                                | 0xFF             | ])              |

|                                       |                        | ADWINT<br>not affected                  |                                                                |                  | ADWINT=1        |

|                                       | 0x21                   |                                         |                                                                | 0x21             |                 |

| REF x (32/256)                        | 0x20                   | ADC0LTH                                 | REF x (32/256)                                                 | 0x20             | ADC0GTH         |

|                                       | 0x1F                   |                                         |                                                                | 0x1F             | ADWINT          |

|                                       | 0x11                   | ADWINT=1                                |                                                                | 0x11             | not affected    |

| REF x (16/256)                        | 0x10                   | ADC0GTH                                 | REF x (16/256)                                                 | 0x10             | ADCOLTH         |

|                                       | 0x0F                   |                                         |                                                                | 0x0F             | $\square$       |

|                                       |                        | ADWINT<br>not affected                  |                                                                |                  | ADWINT=1        |

| 0                                     | 0x00                   |                                         | 0                                                              | 0x00             | ])              |

| ADC0LTH = 0x20<br>An ADC End of       | ), ADC0G<br>Conversion | will cause an ADC                       | Given:<br>AMX0SL = 0x00, AM<br>ADC0LTH = 0x10,                 | ADC0GTH          | = 0x20.         |

|                                       |                        | (ADWINT=1) if the<br>< 0x20 and > 0x10. | An ADC End of Cor<br>Window Compare In<br>resulting ADC Data V | nterrupt (AD     | DWINT=1) if the |

Figure 5.3. 8-Bit ADC Window Interrupt Examples

| R/W     | R/W                                                              | R/W                                                                               | R/W                                                                                     | R/W                                                                                   | R/W                         | R/W         | R/W    | Reset Value  |

|---------|------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------|-------------|--------|--------------|

| ADCSC2  | ADCSC1                                                           | ADCSC0                                                                            | -                                                                                       | -                                                                                     | AMPGN2                      | AMPGN1      | AMPGN0 | 01100000     |

| Bit7    | Bit6                                                             | Bit5                                                                              | Bit4                                                                                    | Bit3                                                                                  | Bit2                        | Bit1        | Bit0   | SFR Address: |

|         |                                                                  |                                                                                   |                                                                                         |                                                                                       |                             |             |        | 0xBC         |

|         | 001: SAR (<br>010: SAR (<br>011: SAR (<br>1xx: SAR (<br>NOTE: SA | Conversion<br>Conversion<br>Conversion<br>Conversion<br>Conversion<br>R conversio | Clock = 1 S<br>Clock = 2 S<br>Clock = 4 S<br>Clock = 8 S<br>Clock = 16 S<br>n clock sho | system Cloc<br>system Cloc<br>system Cloc<br>system Cloc<br>Systems Cl<br>uld be less | k<br>ks<br>ks<br>ks<br>ocks | al to 2MHz. |        |              |

|         | UNUSED.<br>AMPGN2–(                                              |                                                                                   | ,                                                                                       |                                                                                       |                             |             |        |              |

| DIG2 0. | 000: Gain :                                                      |                                                                                   | nui / inpine                                                                            |                                                                                       |                             |             |        |              |

|         | 001: Gain :                                                      |                                                                                   |                                                                                         |                                                                                       |                             |             |        |              |

|         | 010: Gain :                                                      | -                                                                                 |                                                                                         |                                                                                       |                             |             |        |              |

|         | 011: Gain = 10x: Gain =                                          |                                                                                   |                                                                                         |                                                                                       |                             |             |        |              |

|         | 1x: Gain =                                                       | -                                                                                 |                                                                                         |                                                                                       |                             |             |        |              |

|         |                                                                  |                                                                                   |                                                                                         |                                                                                       |                             |             |        |              |

## SFR Definition 6.2. ADC0CF: ADC Configuration ('F220/1/6 and 'F206)

## SFR Definition 6.9. ADC0LTL: ADC Less-Than Data Low Byte (C8051F206)

| R/W         | R/W  | R/W  | R/W      | R/W  | R/W   | R/W  | R/W  | Reset Value  |

|-------------|------|------|----------|------|-------|------|------|--------------|

|             |      |      |          |      |       |      |      | 11111111     |

| Bit7        | Bit6 | Bit5 | Bit4     | Bit3 | Bit2  | Bit1 | Bit0 | SFR Address: |

|             |      |      |          |      |       |      |      | 0xC4         |

| Definition: |      | -    | ADC Less |      | Word. |      |      |              |

| Input Voltage<br>(Analog Input - GND)               | ADC Data<br>Word |                                                            | Input Voltage<br>(Analog Input - GND)                              | ADC Data<br>Word |                 |

|-----------------------------------------------------|------------------|------------------------------------------------------------|--------------------------------------------------------------------|------------------|-----------------|

| REF x (4095/4096)                                   | 0x0FFF           |                                                            | REF x (4095/4096)                                                  | 0x0FFF           |                 |

|                                                     |                  | ADWINT<br>not affected                                     |                                                                    |                  | > ADWINT=1      |

|                                                     | 0x0201           |                                                            |                                                                    | 0x0201           |                 |

| REF x (512/4096)                                    | 0x0200           | ADC0LTH:ADC0LTL                                            | REF x (512/4096)                                                   | 0x0200           | ADC0GTH:ADC0GTL |

|                                                     | 0x01FF           | ADWINT=1                                                   |                                                                    | 0x01FF           | ADWINT          |

|                                                     | 0x0101           | ADWINTET                                                   |                                                                    | 0x0101           | not affected    |

| REF x (256/4096)                                    | 0x0100           | ADC0GTH:ADC0GTL                                            | REF x (256/4096)                                                   | 0x0100           | ADC0LTH:ADC0LTL |

|                                                     | 0x00FF           |                                                            |                                                                    | 0x00FF           |                 |

|                                                     |                  | ADWINT<br>not affected                                     |                                                                    |                  | > ADWINT=1      |

| 0                                                   | 0x0000           |                                                            | 0                                                                  | 0x0000           |                 |

| Given:                                              |                  | -                                                          | Given:                                                             |                  |                 |

| AMX0SL = 0x00, A<br>ADC0LTH:ADC0LT<br>ADC0GTH:ADC0G | ΓL               | 0x00, ADLJST = 0,<br>= 0x0200,<br>00.                      | AMX0SL = 0x00, AI<br>ADC0LTH:ADC0LTL<br>ADC0GTH:ADC0GT             | - =              | 0x0100,         |

| Window Compare                                      | Interrupt        | will cause an ADC<br>(ADWINT=1) if the<br>s < 0x0200 and > | An ADC End of Co<br>Window Compare<br>resulting ADC Dat<br>0x0200. | Interrupt (A     | DWINT=1) if the |

Figure 6.3. 12-Bit ADC Window Interrupt Examples, Right Justified Data

#### 9.2.5. Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP, 0x81) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

The MCU also has built-in hardware for a stack record. The stack record is a 32-bit shift register, where each Push or increment SP pushes one record bit onto the register, and each Call pushes two record bits onto the register. (A Pop or decrement SP pops one record bit, and a Return pops two record bits, also.) The stack record circuitry can also detect an overflow or underflow on the 32-bit shift register, and can notify the emulator software even with the MCU running full-speed debug.

## Table 9.3. Special Function Registers

### SFR's are listed in alphabetical order.

| Address | Register             | Description                            | Page No. |

|---------|----------------------|----------------------------------------|----------|

| 0xE0    | ACC                  | Accumulator                            | 73       |

| 0xBC    | ADC0CF               | ADC Configuration                      | 35       |

| 0xE8    | ADC0CN               | ADC Control                            | 36       |

| 0xC5    | ADC0GTH <sup>1</sup> | ADC Greater-Than Data Word (High Byte) | 37       |

| 0xC4    | ADC0GTL <sup>4</sup> | ADC Greater-Than Data Word (Low Byte)  | 46       |

| 0xBF    | ADC0H <sup>1</sup>   | ADC Data Word (High Byte)              | 37       |

| 0xBE    | ADC0L <sup>4</sup>   | ADC Data Word (Low Byte)               | 45       |

| 0xC7    | ADC0LTH <sup>1</sup> | ADC Less-Than Data Word (High Byte)    | 46       |

| 0xCE    | ADC0LTL <sup>4</sup> | ADC Less-Than Data Word (Low Byte)     | 47       |

| 0xBB    | AMX0SL               | ADC MUX Channel Selection              | 34       |

| 0xF0    | В                    | B Register                             | 73       |

| 0x8E    | CKCON                | Clock Control                          | 131      |

| 0x9E    | CPT0CN               | Comparator 0 Control                   | 55       |

| 0x9F    | CPT1CN               | Comparator 1 Control                   | 56       |

| 0x83    | DPH                  | Data Pointer (High Byte)               | 71       |

| 0x82    | DPL                  | Data Pointer (Low Byte)                | 71       |

| 0xE6    | EIE1                 | Extended Interrupt Enable 1            | 79       |

| 0xE7    | EIE2                 | Extended Interrupt Enable 2            | 80       |

| 0xF6    | EIP1                 | External Interrupt Priority 1          | 81       |

| 0xF7    | EIP2                 | External Interrupt Priority 2          | 82       |

| 0xAF    | EMI0CN <sup>3</sup>  | External Memory Interface Control      | 90       |

| 0xB7    | FLACL                | Flash Memory Read Limit                | 89       |

| 0xB6    | FLSCL                | Flash Memory Timing Prescaler          | 89       |

| 0xA8    | IE                   | Interrupt Enable                       | 77       |

| 0xB8    | IP                   | Interrupt Priority Control             | 78       |

| 0xB2    | OSCICN               | Internal Oscillator Control            | 98       |

| 0xB1    | OSCXCN               | External Oscillator Control            | 99       |

| 0x80    | P0                   | Port 0 Latch                           | 105      |

| 0x90    | P1                   | Port 1 Latch                           | 106      |

| 0xA0    | P2                   | Port 2 Latch                           | 107      |

| 0xB0    | P3                   | Port 3 Latch                           | 108      |

| 0xF1    | P0MODE               | Port0 Digital/Analog Output Mode       | 106      |

| 0xF2    | P1MODE               | Port1 Digital/Analog Output Mode       | 107      |

| 0xF3    | P2MODE               | Port2 Digital/Analog Output Mode       | 108      |

| 0xF4    | P3MODE <sup>2</sup>  | Port3 Digital/Analog Output Mode       | 109      |

| 0x87    | PCON                 | Power Control                          | 84       |

## 10. Flash Memory

This MCU includes 8 k + 128 bytes of on-chip, re-programmable Flash memory for program code and nonvolatile data storage. The Flash memory can be programmed in-system, a single byte at a time, through the JTAG interface or by software using the MOVX instruction. Once cleared to 0, a Flash bit must be erased to set it back to 1. The bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution. Data polling to determine the end of the write/erase operation is not required. The Flash memory is designed to withstand at least 20,000 write/erase cycles. Refer to Table 10.1 for the electrical characteristics of the Flash memory.

### **10.1.** Programming The Flash Memory

The simplest means of programming the Flash memory is through the JTAG interface using programming tools provided by Silicon Labs or a third party vendor. This is the only means for programming a non-initialized device. For details on the JTAG commands to program Flash memory, see Section 18.1.

The Flash memory can be programmed by software using the MOVX instruction with the address and data byte to be programmed provided as normal operands. Before writing to Flash memory using MOVX, flash write operations must be enabled by setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1. Writing to Flash remains enabled until the PSWE bit is cleared by software.

To ensure the contents of the Flash contents, it is strongly recommended that the on-chip  $V_{DD}$  monitor be enabled (by tieing the MONEN pin 'high') in any application that writes and/or erases Flash memory from software.

Writes to Flash memory can clear bits but cannot set them. Only an erase operation can set bits in Flash. The byte location to be programmed must be erased before a new value can be written. The 8kbyte Flash memory is organized in 512-byte sectors. The erase operation applies to an entire sector (setting all bytes in the sector to 0xFF). Setting the PSEE Program Store Erase Enable bit (PSCTL.1) and PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 and then using the MOVX command to write a data byte to any byte location within the sector will erase an entire 512-byte sector. The data byte written can be of any value because it is not actually written to the Flash. Flash erasure remains enabled until the PSEE bit is cleared by software. The following sequence illustrates the algorithm for programming the Flash memory by software:

- 1. Disable interrupts.

- 2. Enable Flash Memory write/erase in FLSCL Register using FLASCL bits.

- 3. Set PSEE (PSCTL.1) to enable Flash sector erase.

- 4. Set PSWE (PSCTL.0) to enable Flash writes.

- 5. Use MOVX to write a data byte to any location within the 512-byte sector to be erased.

- 6. Clear PSEE to disable Flash sector erase.

- Use MOVX to write a data byte to the desired byte location within the erased 512-byte sector. Repeat until finished. (Any number of bytes can be written from a single byte to and entire sector.)

- 8. Clear the PSWE bit to disable Flash writes.

Write/Erase timing is automatically controlled by hardware based on the prescaler value held in the Flash Memory Timing Prescaler register (FLSCL). The 4-bit prescaler value FLASCL determines the time interval for write/erase operations. The FLASCL value required for a given system clock is shown in SFR Definition 10.2, along with the formula used to derive the FLASCL values. When FLASCL is set to 1111b, the

## SFR Definition 12.2. RSTSRC: Reset Source

|          | R              | R/W                              | R/W          | R                 | R           | R/W          | R           | Reset Value  |

|----------|----------------|----------------------------------|--------------|-------------------|-------------|--------------|-------------|--------------|

| -        |                | CORSEF                           | SWRSEF       | WDTRSF            | MCDRSF      | PORSF        | PINRSF      | xxxxxxxx     |

| Bit7     | Bit6           | Bit5                             | Bit4         | Bit3              | Bit2        | Bit1         | Bit0        | SFR Address: |

|          |                |                                  |              |                   |             |              |             | 0xEF         |

|          |                |                                  |              |                   |             |              |             |              |

| (Note: D | Do not use rea | ad-modify-wr                     | ite operatio | ons on this I     | egister.)   |              |             |              |

| Bit7:    | RESERVE        | D.                               |              |                   |             |              |             |              |

| Bit6:    |                | Read only 0                      |              |                   |             |              |             |              |

| Bit5:    |                | Comparator C                     | Reset Ena    | able and Fla      | ag          |              |             |              |

|          | Write          |                                  |              |                   |             |              |             |              |

|          |                | ator 0 is not                    |              |                   |             |              |             |              |

|          | •              | ator 0 is a re                   | set source   | (active low)      |             |              |             |              |

|          | Read           |                                  |              |                   |             |              |             |              |

|          |                | alue read fro                    | om CORSE     | F IS NOT DET      | ned if Comp | parator u na | is not been | enabled as   |

|          | a reset sou    |                                  | waa not fr   | am Campar         | ator 0      |              |             |              |

|          |                | of prior reset<br>of prior reset |              |                   |             |              |             |              |

| Bit4:    |                | oftware Rese                     |              | •                 | 0           |              |             |              |

| DIL4.    | Write          | Sitware itest                    |              | uriay             |             |              |             |              |

|          | 0: No Effect   | rt                               |              |                   |             |              |             |              |

|          |                | an internal re                   | set. RST c   | in is not aff     | ected.      |              |             |              |

| Read     |                |                                  |              |                   |             |              |             |              |

|          | 0: Prior res   | set source wa                    | as not from  | write to the      | SWRSF bi    | it.          |             |              |

|          | 1: Prior res   | set source wa                    | as from wri  | te to the SV      | VRSF bit.   |              |             |              |

| Bit3:    | WDTRSF: \      | Watchdog Ti                      | mer Reset    | Flag (Read        | only)       |              |             |              |

|          | 0: Source of   | of prior reset                   | was not fr   | om WDT tin        | neout.      |              |             |              |

|          |                | of prior reset                   |              |                   |             |              |             |              |

| Bit2:    |                | Missing Cloc                     |              |                   |             |              |             |              |

|          |                | of prior reset                   |              |                   |             |              | t.          |              |

|          |                | of prior reset                   |              |                   | ck Detector | timeout.     |             |              |

| Bit1:    |                | wer-On Res                       | et Force a   | nd Flag           |             |              |             |              |

|          | Write          |                                  |              |                   |             |              |             |              |

|          | 0: No effec    |                                  |              |                   |             |              |             |              |

| Dood     | 1: Forces a    | a Power-On                       | Reset. RS    | i is ariven lo    | JW.         |              |             |              |

| Read     | 0. Source      | of prior roact                   | was not fr   |                   |             |              |             |              |

|          |                | of prior reset<br>of prior reset |              |                   |             |              |             |              |

| Bit0:    |                | W Pin Reset                      |              |                   |             |              |             |              |

|          |                | of prior reset                   |              | om <u>RST</u> nin |             |              |             |              |

|          |                | of prior reset                   |              |                   | •           |              |             |              |

|          | 1. 000100 0    |                                  |              |                   |             |              |             |              |

|          |                |                                  |              |                   |             |              |             |              |

## 15.2. Operation

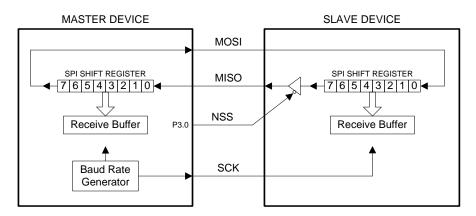

Only a SPI master device can initiate a data transfer. The SPI is placed in master mode by setting the Master Enable flag (MSTEN, SPI0CN.1). Writing a byte of data to the SPI data register (SPI0DAT) when in Master Mode starts a data transfer. The SPI master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPI0CN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. The SPI master can be configured to shift in/out from one to eight bits in a transfer operation in order to accommodate slave devices with different word lengths. The SPIFRS bits in the SPI Configuration Register (SPI0CFG.[2:0]) are used to select the number of bits to shift in/out in a transfer operation.

While the SPI master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. The data byte received from the slave replaces the data in the master's data register. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data transfer in both directions is synchronized with the serial clock generated by the master. Figure 15.3 illustrates the full-duplex operation of an SPI master and an addressed slave.

Figure 15.3. Full Duplex Operation

The SPI data register is double buffered on reads, but not on a write. If a write to SPI0DAT is attempted during a data transfer, the WCOL flag (SPI0CN.6) will be set to logic 1 and the write is ignored. The current data transfer will continue uninterrupted. A read of the SPI data register by the system controller actually reads the receive buffer. If the receive buffer still holds unread data from a previous transfer when the last bit of the current transfer is shifted into the SPI shift register, a receive overrun occurs and the RXOVRN flag (SPI0CN.4) is set to logic 1. The new data is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte causing the overrun is lost.

When the SPI is enabled and not configured as a master, it will operate as an SPI slave. Another SPI device acting as a master will initiate a transfer by driving the NSS signal low. The master then shifts data out of the shift register on the MOSI pin using the its serial clock. The SPIF flag is set to logic 1 at the end of a data transfer (when the NSS signal goes high). The slave can load its shift register for the next data transfer by writing to the SPI data register. The slave must make the write to the data register at least one SPI serial clock cycle before the master starts the next transmission. Otherwise, the byte of data already in the slave's shift register will be transferred.

Multiple masters may reside on the same bus. A Mode Fault flag (MODF, SPI0CN.5) is set to logic 1 when the SPI is configured as a master (MSTEN = 1) and its slave select signal NSS is pulled low. When the Mode Fault flag is set, the MSTEN and SPIEN bits of the SPI control register are cleared by hardware, thereby placing the SPI module in an "off-line" state. In a multiple-master environment, the system controller should check the state of the SLVSEL flag (SPI0CN.2) to ensure the bus is free before setting the MSTEN bit and initiating a data transfer.

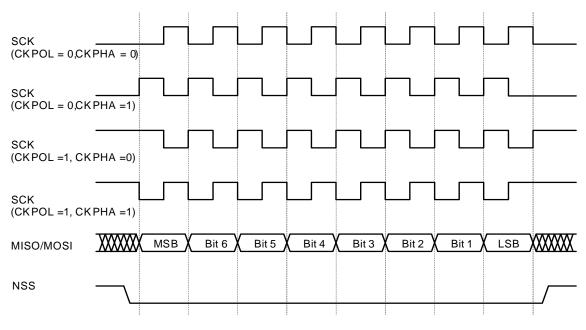

### 15.2. Serial Clock Timing

As shown in Figure 15.4, four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.7) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.6) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. Note: the SPI should be disabled (by clearing the SPIEN bit, SPI0CN.0) while changing the clock phase and polarity.

The SPI Clock Rate Register (SPI0CKR) as shown in SFR Definition 15.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode.

### 15.3. SPI Special Function Registers

The SPI is accessed and controlled through four special function registers in the system controller: SPI0CN Control Register, SPI0DAT Data Register, SPI0CFG Configuration Register, and SPI0CKR Clock Rate Register. The four special function registers related to the operation of the SPI Bus are described in the following section.

| R/W        | R/W       | R/W                         | R/W                         | R/W         | R/W  | R/W  | R/W  | Reset Value         |

|------------|-----------|-----------------------------|-----------------------------|-------------|------|------|------|---------------------|

| SCR7       | SCR6      | SCR5                        | SCR4                        | SCR3        | SCR2 | SCR1 | SCR0 | 00000000            |

| Bit7       | Bit6      | Bit5                        | Bit4                        | Bit3        | Bit2 | Bit1 | Bit0 | SFR Address<br>0x9D |

|            |           |                             |                             |             |      |      |      |                     |

| These bits | determine | the frequer<br>ation. The S | ncy of the S<br>SCK clock f | requency is |      |      |      |                     |

## SFR Definition 15.3. SPI0CKR: SPI Clock Rate Register

## SFR Definition 15.4. SPI0DAT: SPI Data Register

| R/W      | R/W                                                    | R/W                       | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R/W                          | R/W          | R/W           | R/W       | Reset Value          |

|----------|--------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------|---------------|-----------|----------------------|

| -        | -                                                      | -                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                            | -            | -             | -         | 00000000             |

| Bit7     | Bit6                                                   | Bit5                      | Bit4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit3                         | Bit2         | Bit1          | Bit0      | SFR Address:<br>0x9B |

| Bits7–0: | SPI0DAT: S<br>The SPI0D,<br>places the o<br>Mode. A re | AT register<br>data immed | is used to the liately into the liately | ransmit and<br>he shift regi | ster and ini | tiates a tran | sfer wher |                      |

| Oscillator Frequency<br>(MHz) | Divide Factor | Timer 1 Load Value* | Resulting Baud Rate** |

|-------------------------------|---------------|---------------------|-----------------------|

| 7.3728                        | 64            | 0xFC                | 115200                |

| 5.5296                        | 48            | 0xFD                | 115200                |

| 3.6864                        | 32            | 0xFE                | 115200                |

| 1.8432                        | 16            | 0xFF                | 115200                |

| 24.576                        | 320           | 0xEC                | 76800                 |

| 25.0                          | 434           | 0xE5                | 57600 (57870)         |

| 25.0                          | 868           | 0xCA                | 28800                 |

| 24.576                        | 848           | 0xCB                | 28800 (28921)         |

| 24.0                          | 833           | 0xCC                | 28800 (28846)         |

| 23.592                        | 819           | 0xCD                | 28800 (28911)         |

| 22.1184                       | 768           | 0xD0                | 28800                 |

| 18.432                        | 640           | 0xD8                | 28800                 |

| 16.5888                       | 576           | 0xDC                | 28800                 |

| 14.7456                       | 512           | 0xE0                | 28800                 |

| 12.9024                       | 448           | 0xE4                | 28800                 |

| 11.0592                       | 348           | 0xE8                | 28800                 |

| 9.216                         | 320           | 0xEC                | 28800                 |

| 7.3728                        | 256           | 0xF0                | 28800                 |

| 5.5296                        | 192           | 0xF4                | 28800                 |

| 3.6864                        | 128           | 0xF8                | 28800                 |

| 1.8432                        | 64            | 0xFC                | 28800                 |

## Table 16.2. Oscillator Frequencies for Standard Baud Rates (Continued)

## SFR Definition 16.1. SBUF: Serial (UART) Data Buffer

| R/W      | R/W           | R/W                                         | R/W                           | R/W                                       | R/W                          | R/W          | R/W       | Reset Value<br>00000000                      |

|----------|---------------|---------------------------------------------|-------------------------------|-------------------------------------------|------------------------------|--------------|-----------|----------------------------------------------|

| Bit7     | Bit6          | Bit5                                        | Bit4                          | Bit3                                      | Bit2                         | Bit1         | Bit0      | SFR Address:<br>0x99                         |

| Bits7–0: | to SBUF, it g | ally two reg<br>goes to the<br>at initiates | isters; a trai<br>transmit bu | nsmit <sup>`</sup> and a<br>ffer and is h | receive but<br>eld for seria | al transmiss | ion. Movi | ita is moved<br>ng a byte to<br>nes from the |

| TR0            | GATE0 | /INT0 | Counter/Timer |  |  |  |  |  |  |

|----------------|-------|-------|---------------|--|--|--|--|--|--|

| 0              | Х     | Х     | Disabled      |  |  |  |  |  |  |

| 1              | 0     | Х     | Enabled       |  |  |  |  |  |  |

| 1              | 1     | 0     | Disabled      |  |  |  |  |  |  |

| 1              | 1     | 1     | Enabled       |  |  |  |  |  |  |

| X = Don't Care |       |       |               |  |  |  |  |  |  |

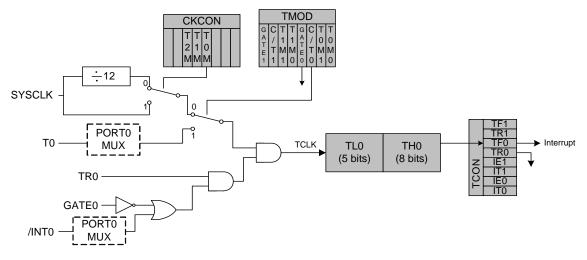

Setting TR0 does not reset the timer register. The timer register should be initialized to the desired value before enabling the timer.

TL1 and TH1 form the 13-bit register for Timer 1 in the same manner as described above for TL0 and TH0. Timer 1 is configured and controlled using the relevant TCON and TMOD bits just as with Timer 0.

Figure 17.1. T0 Mode 0 Block Diagram

#### 17.1.2. Mode 1: 16-bit Counter/Timer

Mode 1 operation is the same as Mode 0, except that the counter/timer registers use all 16 bits. The counter/timers are enabled and configured in Mode 1 in the same manner as for Mode 0.

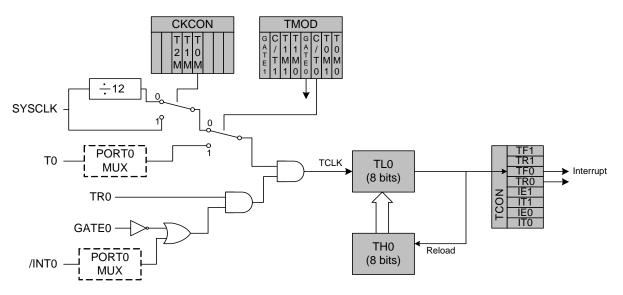

#### 17.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. The TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0. Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0.

Figure 17.2. T0 Mode 2 Block Diagram

| R/W      | R/W                                                                                                                                                                                                                                                                                                                                    | R/W        | R/W           | R/W         | R/W  | R/W  | R/W                  | Reset Value |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|-------------|------|------|----------------------|-------------|--|--|--|--|

| -        | -                                                                                                                                                                                                                                                                                                                                      | T2M        | T1M           | TOM         | -    | -    | -                    | 00000000    |  |  |  |  |

| Bit7     | Bit6                                                                                                                                                                                                                                                                                                                                   | Bit5       | Bit4          | Bit3        | Bit2 | Bit0 | SFR Address:<br>0x8E |             |  |  |  |  |

| Bits7–6: | UNUSED. Read = 00b, Write = don't care.                                                                                                                                                                                                                                                                                                |            |               |             |      |      |                      |             |  |  |  |  |

| Bit5:    | <ul> <li>T2M: Timer 2 Clock Select.</li> <li>This bit controls the division of the system clock supplied to Timer 2. This bit is ignored when the timer is in baud rate generator mode or counter mode (i.e. C/T2 = 1).</li> <li>0: Timer 2 uses the system clock divided by 12.</li> <li>1: Timer 2 uses the system clock.</li> </ul> |            |               |             |      |      |                      |             |  |  |  |  |

| Bit4:    | <ul> <li>T1M: Timer 1 Clock Select.</li> <li>This bit controls the division of the system clock supplied to Timer 1.</li> <li>0: Timer 1 uses the system clock divided by 12.</li> <li>1: Timer 1 uses the system clock.</li> </ul>                                                                                                    |            |               |             |      |      |                      |             |  |  |  |  |

| Bit3:    | <ul> <li>T0M: Timer 0 Clock Select.</li> <li>This bit controls the division of the system clock supplied to Counter/Timer 0.</li> <li>0: Counter/Timer uses the system clock divided by 12.</li> <li>1: Counter/Timer uses the system clock.</li> </ul>                                                                                |            |               |             |      |      |                      |             |  |  |  |  |

| Bits2–0: | UNUSED.                                                                                                                                                                                                                                                                                                                                | Read = 000 | 0b, Write = 0 | don't care. |      |      |                      |             |  |  |  |  |

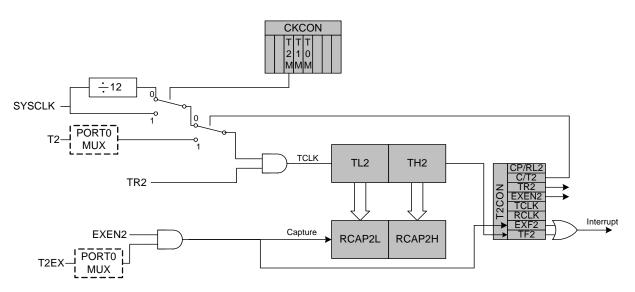

#### 17.2.1. Mode 0: 16-bit Counter/Timer with Capture

In this mode, Timer 2 operates as a 16-bit counter/timer with capture facility. A high-to-low transition on the T2EX input pin causes the 16-bit value in Timer 2 (TH2, TL2) to be loaded into the capture registers (RCAP2H, RCAP2L).

Timer 2 can use either SYSCLK, SYSCLK divided by 12, or high-to-low transitions on the external T2 input pin as its clock source when operating in Counter/Timer with Capture mode. Clearing the C/T2 bit (T2CON.1) selects the system clock as the input for the timer (divided by one or twelve as specified by the Timer Clock Select bit T2M in CKCON). When C/T2 is set to logic 1, a high-to-low transition at the T2 input pin increments the counter/timer register. As the 16-bit counter/timer register increments and overflows from 0xFFFF to 0x0000, the TF2 timer overflow flag (T2CON.7) is set and an interrupt will occur if the interrupt is enabled.

Counter/Timer with Capture mode is selected by setting the Capture/Reload Select bit CP/RL2 (T2CON.0) and the Timer 2 Run Control bit TR2 (T2CON.2) to logic 1. The Timer 2 External Enable EXEN2 (T2CON.3) must also be set to logic 1 to enable a capture. If EXEN2 is cleared, transitions on T2EX will be ignored.

Figure 17.4. T2 Mode 0 Block Diagram

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                         |                                |              |              |            |               | Reset Value |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------|--------------|------------|---------------|-------------|--|--|--|--|--|

| WRMD3                                                                                                           | WRMD2                                                                                                                                                                                                                                                                                                                                                                                                                 | 2 WRMD1                                                                                                                                                 | RMD1 WRMD0 RDMD3               |              | RDMD2        | RDMD1      | RDMD0         | 0000000     |  |  |  |  |  |

| Bit7                                                                                                            | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit5                                                                                                                                                    | Bit4                           | Bit3         | Bit2         | Bit1       | Bit0          |             |  |  |  |  |  |

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                         |                                |              |              |            |               |             |  |  |  |  |  |

| This register determines how the Flash interface logic will respond to reads and writes to the FL DAT Register. |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                         |                                |              |              |            |               |             |  |  |  |  |  |

| Bits7–4:                                                                                                        | The Write<br>DAT Regi<br>0000: A<br>ig                                                                                                                                                                                                                                                                                                                                                                                | ster per the fo<br>FLASHDAT<br>pnored.                                                                                                                  | responds to writes to the FLAS |              |              |            |               |             |  |  |  |  |  |

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                         |                                |              |              |            |               |             |  |  |  |  |  |

|                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                       | by the FLASHADR register. FLASHADR is incremented by one when complete.                                                                                 |                                |              |              |            |               |             |  |  |  |  |  |

|                                                                                                                 | <ul> <li>0010: A FLASHDAT write initiates an erasure (sets all bytes to 0xFF) of the Flash page containing the address in FLASHADR. FLASHDAT must be 0xA5 for the erase to occur. FLASHADR is not affected. If FLASHADR = 0x1DFE – 0x1DFF, the entire user space will be erased (i.e. entire Flash memory except for Reserved area 0x1E00 – 0x1FFF).</li> <li>(All other values for WRMD3–0 are reserved.)</li> </ul> |                                                                                                                                                         |                                |              |              |            |               |             |  |  |  |  |  |

| Dite 2 Or                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                       | O. Dood Mod                                                                                                                                             | Coloct Dite                    |              |              |            |               |             |  |  |  |  |  |