Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                 |

|----------------------------|-----------------------------------------------------------------|

| Product Status             | Not For New Designs                                             |

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 25MHz                                                           |

| Connectivity               | SPI, UART/USART                                                 |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                |

| Number of I/O              | 32                                                              |

| Program Memory Size        | 8KB (8K x 8)                                                    |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 256 x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 48-TQFP                                                         |

| Supplier Device Package    | 48-TQFP (7x7)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f230-gqr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1. | System Overview                            | 11 |

|----|--------------------------------------------|----|

|    | 1.1. CIP-51TM Microcontroller Core         |    |

|    | 1.1.1. Fully 8051 Compatible               |    |

|    | 1.1.2. Improved Throughput                 |    |

|    | 1.1.3. Additional Features                 |    |

|    | 1.2. On-Board Memory                       |    |

|    | 1.3. JTAG                                  |    |

|    | 1.4. Digital/Analog Configurable I/O       |    |

|    | 1.5. Serial Ports                          |    |

|    | 1.6. Analog to Digital Converter           |    |

| _  | 1.7. Comparators                           |    |

|    | Absolute Maximum Ratings                   |    |

|    | Global DC Electrical Characteristics       |    |

|    | Pinout and Package Definitions             |    |

| 5. | ADC (8-Bit, C8051F220/1/6 Only)            |    |

|    | 5.1. Analog Multiplexer and PGA            |    |

|    | 5.2. ADC Modes of Operation                |    |

| _  | 5.3. ADC Programmable Window Detector      |    |

| 6. | ADC (12-Bit, C8051F206 Only)               |    |

|    | 6.1. Analog Multiplexer and PGA            |    |

|    | 6.2. ADC Modes of Operation                |    |

| _  | 6.3. ADC Programmable Window Detector      |    |

|    | Voltage Reference (C8051F206/220/221/226)  |    |

|    | Comparators                                |    |

| 9. | CIP-51 Microcontroller                     |    |

|    | 9.1. Instruction Set                       |    |

|    | 9.1.1. Instruction and CPU Timing          |    |

|    | 9.1.2. MOVX Instruction and Program Memory |    |

|    | 9.2. Memory Organization                   |    |

|    | 9.2.1. Program Memory                      |    |

|    | 9.2.2. Data Memory                         |    |

|    | 9.2.3. General Purpose Registers           |    |

|    | 9.2.4. Bit Addressable Locations           |    |

|    | 9.2.5. Stack                               |    |

|    | 9.3. Special Function Registers            |    |

|    | 9.3.1. Register Descriptions               |    |

|    | 9.4. Interrupt Handler                     |    |

|    | 9.4.1. MCU Interrupt Sources and Vectors   |    |

|    | 9.4.2. External Interrupts                 | 74 |

|    | 9.4.3. Software Controlled Interrupts      |    |

|    | 9.4.4. Interrupt Priorities                |    |

|    | 9.4.5. Interrupt Latency                   |    |

|    | 9.4.6. Interrupt Register Descriptions     | 77 |

| Table 9.1. CIP     | P-51 Instruction Set Summary                     | 60  |

|--------------------|--------------------------------------------------|-----|

|                    | mory Map                                         |     |

|                    | ecial Function Register Memory Map               |     |

|                    | ecial Function Registers                         |     |

| •                  | errupt Summary                                   |     |

| 10. Flash Memory   | '                                                |     |

|                    | ash Memory Electrical Characteristics            | 86  |

|                    | ash Program Memory Security Bytes                |     |

| •                  | M (C8051F206/226/236)                            |     |

| 12. Reset Sources  | ·                                                |     |

|                    | eset Sources Diagram                             | 91  |

|                    | OD Monitor Timing Diagram                        |     |

|                    | DD Monitor Electrical Characteristics            |     |

| 13. Oscillator     |                                                  |     |

|                    | scillator Diagram                                | 97  |

|                    | ernal Oscillator Electrical Characteristics      |     |

| 14. Port Input/Out |                                                  |     |

|                    | ort I/O Functional Block Diagram                 | 102 |

|                    | ort I/O Cell Block Diagram                       |     |

|                    | rt I/O DC Electrical Characteristics             |     |

| 15. Serial Periphe |                                                  | 100 |

| -                  | PI Block Diagram                                 | 110 |

|                    | Plock Diagram                                    |     |

|                    | ıll Duplex Operation                             |     |

|                    | Ill Duplex Operation                             |     |

| 16.UART            | iii Duplex Operation                             | 110 |

|                    | ART Block Diagram                                | 117 |

|                    | ART Modes                                        |     |

|                    | ART Mode 0 Interconnect                          |     |

| •                  | ART Mode 0 Timing Diagram                        |     |

|                    | ART Mode 1 Timing Diagram                        |     |

|                    | ART Modes 1, 2, and 3 Interconnect Diagram       |     |

|                    | ART Modes 2 and 3 Timing Diagram                 |     |

|                    | ART Multi-Processor Mode Interconnect Diagram    |     |

| _                  | cillator Frequencies for Standard Baud Rates     |     |

| 17. Timers         | ciliator i requericies for Standard Dadd Nates   | 122 |

|                    | ) Mode 0 Block Diagram                           | 126 |

| _                  | ) Mode 2 Block Diagram                           |     |

| •                  |                                                  |     |

|                    | ) Mode 3 Block Diagram<br>2 Mode 0 Block Diagram |     |

| •                  |                                                  |     |

|                    | 2 Mode 1 Block Diagram                           |     |

| 19 ITAC            | 2 Mode 2 Block Diagram                           | 130 |

Rev. 1.6

8

# 2. Absolute Maximum Ratings

Table 2.1. Absolute Maximum Ratings\*

| Parameter                                                                     | Conditions | Min  | Тур | Max                   | Units |

|-------------------------------------------------------------------------------|------------|------|-----|-----------------------|-------|

| Ambient Temperature under Bias                                                |            | -55  | _   | 125                   | °C    |

| Storage Temperature                                                           |            | -65  | _   | 150                   | °C    |

| Voltage on any Pin (except V <sub>DD</sub> and Port I/O) with respect to DGND |            | -0.3 | _   | V <sub>DD</sub> + 0.3 | V     |

| Voltage on any Port I/O Pin or RST pins with respect to DGND                  |            | -0.3 | _   | 5.8                   | V     |

| Voltage on V <sub>DD</sub> with respect to DGND                               |            | -0.3 |     | 4.2                   | V     |

| Total Power Dissipation                                                       |            | _    | 1.0 | 800                   | W     |

| Maximum Output Current Sunk by any Port pin                                   |            | _    | _   | 200                   | mA    |

| Maximum Output Current Sunk by any other I/O pin                              |            | _    | _   | 25                    | mA    |

| Maximum Output Current Sourced by any Port pin                                |            | _    | _   | 200                   | mA    |

| Maximum Output Current Sourced by any other I/O pin                           |            | _    | _   | 25                    | mA    |

\*Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the devices at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### **Global DC Electrical Characteristics** 3.

**Table 3.1. Global DC Electrical Characteristics**

-40 to +85 °C unless otherwise specified.

| Parameter                                                                                    | Conditions                                        | Min | Тур               | Max | Units          |

|----------------------------------------------------------------------------------------------|---------------------------------------------------|-----|-------------------|-----|----------------|

| Analog Supply Voltage <sup>1</sup>                                                           |                                                   | 2.7 | 3.0               | 3.6 | V              |

| V <sub>DD</sub> supply current with ADC and comparators active, and CPU active               | Clock = 25 MHz<br>Clock = 1 MHz<br>Clock = 32 kHz | _   | 13<br>1.5<br>300  | _   | mA<br>mA<br>μA |

| V <sub>DD</sub> supply current with ADC and comparators active, and CPU inactive (Idle Mode) | Clock = 25 MHz<br>Clock = 1 MHz<br>Clock = 32 kHz | _   | 9<br>1.8<br>275   | _   | mA<br>mA<br>μA |

| V <sub>DD</sub> supply current with ADC and comparators inactive, and CPU active             | Clock = 25 MHz<br>Clock = 1 MHz<br>Clock = 32 kHz | _   | 12.5<br>1.0<br>25 | _   | mA<br>mA<br>μA |

| Digital Supply Current with CPU inactive (Idle Mode)                                         | Clock = 25 MHz<br>Clock = 1 MHz<br>Clock = 32 kHz | _   | 8.5<br>1.4<br>25  | _   | mA<br>mA<br>μA |

| Digital Supply Current (Stop Mode), V <sub>DD</sub> monitor enabled                          | Oscillator not running                            | _   | 10                | _   | μA             |

| Digital Supply Current (Stop Mode), V <sub>DD</sub> monitor disabled                         | Oscillator not running                            | _   | 0.1               | _   | μA             |

| Digital Supply RAM Data Retention Voltage                                                    |                                                   | _   | 1.5               | _   | V              |

| Specified Operating Temperature Range                                                        |                                                   | -40 | _                 | +85 | °C             |

| SYSCLK (system clock frequency) <sup>2</sup>                                                 |                                                   | 0   | _                 | 25  | MHz            |

| Tsysl (SYSCLK low time)                                                                      |                                                   | 18  | _                 | _   | ns             |

| Tsysh (SYSCLK high time)                                                                     |                                                   | 18  | _                 | _   | ns             |

Rev. 1.6

- Analog Supply AV+ must be greater than 1 V for V<sub>DD</sub> monitor to operate.

SYSCLK must be at least 32 kHz to enable debugging.

24

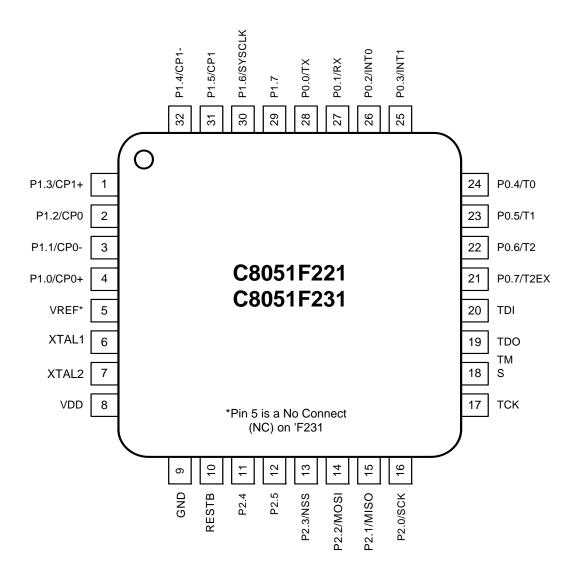

Figure 4.2. LQFP-32 Pin Diagram

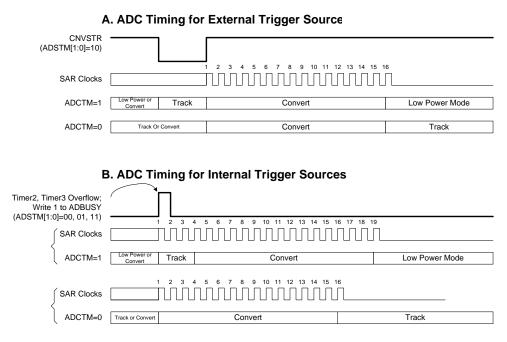

## 6.2. ADC Modes of Operation

The ADC has a maximum conversion speed of 100 ksps. The ADC conversion clock is derived from the system clock. The ADC conversion clock is derived from a divided version of SYSCLK. Divide ratios of 1, 2, 4, 8, or 16 are supported by setting the ADCSC bits in the ADC0CF Register. This is useful to adjust conversion speed to accommodate different system clock speeds.

A conversion can be initiated in one of two ways, depending on the programmed states of the ADC Start of Conversion Mode bits (ADSTM1, ADSTM0) in ADC0CN. Conversions may be initiated by:

- 1. Writing a 1 to the ADBUSY bit of ADC0CN;

- 2. A Timer 2 overflow (i.e. timed continuous conversions).

Writing a 1 to ADBUSY provides software control of the ADC whereby conversions are performed "on-demand". During conversion, the ADBUSY bit is set to 1 and restored to 0 when conversion is complete. The falling edge of ADBUSY triggers an interrupt (when enabled) and sets the ADCINT interrupt flag in the ADC0CN register. Note: When conversions are performed "on-demand", the ADCINT flag, not ADBUSY, should be polled to determine when the conversion has completed. Converted data is available in the ADC data word register, ADC0H.

The ADCTM bit in register ADC0CN controls the ADC track-and-hold mode. In its default state, the ADC input is continuously tracked, except when a conversion is in progress. Setting ADCTM to 1 allows one of two different low power track-and-hold modes to be specified by states of the ADSTM1-0 bits (also in ADC0CN):

- 1. Tracking begins with a write of 1 to ADBUSY and lasts for 3 SAR clocks;

- 2. Tracking starts with an overflow of Timer 2 and lasts for 3 SAR clocks.

Tracking can be disabled (shutdown) when the entire chip is in low power standby or sleep modes.

Figure 6.2. 12-Bit ADC Track and Conversion Example Timing

#### SFR Definition 6.3. ADC0CN: ADC Control ('F220/1/6 and 'F206)

| R/W   | R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W               | Reset Value  |

|-------|-------|--------|--------|--------|--------|--------|-------------------|--------------|

| ADCEN | ADCTM | ADCINT | ADBUSY | ADSTM1 | ADSTM0 | ADWINT | ADLJST            | 00000000     |

| Bit7  | Bit6  | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0              | SFR Address: |

|       |       |        |        |        |        |        | (bit addressable) | 0xE8         |

Bit7: ADCEN: ADC Enable Bit

0: ADC Disabled. ADC is in low power shutdown.

1: ADC Enabled. ADC is active and ready for data conversions.

Bit6: ADCTM: ADC Track Mode Bit

0: When the ADC is enabled, tracking is continuous unless a conversion is in process

1: Tracking Defined by ADSTM1-0 bits

ADSTM1-0:

00: Tracking starts with the write of 1 to ADBUSY and lasts for 3 SAR clocks

01: RESERVED 10: RESERVED

11: Tracking started by the overflow of Timer 2 and last for 3 SAR clocks

Bit5: ADCINT: ADC Conversion Complete Interrupt Flag (cleared by software).

0: ADC has not completed a data conversion since the last time this flag was cleared

1: ADC has completed a data conversion

Bit4: ADBUSY: ADC Busy Bit

Read

0: ADC Conversion complete or no valid data has been converted since a reset. The falling edge of ADBUSY generates an interrupt when enabled.

1: ADC Busy converting data

Write

0: No effect

1: Starts ADC Conversion if ADSTM1-0 = 00b

Bits3-2: ADSTM1-0: ADC Start of Conversion Mode Bits

00: ADC conversion started upon a write of 1 to ADBUSY

01: RESERVED 10: RESERVED

11: ADC conversions initiated on overflows of Timer 2

Bit1: ADWINT: ADC Window Compare Interrupt Flag

0: ADC Window Comparison Data match has not occurred

1: ADC Window Comparison Data match occurred

Bit0: ADLJST: ADC Left Justify Data Bit

0: Data in ADC0H:ADC0L registers are right justified.

1: Data in ADC0H:ADC0L registers are left justified.

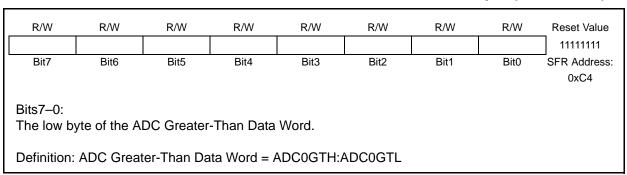

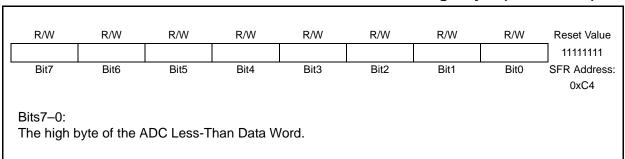

## 6.3. ADC Programmable Window Detector

The ADC programmable window detector is very useful in many applications. It continuously compares the ADC output to user-programmed limits and notifies the system when an out-of-band condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (ADWINT in ADCOCN) can also be used in polled mode. The high and low bytes of the reference words are loaded into the ADC Greater-Than and ADC Less-Than registers (ADCOGTH, ADCOGTL, ADCOLTH, and ADCOLTL). Figure 6.3 and Figure 6.4 show example comparisons for reference. Notice that the window detector flag can be asserted when the measured data is inside or outside the user-programmed limits, depending on the programming of the ADCOGTx and ADCOLTx registers.

#### SFR Definition 6.6. ADC0GTH: ADC Greater-Than Data High Byte (C8051F206)

| R/W                    | R/W                                                          | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value          |  |  |  |

|------------------------|--------------------------------------------------------------|------|------|------|------|------|------|----------------------|--|--|--|

| Bit7                   | Bit6                                                         | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xC5 |  |  |  |

| Bits7–0:<br>The high t | Bits7–0:<br>The high byte of the ADC Greater-Than Data Word. |      |      |      |      |      |      |                      |  |  |  |

# SFR Definition 6.7. ADC0GTL: ADC Greater-Than Data Low Byte (C8051F206)

#### SFR Definition 6.8. ADC0LTH: ADC Less-Than Data High Byte (C8051F206)

SILICON LABS

Table 9.1. CIP-51 Instruction Set Summary (Continued)

| Mnemonic           | Description                           | Bytes | Clock<br>Cycles |

|--------------------|---------------------------------------|-------|-----------------|

| INC @Ri            | Increment indirect RAM                | 1     | 2               |

| DEC A              | Decrement A                           | 1     | 1               |

| DEC Rn             | Decrement register                    | 1     | 1               |

| DEC direct         | Decrement direct byte                 | 2     | 2               |

| DEC @Ri            | Decrement indirect RAM                | 1     | 2               |

| INC DPTR           | Increment Data Pointer                | 1     | 1               |

| MUL AB             | Multiply A and B                      | 1     | 4               |

| DIV AB             | Divide A by B                         | 1     | 8               |

| DA A               | Decimal Adjust A                      | 1     | 1               |

| Logical Operations |                                       |       |                 |

| ANL A,Rn           | AND Register to A                     | 1     | 1               |

| ANL A,direct       | AND direct byte to A                  | 2     | 2               |

| ANL A,@Ri          | AND indirect RAM to A                 | 1     | 2               |

| ANL A,#data        | AND immediate to A                    | 2     | 2               |

| ANL direct,A       | AND A to direct byte                  | 2     | 2               |

| ANL direct,#data   | AND immediate to direct byte          | 3     | 3               |

| ORL A,Rn           | OR Register to A                      | 1     | 1               |

| ORL A,direct       | OR direct byte to A                   | 2     | 2               |

| ORL A,@Ri          | OR indirect RAM to A                  | 1     | 2               |

| ORL A,#data        | OR immediate to A                     | 2     | 2               |

| ORL direct,A       | OR A to direct byte                   | 2     | 2               |

| ORL direct,#data   | OR immediate to direct byte           | 3     | 3               |

| XRL A,Rn           | Exclusive-OR Register to A            | 1     | 1               |

| XRL A,direct       | Exclusive-OR direct byte to A         | 2     | 2               |

| XRL A,@Ri          | Exclusive-OR indirect RAM to A        | 1     | 2               |

| XRL A,#data        | Exclusive-OR immediate to A           | 2     | 2               |

| XRL direct,A       | Exclusive-OR A to direct byte         | 2     | 2               |

| XRL direct,#data   | Exclusive-OR immediate to direct byte | 3     | 3               |

| CLR A              | Clear A                               | 1     | 1               |

| CPL A              | Complement A                          | 1     | 1               |

| RL A               | Rotate A left                         | 1     | 1               |

| RLC A              | Rotate A left through carry           | 1     | 1               |

| RR A               | Rotate A right                        | 1     | 1               |

| RRC A              | Rotate A right through carry          | 1     | 1               |

| SWAP A             | Swap nibbles of A                     | 1     | 1               |

| Data Transfer      | 1                                     | L     | 1               |

| MOV A,Rn           | Move register to A                    | 1     | 1               |

| MOV A,direct       | Move direct byte to A                 | 2     | 2               |

| MOV A,@Ri          | Move indirect RAM to A                | 1     | 2               |

#### 9.2. Memory Organization

The memory organization of the CIP-51 System Controller is similar to that of a standard 8051. There are two separate memory spaces: program memory and data memory. Program and data memory share the same address space but are accessed via different instruction types. There are 256 bytes of internal data memory and 8 kB of internal program memory address space implemented within the CIP-51. The CIP-51 memory organization is shown in Figure 9.2.

#### 9.2.1. Program Memory

The CIP-51 has a 8 kB program memory space. The MCU implements 8320 bytes of this program memory space as in-system, reprogrammable Flash memory, organized in a contiguous block from addresses 0x0000 to 0x207F. Note: 512 bytes (0x1E00 – 0x1FFF) of this memory are reserved for factory use and are not available for user program storage.

Program memory is normally assumed to be read-only. However, the CIP-51 can write to program memory by setting the Program Store Write Enable bit (PSCTL.0) and using the MOVX instruction. This feature provides a mechanism for the CIP-51 to update program code and use the program memory space for non-volatile data storage. Refer to Section 10 Flash Memory for further details.

#### 9.2.2. Data Memory

The CIP-51 implements 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct bit addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F will access the upper 128 bytes of data memory. Figure 9.2 illustrates the data memory organization of the CIP-51.

Additionally, the C8051F206/226/236 feature 1024 Bytes of RAM mapped in the external data memory space. All address locations may be accessed using the MOVX instruction. (Please see Section 11).

**Table 9.3. Special Function Registers**

SFR's are listed in alphabetical order.

| Address | Register             | Description                            | Page No. |

|---------|----------------------|----------------------------------------|----------|

| 0xE0    | ACC                  | Accumulator                            | 73       |

| 0xBC    | ADC0CF               | ADC Configuration                      | 35       |

| 0xE8    | ADC0CN               | ADC Control                            | 36       |

| 0xC5    | ADC0GTH <sup>1</sup> | ADC Greater-Than Data Word (High Byte) | 37       |

| 0xC4    | ADC0GTL <sup>4</sup> | ADC Greater-Than Data Word (Low Byte)  | 46       |

| 0xBF    | ADC0H <sup>1</sup>   | ADC Data Word (High Byte)              | 37       |

| 0xBE    | ADC0L <sup>4</sup>   | ADC Data Word (Low Byte)               | 45       |

| 0xC7    | ADC0LTH <sup>1</sup> | ADC Less-Than Data Word (High Byte)    | 46       |

| 0xCE    | ADC0LTL <sup>4</sup> | ADC Less-Than Data Word (Low Byte)     | 47       |

| 0xBB    | AMX0SL               | ADC MUX Channel Selection              | 34       |

| 0xF0    | В                    | B Register                             | 73       |

| 0x8E    | CKCON                | Clock Control                          | 131      |

| 0x9E    | CPT0CN               | Comparator 0 Control                   | 55       |

| 0x9F    | CPT1CN               | Comparator 1 Control                   | 56       |

| 0x83    | DPH                  | Data Pointer (High Byte)               | 71       |

| 0x82    | DPL                  | Data Pointer (Low Byte)                | 71       |

| 0xE6    | EIE1                 | Extended Interrupt Enable 1            | 79       |

| 0xE7    | EIE2                 | Extended Interrupt Enable 2            | 80       |

| 0xF6    | EIP1                 | External Interrupt Priority 1          | 81       |

| 0xF7    | EIP2                 | External Interrupt Priority 2          | 82       |

| 0xAF    | EMI0CN <sup>3</sup>  | External Memory Interface Control      | 90       |

| 0xB7    | FLACL                | Flash Memory Read Limit                | 89       |

| 0xB6    | FLSCL                | Flash Memory Timing Prescaler          | 89       |

| 0xA8    | IE                   | Interrupt Enable                       | 77       |

| 0xB8    | IP                   | Interrupt Priority Control             | 78       |

| 0xB2    | OSCICN               | Internal Oscillator Control            | 98       |

| 0xB1    | OSCXCN               | External Oscillator Control            | 99       |

| 0x80    | P0                   | Port 0 Latch                           | 105      |

| 0x90    | P1                   | Port 1 Latch                           | 106      |

| 0xA0    | P2                   | Port 2 Latch                           | 107      |

| 0xB0    | P3                   | Port 3 Latch                           | 108      |

| 0xF1    | POMODE               | Port0 Digital/Analog Output Mode       | 106      |

| 0xF2    | P1MODE               | Port1 Digital/Analog Output Mode       | 107      |

| 0xF3    | P2MODE               | Port2 Digital/Analog Output Mode       | 108      |

| 0xF4    | P3MODE <sup>2</sup>  | Port3 Digital/Analog Output Mode       | 109      |

| 0x87    | PCON                 | Power Control                          | 84       |

| 0.001   | 1 0011               | 1 OVVC1 CONTROL                        | 04       |

# SFR Definition 9.5. ACC: Accumulator

| R/W              | Reset Value  |

|-------|-------|-------|-------|-------|-------|-------|------------------|--------------|

| ACC.7 | ACC.6 | ACC.5 | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0            | 00000000     |

| Bit7  | Bit6  | Bit5  | Bit4  | Bit3  | Bit2  | Bit1  | Bit0             | SFR Address: |

|       |       |       |       |       |       |       | (hit addressable | ) 0vE0       |

Bits 7-0: ACC: Accumulator

This register is the accumulator for arithmetic operations.

# SFR Definition 9.6. B: B Register

| R/W              | Reset Value  |

|------|------|------|------|------|------|------|------------------|--------------|

| B.7  | B.6  | B.5  | B.4  | B.3  | B.2  | B.1  | B.0              | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0             | SFR Address: |

|      |      |      |      |      |      |      | (bit addressable | e) 0xF0      |

Bits 7-0: B: B Register

This register serves as a second accumulator for certain arithmetic operations.

## SFR Definition 9.10. EIE1: Extended Interrupt Enable 1

| R/W   | R/W   | R/W   | R/W   | R/W  | R/W    | R/W  | R/W   | Reset Value  |

|-------|-------|-------|-------|------|--------|------|-------|--------------|

| ECP1R | ECP1F | ECP0R | ECP0F | -    | EWADC0 | -    | ESPI0 | 00000000     |

| Bit7  | Bit6  | Bit5  | Bit4  | Bit3 | Bit2   | Bit1 | Bit0  | SFR Address: |

|       |       |       |       |      |        |      |       | 0xF6         |

Bit7: ECP1R: Enable Comparator 1 (CP1) Rising Edge Interrupt.

This bit sets the masking of the CP1 interrupt.

0: Disable CP1 Rising Edge interrupt.

1: Enable interrupt requests generated by the CP1RIF flag (CPT1CN.3).

Bit6: ECP1F: Enable Comparator 1 (CP1) Falling Edge Interrupt.

This bit sets the masking of the CP1 interrupt.

0: Disable CP1 Falling Edge interrupt.

1: Enable interrupt requests generated by the CP1FIF flag (CPT1CN.4).

Bit5: ECP0R: Enable Comparator 0 (CP0) Rising Edge Interrupt.

This bit sets the masking of the CP0 interrupt.

0: Disable CP0 Rising Edge interrupt.

1: Enable interrupt requests generated by the CP0RIF flag (CPT0CN.3).

Bit4: ECP0F: Enable Comparator 0 (CP0) Falling Edge Interrupt.

This bit sets the masking of the CP0 interrupt.

0: Disable CP0 Falling Edge interrupt.

1: Enable interrupt requests generated by the CP0FIF flag (CPT0CN.4).

Bit3: Reserved. Read = 0, Write = don't care.

Bit2: EWADC0: Enable Window Comparison ADC0 Interrupt.

This bit sets the masking of ADC0 window compare interrupt.

0: Disable ADC0 Window Comparison Interrupt.

1: Enable Interrupt requests generated by ADC0 Window Comparisons.

Bit1: Reserved. Read = 0, Write = don't care.

Bit0: ESPI0: Enable Serial Peripheral Interface 0 Interrupt.

This bit sets the masking of SPI0 interrupt.

0: Disable all SPI0 interrupts.

1: Enable Interrupt requests generated by SPI0.

The Flash Access Limit security feature protects proprietary program code and data from being read by software running on the CIP-51. This feature provides support for OEMs that wish to program the MCU with proprietary value-added firmware before distribution. The value-added firmware can be protected while allowing additional code to be programmed in remaining program memory space later.

The Software Read Limit (SRL) is a 16-bit address that establishes two logical partitions in the program memory space. The first is an upper partition consisting of all the program memory locations at or above the SRL address, and the second is a lower partition consisting of all the program memory locations starting at 0x0000 up to (but excluding) the SRL address. Software in the upper partition can execute code in the lower partition, but is prohibited from reading locations in the lower partition using the MOVC instruction. (Executing a MOVC instruction from the upper partition with a source address in the lower partition will always return a data value of 0x00.) Software running in the lower partition can access locations in both the upper and lower partition without restriction.

The Value-added firmware should be placed in the lower partition. On reset, control is passed to the value-added firmware via the reset vector. Once the value-added firmware completes its initial execution, it branches to a predetermined location in the upper partition. If entry points are published, software running in the upper partition may execute program code in the lower partition, but it cannot read the contents of the lower partition. Parameters may be passed to the program code running in the lower partition either through the typical method of placing them on the stack or in registers before the call or by placing them in prescribed memory locations in the upper partition.

The SRL address is specified using the contents of the Flash Access Register. The 16-bit SRL address is calculated as 0xNN00, where NN is the contents of the SRL Security Register. Thus, the SRL can be located on 256-byte boundaries anywhere in program memory space. However, the 512-byte erase sector size essentially requires that a 512 boundary be used. The contents of a non-initialized SRL security byte is 0x00, thereby setting the SRL address to 0x0000 and allowing read access to all locations in program memory space by default.

# SFR Definition 10.1. PSCTL: Program Store RW Control

|   | R/W  | Reset Value  |

|---|------|------|------|------|------|------|------|------|--------------|

|   | -    | -    | -    | -    | -    | -    | PSEE | PSWE | 00000000     |

|   | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

| ١ |      |      |      |      |      |      |      |      | 0x8F         |

Bits7–2: UNUSED. Read = 000000b, Write = don't care.

Bit1: PSEE: Program Store Erase Enable.

Setting this bit allows an entire page of the Flash program memory to be erased (provided the PSWE bit is set to '1'). After setting this bit, a write to Flash memory using the MOVX instruction will erase the entire page that contains the location addressed by the MOVX instruction. The value of the data byte written does not matter.

0: Flash program memory erasure disabled.

1: Flash program memory erasure enabled.

Bit0: PSWE: Program Store Write Enable.

Setting this bit allows writing a byte of data to the Flash program memory using the MOVX instruction. The location must be erased before writing data.

0: Write to Flash program memory disabled.

1: Write to Flash program memory enabled.

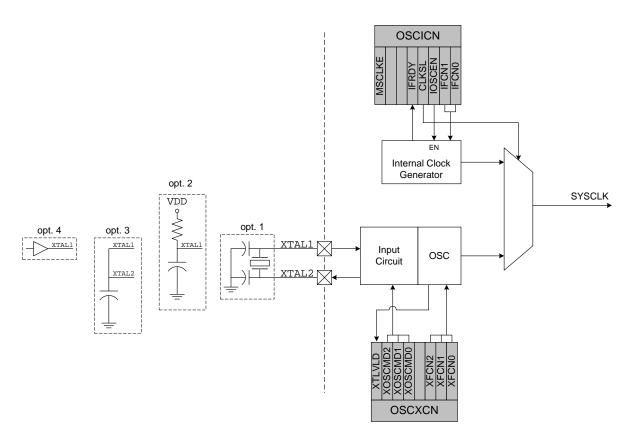

#### 13. Oscillator

The MCU includes an internal oscillator and an external oscillator drive circuit, either of which can generate the system clock. The MCU boots from the internal oscillator after any reset. This internal oscillator can be enabled/disabled and its frequency can be set using the Internal Oscillator Control Register (OSCICN) as shown in SFR Definition 13.1. The internal oscillator's electrical specifications are given in Table 13.1.

Both oscillators are disabled when the  $\overline{RST}$  pin is held low. The MCU can run from the internal oscillator permanently, or it can switch to the external oscillator if desired using CLKSL bit in the OSCICN Register. The external oscillator requires an external resonator, crystal, capacitor, or RC network connected to the XTAL1/XTAL2 pins (see Figure 13.1). The oscillator circuit must be configured for one of these sources in the OSCXCN register. An external CMOS clock can also provide the system clock by driving the XTAL1 pin. The XTAL1 and XTAL2 pins are NOT 5 V tolerant.

Figure 13.1. Oscillator Diagram

# 14. Port Input/Output

#### Description

The C8051F221/231 have three I/O Ports: Port0, Port1, and Port2. The C8051F206, C8051F220/6 and C8051F230/6 have four I/O Ports: Port0, Port1, Port2, and Port3. A wide array of digital resources can be assigned to these ports by the simple configuration of the port's corresponding multiplexer (MUX). Please see Figure 8.1. Additionally, all external port pins are available as analog input.

#### 14.1. Port I/O Initialization

Port I/O initialization is straightforward. Registers PRT0MX, PRT1MX and PRT2MX must be loaded with the appropriate values to select the digital I/O functions required by the design. The output driver characteristics of the I/O pins are defined using the Port Configuration Registers PRT0CF, PRT1CF, PRT2CF and PRT3CF. Each Port Output driver can be configured as either Open Drain or Push-Pull. This is required even for the digital resources selected in the PRTnMX registers, and is not automatic.

Any or all pins may be configured as digital I/O or as analog input. The default mode is digital I/O. The P0MODE, P1MODE, P2MODE, and P3MODE special function registers are used to configure the port pins as digital or analog as defined in this section.

The final step is initializing the individual resources selected using the appropriate setup registers. Initialization procedures for the various digital resources may be found in the detailed explanation of each available function. The reset state of each register is shown in the figures that describe each individual register.

NOTE: The input mode of pins configured for use with Timer 0, 1, or 2 must be manually configured.

- 1. The output mode of all ports pins must be configured regardless of whether the port pin is either standard general-purpose I/O or controlled by a digital peripheral.

- 2. For all pins used as Timer inputs (P0.4/T0, P0.5/T1, P0.6/T2, and P0.7/T2EX), the output mode must be "open-drain" (which is the reset state), and "1" must be written to the associated port pin to prevent possible contention for the port pin that could result in an overcurrent condition. For example, to configure a Timer0, set PRT0MX's T0E Timer0 enable bit to '1' to route Timer0 to Port Pin P0.4. Then place P0.4/T0 in open-drain configuration (which is set in PRT0CF by default), and write a '1' to P0.4 to set its output state to high impedance for use as a digital peripheral input (port pins also default to logic high state upon reset). Lastly, ensure P0MODE.4 is '1' for digital input mode. (All pins default to digital input mode upon reset.)

## SFR Definition 14.9. P1MODE: Port1 Digital/Analog Input Mode

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 11111111     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0xF2         |

Bits7-0: Port1 Digital/Analog Output Mode

0: Corresponding Port1 pin Digital Input disabled. (For analog use, i.e., ADC or comparators).

1: Corresponding Port1 pin Digital Input is enabled.

# SFR Definition 14.10. P2: Port2 Register

| R/W              | Reset Value  |

|------|------|------|------|------|------|------|------------------|--------------|

| P2.7 | P2.6 | P2.5 | P2.4 | P2.3 | P2.2 | P2.1 | P2.0             | 11111111     |

| Bit7 | Bit6 | Bit  | Bit4 | Bit3 | Bit2 | Bit1 | Bit0             | SFR Address: |

|      |      |      |      |      |      |      | (bit addressable | e) 0xA0      |

Bits7-0: P2.[7:0]

(Write - Output appears on I/O pins per PRT0MX, PRT1MX, and PRT2MX registers)

0: Logic Low Output.

1: Logic High Output (high impedance if corresponding PRT2CF.n bit = 0) (Read - Regardless of PRT0MX, PRT1MX, and PRT2MX Register settings).

0: P2.n is logic low.1: P2.n is logic high.

# SFR Definition 14.11. PRT2CF: Port2 Configuration Register

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0xA6         |

Bits7-0: PRT2CF.[7:0]: Output Configuration Bits for P2.7-P2.0 (respectively)

0: Corresponding P2.n Output Mode is Open-Drain.

1: Corresponding P2.n Output Mode is Push-Pull.

# SFR Definition 17.4. TL0: Timer 0 Low Byte

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0x8A         |

Bits 7-0: TL0: Timer 0 Low Byte.

The TL0 register is the low byte of the 16-bit Timer 0.

# SFR Definition 17.5. TL1: Timer 1 Low Byte

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0x8B         |

Bits 7-0: TL1: Timer 1 Low Byte.

The TL1 register is the low byte of the 16-bit Timer 1.

# SFR Definition 17.6. TH0: Timer 0 High Byte

| R/W  | Reset Value          |

|------|------|------|------|------|------|------|------|----------------------|

|      |      |      |      |      |      |      |      | 00000000             |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0x8C |

Bits 7-0: TH0: Timer 0 High Byte.

The TH0 register is the high byte of the 16-bit Timer 0.

# SFR Definition 17.7. TH1: Timer 1 High Byte

| R/W  | Reset Value  |

|------|------|------|------|------|------|------|------|--------------|

|      |      |      |      |      |      |      |      | 00000000     |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address: |

|      |      |      |      |      |      |      |      | 0x8D         |

Bits 7-0: TH1: Timer 1 High Byte.

The TH1 register is the high byte of the 16-bit Timer 1.

SILICON LABS

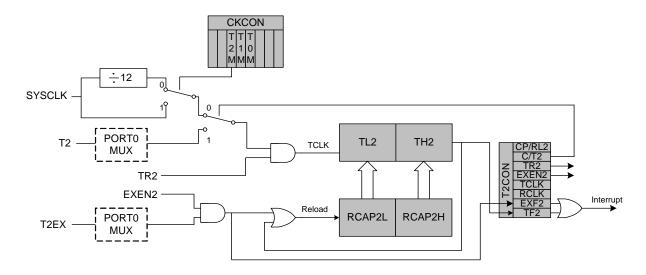

#### 17.2.2. Mode 1: 16-bit Counter/Timer with Auto-Reload

The Counter/Timer with Auto-Reload mode sets the TF2 timer overflow flag when the counter/timer register overflows from 0xFFFF to 0x0000. An interrupt is generated if enabled. On overflow, the 16-bit value held in the two capture registers (RCAP2H, RCAP2L) is automatically loaded into the counter/timer register and the timer is restarted.

Counter/Timer with Auto-Reload mode is selected by clearing the CP/RL2 bit. Setting TR2 to logic 1 enables and starts the timer. Timer 2 can use either the system clock or transitions on an external input pin as its clock source, as specified by the C/T2 bit. If EXEN2 is set to logic 1, a high-to-low transition on T2EX will also cause Timer 2 to be reloaded. If EXEN2 is cleared, transitions on T2EX will be ignored.

Figure 17.5. T2 Mode 1 Block Diagram

#### **18. JTAG**

#### Description

The MCU has an on-chip JTAG interface and logic to support Flash read and write operations and non-intrusive in-circuit debug. The C8051F2xx may be placed in a JTAG test chain in order to maintain only one JTAG interface in a system for boundary scan of other parts, and still utilize the C8051F2xx debug and Flash programming. However, the C8051F2xx does NOT support boundary scan and will act as BYPASS as specified in IEEE 1149.1.

The JTAG interface is implemented via four dedicated pins on the MCU, which are TCK, TMS, TDI, and TDO. These pins are all 5 volt tolerant.

Through the 16-bit JTAG Instruction Register (IR), five instructions shown in JTAG Register Definition 18.1 can be commanded. These commands can either select the device ID code, or select registers for Flash programming operations. BYPASS is shown to illustrate its default setting. There are four Data Registers associated with the Flash read and write operations on the MCU.

#### JTAG Register Definition 18.1. IR: JTAG Instruction

|     |          |      |         |      |  |   |      |    |        |      |  |      | Reset Value |

|-----|----------|------|---------|------|--|---|------|----|--------|------|--|------|-------------|

|     |          |      |         |      |  |   |      | Į. |        |      |  |      | 0x0000      |

| -   | Bit15    | ,    | ,       | ,    |  | , |      |    |        |      |  | Bit0 | 1           |

|     |          |      |         |      |  |   |      |    |        |      |  |      |             |

|     |          |      |         |      |  |   |      |    |        |      |  |      |             |

| l f | ID value |      | <u></u> | 4ion |  |   | <br> |    | oorin: | lion |  |      |             |

|     | IR value | l in | struct  | tion |  |   |      | De | scrip  | tion |  |      |             |

| IR value | Instruction   | Description                                                                                                                                                                                                               |

|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0004   | IDCODE        | Selects device ID Register                                                                                                                                                                                                |

| 0xFFFF   | BYPASS        | Selects bypass Data Register and is DEFAULT for the device. Note: The device does NOT support boundary scan. However, it may be placed in a scan chain and bypassed in a system of other devices utilizing boundary scan. |

| 0x0082   | Flash Control | Selects FLASHCON Register to control how the interface logic responds to reads and writes to the FLASHDAT Register                                                                                                        |

| 0x0083   | Flash Data    | Selects FLASHDAT Register for reads and writes to the Flash memory                                                                                                                                                        |

| 0x0084   | Flash Address | Selects FLASHADR Register which holds the address of all Flash read, write, and erase operations                                                                                                                          |

| 0x0085   | Flash Scale   | Selects FLASHSCL Register which controls the prescaler used to generate timing signals for Flash operations                                                                                                               |