#### Silicon Labs - C8051F236 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                    |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | 8051                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 25MHz                                                       |

| Connectivity               | SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                            |

| Number of I/O              | 32                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 1.25К х 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                 |

| Data Converters            | <u>.</u>                                                    |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                           |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 48-TQFP                                                     |

| Supplier Device Package    | 48-TQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f236 |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1. | System Overview                            | 11 |

|----|--------------------------------------------|----|

|    | 1.1. CIP-51TM Microcontroller Core         | 15 |

|    | 1.1.1. Fully 8051 Compatible               | 15 |

|    | 1.1.2. Improved Throughput                 | 15 |

|    | 1.1.3. Additional Features                 |    |

|    | 1.2. On-Board Memory                       | 17 |

|    | 1.3. JTAG                                  | 18 |

|    | 1.4. Digital/Analog Configurable I/O       | 19 |

|    | 1.5. Serial Ports                          | 20 |

|    | 1.6. Analog to Digital Converter           | 20 |

|    | 1.7. Comparators                           |    |

| 2. | Absolute Maximum Ratings                   | 23 |

| 3. | Global DC Electrical Characteristics       | 24 |

| 4. | Pinout and Package Definitions             | 25 |

| 5. | ADC (8-Bit, C8051F220/1/6 Only)            | 32 |

|    | 5.1. Analog Multiplexer and PGA            | 32 |

|    | 5.2. ADC Modes of Operation                |    |

|    | 5.3. ADC Programmable Window Detector      |    |

| 6. | ADC (12-Bit, C8051F206 Only)               |    |

|    | 6.1. Analog Multiplexer and PGA            |    |

|    | 6.2. ADC Modes of Operation                | 41 |

|    | 6.3. ADC Programmable Window Detector      | 46 |

| 7. | Voltage Reference (C8051F206/220/221/226)  |    |

| 8. |                                            |    |

| 9. | CIP-51 Microcontroller                     |    |

|    | 9.1. Instruction Set                       |    |

|    | 9.1.1. Instruction and CPU Timing          |    |

|    | 9.1.2. MOVX Instruction and Program Memory |    |

|    | 9.2. Memory Organization                   |    |

|    | 9.2.1. Program Memory                      |    |

|    | 9.2.2. Data Memory                         |    |

|    | 9.2.3. General Purpose Registers           |    |

|    | 9.2.4. Bit Addressable Locations           |    |

|    | 9.2.5. Stack                               |    |

|    | 9.3. Special Function Registers            |    |

|    | 9.3.1. Register Descriptions               |    |

|    | 9.4. Interrupt Handler                     |    |

|    | 9.4.1. MCU Interrupt Sources and Vectors   |    |

|    | 9.4.2. External Interrupts                 |    |

|    | 9.4.3. Software Controlled Interrupts      |    |

|    | 9.4.4. Interrupt Priorities                |    |

|    | 9.4.5. Interrupt Latency                   |    |

|    | 9.4.6. Interrupt Register Descriptions     | 17 |

# C8051F2xx

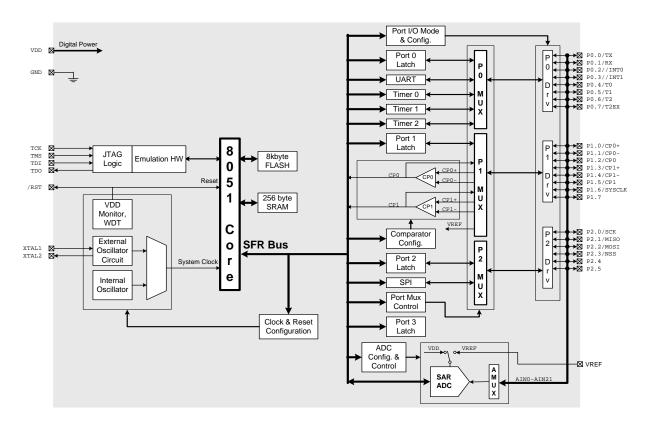

Figure 1.2. C8051F221 Block Diagram (32 LQFP)

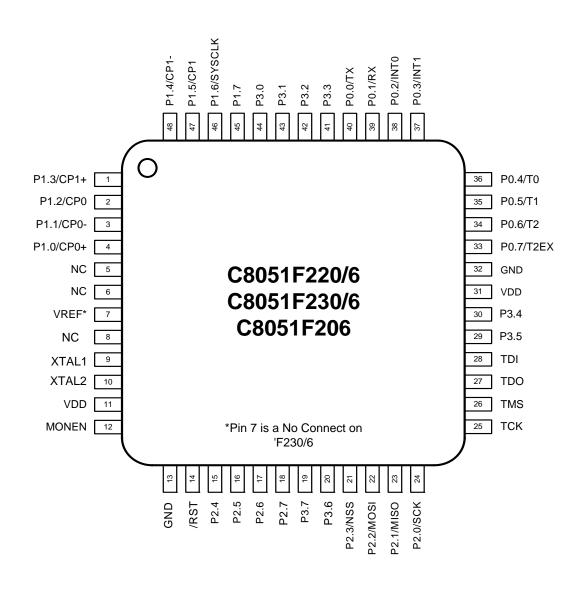

Figure 4.1. TQFP-48 Pin Diagram

| R/W      | R/W                                         | R/W       | R/W          | R/W         | R/W         | R/W         | R/W    | Reset Value  |  |  |  |

|----------|---------------------------------------------|-----------|--------------|-------------|-------------|-------------|--------|--------------|--|--|--|

| ADCSC2   |                                             | ADCSC0    | -            | -           | AMPGN2      |             | AMPGN0 | 01100000     |  |  |  |

| Bit7     | Bit6                                        | Bit5      | Bit4         | Bit3        | Bit2        | Bit1        | Bit0   | SFR Address: |  |  |  |

| Biti     | Bito                                        | Dito      | DRH          | Dito        | DILL        | Bitt        | Bito   | 0xBC         |  |  |  |

|          |                                             |           |              |             |             |             |        |              |  |  |  |

| Bits7-5: | ADCSC2-0                                    | : ADC SAR | Conversior   | n Clock Per | iod Bits    |             |        |              |  |  |  |

|          | 000: SAR Conversion Clock = 1 System Clock  |           |              |             |             |             |        |              |  |  |  |

|          | 001: SAR Conversion Clock = 2 System Clocks |           |              |             |             |             |        |              |  |  |  |

|          | 010: SAR (                                  |           |              |             |             |             |        |              |  |  |  |

|          | 011: SAR (                                  |           |              |             |             |             |        |              |  |  |  |

|          | 1xx: SAR C                                  |           |              | •           |             |             |        |              |  |  |  |

|          | NOTE: SA                                    |           |              |             | than or equ | al to 2MHz. |        |              |  |  |  |

|          | UNUSED.                                     |           |              |             |             |             |        |              |  |  |  |

| Bits2–0: | AMPGN2-0                                    |           | nal Amplifie | er Gain     |             |             |        |              |  |  |  |

|          | 000: Gain :                                 |           |              |             |             |             |        |              |  |  |  |

|          | 001: Gain :                                 | _         |              |             |             |             |        |              |  |  |  |

|          | 010: Gain :                                 |           |              |             |             |             |        |              |  |  |  |

|          | 011: Gain =                                 |           |              |             |             |             |        |              |  |  |  |

|          | 10x: Gain =                                 |           |              |             |             |             |        |              |  |  |  |

|          | 11x: Gain =                                 | = 0.5     |              |             |             |             |        |              |  |  |  |

|          |                                             |           |              |             |             |             |        |              |  |  |  |

|          |                                             |           |              |             |             |             |        |              |  |  |  |

|          |                                             |           |              |             |             |             |        |              |  |  |  |

### SFR Definition 5.2. ADC0CF: ADC Configuration Register

### Table 5.1. 8-Bit ADC Electrical Characteristics

VDD = 3.0 V, VREF = 2.40 V, PGA Gain = 1, -40 to +85 ×C unless otherwise specified.

| Parameter                        | Conditions                         | Min       | Тур     | Max      | Units  |  |  |  |  |

|----------------------------------|------------------------------------|-----------|---------|----------|--------|--|--|--|--|

| DC Accuracy                      |                                    | •         |         |          | •      |  |  |  |  |

| Resolution                       |                                    |           | 8       | —        | bits   |  |  |  |  |

| Integral Nonlinearity            |                                    |           | —       | ±1/2     | LSB    |  |  |  |  |

| Differential Nonlinearity        | Guaranteed Monotonic               | _         | —       | ±1/2     | LSB    |  |  |  |  |

| Offset Error                     |                                    | ±2        | —       | ±1/2     | LSB    |  |  |  |  |

| Gain Error                       |                                    | ±2        | —       | ±1/2     | LSB    |  |  |  |  |

| Offset Temperature Coefficient   |                                    |           | ±0.25   | _        | ppm/°C |  |  |  |  |

| Dynamic Performance (10 kHz sine | wave input, 0 to –1 dB of full     | scale, 10 | 0 ksps) |          |        |  |  |  |  |

| Signal-to-Noise Plus Distortion  |                                    | 49.5      | —       | _        | dB     |  |  |  |  |

| Total Harmonic Distortion        | Up to the 5 <sup>th</sup> harmonic | -60       | -65     | _        | dB     |  |  |  |  |

| Spurious-Free Dynamic Range      |                                    |           | -65     | _        | dB     |  |  |  |  |

| Conversion Rate                  |                                    | •         |         |          | •      |  |  |  |  |

| Conversion Time in SAR Clocks    |                                    | 16        | —       | —        | clocks |  |  |  |  |

| SAR Clock Frequency              |                                    |           | —       | 2.5      | MHz    |  |  |  |  |

| Track/Hold Acquisition Time      |                                    | 1.5       | —       | _        | μs     |  |  |  |  |

| Throughput Rate                  |                                    | _         | —       | 100      | ksps   |  |  |  |  |

| Analog Inputs                    | ·                                  |           |         |          |        |  |  |  |  |

| Input Voltage Range              |                                    | 0         | —       | $V_{DD}$ | V      |  |  |  |  |

| Input Capacitance                |                                    |           | 10      | _        | pF     |  |  |  |  |

| Power Specifications             |                                    |           |         |          |        |  |  |  |  |

| Power Supply Current             | Operating Mode, 100 ksps           |           | 0.45    | 1.0      | mA     |  |  |  |  |

| Power Supply Current in Shutdown |                                    |           | 0.1     | 1        | μA     |  |  |  |  |

| Power Supply Rejection           |                                    |           | ±0.3    |          | mV/V   |  |  |  |  |

| R/W     | R/W                                                              | R/W                                                                               | R/W                                                                                     | R/W                                                                                   | R/W                         | R/W         | R/W    | Reset Value  |

|---------|------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------|-------------|--------|--------------|

| ADCSC2  | ADCSC1                                                           | ADCSC0                                                                            | -                                                                                       | -                                                                                     | AMPGN2                      | AMPGN1      | AMPGN0 | 01100000     |

| Bit7    | Bit6                                                             | Bit5                                                                              | Bit4                                                                                    | Bit3                                                                                  | Bit2                        | Bit1        | Bit0   | SFR Address: |

|         |                                                                  |                                                                                   |                                                                                         |                                                                                       |                             |             |        | 0xBC         |

|         | 001: SAR (<br>010: SAR (<br>011: SAR (<br>1xx: SAR (<br>NOTE: SA | Conversion<br>Conversion<br>Conversion<br>Conversion<br>Conversion<br>R conversio | Clock = 1 S<br>Clock = 2 S<br>Clock = 4 S<br>Clock = 8 S<br>Clock = 16 S<br>n clock sho | system Cloc<br>system Cloc<br>system Cloc<br>system Cloc<br>Systems Cl<br>uld be less | k<br>ks<br>ks<br>ks<br>ocks | al to 2MHz. |        |              |

|         | UNUSED.<br>AMPGN2–(                                              |                                                                                   | ,                                                                                       |                                                                                       |                             |             |        |              |

| DIG2 0. | 000: Gain :                                                      |                                                                                   | nui / inpine                                                                            |                                                                                       |                             |             |        |              |

|         | 001: Gain :                                                      |                                                                                   |                                                                                         |                                                                                       |                             |             |        |              |

|         | 010: Gain :                                                      | -                                                                                 |                                                                                         |                                                                                       |                             |             |        |              |

|         | 011: Gain = 10x: Gain =                                          |                                                                                   |                                                                                         |                                                                                       |                             |             |        |              |

|         | 1x: Gain =                                                       | -                                                                                 |                                                                                         |                                                                                       |                             |             |        |              |

|         |                                                                  |                                                                                   |                                                                                         |                                                                                       |                             |             |        |              |

# SFR Definition 6.2. ADC0CF: ADC Configuration ('F220/1/6 and 'F206)

### **Table 7.1. Reference Electrical Characteristics**

$V_{DD}$  = 3.0 V, Temperature –40 to +85 ×C

| External Reference ([REFS | 6L1: REFSL0] = 00), V <sub>REF</sub> = 2.4 V) | Min  | Тур | Max                        | Units |

|---------------------------|-----------------------------------------------|------|-----|----------------------------|-------|

| Input Voltage Range       |                                               | 1.00 |     | (V <sub>DD</sub> ) – 0.3 V | V     |

| Input Current             |                                               | _    | 0.1 | 10                         | μA    |

| Input Resistance          |                                               | 100  |     | —                          | MΩ    |

| R/W     | R                       | R/W          | R/W        | R/W          | R/W            | R/W            | R/W         | Reset Value  |

|---------|-------------------------|--------------|------------|--------------|----------------|----------------|-------------|--------------|

| CP1EN   | CP10UT                  | CP1RIF       | CP1FIF     | CP1HYP1      | CP1HYP0        | CP1HYN1        | CP1HYNC     | 00000000     |

| Bit7    | Bit6                    | Bit5         | Bit4       | Bit3         | Bit2           | Bit1           | Bit0        | SFR Address: |

|         |                         |              |            |              |                |                |             | 0x9F         |

|         | 00/51/0                 |              |            |              |                |                |             |              |

| Bit7:   | CP1EN: Co               | •            |            |              |                |                |             |              |

|         | 0: Compara              |              |            |              |                |                |             |              |

| Dito    | 1: Compara              |              |            | lata Elan    |                |                |             |              |

| Bit6:   | CP1OUT: C<br>0: Voltage | •            | •          | late Flag    |                |                |             |              |

|         | 1: Voltage              |              |            |              |                |                |             |              |

| Bit5:   | CP1RIF: Co              |              |            | ae Interrunt | Flag           |                |             |              |

| Dito.   |                         |              |            |              | s occurred s   | ince this fla  | n was clea  | ared         |

|         |                         |              |            |              | ccurred since  |                |             |              |

| Bit4:   | CP1FIF: Co              |              |            |              |                | o ano nag n    |             | •            |

|         |                         |              | •          | • •          | is occurred s  | since this fla | ad was clea | ared         |

|         |                         |              |            |              | ccurred sinc   |                |             |              |

| Bit3-2: |                         |              | • •        |              | sis Control B  | •              |             |              |

|         | 00: Positive            | e Hysteresis | s Disabled | -            |                |                |             |              |

|         | 01: Positive            | e Hysteresis | s = 2 mV   |              |                |                |             |              |

|         | 10: Positive            | e Hysteresis | s = 4 mV   |              |                |                |             |              |

|         | 11: Positive            | e Hysteresis | s = 10 mV  |              |                |                |             |              |

| Bit1-0: |                         |              | •          |              | esis Control I | Bits           |             |              |

|         | 00: Negativ             |              |            |              |                |                |             |              |

|         | 01: Negativ             |              |            |              |                |                |             |              |

|         | 10: Negativ             |              |            |              |                |                |             |              |

|         | 11: Negativ             | e Hysteres   | is = 10 mV |              |                |                |             |              |

|         |                         |              |            |              |                |                |             |              |

### SFR Definition 8.2. CPT1CN: Comparator 1 Control

#### Notes on Registers, Operands and Addressing Modes:

Rn - Register R0-R7 of the currently selected register bank.

@Ri - Data RAM location addressed indirectly through register R0–R1

**rel -** 8-bit, signed (two's compliment) offset relative to the first byte of the following instruction. Used by SJMP and all conditional jumps.

**direct** - 8-bit internal data location's address. This could be a direct-access Data RAM location (0x00– 0x7F) or an SFR (0x80–0xFF).

#data - 8-bit constant

#data 16 - 16-bit constant

bit - Direct-addressed bit in Data RAM or SFR.

**addr 11 -** 11-bit destination address used by ACALL and AJMP. The destination must be within the same 2 kB page of program memory as the first byte of the following instruction.

**addr 16 -** 16-bit destination address used by LCALL and LJMP. The destination may be anywhere within the 8 kB program memory space.

There is one unused opcode (0xA5) that performs the same function as NOP. All mnemonics copyrighted © Intel Corporation 1980.

| R/W   | R/W                                                                                                                                                                                                                                                                                                   | R/W                                                                                                                                                                                                                                                                                             | R/W          | R/W                        | R/W          | R/W                 | R/W         | Reset Value          |  |  |  |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------|--------------|---------------------|-------------|----------------------|--|--|--|

| EXVLD | -                                                                                                                                                                                                                                                                                                     | ESCI3                                                                                                                                                                                                                                                                                           | ESCI2        | ESCI1                      | ESCI0        | EADC0               | -           | 00000000             |  |  |  |

| Bit7  | Bit6                                                                                                                                                                                                                                                                                                  | Bit5                                                                                                                                                                                                                                                                                            | Bit4         | Bit3                       | Bit2         | Bit1                | Bit0        | SFR Address:<br>0xE7 |  |  |  |

| Bit7: | <ul><li>This bit sets the masking of the XTLVLD interrupt.</li><li>0: Disable all XTLVLD interrupts.</li><li>1: Enable interrupt requests generated by the XTLVLD flag (OSCXCN.7)</li></ul>                                                                                                           |                                                                                                                                                                                                                                                                                                 |              |                            |              |                     |             |                      |  |  |  |

| Bit6: | Reserved. Must write 0. Reads 0.                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                 |              |                            |              |                     |             |                      |  |  |  |

| Bit5: | <ul> <li>Bit5: ESCI3: Enable Software Controlled Interrupt 3.</li> <li>This bit sets the masking of Software Controlled Interrupt 3.</li> <li>0: Disable Software Controlled Interrupt 3.</li> <li>1: Enable interrupt requests generated setting the Software Controlled Interrupt Bit 3.</li> </ul> |                                                                                                                                                                                                                                                                                                 |              |                            |              |                     |             |                      |  |  |  |

| Bit4: | ESCI2: Enable Software Controlled Interrupt 2.<br>This bit sets the masking of Software Controlled Interrupt 2.<br>0: Disable Software Controlled Interrupt 2.<br>1: Enable interrupt requests generated setting the Software Controlled Interrupt Bit 2.                                             |                                                                                                                                                                                                                                                                                                 |              |                            |              |                     |             |                      |  |  |  |

| Bit3: | This bit set<br>0: Disable                                                                                                                                                                                                                                                                            | able Softwar<br>s the maskir<br>Software Co<br>interrupt req                                                                                                                                                                                                                                    | ng of Softwa | are Controll<br>terrupt 1. | ed Interrupt | 1.<br>are Controlle | ed Interrup | ot Bit 1.            |  |  |  |

| Bit2: | This bit set<br>0: Disable                                                                                                                                                                                                                                                                            | <ul> <li>ESCI0: Enable Software Controlled Interrupt 0.</li> <li>This bit sets the masking of Software Controlled Interrupt 0.</li> <li>0: Disable Software Controlled Interrupt 0.</li> <li>1: Enable interrupt requests generated setting the Software Controlled Interrupt Bit 0.</li> </ul> |              |                            |              |                     |             |                      |  |  |  |

| Bit1: | This bit set<br>0: Disable                                                                                                                                                                                                                                                                            | <ul><li>EADC0: Enable ADC0 End of Conversion Interrupt.</li><li>This bit sets the masking of the ADC0 End of Conversion Interrupt.</li><li>0: Disable ADC0 Conversion Interrupt.</li><li>1: Enable interrupt requests generated by the ADC0 Conversion Interrupt.</li></ul>                     |              |                            |              |                     |             |                      |  |  |  |

| Bit0: | Reserved.                                                                                                                                                                                                                                                                                             | Read = 0, \                                                                                                                                                                                                                                                                                     | Vrite = don' | t care.                    |              |                     |             |                      |  |  |  |

### SFR Definition 9.11. EIE2: Extended Interrupt Enable 2

### 10. Flash Memory

This MCU includes 8 k + 128 bytes of on-chip, re-programmable Flash memory for program code and nonvolatile data storage. The Flash memory can be programmed in-system, a single byte at a time, through the JTAG interface or by software using the MOVX instruction. Once cleared to 0, a Flash bit must be erased to set it back to 1. The bytes would typically be erased (set to 0xFF) before being reprogrammed. The write and erase operations are automatically timed by hardware for proper execution. Data polling to determine the end of the write/erase operation is not required. The Flash memory is designed to withstand at least 20,000 write/erase cycles. Refer to Table 10.1 for the electrical characteristics of the Flash memory.

#### **10.1.** Programming The Flash Memory

The simplest means of programming the Flash memory is through the JTAG interface using programming tools provided by Silicon Labs or a third party vendor. This is the only means for programming a non-initialized device. For details on the JTAG commands to program Flash memory, see Section 18.1.

The Flash memory can be programmed by software using the MOVX instruction with the address and data byte to be programmed provided as normal operands. Before writing to Flash memory using MOVX, flash write operations must be enabled by setting the PSWE Program Store Write Enable bit (PSCTL.0) to logic 1. Writing to Flash remains enabled until the PSWE bit is cleared by software.

To ensure the contents of the Flash contents, it is strongly recommended that the on-chip  $V_{DD}$  monitor be enabled (by tieing the MONEN pin 'high') in any application that writes and/or erases Flash memory from software.

Writes to Flash memory can clear bits but cannot set them. Only an erase operation can set bits in Flash. The byte location to be programmed must be erased before a new value can be written. The 8kbyte Flash memory is organized in 512-byte sectors. The erase operation applies to an entire sector (setting all bytes in the sector to 0xFF). Setting the PSEE Program Store Erase Enable bit (PSCTL.1) and PSWE Program Store Write Enable bit (PSCTL.0) to logic 1 and then using the MOVX command to write a data byte to any byte location within the sector will erase an entire 512-byte sector. The data byte written can be of any value because it is not actually written to the Flash. Flash erasure remains enabled until the PSEE bit is cleared by software. The following sequence illustrates the algorithm for programming the Flash memory by software:

- 1. Disable interrupts.

- 2. Enable Flash Memory write/erase in FLSCL Register using FLASCL bits.

- 3. Set PSEE (PSCTL.1) to enable Flash sector erase.

- 4. Set PSWE (PSCTL.0) to enable Flash writes.

- 5. Use MOVX to write a data byte to any location within the 512-byte sector to be erased.

- 6. Clear PSEE to disable Flash sector erase.

- Use MOVX to write a data byte to the desired byte location within the erased 512-byte sector. Repeat until finished. (Any number of bytes can be written from a single byte to and entire sector.)

- 8. Clear the PSWE bit to disable Flash writes.

Write/Erase timing is automatically controlled by hardware based on the prescaler value held in the Flash Memory Timing Prescaler register (FLSCL). The 4-bit prescaler value FLASCL determines the time interval for write/erase operations. The FLASCL value required for a given system clock is shown in SFR Definition 10.2, along with the formula used to derive the FLASCL values. When FLASCL is set to 1111b, the

### 11. On-Chip XRAM (C8051F206/226/236)

The C8051F206/226/236 features 1024 Bytes of RAM mapped into the external data memory space. All address locations may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using indirect MOVX addressing mode. If the MOVX instruction is used with an 8-bit operand (such as @R1), then the high byte is the External Memory Interface Control Register (EMI0CN, shown in SFR Definition 11.1). Addressing using 8 bits will map to one of four 256-byte pages, and these pages are selected by setting the PGSEL bits in the EMI0CN register.

NOTE: The MOVX instruction is also used for write to the Flash memory. Please see section 10 for details. The MOVX instruction will access XRAM by default.

For any of the addressing modes, the upper 6 bits of the 16-bit external data memory address word are "don't cares". As a result, the 1024-byte RAM is mapped modulo style ("wrap around") over the entire 64k of possible address values. For example, the XRAM byte at address 0x0000 is also at address 0x0400, 0x0800, 0x0C00, 0x1000, etc. This feature is useful when doing a linear memory fill, as the address pointer does not have to be reset when reaching the RAM block boundary.

#### SFR Definition 11.1. EMI0CN: External Memory Interface Control

| R                                                                                                                                                | R    | R    | R    | R    | R    | R/W    | R/W    | Reset Value  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|--------|--------|--------------|--|

| -                                                                                                                                                | -    | -    | -    | -    | -    | PGSEL1 | PGSEL0 | 00000000     |  |

| Bit7                                                                                                                                             | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1   | Bit0   | SFR Address: |  |

|                                                                                                                                                  |      |      |      |      |      |        |        | 0xAF         |  |

| -     -     -     -     PGSEL1     PGSEL0     0000000       Bit7     Bit6     Bit5     Bit4     Bit3     Bit2     Bit1     Bit0     SFR Address: |      |      |      |      |      |        |        |              |  |

| SFR Definition 13.2 | . OSCXCN: External | <b>Oscillator Control</b> |

|---------------------|--------------------|---------------------------|

|---------------------|--------------------|---------------------------|

| R                 | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W                                                         | R/W                        | R/W          | R/W                      | R/W      | R/W            | Reset Value  |  |  |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------|--------------|--------------------------|----------|----------------|--------------|--|--|--|

| XTLVLD            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |                            |              | XFCN2                    | XFCN1    | XFCN0          | 00110000     |  |  |  |

| Bit7              | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                             | Bit4                       | Bit3         | Bit2                     | Bit1     | Bit0           | SFR Address: |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |                            |              |                          |          |                | 0xB1         |  |  |  |

| Bit7:             | (Valid o<br>0: Crys                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0: Crystal Oscilla<br>nly when XOSCI<br>tal Oscillator is u | MD = 1xx.)<br>inused or no | ot yet stabl | 9                        |          |                |              |  |  |  |

| Bits6–4:          | <ol> <li>Crystal Oscillator is running and stable</li> <li>Bits6–4: XOSCMD2–0: External Oscillator Mode Bits</li> <li>00x: Off. XTAL1 pin is grounded internally.</li> <li>010: System Clock from External CMOS Clock on XTAL1 pin.</li> <li>011: System Clock from External CMOS Clock on XTAL1 pin divided by 2.</li> <li>10x: RC/C Oscillator Mode with divide by 2 stage.</li> <li>110: Crystal Oscillator Mode</li> <li>111: Crystal Oscillator Mode with divide by 2 stage.</li> </ol> |                                                             |                            |              |                          |          |                |              |  |  |  |

| D:+0.             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | •                                                           |                            | •            | -                        |          |                |              |  |  |  |

| Bit3:<br>Bits2–0: |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | VED. Read = u<br>-0: External Osc                           |                            |              |                          |          |                |              |  |  |  |

| Dit32-0.          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1: see table belo                                           | •                          |              |                          |          |                |              |  |  |  |

|                   | XFCN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Crystal (XOSC                                               |                            | RC (XO       | SCMD = 10                | )x) C (X | OSCMD =        | 10x)         |  |  |  |

|                   | 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | f ≤ 12.5                                                    |                            | -            | 25 kHz                   |          | Factor = 0     |              |  |  |  |

|                   | 001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12.5 kHz < f ≤                                              |                            |              | < f ≤ 50 kH              |          | Factor = $1$   |              |  |  |  |

|                   | 010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30.35 kHz < f s                                             |                            | -            | $< f \le 100 \text{ kH}$ |          | K Factor = 4.4 |              |  |  |  |

|                   | 011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 93.8 kHz < f ≤                                              |                            |              | < f ≤ 200 k              |          | Factor = 1     |              |  |  |  |

|                   | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 267 kHz < f ≤                                               |                            |              | < f ≤ 400 k              |          | Factor = 3     |              |  |  |  |

|                   | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 722 kHz < f ≤                                               | 2.23 MHz                   | 400 kHz      | < f ≤ 800 k              | Hz K     | Factor = 1     | 00           |  |  |  |

|                   | 110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2.23 MHz < f ≤                                              | 6.74 MHz                   | 800 kHz      | < f ≤ 1.6 M              | Hz K     | Factor = 4     | 20           |  |  |  |

|                   | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | f > 6.74                                                    | MHz                        | 1.6 MHz      | < f ≤ 3.2 M              | Hz K     | Factor = 14    | 400          |  |  |  |

|                   | Choose                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (Circuit from Fig<br>XFCN value to<br>t from Figure 13      | match the c                | rystal frequ | iency.                   | 1x)      |                |              |  |  |  |

|                   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | oscillation frequ                                           | •                          |              | - 100                    |          |                |              |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (10 <sup>3</sup> ) / (R x C), v                             |                            | -            |                          |          |                |              |  |  |  |

|                   | f = frequ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ency of oscillati                                           | on in MHz                  |              |                          |          |                |              |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | acitor value in p                                           |                            |              |                          |          |                |              |  |  |  |

|                   | R = Pul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -up resistor valu                                           | e in k $\Omega$            |              |                          |          |                |              |  |  |  |

| C MODE            | <pre>C MODE (Circuit from Figure 13.1, Option 3; XOSCMD = 10x)<br/>Choose K Factor (KF) for the oscillation frequency desired:<br/>f = KF / (C x AV+), where<br/>f = frequency of oscillation in MHz<br/>C = capacitor value on XTAL1, XTAL2 pins in pF</pre>                                                                                                                                                                                                                                |                                                             |                            |              |                          |          |                |              |  |  |  |

|                   | $V_{DD} = F$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ower supply vol                                             | tage on MC                 | U in volts   |                          |          |                |              |  |  |  |

# SFR Definition 14.9. P1MODE: Port1 Digital/Analog Input Mode

| R/W      | R/W       | R/W                 | R/W  | R/W  | R/W  | R/W         | R/W         | Reset Value  |

|----------|-----------|---------------------|------|------|------|-------------|-------------|--------------|

|          |           |                     |      |      |      |             |             | 11111111     |

| Bit7     | Bit6      | Bit5                | Bit4 | Bit3 | Bit2 | Bit1        | Bit0        | SFR Address: |

|          |           |                     |      |      |      |             |             | 0xF2         |

| Bits7–0: | comparato | oonding Por<br>rs). | •    |      | ,    | analog use, | i.e., ADC o | Dr           |

### SFR Definition 14.10. P2: Port2 Register

| R/W      | R/W                                      | R/W                                      | R/W          | R/W         | R/W         | R/W        | R/W               | Reset Value  |  |

|----------|------------------------------------------|------------------------------------------|--------------|-------------|-------------|------------|-------------------|--------------|--|

| P2.7     | P2.6                                     | P2.5                                     | P2.4         | P2.3        | P2.2        | P2.1       | P2.0              | 11111111     |  |

| Bit7     | Bit6                                     | Bit                                      | Bit4         | Bit3        | Bit2        | Bit1       | Bit0              | SFR Address: |  |

|          |                                          |                                          |              |             |             |            | (bit addressable) | 0xA0         |  |

|          |                                          |                                          |              |             |             |            |                   |              |  |

| Bits7–0: |                                          | itout appea                              | rs on I/O pi | ns per PRT  | OMX PRT     | 1MX and F  | PRT2MX regist     | ters)        |  |

| Bits7–0: | (Write - Ou                              |                                          |              | ns per PRT  | TOMX, PRT   | 1MX, and F | PRT2MX regis      | ters)        |  |

| Bits7–0: | (Write - Ou<br>0: Logic Lo               | ow Output.                               |              | •           | ·           | ·          | C C               | ters)        |  |

| Bits7–0: | (Write - Ou<br>0: Logic Lo<br>1: Logic H | ow Output.<br>ligh Output                | (high impe   | dance if co | rresponding | g PRT2CF.  | n bit = 0)        | ters)        |  |

| Bits7–0: | (Write - Ou<br>0: Logic Lo<br>1: Logic H | ow Output.<br>ligh Output<br>egardless o |              | dance if co | rresponding | g PRT2CF.  | n bit = 0)        | ters)        |  |

# SFR Definition 14.11. PRT2CF: Port2 Configuration Register

| R/W      | R/W                                    | R/W        | R/W         | R/W         | R/W    | R/W          | R/W  | Reset Value |

|----------|----------------------------------------|------------|-------------|-------------|--------|--------------|------|-------------|

|          |                                        |            |             |             |        |              |      | 0000000     |

| Bit7     | Bit6                                   | Bit5       | Bit4        | Bit3        | Bit2   | Bit1         | Bit0 | SFR Address |

|          |                                        |            |             |             |        |              |      | 0xA6        |

| Bits7–0: | PRT2CF.[7:<br>0: Corresp<br>1: Corresp | onding P2. | n Output Mo | ode is Open | Drain. | espectively) |      |             |

# C8051F2xx

### 15.2. Operation

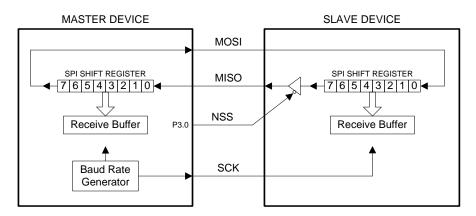

Only a SPI master device can initiate a data transfer. The SPI is placed in master mode by setting the Master Enable flag (MSTEN, SPI0CN.1). Writing a byte of data to the SPI data register (SPI0DAT) when in Master Mode starts a data transfer. The SPI master immediately shifts out the data serially on the MOSI line while providing the serial clock on SCK. The SPIF (SPI0CN.7) flag is set to logic 1 at the end of the transfer. If interrupts are enabled, an interrupt request is generated when the SPIF flag is set. The SPI master can be configured to shift in/out from one to eight bits in a transfer operation in order to accommodate slave devices with different word lengths. The SPIFRS bits in the SPI Configuration Register (SPI0CFG.[2:0]) are used to select the number of bits to shift in/out in a transfer operation.

While the SPI master transfers data to a slave on the MOSI line, the addressed SPI slave device simultaneously transfers the contents of its shift register to the SPI master on the MISO line in a full-duplex operation. The data byte received from the slave replaces the data in the master's data register. Therefore, the SPIF flag serves as both a transmit-complete and receive-data-ready flag. The data transfer in both directions is synchronized with the serial clock generated by the master. Figure 15.3 illustrates the full-duplex operation of an SPI master and an addressed slave.

Figure 15.3. Full Duplex Operation

The SPI data register is double buffered on reads, but not on a write. If a write to SPI0DAT is attempted during a data transfer, the WCOL flag (SPI0CN.6) will be set to logic 1 and the write is ignored. The current data transfer will continue uninterrupted. A read of the SPI data register by the system controller actually reads the receive buffer. If the receive buffer still holds unread data from a previous transfer when the last bit of the current transfer is shifted into the SPI shift register, a receive overrun occurs and the RXOVRN flag (SPI0CN.4) is set to logic 1. The new data is not transferred to the receive buffer, allowing the previously received data byte to be read. The data byte causing the overrun is lost.

When the SPI is enabled and not configured as a master, it will operate as an SPI slave. Another SPI device acting as a master will initiate a transfer by driving the NSS signal low. The master then shifts data out of the shift register on the MOSI pin using the its serial clock. The SPIF flag is set to logic 1 at the end of a data transfer (when the NSS signal goes high). The slave can load its shift register for the next data transfer by writing to the SPI data register. The slave must make the write to the data register at least one SPI serial clock cycle before the master starts the next transmission. Otherwise, the byte of data already in the slave's shift register will be transferred.

| SFR Definition | 15.2. | SPI0CN: | SPI | Control |

|----------------|-------|---------|-----|---------|

|----------------|-------|---------|-----|---------|

| R/W   | R/W                                                                                                                                                                                                                                                                                            | R/W           | R/W                                          | R           | R             | R/W                               | R/W         | Reset Value                                |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------------------------------|-------------|---------------|-----------------------------------|-------------|--------------------------------------------|--|--|--|--|

| SPIF  | WCOL                                                                                                                                                                                                                                                                                           | MODF          | RXOVRN                                       | TXBSY       | SLVSEL        | MSTEN                             | SPIEN       | 00000000                                   |  |  |  |  |

| Bit7  | Bit6                                                                                                                                                                                                                                                                                           | Bit5          | Bit4                                         | Bit3        | Bit2          | Bit1                              | Bit0        | SFR Address:<br>0xF8                       |  |  |  |  |

| Bit7: | 7: SPIF: SPI Interrupt Flag.<br>This bit is set to logic 1 by hardware at the end of a data transfer. If interrupts are enable setting this bit causes the CPU to vector to the SPI0 interrupt service routine. This bit is automatically cleared by hardware. It must be cleared by software. |               |                                              |             |               |                                   |             |                                            |  |  |  |  |

| Bit6: | WCOL: Write Collision Flag.<br>This bit is set to logic 1 by hardware (and generates a SPI interrupt) to indicate a write to th<br>SPI data register was attempted while a data transfer was in progress. It is cleared by sof<br>ware.                                                        |               |                                              |             |               |                                   |             |                                            |  |  |  |  |

| Bit5: | This bit is s collision is a                                                                                                                                                                                                                                                                   | detected (N   | by hardwar                                   | nd MSTEN    |               | Pl interrupt) v<br>bit is not aut |             |                                            |  |  |  |  |

| Bit4: | This bit is s<br>still holds u<br>shifted into                                                                                                                                                                                                                                                 | nread data    | by hardwar<br>from a previ<br>ft register. T | ous transfe | er and the la | st bit of the                     | current tra | eceive buffer<br>Insfer is<br>are. It must |  |  |  |  |

| Bit3: |                                                                                                                                                                                                                                                                                                | et to logic 1 | •                                            |             |               | e transfer is                     | in progres  | s. It is                                   |  |  |  |  |

| Bit2: | SLVSEL: Slave Selected Flag.<br>This bit is set to logic 1 whenever the NSS pin is low indicating it is enabled as a slave. It is<br>cleared to logic 0 when NSS is high (slave disabled).                                                                                                     |               |                                              |             |               |                                   |             |                                            |  |  |  |  |

| Bit1: | MSTEN: Master Mode Enable.<br>0: Disable master mode. Operate in slave mode.<br>1: Enable master mode. Operate as a master.                                                                                                                                                                    |               |                                              |             |               |                                   |             |                                            |  |  |  |  |

| Bit0: | SPIEN: SPI Enable.<br>This bit enables/disables the SPI.<br>0: SPI disabled.<br>1: SPI enabled.                                                                                                                                                                                                |               |                                              |             |               |                                   |             |                                            |  |  |  |  |

If T1M (CKCON.4) is logic 1, then the above equation becomes:

T1\_OVERFLOWRATE = (SYSCLK) / (256 - TH1).

If T1M (CKCON.4) is logic 0, then the above equation becomes:

$T1_OVERFLOWRATE = (SYSCLK/12) / (256 - TH1).$

The Timer 2 overflow rate, when in Baud Rate Generator Mode and using an internal clock source, is determined solely by the Timer 2 16-bit reload value (RCAP2H:RCAP2L). The Timer 2 clock source is fixed at SYSCLK/2. The Timer 2 overflow rate can be calculated as follows:

T2\_OVERFLOWRATE = (SYSCLK/2) / (65536 - [RCAP2H:RCAP2L]).

Timer 2 can be selected as the baud rate generator for RX and/or TX by setting RCLK (T2CON.5) and/or TCLK (T2CON.4), respectively. When either RCLK or TCLK is set to logic 1, Timer 2 interrupts are automatically disabled and the timer is forced into Baud Rate Generator Mode with SYSCLK/2 as its clock source. If a different timebase is required, setting the C/T2 bit (T2CON.1) to logic 1 will allow Timer 2 to be clocked from the external input pin T2. See the Timers section for complete timer configuration details.

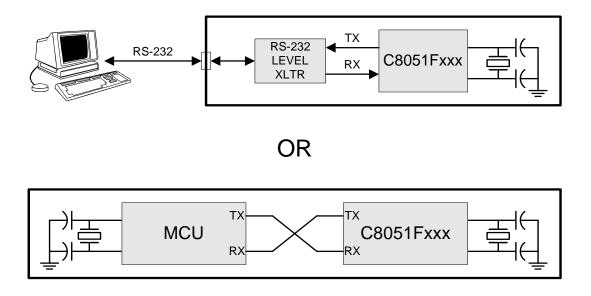

Figure 16.5. UART Modes 1, 2, and 3 Interconnect Diagram

|  | SFR | Definition | 17.2. | TMOD: | Timer Mod | le |

|--|-----|------------|-------|-------|-----------|----|

|--|-----|------------|-------|-------|-----------|----|

| R/W                                                                                                      | R/                                                                                                                                                                                             | W                                                                                                                                  | R/W                                                                                                                             | R/W                                                                                                                                                               | R/W                                                                                                                                       | R/W                                                              | R/W                                                   | R/W                  | Reset Value  |  |

|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------|----------------------|--------------|--|

| GATE                                                                                                     | 1 C/                                                                                                                                                                                           | Γ1   ٦                                                                                                                             | T1M1 T1M0                                                                                                                       |                                                                                                                                                                   | GATE0                                                                                                                                     | C/T0                                                             | T0M1                                                  | T0M0                 | 00000000     |  |

| Bit7                                                                                                     | Bit7 Bit6                                                                                                                                                                                      |                                                                                                                                    | Bit5                                                                                                                            | Bit4                                                                                                                                                              | Bit3                                                                                                                                      | Bit1                                                             | Bit0                                                  | SFR Address:<br>0x89 |              |  |

| Bit7:                                                                                                    | GATE                                                                                                                                                                                           | 1: Timer                                                                                                                           |                                                                                                                                 |                                                                                                                                                                   |                                                                                                                                           |                                                                  |                                                       |                      |              |  |

| Bitr.                                                                                                    |                                                                                                                                                                                                |                                                                                                                                    |                                                                                                                                 |                                                                                                                                                                   | irrespective                                                                                                                              | of /INT1 lo                                                      | gic level.                                            |                      |              |  |