Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | M8C                                                                        |

| Core Size                  | 8-Bit                                                                      |

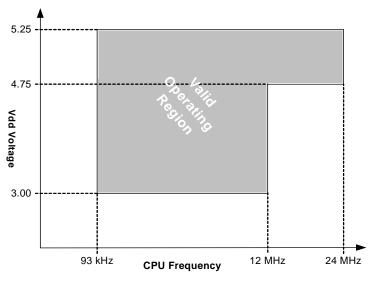

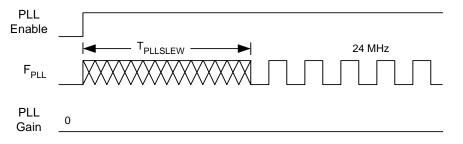

| Speed                      | 24MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 16                                                                         |

| Program Memory Size        | 16KB (16K × 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                |                                                                            |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                 |

| Data Converters            | A/D 4x14b; D/A 4x9b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

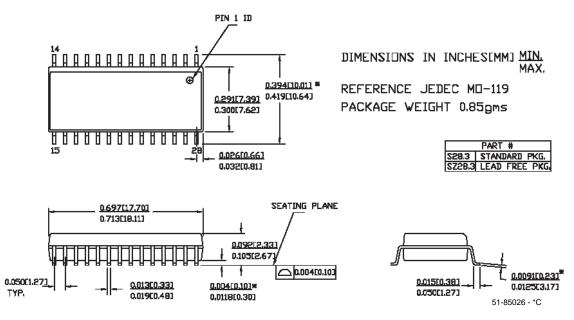

| Mounting Type              | Surface Mount                                                              |

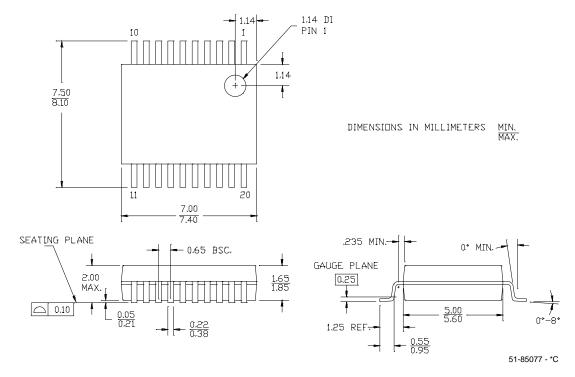

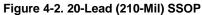

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c27243-24pvi |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

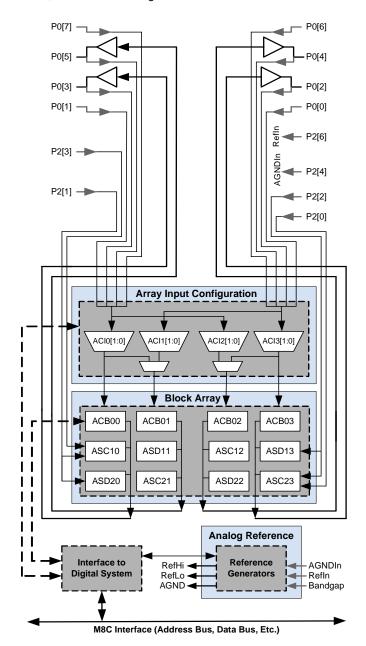

Analog blocks are provided in columns of three, which includes one CT (Continuous Time) and two SC (Switched Capacitor) blocks, as shown in the figure below.

Analog System Block Diagram

### Additional System Resources

System Resources, some of which have been previously listed, provide additional capability useful to complete systems. Additional resources include a multiplier, decimator, switch mode pump, low voltage detection, and power on reset. Brief statements describing the merits of each system resource are presented below.

- Digital clock dividers provide three customizable clock frequencies for use in applications. The clocks can be routed to both the digital and analog systems. Additional clocks can be generated using digital PSoC blocks as clock dividers.

- A multiply accumulate (MAC) provides a fast 8-bit multiplier with 32-bit accumulate, to assist in both general math as well as digital filters.

- The decimator provides a custom hardware filter for digital signal processing applications including the creation of Delta Sigma ADCs.

- The I2C module provides 100 and 400 kHz communication over two wires. Slave, master, and multi-master modes are all supported.

- Low Voltage Detection (LVD) interrupts can signal the application of falling voltage levels, while the advanced POR (Power On Reset) circuit eliminates the need for a system supervisor.

- An internal 1.3V reference provides an absolute reference for the analog system, including ADCs and DACs.

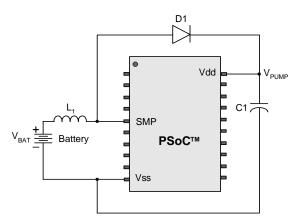

- An integrated switch mode pump (SMP) generates normal operating voltages from a single 1.2V battery cell, providing a low cost boost converter.

## **PSoC Device Characteristics**

Depending on your PSoC device characteristics, the digital and analog systems can have 16, 8, or 4 digital blocks and 12, 6, or 3 analog blocks. The following table lists the resources available for specific PSoC device groups. The PSoC device covered by this data sheet is shown in the second row of the table.

### **PSoC Device Characteristics**

| PSoC Part<br>Number | Digital<br>IO | Digital<br>Rows | Digital<br>Blocks | Analog<br>Inputs | Analog<br>Outputs | Analog<br>Columns | Analog<br>Blocks |

|---------------------|---------------|-----------------|-------------------|------------------|-------------------|-------------------|------------------|

| CY8C29x66           | up to<br>64   | 4               | 16                | 12               | 4                 | 4                 | 12               |

| CY8C27x43           | up to<br>44   | 2               | 8                 | 12               | 4                 | 4                 | 12               |

| CY8C24x23           | up to<br>24   | 1               | 4                 | 12               | 2                 | 2                 | 6                |

| CY8C24x23A          | up to<br>24   | 1               | 4                 | 12               | 2                 | 2                 | 6                |

| CY8C22x13           | up to<br>16   | 1               | 4                 | 8                | 1                 | 1                 | 3                |

### **PSoC Designer Software Subsystems**

### Device Editor

The Device Editor subsystem allows the user to select different onboard analog and digital components called user modules using the PSoC blocks. Examples of user modules are ADCs, DACs, Amplifiers, and Filters.

The device editor also supports easy development of multiple configurations and dynamic reconfiguration. Dynamic configuration allows for changing configurations at run time.

PSoC Designer sets up power-on initialization tables for selected PSoC block configurations and creates source code for an application framework. The framework contains software to operate the selected components and, if the project uses more than one operating configuration, contains routines to switch between different sets of PSoC block configurations at run time. PSoC Designer can print out a configuration sheet for a given project configuration for use during application programming in conjunction with the Device Data Sheet. Once the framework is generated, the user can add application-specific code to flesh out the framework. It's also possible to change the selected components and regenerate the framework.

### Design Browser

The Design Browser allows users to select and import preconfigured designs into the user's project. Users can easily browse a catalog of preconfigured designs to facilitate time-to-design. Examples provided in the tools include a 300-baud modem, LIN Bus master and slave, fan controller, and magnetic card reader.

### Application Editor

In the Application Editor you can edit your C language and Assembly language source code. You can also assemble, compile, link, and build.

**Assembler.** The macro assembler allows the assembly code to be merged seamlessly with C code. The link libraries automatically use absolute addressing or can be compiled in relative mode, and linked with other software modules to get absolute addressing.

**C Language Compiler.** A C language compiler is available that supports Cypress MicroSystems' PSoC family devices. Even if you have never worked in the C language before, the product quickly allows you to create complete C programs for the PSoC family devices.

The embedded, optimizing C compiler provides all the features of C tailored to the PSoC architecture. It comes complete with embedded libraries providing port and bus operations, standard keypad and display support, and extended math functionality.

### Debugger

The PSoC Designer Debugger subsystem provides hardware in-circuit emulation, allowing the designer to test the program in a physical system while providing an internal view of the PSoC device. Debugger commands allow the designer to read and program and read and write data memory, read and write IO registers, read and write CPU registers, set and clear breakpoints, and provide program run, halt, and step control. The debugger also allows the designer to create a trace buffer of registers and memory locations of interest.

### Online Help System

The online help system displays online, context-sensitive help for the user. Designed for procedural and quick reference, each functional subsystem has its own context-sensitive help. This system also provides tutorials and links to FAQs and an Online Support Forum to aid the designer in getting started.

### Hardware Tools

### In-Circuit Emulator

A low cost, high functionality ICE (In-Circuit Emulator) is available for development support. This hardware has the capability to program single devices.

The emulator consists of a base unit that connects to the PC by way of the parallel or USB port. The base unit is universal and will operate with all PSoC devices. Emulation pods for each device family are available separately. The emulation pod takes the place of the PSoC device in the target board and performs full speed (24 MHz) operation.

This chapter describes, lists, and illustrates the CY8C27x43 PSoC device pins and pinout configurations.

## 1.1 Pinouts

The CY8C27x43 PSoC device is available in a variety of packages which are listed and illustrated in the following tables. Every port pin (labeled with a "P") is capable of Digital IO. However, Vss, Vdd, SMP, and XRES are not capable of Digital IO.

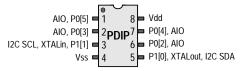

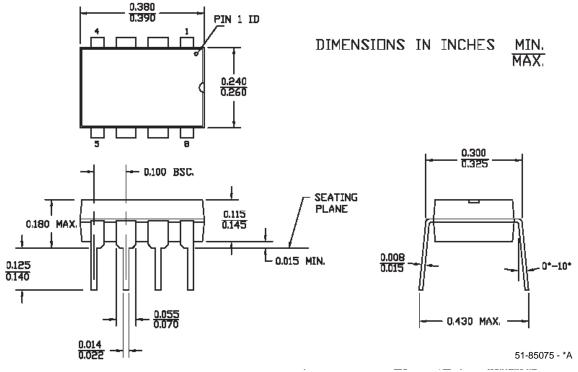

### 1.1.1 8-Pin Part Pinout

| Pin | Ту        | ре     | Pin   | Description                                        |

|-----|-----------|--------|-------|----------------------------------------------------|

| No. | Digital   | Analog | Name  | Description                                        |

| 1   | 10        | 10     | P0[5] | Analog column mux input and column output.         |

| 2   | 10        | 10     | P0[3] | Analog column mux input and column output.         |

| 3   | 10        |        | P1[1] | Crystal Input (XTALin), I2C Serial Clock (SCL)     |

| 4   | Power     |        | Vss   | Ground connection.                                 |

| 5   | IO        |        | P1[0] | Crystal Output (XTALout), I2C Serial Data<br>(SDA) |

| 6   | 10        | 10     | P0[2] | Analog column mux input and column output.         |

| 7   | 10        | 10     | P0[4] | Analog column mux input and column output.         |

| 8   | Power Vdd |        | Vdd   | Supply voltage.                                    |

**LEGEND**: A = Analog, I = Input, and O = Output.

### CY8C27143 8-Pin PSoC Device

## 1.1.2 20-Pin Part Pinout

### Table 1-2. 20-Pin Part Pinout (SSOP, SOIC)

| Pin | Ту      | ре     | Pin   |                                                                       |  |  |  |

|-----|---------|--------|-------|-----------------------------------------------------------------------|--|--|--|

| No. | Digital | Analog | Name  | Description                                                           |  |  |  |

| 1   | 10      | I      | P0[7] | Analog column mux input.                                              |  |  |  |

| 2   | 10      | 10     | P0[5] | Analog column mux input and column output.                            |  |  |  |

| 3   | 10      | 10     | P0[3] | Analog column mux input and column output.                            |  |  |  |

| 4   | 10      | I      | P0[1] | Analog column mux input.                                              |  |  |  |

| 5   | Po      | wer    | SMP   | Switch Mode Pump (SMP) connection to<br>external components required. |  |  |  |

| 6   | 10      |        | P1[7] | I2C Serial Clock (SCL)                                                |  |  |  |

| 7   | 10      |        | P1[5] | I2C Serial Data (SDA)                                                 |  |  |  |

| 8   | 10      |        | P1[3] |                                                                       |  |  |  |

| 9   | 10      |        | P1[1] | Crystal Input (XTALin), I2C Serial Clock (SC                          |  |  |  |

| 10  | Power   |        | Vss   | Ground connection.                                                    |  |  |  |

| 11  | IO      |        | P1[0] | Crystal Output (XTALout), I2C Serial Data (SDA)                       |  |  |  |

| 12  | ю       |        | P1[2] |                                                                       |  |  |  |

| 13  | 10      |        | P1[4] | Optional External Clock Input (EXTCLK)                                |  |  |  |

| 14  | 10      |        | P1[6] |                                                                       |  |  |  |

| 15  | Inj     | out    | XRES  | Active high external reset with internal pull down.                   |  |  |  |

| 16  | IO      | I      | P0[0] | Analog column mux input.                                              |  |  |  |

| 17  | 10      | 10     | P0[2] | Analog column mux input and column output.                            |  |  |  |

| 18  | Ю       | 10     | P0[4] | Analog column mux input and column output.                            |  |  |  |

| 19  | ю       | Ι      | P0[6] | Analog column mux input.                                              |  |  |  |

| 20  | Power V |        | Vdd   | Supply voltage.                                                       |  |  |  |

#### CY8C27243 20-Pin PSoC Device

LEGEND: A = Analog, I = Input, and O = Output.

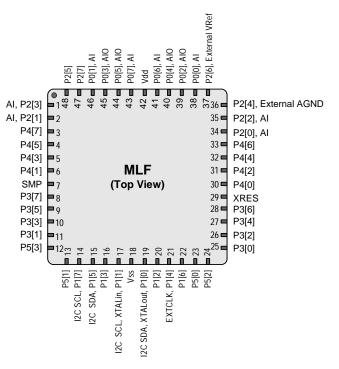

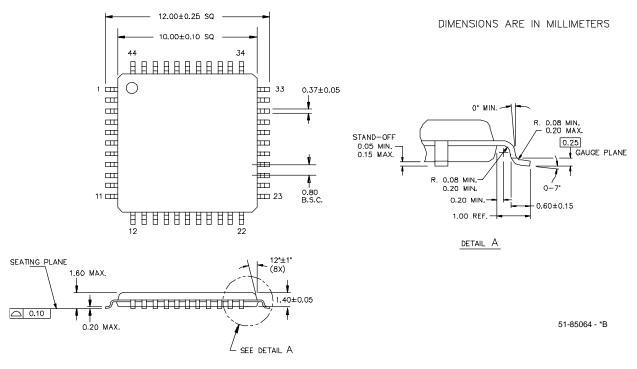

#### Table 1-6. 48-Pin Part Pinout (MLF\*)

| Pin | Ту      | ре     | Pin   |                                                                    |

|-----|---------|--------|-------|--------------------------------------------------------------------|

| No. | Digital | Analog | Name  | Description                                                        |

| 1   | 10      |        | P2[3] | Direct switched capacitor block input.                             |

| 2   | 10      | I      | P2[1] | Direct switched capacitor block input.                             |

| 3   | 10      |        | P4[7] |                                                                    |

| 4   | 10      |        | P4[5] |                                                                    |

| 5   | 10      |        | P4[3] |                                                                    |

| 6   | 10      |        | P4[1] |                                                                    |

| 7   | Po      | wer    | SMP   | Switch Mode Pump (SMP) connection to external components required. |

| 8   | 10      |        | P3[7] |                                                                    |

| 9   | 10      |        | P3[5] |                                                                    |

| 10  | Ю       |        | P3[3] |                                                                    |

| 11  | 10      |        | P3[1] |                                                                    |

| 12  | 10      |        | P5[3] |                                                                    |

| 13  | Ю       |        | P5[1] |                                                                    |

| 14  | 10      |        | P1[7] | I2C Serial Clock (SCL)                                             |

| 15  | Ю       |        | P1[5] | I2C Serial Data (SDA)                                              |

| 16  | 10      |        | P1[3] |                                                                    |

| 17  | 10      |        | P1[1] | Crystal Input (XTALin), I2C Serial Clock (SCL)                     |

| 18  | Po      | wer    | Vss   | Ground connection.                                                 |

| 19  | IO      |        | P1[0] | Crystal Output (XTALout), I2C Serial Data<br>(SDA)                 |

| 20  | 10      |        | P1[2] |                                                                    |

| 21  | 10      |        | P1[4] | Optional External Clock Input (EXTCLK)                             |

| 22  | 10      |        | P1[6] |                                                                    |

| 23  | Ю       |        | P5[0] |                                                                    |

| 24  | 10      |        | P5[2] |                                                                    |

| 25  | 10      |        | P3[0] |                                                                    |

| 26  | 10      |        | P3[2] |                                                                    |

| 27  | 10      |        | P3[4] |                                                                    |

| 28  | 10      |        | P3[6] |                                                                    |

| 29  |         | out    | XRES  | Active high external reset with internal pull down.                |

| 30  | 10      |        | P4[0] |                                                                    |

| 31  | 10      |        | P4[2] |                                                                    |

| 32  | 10      |        | P4[4] |                                                                    |

| 33  | 10      |        | P4[6] |                                                                    |

| 34  | 10      | I      | P2[0] | Direct switched capacitor block input.                             |

| 35  | 10      | I      | P2[2] | Direct switched capacitor block input.                             |

| 36  | 10      |        | P2[4] | External Analog Ground (AGND)                                      |

| 37  | 10      |        | P2[6] | External Voltage Reference (VRef)                                  |

| 38  | 10      | I      | P0[0] | Analog column mux input.                                           |

| 39  | IO      | IO     | P0[2] | Analog column mux input and column output.                         |

| 40  | IO      | IO     | P0[4] | Analog column mux input and column output.                         |

| 41  | IO      | I      | P0[6] | Analog column mux input.                                           |

| 42  |         | wer    | Vdd   | Supply voltage.                                                    |

| 43  | 10      | I      | P0[7] | Analog column mux input.                                           |

| 44  | IO      | IO     | P0[5] | Analog column mux input and column output.                         |

| 45  | IO      | IO     | P0[3] | Analog column mux input and column output.                         |

| 46  | IO      | I      | P0[1] | Analog column mux input.                                           |

| 47  | IO      |        | P2[7] |                                                                    |

| 48  | 10      |        | P2[5] |                                                                    |

#### CY8C27643 48-Pin PSoC Device

LEGEND: A = Analog, I = Input, and O = Output.

$^{\ast}$  The MLF package has a center pad that must be connected to ground (Vss).

| PRTOIDE         00         R/W         40         ASC10CR0         80         R/W         C0           PRTOBE         01         R/W         441         ASC10CR1         81         R/W         C2           PRTOBM2         03         R/W         443         ASC10CR1         84         R/W         C3           PRTIDR         04         R/W         444         ASD11CR1         85         R/W         C4           PRTIG         05         R/W         445         ASD11CR1         86         R/W         C6           PRTIG         06         R/W         446         ASD11CR2         86         R/W         C6           PRTZDR         08         R/W         448         ASC12CR1         88         R/W         C8           PRTZBN2         08         R/W         448         ASC12CR2         88         R/W         C8           PRTZBN2         08         R/W         444         ASD13CR1         80         R/W         C6           PRTZBN2         00         R/W         446         ASD13CR2         86         R/W         C0         P           PRT3L         00         R/W         450         <                                                                                                                                                           | Name     | Addr<br>(0,Hex) | Access |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------|--------|----------|-----------------|--------|----------|-----------------|--------|----------|-----------------|--------|

| PRTODM2         O2         R/W         H         42         ASC10CR2         82         R/W         CC3           PRTIDM         04         R/W         H         44         ASD11CR0         84         R/W         CC3           PRTIDR         04         R/W         H         45         ASD11CR1         85         R/W         CC6           PRTISD         05         R/W         H         ASD11CR1         85         R/W         CC6           PRTISD         06         R/W         H         ASD11CR1         85         R/W         CC6           PRTOM2         08         R/W         H         ASC12CR2         AS         R/W         CA           PRTZSS         0.0         R/W         H         ASC12CR3         B         R/W         CA           PRTZSS         0.0         R/W         H         ASC12CR3         B         R/W         CC8           PRTADR         0.0         R/W         H         ASC12CR3         B         R/W         CC6           PRTADR         0.0         R/W         ASC12CR3         B         R/W         CC7           PRTADR         0.0         R/W         ASC12CR                                                                                                                                                               |          |                 |        |          | -               |        |          |                 |        |          |                 |        |

| PRTODRUZ         0.3         F.W.         4.4         ASC10CR3         8.3         R.W.         C.G.           PRTIJR         0.4         R.W.         4.5         ASD11CR1         85         R.W.         C.G.           PRTIJS         0.5         R.W.         4.6         ASD11CR1         85         R.W.         C.G.           PRTIJDR         0.6         R.W.         4.7         ASD11CR1         85         R.W.         C.G.           PRTIJDR         0.6         R.W.         4.8         ASC12CR1         83         R.W.         C.G.           PRT2DR         0.8         R.W.         4.4         ASC12CR2         8.4         R.W.         C.G.           PRT2DR         0.6         R.W.         4.4         ASC12CR3         8.8         R.W.         C.G.           PRT3DR         0.6         R.W.         4.6         ASD13CR1         8.0         R.W.         C.G.           PRT3DR         0.6         R.W.         4.6         ASD20CR0         9.0         R.W.         D.0           PRT3DR         0.7         R.W.         5.0         ASD20CR0         9.0         R.W.         D.0           PRT3DR         10         R                                                                                                                                    |          | -               |        |          |                 |        |          |                 |        |          |                 |        |

| PRT1IE         04         RW         44         ASD11CR0         84         RW         CC         5           PRT16S         06         RW         46         ASD11CR1         86         RW         C6         C7           PRT10M2         07         RW         47         ASD11CR3         87         RW         C7           PRT2DR         08         RW         48         ASC12CR0         88         RW         C6           PRT3DR         08         RW         44         ASC12CR1         89         RW         C4           PRT3DR         00         RW         44         ASC12CR3         48         RW         C4           PRT3DR         0C         RW         44         ASD13CR0         86         RW         C6           PRT3DR         0C         RW         44         ASD13CR0         86         RW         C6           PRT3DR         0C         RW         45         ASD20CR1         87         RW         C6           PRT3DR         10         RW         51         ASD20CR1         97         RW         D0           PRT3DR         11         RVW         52         ASD20CR1                                                                                                                                                                        |          | -               |        |          |                 |        |          |                 |        |          |                 |        |

| PRT11E         O.G         R.W         45         ASD11CR1         85         R.W         C.G         PRT102         OF         R.W         C.G         PRT102         OF         R.W         C.G         PRT102         OF         R.W         C.G         PRT102         OF         R.W         C.G         PRT2DR         OS         R.W         C.G         D.S         PRT2DR         OS         R.W         C.G         D.S         PRT2DR         OS         R.W         C.G         D.S         PRT2DR         OS         R.S         D.S                                                                                  | -        |                 |        |          |                 |        |          |                 |        |          |                 |        |

| PRT10S         06         RW         46         ASD11CR3         87         RW         C6           PRT1DM2         07         RW         47         ASD11CR3         RS         RW         C6           PRT2E         08         RW         48         ASC12CR1         88         RW         C6           PRT2G         00         RW         44         ASC12CR2         84         RW         CA           PRT3DR         00         RW         44         ASC12CR3         88         RW         CA           PRT3DR         00         RW         44         ASC12CR3         88         RW         CC           PRT3DR         00         RW         44         ASC12CR3         88         RW         CC           PRT3DR         00         RW         45         ASD20CR1         80         RW         CD           PRT3DR         00         RW         51         ASD20CR3         93         RW         D0           PRT4GS         16         RW         55         ASC21CR3         93         RW         D2         RM3           PRT3DR         14         RW         56         ASC21CR3         94<                                                                                                                                                                        |          | -               |        |          |                 |        |          |                 |        |          |                 |        |

| PRT1DM2         07         RW         47         ASD11CR3         87         RW         C.7           PRT2DR         08         RW         48         ASC12CR0         88         RW         C6           PRT3CS         0A         RW         40         ASC12CR0         88         RW         C6           PRT3CS         0A         RW         44         ASC12CR1         89         RW         C6           PRT3DR         0C         RW         44         ASC12CR2         88         RW         C6           PRT3DR         0D         RW         44         ASC12CR2         88         RW         C6           PRT3DR         0D         RW         44         ASD13CR3         86         RW         C6           PRT3DR         0C         RW         44         ASD2CR0         90         RW         D0           PRT3DR         10         RW         50         ASD2CR19         91         RW         D1           PRT41E         11         RW         51         ASD2CR18         93         RW         D2         PRT3           PRT41E         18         W         55         ASC21CR19                                                                                                                                                                                 |          |                 |        |          |                 |        |          |                 |        |          |                 |        |

| PRT2DR         06         R/W         48         ASC12CR1         89         R/W         C63           PRT2E         00         R/W         49         ASC12CR1         89         R/W         C63           PRT2DM2         06         R/W         40         ASC12CR2         8A         R/W         C64           PRT3DR         0C         R/W         40         ASC12CR3         8B         R/W         C62           PRT3DR         0C         R/W         40         ASD13CR4         8D         R/W         C62           PRT3DR         0C         R/W         40         ASD13CR4         8D         R/W         C62           PRT3DR         0F         R/W         44         ASD13CR4         8F         R/W         C62           PRT3DR         0F         R/W         451         ASD20CR1         90         R/W         D0           PRT41E         11         R/W         53         ASD20CR3         93         R/W         D3           PRT3DR         14         R/W         55         ASC21CR1         95         R/W         D6           PRT3DR         14         R/W         56         ASC221CR1                                                                                                                                                                 |          |                 |        |          |                 |        |          |                 |        |          |                 |        |

| PRT2DS         0.A         R/W         4A         ASC12CR2         8A         R/W         C.A           PRT3DR         06         R/W         4B         ASC12CR2         8A         R/W         CG           PRT3DR         0C         R/W         4C         ASD13CR0         8C         R/W         CC           PRT3DR         0D         R/W         4D         ASD13CR2         8R         R/W         CC           PRT3DR         0D         R/W         4D         ASD13CR2         8R         R/W         CC           PRT3DR         0D         R/W         4F         ASD13CR3         8F         R/W         CC           PRT4DR         10         R/W         51         ASD20CR1         91         R/W         D0           PRT4DR         13         R/W         53         ASD20CR2         92         R/W         D4           PRT3DR         14         R/W         54         ASC21CR1         91         R/W         D4           PRT3DK         15         R/W         55         ASC21CR2         96         R/W         12C_CRG         D6           PRT3DK         14         R/W         56         A                                                                                                                                                               | PRT2DR   | 08              | RW     |          |                 |        | ASC12CR0 | 88              | RW     |          | C8              |        |

| PRT2DM2         0B         RW         4B         ASC12CR3         8B         RW         CB           PRT3JE         0C         RW         4D         ASD13CR1         8D         RW         CC           PRT3JE         0D         RW         4D         ASD13CR1         8D         RW         CC           PRT3JE         0F         RW         4E         ASD13CR3         8F         RW         CF           PRT3DM2         0F         RW         4E         ASD13CR3         8F         RW         CF           PRT3DM2         0F         RW         4E         ASD13CR3         8F         RW         CF           PRT4DM2         10         RW         50         ASD20CR3         91         RW         D0           PRT4DM2         12         RW         53         ASD20CR3         93         RW         D3           PRT3DR         14         RW         54         ASD21CR3         96         RW         CC_SCR         D7           PRT3DR         14         RW         57         ASC21CR3         97         RW         I2C_SCR         D7           PRT3DM2         17         RW         55                                                                                                                                                                           | PRT2IE   | 09              | RW     |          | 49              |        | ASC12CR1 | 89              | RW     |          | C9              |        |

| PRT3DR         0C         RW         4C         ASD13CR0         8C         RW         CC         CC           PRT3GS         0E         RW         4D         ASD13CR1         8D         RW         CD           PRT3GS         0E         RW         4E         ASD13CR2         8E         RW         CE           PRT3GS         0F         RW         4F         ASD13CR2         8E         RW         CE           PRT4DR         10         RW         50         ASD20CR2         90         RW         D0           PRT41R         11         RW         51         ASD20CR2         92         RW         D2           PRT41R         11         RW         53         ASD20CR2         92         RW         D3           PRT41SE         11         RW         55         ASC21CR1         95         RW         D3           PRT51E         16         RW         56         ASC21CR2         96         RW         ICC_CFG         D6         RW           PRT50M2         17         RW         57         ASC21CR2         9A         RW         INT_CLR0         DA         RW         ICC_CFG         D8                                                                                                                                                                   | PRT2GS   | 0A              | RW     |          | 4A              |        | ASC12CR2 | 8A              | RW     |          | CA              |        |

| PRT31E         OD         RW         4D         ASD13CR1         8D         RW         CD           PRT30M2         0F         RW         4E         ASD13CR2         8E         RW         CF           PRT3DM2         0F         RW         4F         ASD13CR2         8F         RW         CF           PRT4DR         10         RW         50         ASD20CR1         91         RW         D0           PRT41E         11         RW         51         ASD20CR2         92         RW         D2           PRT40M2         13         RW         53         ASD20CR2         93         RW         D3           PRT50R         14         RW         55         ASD20CR3         93         RW         D4           PRT30K2         16         RW         56         ASC21CR3         98         RW         ICC_CFG         D6         RW           PRT30K2         17         RW         57         ASC21CR3         98         RW         ICC_CFG         D6         RW           18         58         ASD22CR3         98         RW         ICL_CR         DA         RW           10         55 <t< td=""><td></td><td>-</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                  |          | -               |        |          |                 |        |          |                 |        |          |                 |        |

| PRT3G         OE         RW         4E         ASD13CR2         8E         RW         CE           PRT3DM2         OF         RW         4F         ASD13CR3         8F         RW         CF           PRT4DR         10         RW         50         ASD20CR0         90         RW         D0           PRT4IE         11         RW         51         ASD20CR3         93         RW         D3           PRT4GS         12         RW         52         ASD20CR3         93         RW         D3           PRT5DR         14         RW         55         ASC21CR0         94         RW         D4           PRTSDR         16         RW         56         ASC21CR2         96         RW         IC2_CFG         D5           PRTSDR         17         RW         57         ASC21CR2         96         RW         IC2_SCR         D7         #           PRTSDR         18          58         ASD22CR1         98         RW         IC2_MSCR         D8         RW           10          5D         ASC23CR1         98         RW         INT_CLR1         D8         RW                                                                                                                                                                                                   |          |                 |        |          |                 |        |          |                 |        |          |                 |        |

| PRT3DM2         OF         RW         4F         ASD13CR3         8F         RW         CF           PRT4DR         10         RW         50         ASD20CR0         90         RW         D0           PRT4E         11         RW         51         ASD20CR1         91         RW         D2           PRT4E         11         RW         53         ASD20CR3         93         RW         D3           PRT5DR         14         RW         54         ASD20CR3         93         RW         D4           PRT5DR         14         RW         55         ASC1CR1         95         RW         D4           PRT5DR         16         RW         56         ASC21CR2         96         RW         12C_CBC         D6         RW           PRT5DN2         17         RW         57         ASC21CR2         98         RW         IZC_SCR         D7         #           19         C         59         ASD22CR3         98         RW         INT_CLR1         D8         RW           10         C         5C         ASC23CR1         90         RW         INT_CLR1         D8         RW           10<                                                                                                                                                                        |          |                 |        |          |                 |        |          |                 |        |          |                 |        |

| PRT4DR         10         RW         50         ASD20CR0         90         RW         D0           PRT4IE         11         RW         51         ASD20CR1         91         RW         D1           PRT40S         12         RW         53         ASD20CR2         92         RW         D2           PRT4DR         13         RW         53         ASD21CR2         92         RW         D3           PRT5DR         14         RW         54         ASC21CR2         96         RW         D4           PRT5GS         16         RW         56         ASC21CR3         97         RW         I2C_CFG         D6         RW           PRT5DM2         17         RW         56         ASC21CR3         97         RW         I2C_CMC         D8         RW           18          58         ASD22CR1         98         RW         I2C_CMC         DA         RW           10          56         ASC23CR3         96         RW         INT_CLR1         DB         RW           11C          55         ASC23CR3         96         RW         INT_MSK1         E1         RW                                                                                                                                                                                                  |          | -               |        |          |                 |        |          | -               |        |          |                 |        |

| PRT4IE         11         RW         51         ASD20CR1         91         RW         D1           PRT4GS         12         RW         52         ASD20CR2         92         RW         D2           PRT4DW2         13         RW         53         ASD20CR3         93         RW         D3           PRT5DR         14         RW         54         ASC21CR1         95         RW         D4           PRT5DR         14         RW         56         ASC21CR2         96         RW         12C_CFG         D6         RW           PRT5DL2         17         RW         57         ASC21CR2         98         RW         12C_CSCR         D7         #           PRT5DL1         17         RW         57         ASC22CR1         99         RW         12C_CMSCR         D8         RW           18         58         ASD22CR3         98         RW         INT_CLR1         D8         RW           10         50         ASC23CR3         9F         RW         INT_MSK3         DE         RW           11         1         F         55         ASC23CR3         9F         RW         INT_MSK3         DE                                                                                                                                                             |          | -               |        |          |                 |        |          |                 |        |          |                 |        |

| PRT4DX2         12         RW         52         ASD20CR2         92         RW         D2           PRT4DM2         13         RW         53         ASD20CR3         93         RW         D3           PRT5DR         14         RW         55         ASC21CR0         94         RW         D4           PRT5IE         15         RW         56         ASC21CR3         97         RW         I2C_CFG         D6         RW           PRT50S         16         RW         57         ASC21CR3         97         RW         I2C_CFG         D8         RW           PRT50M2         17         RW         57         ASC22CR3         98         RW         I2C_DR         D8         RW           14         C         58         ASD22CR3         98         RW         IZC_MSC         D0         RW           16         C         56         ASC23CR1         90         RW         INT_CLR3         DD         RW           17         AMX_IN         60         RW         ASC         INT_MSK1         E1         RW           DB800DR0         23         #         ARF_CR         63         RW         A3                                                                                                                                                                   |          | -               |        |          |                 |        |          |                 |        |          |                 |        |

| PRT4DM2         13         RW         53         ASD20CR3         93         RW         D3           PRT5DR         14         RW         54         ASC21CR1         94         RW         D4           PRT5DR         15         RW         55         ASC21CR1         95         RW         D25           PRT5CS         16         RW         56         ASC21CR2         96         RW         I2C_SCR         D7         #           PRT5DM2         17         RW         57         ASC21CR3         97         RW         I2C_SCR         D7         #           18          58         ASD22CR1         99         RW         IZC_MSCR         D9         #           14          55         ASD22CR2         9A         RW         INT_CLR0         DA         RW           16          56         ASD22CR3         9B         RW         INT_CLR3         DD         RW           17          57         ASC23CR3         9F         RW         DE         RW           18          56         ASC23CR3         9F         RW         DE         RW         DB                                                                                                                                                                                                                    |          |                 |        |          |                 |        |          |                 |        |          |                 |        |

| PRT50R         14         RW         54         ASC21CR0         94         RW         D4           PRTSIE         15         RW         55         ASC21CR1         95         RW         D5           PRTS0M         17         RW         56         ASC21CR2         96         RW         I2C_CFG         D6         RW           PRT50M2         17         RW         57         ASC21CR3         97         RW         I2C_SCR         D7         #           18          58         ASD22CR1         99         RW         I2C_MSCR         D9         #           14          58         ASD22CR2         9A         RW         INT_CLR0         DA         RW           16          55         ASC23CR3         9E         RW         INT_CLR3         DC         RW         RW         DR         DR         RW         DR         DR         RW         DR         RW         INT_MSK3         DE         RW         DR         RW         INT_MSK3         DE         RW         DB         DB         DB         DB         DE         DB         RW         DB         DB         DE         RW <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>-</td><td></td><td></td><td></td><td>   </td></t<>                                                |          |                 |        |          |                 |        |          | -               |        |          |                 |        |

| PRT6IE         15         RW         55         ASC21CR1         95         RW         D5           PRT6GS         16         RW         56         ASC21CR2         96         RW         I2C_CFG         D6         RW           PRT5DM2         17         RW         S8         ASD22CR3         97         RW         I2C_SCR         D7         #           18         58         ASD22CR1         99         RW         I2C_MSCR         D8         RW           14         54         ASD22CR2         9A         RW         INT_CLR         DA         RW           18         55         ASC23CR1         99         RW         INT_CLR         DA         RW           10         55         ASC23CR3         95         RW         INT_CLR3         DD         RW           116         55         ASC23CR3         97         RW         INT_MSK3         DE         RW           118         57         ASC33CR3         97         RW         INT_MSK3         DE         RW           116         58         ASC23CR3         97         RW         INT_MSK3         DE         RW           DB800DR0 <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                              |          |                 |        |          |                 |        |          |                 |        |          |                 |        |

| PRT5GS         16         RW         56         ASC21CR2         96         RW         12C_CFG         D6         RW           PRT5DM2         17         RW         57         ASC21CR3         97         RW         12C_SCR         D7         #           19         59         ASD22CR1         99         RW         12C_MSCR         D9         #           14         54         ASD22CR3         98         RW         INT_CLR1         D8         RW           16         56         ASD22CR3         98         RW         INT_CLR1         D8         RW           16         56         ASC23CR1         90         RW         INT_CLR3         DD         RW           17         T         55         ASC23CR2         95         RW         INT_MSK3         DE         RW           18         58         ASC23CR2         97         RW         INT_MSK3         DE         RW           16         4         ASC23CR2         97         RW         INT_MSK3         DE         RW           DB800DR0         20         #         AMX_I         60         RW         A0         INT_MSK1         E1         RW                                                                                                                                                            |          |                 |        |          |                 |        |          |                 |        |          |                 |        |

| 18         18         58         ASD22CR0         98         RW         12C_DR         D8         RW           14         59         ASD22CR1         99         RW         IIZ_MSCR         D9         #           18         58         ASD22CR2         9A         RW         INT_CLR0         DA         RW           18         58         ASD22CR3         9B         RW         INT_CLR1         DB         RW           10         55C         ASC32CR1         9D         RW         INT_CLR3         DD         RW           11         10         55F         ASC23CR2         9E         RW         INT_MSK3         DE         RW           11F         55F         ASC23CR3         9F         RW         DF         DB00DR0         20         #         AMX_IN         60         RW         ASC32CR2         9E         RW         INT_MSK3         DE         RW           DB800DR0         20         #         AMX_IN         60         RW         ASC32CR2         9E         RW         INT_MSK3         DE         RW         DB00DR0         28         W         DB01DR1         21         W         61         A1         IN                                                                                                                                       | -        | -               |        |          |                 |        |          |                 |        | I2C CFG  |                 | RW     |

| 19         59         ASD22CR1         99         RW         I2C_MSCR         D9         #           1A         5A         ASD22CR2         9A         RW         INT_CLR0         DA         RW           1B         5B         ASD22CR3         9B         RW         INT_CLR1         DB         RW           1C         5C         ASC23CR0         9C         RW         INT_CLR3         DD         RW           1D         5D         ASC23CR1         9D         RW         INT_CLR3         DD         RW           1E         5F         ASC23CR2         9F         RW         INT_MSK3         DE         RW           DB800DR0         20         #         AMA_IN         60         RW         A0         INT_MSK1         E1         RW           DB800DR1         21         W         61         A1         INT_MSK1         E1         RW           DB800DR2         22         RW         61         A1         INT_MSK1         E1         RW           DB800DR1         24         #         CMP_CR0         63         RW         A3         RES_WDT         E3         W           DB801DR2         26 </td <td>PRT5DM2</td> <td>17</td> <td>RW</td> <td></td> <td>57</td> <td></td> <td>ASC21CR3</td> <td>97</td> <td>RW</td> <td>I2C_SCR</td> <td>D7</td> <td>#</td> | PRT5DM2  | 17              | RW     |          | 57              |        | ASC21CR3 | 97              | RW     | I2C_SCR  | D7              | #      |

| 1A         1A         5A         ASD22CR2         9A         RW         INT_CLR0         DA         RW           1B         5B         ASD22CR3         9B         RW         INT_CLR1         DB         RW           1C         5C         ASC23CR0         9C         RW         INT_CLR3         DD         RW           1D         5D         ASC23CR1         9D         RW         INT_CLR3         DD         RW           1E         5F         ASC23CR2         9E         RW         INT_MSK3         DE         RW           DB800DR0         20         #         AMX_IN         60         RW         ASC23CR3         9F         RW         DF           DB800DR1         21         W         61         AT         INT_MSK0         E0         RW           DB800DR0         23         #         ARF_CR         63         RW         A3         RES_WDT         E3         W           DB800DR1         24         #         CMP_CR0         64         A4         A4         DEC_DL         E5         RC           DB801DR1         25         W         ASY         CR67         A7         DEC_DL         E5                                                                                                                                                            |          | 18              |        |          | 58              |        | ASD22CR0 | 98              | RW     | I2C_DR   | D8              | RW     |

| 1B         5B         ASD22CR3         9B         RW         INT_CLR1         DB         RW           1C         5C         ASC23CR0         9C         RW         DC         DC           1D         5D         ASC23CR1         9D         RW         INT_CLR3         DD         RW           1E         5E         ASC23CR2         9E         RW         INT_MSK3         DE         RW           DB800DR         20         #         AMX_IN         60         RW         AO         INT_MSK3         DE         RW           DB800DR0         20         #         AMX_IN         60         RW         AO         INT_MSK1         E1         RW           DB800DR0         23         #         ARF_CR         63         RW         A3         RES_WDT         E3         W           DB801DR1         25         W         ASY_CR         65         #         A4         DEC_DL         E5         RC           DB801DR1         25         W         ASY_CR         66         RW         A6         DEC_OL         E5         RV           DB801CR0         27         #         67         A7         DEC_CR1                                                                                                                                                                  |          | 19              |        |          | 59              |        | ASD22CR1 | 99              | RW     | I2C_MSCR | D9              | #      |

| 1C         5C         ASC23CR0         9C         RW         INT_CLR3         DC           1D         5D         ASC23CR1         9D         RW         INT_CLR3         DD         RW           1F         5F         ASC23CR2         9E         RW         INT_MSK3         DE         RW           DB600DR0         20         #         AMX_IN         60         RW         AO         INT_MSK0         EO         RW           DB600DR1         21         W         61         A1         INT_MSK0         EO         RW           DB600DR2         22         RW         62         A2         INT_MSK1         E1         RW           DB601DR1         24         #         CMP_CR0         64         #         A4         DEC_DH         E5         RC           DB801DR1         25         W         ASY_CR         65         #         A5         DEC_DH         E5         RW           DB801DR2         26         RW         CMP_CR1         66         RW         A6         DEC_CR1         E7         RW           DC802DR1         29         W         69         A9         MUL_Y         E9         W                                                                                                                                                               |          |                 |        |          |                 |        |          |                 |        |          | DA              | RW     |

| 1D         5D         ASC23CR1         9D         RW         INT_CLR3         DD         RW           1E         5E         ASC23CR2         9E         RW         INT_MSK3         DE         RW           DB800DR0         20         #         AMX_IN         60         RW         AO         INT_MSK0         EO         RW           DB800DR1         21         W         61         A1         INT_MSK1         E1         RW           DB800DR1         21         W         61         A1         INT_MSK1         E1         RW           DB800CR0         23         #         ARF_CR         63         RW         A3         RES_WDT         E3         W           DB801DR1         25         W         ASY_CR         65         #         A5         DEC_DL         E5         RC           DB801DR2         26         RW         CMP_CR1         66         RW         A6         DEC_CR1         E7         RW           DC802DR0         28         #         68         A8         A8         MUL_Y         E9         W           DC802DR1         29         W         69         A7         DEC_CR1                                                                                                                                                                  |          |                 |        |          |                 |        |          |                 |        | INT_CLR1 |                 | RW     |

| 1E         5E         ASC23CR2         9E         RW         INT_MSK3         DE         RW           DBB00DR         20         #         AMX_IN         60         RW         AO         INT_MSK0         E0         RW           DBB00DR1         21         W         61         A1         INT_MSK1         E1         RW           DBB00DR2         22         RW         62         A2         INT_VC         E2         RC           DBB00DR1         24         #         CMP_CR0         64         #         A4         DEC_DL         E5         RC           DBB01DR1         25         W         ASY_CR         65         #         A4         DEC_DL         E5         RC           DBB01DR1         25         W         ASY_CR         65         #         A4         DEC_DL         E5         RC           DB801DR2         26         RW         CMB         A6         DEC_DL         E5         RC           DB801DR2         28         #         68         A8         MUL_X         E8         W           DC802DR1         29         W         69         A9         MUL_Y         E9         W<                                                                                                                                                                |          |                 |        |          |                 |        |          |                 |        |          |                 |        |

| 1F         5F         ASC23CR3         9F         RW         DF           DBB00DR0         20         #         AMX_IN         60         RW         A0         INT_MSK0         E0         RW           DBB00DR1         21         W         61         A1         INT_MSK1         E1         RW           DBB00DR2         22         RW         62         A2         INT_VC         E2         RC           DBB00DR0         23         #         ARF_CR         63         RW         A3         RES_WDT         E3         W           DB801DR1         25         W         ASY_CR         65         #         A4         DEC_DH         E4         RC           DB801DR1         25         W         ASY_CR         65         #         A5         DEC_DL         E5         RC           DB801DR1         25         W         CMP_CR1         66         RW         A6         DEC_CR1         E7         RW           DC802DR1         29         W         69         A8         MUL_X         E8         W           DC802DR2         2A         RW         6A         AA         AMU_DL         E <r< td=""></r<>                                                                                                                                                           |          |                 |        |          |                 |        |          |                 |        |          |                 |        |

| DBB00DR0         20         #         AMX_IN         60         RW         A0         INT_MSK0         E0         RW           DBB00DR1         21         W         61         A1         INT_MSK1         E1         RW           DBB00DR2         22         RW         62         A2         INT_VC         E2         RC           DBB00CR0         23         #         ARF_CR         63         RW         A3         RES_WDT         E3         W           DBB01DR0         24         #         CMP_CR0         64         #         A4         DEC_DL         E5         RC           DB801DR1         25         W         ASY_CR         65         #         A5         DEC_DL         E5         RC           DB801CR0         27         #         67         A7         DEC_CR1         E7         RW           DC802DR1         29         W         68         A8         MUL_Y         E9         W           DC802DR2         2A         RW         66         AA         AA         MUL_DH         EA         R           DC803DR1         2D         W         6B         AA         AC         ACC_DRD                                                                                                                                                                |          |                 |        |          |                 |        |          | -               |        | INT_MSK3 |                 | RW     |

| DBB00DR1         21         W         -         61         A1         INT_MSK1         E1         RW           DBB00DR2         22         RW         62         A2         INT_VC         E2         RC           DBB00DR0         23         #         ARF_CR         63         RW         A3         RES_WDT         E3         W           DBB01DR0         24         #         CMP_CR0         64         #         A4         DEC_DH         E4         RC           DBB01DR1         25         W         ASY_CR         65         #         A4         DEC_DL         E5         RC           DB801DR2         26         RW         CMP_CR1         66         RW         A6         DEC_CR1         E7         RW           DCB02DR0         28         #         68         A8         MUL_X         E8         W           DCB02DR1         29         W         69         A9         MUL_Y         E9         W           DCB02DR2         2A         RW         6A         AA         MUL_DH         EA         R           DCB03DR1         2D         W         6D         AD         ACC_DRO         ED <td>DBB00DB0</td> <td></td> <td>#</td> <td>ΔΜΧ ΙΝΙ</td> <td></td> <td>RW/</td> <td>ASUZSUKS</td> <td></td> <td>RVV</td> <td>INT MSKO</td> <td></td> <td>RW/</td>  | DBB00DB0 |                 | #      | ΔΜΧ ΙΝΙ  |                 | RW/    | ASUZSUKS |                 | RVV    | INT MSKO |                 | RW/    |

| DBB00DR2         22         RW         62         A         A2         INT_VC         E2         RC           DBB00CR0         23         #         ARF_CR         63         RW         A3         RES_WDT         E3         W           DB01DR0         24         #         CMP_CR0         64         #         A4         DEC_DH         E4         RC           DB01DR1         25         W         ASY_CR         65         #         A5         DEC_DL         E5         RC           DB01DR2         26         RW         CMP_CR1         66         RW         A6         DEC_CR1         E7         RW           DCB02DR0         28         #         68         A3         MUL_X         E8         W           DCB02DR1         29         W         69         A49         MUL_V         E9         W           DCB03DR1         20         W         66         AA         AA         MUL_DL         EB         R           DCB03DR1         2C         #         6C         AC         ACC_DR0         ED         RW           DCB03DR2         2E         RW         6F         AB         ACC_DR3                                                                                                                                                                      |          | -               |        |          |                 | 1      |          |                 |        | _        | -               |        |

| DBB00CR0         23         #         ARF_CR         63         RW         A3         RES_WDT         E3         W           DBB01DR0         24         #         CMP_CR0         64         #         A4         DEC_DH         E4         RC           DBB01DR1         25         W         ASY_CR         65         #         A5         DEC_DL         E5         RC           DBB01DR2         26         RW         CMP_CR1         66         RW         A6         DEC_CR1         E7         RW           DBB01CR0         27         #         66         RW         A6         DEC_CR1         E7         RW           DCB02DR0         28         #         68         A8         MUL_Y         E9         W           DCB02DR1         29         W         6A         AA         AA         MUL_DL         EB         R           DCB02DR2         2A         RW         6A         AA         AA         MUL_DL         EB         R           DCB03DR1         2D         W         6D         AA         AC         ACC_DR3         EE         RW           DCB03DR1         2D         W         6E                                                                                                                                                                       |          |                 |        |          |                 |        |          |                 |        |          |                 |        |

| DBB01DR0         24         #         CMP_CR0         64         #         A4         DEC_DH         E4         RC           DBB01DR1         25         W         ASY_CR         65         #         A5         DEC_DL         E5         RC           DBB01DR2         26         RW         CMP_CR1         66         RW         A6         DEC_CR1         E7         RW           DBB01CR0         27         #         66         RW         A6         DEC_CR1         E7         RW           DCB02DR0         28         #         68         A8         MUL_X         E8         W           DCB02DR1         29         W         68         A8         MUL_DH         EA         R           DCB02DR1         29         W         6A         AA         AB         MUL_DH         EA         R           DCB02DR1         20         W         6A         AA         AC         ACC_DR1         EC         RW           DCB03DR1         2D         W         6C         AC         AC         ACC_DR3         EE         RW           DCB03DR2         2E         RW         6E         AE         ACC_DR3                                                                                                                                                                     |          |                 |        | ARF CR   | -               | RW     |          |                 |        | -        |                 |        |

| DBB01DR2         26         RW         CMP_CR1         66         RW         A6         DEC_CR0         E6         RW           DBB01CR0         27         #         67         A7         DEC_CR1         E7         RW           DCB02DR0         28         #         68         A8         MUL_X         E8         W           DCB02DR1         29         W         69         A9         MUL_Y         E9         W           DCB02DR2         2A         RW         6A         A8         MUL_DL         EB         R           DCB02DR0         2E         RW         6A         AA         MUL_DL         EB         R           DCB02DR0         2C         #         6C         AA         AC         ACC_DR1         EC         RW           DCB03DR1         2D         W         6D         AE         ACC_DR0         ED         RW           DCB03DR2         2E         RW         6E         AE         ACC_DR2         EF         RW           DB810DR1         30         #         ACB00CR3         70         RW         RDIOSIN         B0         RW         F1         DB           DB810DR1                                                                                                                                                                        | DBB01DR0 | 24              | #      | CMP_CR0  | 64              | #      |          | A4              |        | DEC_DH   | E4              | RC     |

| DBB01CR0         27         #         67         A7         DEC_CR1         E7         RW           DCB02DR0         28         #         68         A8         MUL_X         E8         W           DCB02DR1         29         W         69         A9         MUL_Y         E9         W           DCB02DR2         2A         RW         6A         AA         MUL_DH         EA         R           DCB02CR0         2B         #         6B         AB         MUL_DL         EB         R           DCB03DR0         2C         #         6C         AC         AC         ACC_DR1         EC         RW           DCB03DR1         2D         W         6D         AD         AC         ACC_DR3         EE         RW           DCB03DR1         2D         W         6E         AE         ACC_DR3         EE         RW           DCB03CR0         2F         #         6F         AF         ACC_DR2         EF         RW           DB810DR1         30         #         ACB00CR3         70         RW         RDI0SYN         B1         RW         F1         DB810DR3         E         RW         F2                                                                                                                                                                        | DBB01DR1 | 25              | W      | ASY_CR   | 65              | #      |          | A5              |        | DEC_DL   | E5              | RC     |

| DCB02DR0         28         #         68         A8         MUL_X         E8         W           DCB02DR1         29         W         69         A9         MUL_Y         E9         W           DCB02DR2         2A         RW         6A         AA         MUL_DH         EA         R           DCB02DR0         2B         #         6B         AA         MUL_DH         EA         R           DCB03DR0         2C         #         6C         AC         ACC_DR1         EC         RW           DCB03DR1         2D         W         6C         AC         ACC_DR3         EE         RW           DCB03DR1         2D         W         6E         AE         ACC_DR3         EE         RW           DCB03DR1         2D         W         6F         AF         ACC_DR2         EF         RW           DCB03CR0         2F         #         ACB00CR3         70         RW         RDI0RI         B0         RW         F0         PD           DB810DR1         31         W         ACB00CR1         72         RW         RDI0IS         B2         RW         F3         DBB11DR1         S         ACB01C                                                                                                                                                                | DBB01DR2 | 26              | RW     | CMP_CR1  | 66              | RW     |          | A6              |        | DEC_CR0  | E6              | RW     |

| DCB02DR1         29         W         69         A9         MUL_Y         E9         W           DCB02DR2         2A         RW         6A         AA         MUL_DH         EA         R           DCB02CR0         2B         #         6B         AB         MUL_DL         EB         R           DCB03DR0         2C         #         6C         AC         ACC_DR1         EC         RW           DCB03DR1         2D         W         6D         AD         ACC_DR0         ED         RW           DCB03DR1         2D         W         6D         AE         ACC_DR0         ED         RW           DCB03DR2         2E         RW         6E         AF         ACC_DR3         EE         RW           DCB03DR0         30         #         ACB00CR3         70         RW         RDIORI         B0         RW         F0         D           DB810DR1         31         W         ACB00CR1         72         RW         RDIOS         B2         RW         F1         D         D         DB10R1         31         W         ACB01CR2         73         RW         RDIOS         B2         RW         F3                                                                                                                                                              |          |                 |        |          | 67              |        |          | A7              |        | DEC_CR1  |                 |        |

| DCB02DR2         2A         RW         6A         AA         MUL_DH         EA         R           DCB02CR0         2B         #         6B         AB         MUL_DL         EB         R           DCB03DR0         2C         #         6C         AC         AC         ACC_DR1         EC         RW           DCB03DR1         2D         W         6D         AD         ACC_DR0         ED         RW           DCB03DR2         2E         RW         6E         AE         ACC_DR3         EE         RW           DCB03OR0         2F         #         6F         AE         ACC_DR3         EE         RW           DB810DR0         30         #         ACB00CR3         70         RW         RDI0RI         B0         RW         F0         D           DB810DR1         31         W         ACB00CR1         72         RW         RDI0SYN         B1         RW         F1         D           DB810DR2         32         RW         ACB00CR2         73         RW         RDI0IT0         B3         RW         F3         D           DB811DR0         34         #         ACB01CR0         75 <t< td=""><td></td><td>-</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                          |          | -               |        |          |                 |        |          |                 |        |          |                 |        |

| DCB02CR0         2B         #         6B         AB         MUL_DL         EB         R           DCB03DR0         2C         #         6C         AC         AC         ACC_DR1         EC         RW           DCB03DR1         2D         W         6D         AD         AC         ACC_DR0         ED         RW           DCB03DR2         2E         RW         6E         AE         ACC_DR3         EE         RW           DCB03CR0         2F         #         6F         AF         ACC_DR2         EF         RW           DB810DR0         30         #         ACB00CR3         70         RW         RDI0SI         B0         RW         F1           DB810DR1         31         W         ACB00CR1         72         RW         RDI0SI         B2         RW         F2           DB810DR2         32         RW         ACB01CR3         74         RW         RDI0IT0         B3         RW         F3            DB811DR0         34         #         ACB01CR1         75         RW         RDI0R0         B5         RW         F5            DB811DR1         35         W                                                                                                                                                                                         |          | -               |        |          |                 |        |          |                 |        | _        |                 |        |

| DCB03DR0         2C         #         6C         AC         AC         ACC_DR1         EC         RW           DCB03DR1         2D         W         6D         AD         AD         ACC_DR0         ED         RW           DCB03DR2         2E         RW         6E         AE         ACC_DR3         EE         RW           DCB03CR0         2F         #         6F         AF         ACC_DR2         EF         RW           DB810DR0         30         #         ACB00CR3         70         RW         RDI0RI         B0         RW         F0         PRW           DB810DR1         31         W         ACB00CR0         71         RW         RDI0SIN         B1         RW         F1         PRW           DB810DR2         32         RW         ACB00CR1         72         RW         RDI0SIN         B1         RW         F2         PRW           DB810DR2         33         #         ACB01CR1         72         RW         RDI0SIN         B2         RW         F3         PRW           DB810DR3         34         #         ACB01CR2         73         RW         RDI0LT0         B3         RW         F4 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>_</td> <td></td> <td></td>                          |          |                 |        |          |                 |        |          |                 |        | _        |                 |        |