Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c27643-24lfxi |

|----------------------------|-----------------------------------------------------------------------------|

| Supplier Device Package    | 48-QFN (7x7)                                                                |

| Package / Case             | 48-VFQFN Exposed Pad                                                        |

| Mounting Type              | Surface Mount                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Oscillator Type            | Internal                                                                    |

| Data Converters            | A/D 4x14b; D/A 4x9b                                                         |

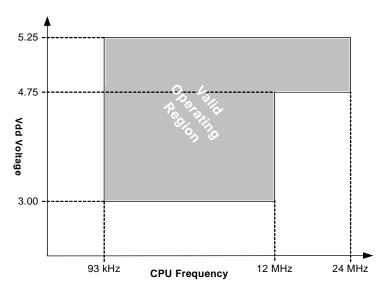

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                  |

| RAM Size                   | 256 x 8                                                                     |

| EEPROM Size                | -                                                                           |

| Program Memory Type        | FLASH                                                                       |

| Program Memory Size        | 16KB (16K x 8)                                                              |

| Number of I/O              | 44                                                                          |

| Peripherals                | POR, PWM, WDT                                                               |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Speed                      | 24MHz                                                                       |

| Core Size                  | 8-Bit                                                                       |

| Core Processor             | M8C                                                                         |

| Product Status             | Obsolete                                                                    |

| Details                    |                                                                             |

processor. The CPU utilizes an interrupt controller with 17 vectors, to simplify programming of real time embedded events. Program execution is timed and protected using the included Sleep and Watch Dog Timers (WDT).

Memory encompasses 16 KB of Flash for program storage, 256 bytes of SRAM for data storage, and up to 2 KB of EEPROM emulated using the Flash. Program Flash utilizes four protection levels on blocks of 64 bytes, allowing customized software IP protection.

The PSoC device incorporates flexible internal clock generators, including a 24 MHz IMO (internal main oscillator) accurate to 2.5% over temperature and voltage. The 24 MHz IMO can also be doubled to 48 MHz for use by the digital system. A low power 32 kHz ILO (internal low speed oscillator) is provided for the Sleep timer and WDT. If crystal accuracy is desired, the ECO (32.768 kHz external crystal oscillator) is available for use as a Real Time Clock (RTC) and can optionally generate a crystal-accurate 24 MHz system clock using a PLL. The clocks, together with programmable clock dividers (as a System Resource), provide the flexibility to integrate almost any timing requirement into the PSoC device.

PSoC GPIOs provide connection to the CPU, digital and analog resources of the device. Each pin's drive mode may be selected from eight options, allowing great flexibility in external interfacing. Every pin also has the capability to generate a system interrupt on high level, low level, and change from last read.

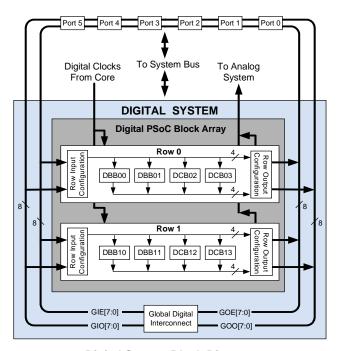

#### The Digital System

The Digital System is composed of 8 digital PSoC blocks. Each block is an 8-bit resource that can be used alone or combined with other blocks to form 8, 16, 24, and 32-bit peripherals, which are called user module references.

**Digital System Block Diagram**

Digital peripheral configurations include those listed below.

- PWMs (8 to 32 bit)

- PWMs with Dead band (8 to 32 bit)

- Counters (8 to 32 bit)

- Timers (8 to 32 bit)

- UART 8 bit with selectable parity (up to 2)

- SPI master and slave (up to 2)

- I2C slave and master (1 available as a System Resource)

- Cyclical Redundancy Checker/Generator (8 to 32 bit)

- IrDA (up to 2)

- Pseudo Random Sequence Generators (8 to 32 bit)

The digital blocks can be connected to any GPIO through a series of global buses that can route any signal to any pin. The buses also allow for signal multiplexing and for performing logic operations. This configurability frees your designs from the constraints of a fixed peripheral controller.

Digital blocks are provided in rows of four, where the number of blocks varies by PSoC device family. This allows you the optimum choice of system resources for your application. Family resources are shown in the table titled "PSoC Device Characteristics" on page 3.

#### The Analog System

The Analog System is composed of 12 configurable blocks, each comprised of an opamp circuit allowing the creation of complex analog signal flows. Analog peripherals are very flexible and can be customized to support specific application requirements. Some of the more common PSoC analog functions (most available as user modules) are listed below.

- Analog-to-digital converters (up to 4, with 6- to 14-bit resolution, selectable as Incremental, Delta Sigma, and SAR)

- Filters (2, 4, 6, and 8 pole band-pass, low-pass, and notch)

- Amplifiers (up to 4, with selectable gain to 48x)

- Instrumentation amplifiers (up to 2, with selectable gain to 93x)

- Comparators (up to 4, with 16 selectable thresholds)

- DACs (up to 4, with 6- to 9-bit resolution)

- Multiplying DACs (up to 4, with 6- to 9-bit resolution)

- High current output drivers (four with 30 mA drive as a Core Resource)

- 1.3V reference (as a System Resource)

- DTMF dialer

- Modulators

- Correlators

- Peak detectors

- Many other topologies possible

CY8C27x43 Final Data Sheet PSoC™ Overview

#### **Getting Started**

The quickest path to understanding the PSoC silicon is by reading this data sheet and using the PSoC Designer Integrated Development Environment (IDE). This data sheet is an overview of the PSoC integrated circuit and presents specific pin, register, and electrical specifications. For in-depth information, along with detailed programming information, reference the  $PSoC^{TM}$  Mixed Signal Array Technical Reference Manual.

For up-to-date Ordering, Packaging, and Electrical Specification information, reference the latest PSoC device data sheets on the web at http://www.cypress.com/psoc.

#### **Development Kits**

Development Kits are available from the following distributors: Digi-Key, Avnet, Arrow, and Future. The Cypress Online Store at <a href="http://www.onfulfillment.com/cypressstore/">http://www.onfulfillment.com/cypressstore/</a> contains development kits, C compilers, and all accessories for PSoC development. Click on *PSoC (Programmable System-on-Chip)* to view a current list of available items.

#### Tele-Training

Free PSoC "Tele-training" is available for beginners and taught by a live marketing or application engineer over the phone. Five training classes are available to accelerate the learning curve including introduction, designing, debugging, advanced design, advanced analog, as well as application-specific classes covering topics like PSoC and the LIN bus. For days and times of the tele-training, see <a href="http://www.cypress.com/support/training.cfm">http://www.cypress.com/support/training.cfm</a>.

#### Consultants

Certified PSoC Consultants offer everything from technical assistance to completed PSoC designs. To contact or become a PSoC Consultant, go to the following Cypress support web site: http://www.cypress.com/support/cypros.cfm.

#### **Technical Support**

PSoC application engineers take pride in fast and accurate response. They can be reached with a 4-hour guaranteed response at http://www.cypress.com/support/login.cfm.

#### Application Notes

A long list of application notes will assist you in every aspect of your design effort. To locate the PSoC application notes, go to http://www.cypress.com/design/results.cfm.

#### **Development Tools**

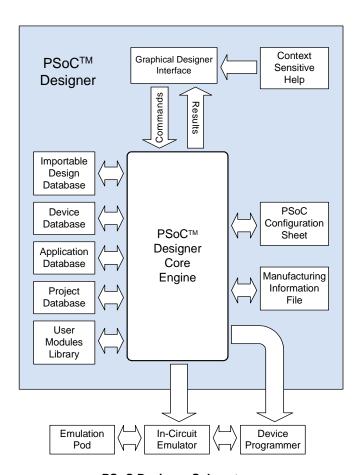

The Cypress MicroSystems PSoC Designer is a Microsoft® Windows-based, integrated development environment for the Programmable System-on-Chip (PSoC) devices. The PSoC Designer IDE and application runs on Windows NT 4.0, Windows 2000, Windows Millennium (Me), or Windows XP. (Reference the PSoC Designer Functional Flow diagram below.)

PSoC Designer helps the customer to select an operating configuration for the PSoC, write application code that uses the PSoC, and debug the application. This system provides design database management by project, an integrated debugger with In-Circuit Emulator, in-system programming support, and the CYASM macro assembler for the CPUs.

PSoC Designer also supports a high-level C language compiler developed specifically for the devices in the family.

**PSoC Designer Subsystems**

CY8C27x43 Final Data Sheet PSoC™ Overview

#### **PSoC Designer Software Subsystems**

#### Device Editor

The Device Editor subsystem allows the user to select different onboard analog and digital components called user modules using the PSoC blocks. Examples of user modules are ADCs, DACs, Amplifiers, and Filters.

The device editor also supports easy development of multiple configurations and dynamic reconfiguration. Dynamic configuration allows for changing configurations at run time.

PSoC Designer sets up power-on initialization tables for selected PSoC block configurations and creates source code for an application framework. The framework contains software to operate the selected components and, if the project uses more than one operating configuration, contains routines to switch between different sets of PSoC block configurations at run time. PSoC Designer can print out a configuration sheet for a given project configuration for use during application programming in conjunction with the Device Data Sheet. Once the framework is generated, the user can add application-specific code to flesh out the framework. It's also possible to change the selected components and regenerate the framework.

#### Design Browser

The Design Browser allows users to select and import preconfigured designs into the user's project. Users can easily browse a catalog of preconfigured designs to facilitate time-to-design. Examples provided in the tools include a 300-baud modem, LIN Bus master and slave, fan controller, and magnetic card reader.

#### Application Editor

In the Application Editor you can edit your C language and Assembly language source code. You can also assemble, compile, link, and build.

**Assembler.** The macro assembler allows the assembly code to be merged seamlessly with C code. The link libraries automatically use absolute addressing or can be compiled in relative mode, and linked with other software modules to get absolute addressing.

**C Language Compiler.** A C language compiler is available that supports Cypress MicroSystems' PSoC family devices. Even if you have never worked in the C language before, the product quickly allows you to create complete C programs for the PSoC family devices.

The embedded, optimizing C compiler provides all the features of C tailored to the PSoC architecture. It comes complete with embedded libraries providing port and bus operations, standard keypad and display support, and extended math functionality.

#### Debugger

The PSoC Designer Debugger subsystem provides hardware in-circuit emulation, allowing the designer to test the program in a physical system while providing an internal view of the PSoC device. Debugger commands allow the designer to read and program and read and write data memory, read and write IO registers, read and write CPU registers, set and clear breakpoints, and provide program run, halt, and step control. The debugger also allows the designer to create a trace buffer of registers and memory locations of interest.

#### Online Help System

The online help system displays online, context-sensitive help for the user. Designed for procedural and quick reference, each functional subsystem has its own context-sensitive help. This system also provides tutorials and links to FAQs and an Online Support Forum to aid the designer in getting started.

#### Hardware Tools

#### In-Circuit Emulator

A low cost, high functionality ICE (In-Circuit Emulator) is available for development support. This hardware has the capability to program single devices.

The emulator consists of a base unit that connects to the PC by way of the parallel or USB port. The base unit is universal and will operate with all PSoC devices. Emulation pods for each device family are available separately. The emulation pod takes the place of the PSoC device in the target board and performs full speed (24 MHz) operation.

#### **Document Conventions**

#### Acronyms Used

The following table lists the acronyms that are used in this document.

| Acronym | Description                                         |

|---------|-----------------------------------------------------|

| AC      | alternating current                                 |

| ADC     | analog-to-digital converter                         |

| API     | application programming interface                   |

| CPU     | central processing unit                             |

| CT      | continuous time                                     |

| DAC     | digital-to-analog converter                         |

| DC      | direct current                                      |

| ECO     | external crystal oscillator                         |

| EEPROM  | electrically erasable programmable read-only memory |

| FSR     | full scale range                                    |

| GPIO    | general purpose IO                                  |

| GUI     | graphical user interface                            |

| HBM     | human body model                                    |

| ICE     | in-circuit emulator                                 |

| ILO     | internal low speed oscillator                       |

| IMO     | internal main oscillator                            |

| Ю       | input/output                                        |

| IPOR    | imprecise power on reset                            |

| LSb     | least-significant bit                               |

| LVD     | low voltage detect                                  |

| MSb     | most-significant bit                                |

| PC      | program counter                                     |

| PLL     | phase-locked loop                                   |

| POR     | power on reset                                      |

| PPOR    | precision power on reset                            |

| PSoC™   | Programmable System-on-Chip™                        |

| PWM     | pulse width modulator                               |

| RAM     | random access memory                                |

| SC      | switched capacitor                                  |

| SLIMO   | slow IMO                                            |

| SMP     | switch mode pump                                    |

#### Units of Measure

A units of measure table is located in the Electrical Specifications section. Table 3-1 on page 17 lists all the abbreviations used to measure the PSoC devices.

#### **Numeric Naming**

Hexidecimal numbers are represented with all letters in uppercase with an appended lowercase 'h' (for example, '14h' or '3Ah'). Hexidecimal numbers may also be represented by a '0x' prefix, the C coding convention. Binary numbers have an appended lowercase 'b' (e.g., 01010100b' or '01000011b'). Numbers not indicated by an 'h' or 'b' are decimal.

#### **Table of Contents**

For an in depth discussion and more information on your PSoC device, obtain the *PSoC Mixed Signal Array Technical Reference Manual.* This document encompasses and is organized into the following chapters and sections.

| 1. | Pin  | Information                                                                         | 8  |

|----|------|-------------------------------------------------------------------------------------|----|

|    | 1.1  | Pinouts                                                                             | 8  |

|    |      | 1.1.1 8-Pin Part Pinout                                                             | 8  |

|    |      | 1.1.2 20-Pin Part Pinout                                                            | 9  |

|    |      | 1.1.3 28-Pin Part Pinout                                                            | 10 |

|    |      | 1.1.4 44-Pin Part Pinout                                                            |    |

|    |      | 1.1.5 48-Pin Part Pinouts                                                           | 12 |

| 2. | Reg  | ister Reference                                                                     | 14 |

|    | 2.1  | Register Conventions                                                                | 14 |

|    | 2.2  | Register Mapping Tables                                                             |    |

| 3. | Elec | etrical Specifications                                                              | 17 |

|    | 3.1  | Absolute Maximum Ratings                                                            | 18 |

|    | 3.2  | Operating Temperature                                                               |    |

|    | 3.3  | DC Electrical Characteristics                                                       |    |

|    | 0.0  | 3.3.1 DC Chip-Level Specifications                                                  |    |

|    |      | 3.3.2 DC General Purpose IO Specifications                                          |    |

|    |      | 3.3.3 DC Operational Amplifier Specifications                                       |    |

|    |      | 3.3.4 DC Analog Output Buffer Specifications                                        |    |

|    |      | 3.3.5 DC Switch Mode Pump Specifications                                            |    |

|    |      | 3.3.6 DC Analog Reference Specifications                                            |    |

|    |      | 3.3.7 DC Analog PSoC Block Specifications                                           |    |

|    |      | 3.3.8 DC POR and LVD Specifications                                                 |    |

|    | 0.4  | 3.3.9 DC Programming Specifications                                                 |    |

|    | 3.4  | AC Electrical Characteristics                                                       |    |

|    |      | 3.4.1 AC Chip-Level Specifications                                                  |    |

|    |      | 3.4.2 AC General Purpose IO Specifications                                          |    |

|    |      | 3.4.3 AC Operational Amplifier Specifications 3.4.4 AC Digital Block Specifications |    |

|    |      | 3.4.5 AC Analog Output Buffer Specifications                                        |    |

|    |      | 3.4.6 AC External Clock Specifications                                              |    |

|    |      | 3.4.7 AC Programming Specifications                                                 |    |

|    |      | 3.4.8 AC I2C Specifications                                                         |    |

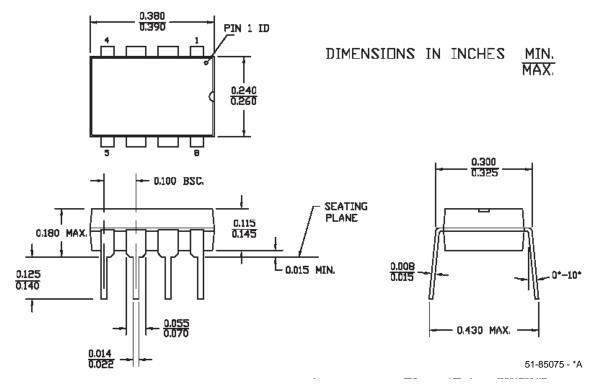

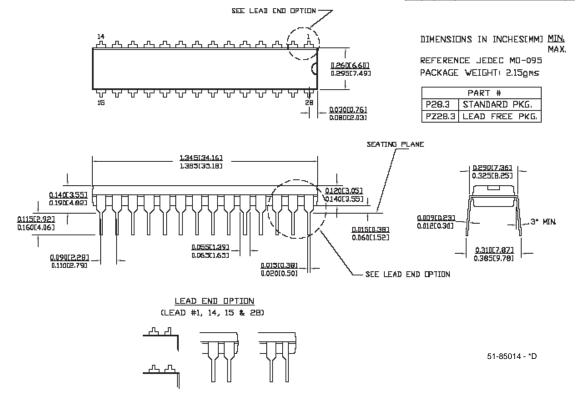

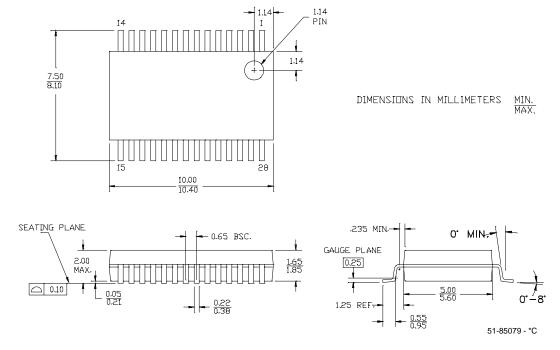

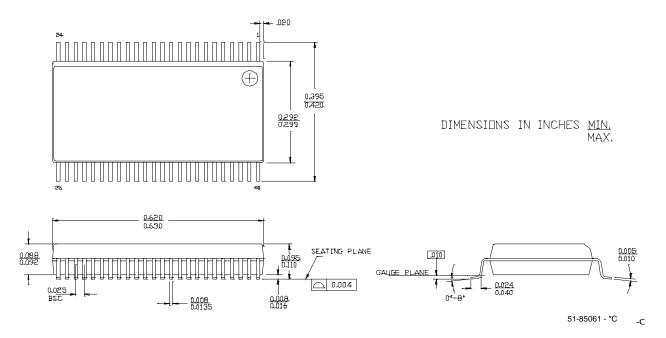

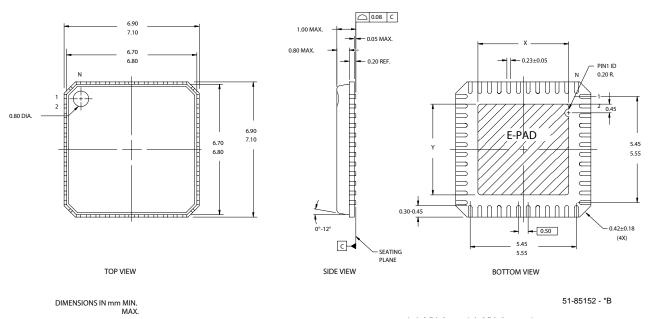

| 4. | Pac  | kaging Information                                                                  | 36 |

|    | 4.1  | Packaging Dimensions                                                                |    |

|    | 4.2  | Thermal Impedances                                                                  |    |

|    | 4.3  | Capacitance on Crystal Pins                                                         |    |

| 5. | Ord  | ering Information                                                                   | 42 |

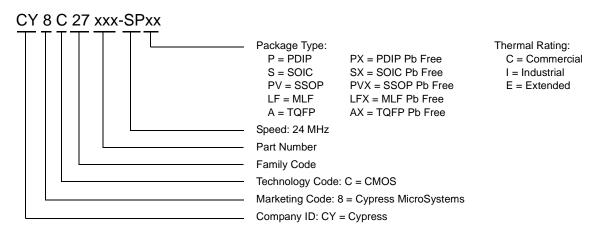

|    | 5.1  | Ordering Code Definitions                                                           |    |

| 6. | Sale | es and Service Information                                                          | 44 |

|    | 6.1  | Revision History                                                                    |    |

|    | -    | Copyrights and Code Protection                                                      |    |

CY8C27x43 Final Data Sheet 1. Pin Information

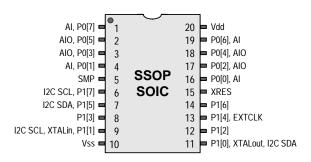

#### 1.1.2 20-Pin Part Pinout

Table 1-2. 20-Pin Part Pinout (SSOP, SOIC)

| Pin | Ту       | ре     | Pin   | Description                                                        |  |  |

|-----|----------|--------|-------|--------------------------------------------------------------------|--|--|

| No. | Digital  | Analog | Name  | Description                                                        |  |  |

| 1   | Ю        | ı      | P0[7] | Analog column mux input.                                           |  |  |

| 2   | 10       | 10     | P0[5] | Analog column mux input and column output.                         |  |  |

| 3   | Ю        | 10     | P0[3] | Analog column mux input and column output.                         |  |  |

| 4   | Ю        | I      | P0[1] | Analog column mux input.                                           |  |  |

| 5   | Po       | wer    | SMP   | Switch Mode Pump (SMP) connection to external components required. |  |  |

| 6   | Ю        |        | P1[7] | I2C Serial Clock (SCL)                                             |  |  |

| 7   | 10       |        | P1[5] | I2C Serial Data (SDA)                                              |  |  |

| 8   | Ю        |        | P1[3] |                                                                    |  |  |

| 9   | Ю        |        | P1[1] | Crystal Input (XTALin), I2C Serial Clock (SCL)                     |  |  |

| 10  | 10 Power |        | Vss   | Ground connection.                                                 |  |  |

| 11  | Ю        |        | P1[0] | Crystal Output (XTALout), I2C Serial Data (SDA)                    |  |  |

| 12  | Ю        |        | P1[2] |                                                                    |  |  |

| 13  | Ю        |        | P1[4] | Optional External Clock Input (EXTCLK)                             |  |  |

| 14  | Ю        |        | P1[6] |                                                                    |  |  |

| 15  | Inp      | out    | XRES  | Active high external reset with internal pull down.                |  |  |

| 16  | Ю        | I      | P0[0] | Analog column mux input.                                           |  |  |

| 17  | 10       | 10     | P0[2] | Analog column mux input and column outp                            |  |  |

| 18  | Ю        | Ю      | P0[4] | Analog column mux input and column output                          |  |  |

| 19  | Ю        | I      | P0[6] | Analog column mux input.                                           |  |  |

| 20  | Po       | wer    | Vdd   | Supply voltage.                                                    |  |  |

**LEGEND**: A = Analog, I = Input, and O = Output.

#### CY8C27243 20-Pin PSoC Device

CY8C27x43 Final Data Sheet 1. Pin Information

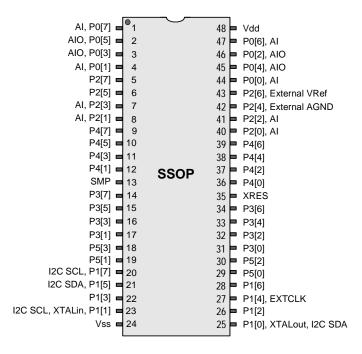

#### 1.1.5 48-Pin Part Pinouts

Table 1-5. 48-Pin Part Pinout (SSOP)

| No.         Digital Digital         Analog Polity         Polity Digital         Analog Polity         Analog column mux input.           1         10         10         10         POI;         Analog column mux input and column output.           3         10         10         POI;         Analog column mux input and column output.           4         10         1         POI;         Analog column mux input and column output.           6         10         P2I;         Analog column mux input.           6         10         P2I;         Analog column mux input.           7         10         1         P2I;         Analog column mux input.           8         10         1         P2I;         Description           8         10         1         P2I;         Description           10         1         P2I;         Description           11         10         1         P2I;         Description           12         10         1         P2I;         Description           13         10         P4I;         Description         Description           14         10         1         P2I;         Description         Description           15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |     |     |             |                                                |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-----|-------------|------------------------------------------------|--|--|--|--|

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pin<br>No. |     | 1   | Pin<br>Name | Description                                    |  |  |  |  |

| 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            | _   |     |             | Analog column mux input                        |  |  |  |  |

| 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |     |     |             |                                                |  |  |  |  |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |     |     |             |                                                |  |  |  |  |

| Section   P2 7    Section   P2 5    Section   P2 5    P3 5    P4 5 |            | _   | _   |             |                                                |  |  |  |  |

| 6         IO         P2[5]           7         IO         I         P2[3]         Direct switched capacitor block input.           8         IO         I         P2[1]         Direct switched capacitor block input.           9         IO         P4[7]         P4[7]           10         IO         P4[5]         P4[7]           11         IO         P4[3]         P4[1]           12         IO         P4[1]         P4[1]           13         Power         SMP         Switch Mode Pump (SMP) connection to external components required.           14         IO         P3[7]         P4[1]         P4[1]           15         IO         P3[5]         P4[7]         P4[7]           16         IO         P3[3]         P4[7]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |     |     |             | 7 titalog column max input.                    |  |  |  |  |

| 7         IO         I         P2[3]         Direct switched capacitor block input.           8         IO         I         P2[1]         Direct switched capacitor block input.           9         IO         P4[7]         P4[7]           10         IO         P4[7]         P4[7]           11         IO         P4[3]         P4[1]           12         IO         P4[1]         P4[1]           12         IO         P4[1]         P4[1]           13         Power         SMP         Switch Mode Pump (SMP) connection to external components required.           14         IO         P3[7]         P4[7]           15         IO         P3[3]         P4           16         IO         P3[3]         P4           17         IO         P3[1]         P4           18         IO         P5[3]         P4           19         IO         P5[1]         P4           20         IO         P1[5]         I2C Serial Clock (SCL)           21         IO         P1[6]         P4           22         IO         P1[7]         Crystal Input (XTALin), I2C Serial Data (SDA)           25         IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _          |     |     |             |                                                |  |  |  |  |

| 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |     | 1   |             | Direct switched capacitor block input          |  |  |  |  |

| 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |            |     |     |             | · · · · · · · · · · · · · · · · · · ·          |  |  |  |  |

| 10         IO         P4[5]           11         IO         P4[3]           12         IO         P4[1]           13         Power         SMP         Switch Mode Pump (SMP) connection to external components required.           14         IO         P3[7]         P3[7]           15         IO         P3[8]         P3[7]           16         IO         P3[8]         P3[8]           17         IO         P3[1]         P3[1]           18         IO         P5[3]         P4[7]           19         IO         P5[1]         P5[7]           20         IO         P1[7]         I2C Serial Clock (SCL)           21         IO         P1[8]         P1[8]         P1[8]           22         IO         P1[9]         Crystal Input (XTALin), I2C Serial Clock (SCL)           24         Power         Vss         Ground connection.           25         IO         P1[9]         Crystal Output (XTALin), I2C Serial Data (SDA)           26         IO         P1[9]         Crystal Output (XTALin), I2C Serial Data (SDA)           27         IO         P1[8]         Optional External Clock Input (EXTCLK)           28         IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _          |     |     |             | Birect switched capacitor block input.         |  |  |  |  |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |     |     |             |                                                |  |  |  |  |

| 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | _   |     |             |                                                |  |  |  |  |

| SMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |     |     |             |                                                |  |  |  |  |

| external components required.   14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |     | wer |             | Switch Mode Pump (SMP) connection to           |  |  |  |  |

| 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10         | 10  | WCI | Olvii       |                                                |  |  |  |  |

| 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14         | Ю   |     | P3[7]       |                                                |  |  |  |  |

| 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15         | 10  |     | P3[5]       |                                                |  |  |  |  |

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16         | Ю   |     | P3[3]       |                                                |  |  |  |  |

| 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17         | Ю   |     | P3[1]       |                                                |  |  |  |  |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18         | Ю   |     | P5[3]       |                                                |  |  |  |  |

| 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19         | Ю   |     | P5[1]       |                                                |  |  |  |  |

| 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 20         | Ю   |     | P1[7]       | I2C Serial Clock (SCL)                         |  |  |  |  |

| 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21         | Ю   |     | P1[5]       | I2C Serial Data (SDA)                          |  |  |  |  |

| Power   Vss   Ground connection.   P1[0]   Crystal Output (XTALout), I2C Serial Data (SDA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22         | Ю   |     | P1[3]       |                                                |  |  |  |  |