Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | FR81S                                                                           |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, CSIO, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 44                                                                              |

| Program Memory Size        | 320KB (320K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | 64K x 8                                                                         |

| RAM Size                   | 56K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 26x12b; D/A 1x8b                                                            |

| Oscillator Type            | External                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-LQFP                                                                         |

| Supplier Device Package    | 64-LQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb91f522bsbpmc1-gte1 |

|    |    | Pin   | no.   |     |     | Pin<br>Name           | Polarity | I/O<br>circuit | Function* <sup>9</sup>                         |

|----|----|-------|-------|-----|-----|-----------------------|----------|----------------|------------------------------------------------|

| 64 | 80 | 100   | 120   | 144 | 176 | Name                  |          | types*8        |                                                |

|    |    |       |       |     |     | P057                  | -        |                | General-purpose I/O port                       |

|    |    |       |       |     |     | RDY *2, *3,<br>*4, *5 | -        |                | External bus/Ready input (0)                   |

|    |    |       |       |     |     | SCK10_1               | -        |                | Multi-function serial ch.10 clock I/O (1)      |

| 19 | 24 | *4    | *4    |     |     | AN42                  | -        | _              | ADC analog 42 input                            |

| *1 | *1 | 29 *1 | 35 *1 | 41  | 51  | ICU8_0                | -        | G              | Input capture ch.8 input (0)                   |

|    |    |       |       |     |     | TRG0_2                | -        |                | PPG trigger 0 input (2)                        |

|    |    |       |       |     |     | PPG1_1                | -        |                | PPG ch.1 output (1)                            |

|    |    |       |       |     |     | ICU1_1                | -        |                | Input capture ch.1 input (1)                   |

|    |    |       |       |     |     | TIN6_1                | -        |                | Reload timer ch.6 event input (1)              |

|    |    |       |       |     |     | P142                  | -        |                | General-purpose I/O port                       |

|    |    |       |       |     |     | SCK10_0               |          |                | Multi-function serial ch.10 clock I/O (0)/     |

| -  | -  | -     | -     | 44  | 54  | /<br>SCL10            | -        | F              | I <sup>2</sup> C bus serial clock I/O          |

|    |    |       |       |     |     | PPG38_0               | -        |                | PPG ch.38 output (0)                           |

|    |    |       |       |     |     | TIN7_1                | -        |                | Reload timer ch.7 event input (1)              |

|    |    |       |       |     |     | P143                  | -        |                | General-purpose I/O port                       |

|    |    |       |       |     |     | SOT10_0               |          |                | Multi-function serial ch.10 serial data output |

| -  | -  | -     | -     | 45  | 55  | /SDA10                | -        | F              | (0)/ I <sup>2</sup> C bus serial data I/O      |

|    |    |       |       |     |     | PPG39_0               | -        |                | PPG ch.39 output (0)                           |

|    |    |       |       |     |     | TOT4_1                | -        |                | Reload timer ch.4 output (1)                   |

|    |    | _     |       | _   | 56  | P182                  | -        | Α              | General-purpose I/O port                       |

|    |    |       |       | _   | 30  | PPG42_0               | -        |                | PPG ch.42 output (0)                           |

|    |    |       |       |     |     | P060                  | -        |                | General-purpose I/O port                       |

|    |    |       |       |     |     | SCS10_0               | -        |                | Serial chip select 10 I/O (0)                  |

|    |    | 32    | 38    | 46  | 57  | PPG2_1                | -        | Α              | PPG ch.2 output (1)                            |

| -  | _  | 32    | 30    | 40  | 31  | ICU2_1                | -        | ^              | Input capture ch.2 input (1)                   |

|    |    |       |       |     |     | TOT5_1                | -        |                | Reload timer ch.5 output (1)                   |

|    |    |       |       |     |     | INT13_0               | -        |                | INT13 External interrupt input (0)             |

|    |    |       |       |     |     | P061                  | -        |                | General-purpose I/O port                       |

|    |    |       |       |     |     | SOT10 1               | _        |                | Multi-function serial ch.10                    |

|    |    |       |       |     |     | _                     |          |                | serial data output (1)                         |

|    |    |       |       |     |     | AN41                  | -        |                | ADC analog 41 input                            |

| 22 | 27 | 33    | 39    | 47  | 58  | ICU6_0                | -        | В              | Input capture ch.6 input (0)                   |

|    |    |       |       |     |     | PPG3_1                | -        |                | PPG ch.3 output (1)                            |

|    |    |       |       |     |     | ICU3_1                | -        |                | Input capture ch.3 input (1)                   |

|    |    |       |       |     |     | TOT6_1                | -        |                | Reload timer ch.6 output (1)                   |

|    |    |       |       |     |     | INT13_1               | -        |                | INT13 External interrupt input (1)             |

| A 1.1                                            |                              | Address offset value / Register name |                              |                               |                                |  |  |  |  |  |

|--------------------------------------------------|------------------------------|--------------------------------------|------------------------------|-------------------------------|--------------------------------|--|--|--|--|--|

| Address                                          | +0                           | +1                                   | +2                           | +3                            | Block                          |  |  |  |  |  |

| 0001F8 <sub>H</sub>                              | TMRLRAI<br>XXXXXXXX          | 6 [R/W] H<br>XXXXXXXX                | TMR6<br>XXXXXXXX             | [R] H<br>XXXXXXXX             | Dalaad Timaa C                 |  |  |  |  |  |

| 0001FC <sub>н</sub>                              | TMRLRB0<br>XXXXXXXX          | 6 [R/W] H<br>XXXXXXXX                | TMCSR6 [F<br>00000000        |                               | Reload Timer 6                 |  |  |  |  |  |

| 000200 <sub>H</sub><br>to<br>000238 <sub>H</sub> | _                            | _                                    | _                            | _                             | Reserved                       |  |  |  |  |  |

| 00023С <sub>н</sub>                              | DACR0 [R/W] B,H,W<br>0       | DADR0 [R/W] B,H,W<br>XXXXXXXX        | DACR1 [R/W] B,H,W            | DADR1 [R/W] B,H,W<br>XXXXXXXX | DA Converter                   |  |  |  |  |  |

| 000240 <sub>H</sub>                              |                              |                                      | [R/W] W<br>11111111 11111111 |                               |                                |  |  |  |  |  |

| 000244н                                          |                              | TCDT3<br>00000000 00000000           | [R/W] W<br>00000000 00000000 |                               | Free-run Timer 3<br>32-bit FRT |  |  |  |  |  |

| 000248н                                          | TCCSH3 [R/W]<br>B,H,W<br>000 | TCCSL3 [R/W]<br>B,H,W<br>-1-00000    | _                            | _                             | 32-DIL FR I                    |  |  |  |  |  |

| 00024Сн                                          |                              |                                      |                              |                               |                                |  |  |  |  |  |

| 000250н                                          |                              | TCDT4<br>00000000 00000000           | [R/W] W<br>00000000 00000000 |                               | Free-run Timer 4<br>32-bit FRT |  |  |  |  |  |

| 000254н                                          | TCCSH4 [R/W]<br>B,H,W<br>000 | TCCSL4 [R/W]<br>B,H,W<br>-1-00000    | _                            | _                             |                                |  |  |  |  |  |

| 000258 <sub>Н</sub><br>to<br>0002C0 <sub>Н</sub> | _                            | _                                    | _                            | _                             | Reserved                       |  |  |  |  |  |

| 0002C4 <sub>H</sub><br>to<br>0002FC <sub>H</sub> | _                            | _                                    | _                            | _                             | Reserved                       |  |  |  |  |  |

| 000300 <sub>H</sub><br>to<br>00030C <sub>H</sub> | _                            | _                                    | _                            | _                             | Reserved                       |  |  |  |  |  |

| 000310 <sub>H</sub>                              | _                            | _                                    | MPUCR<br>000000-0            |                               |                                |  |  |  |  |  |

| 000314 <sub>H</sub>                              | _                            | _                                    | _                            | _                             |                                |  |  |  |  |  |

| 000318 <sub>H</sub>                              |                              | MPU [S]                              |                              |                               |                                |  |  |  |  |  |

| 00031С <sub>н</sub>                              | _                            | (Only CPU core can access this area) |                              |                               |                                |  |  |  |  |  |

| 000320н                                          | XX                           |                                      | R [R] W<br>XXXXXXXX XXXXX    | XX                            | arou)                          |  |  |  |  |  |

| 000324н                                          | _                            | _                                    | DPVSR<br>0                   | = =                           |                                |  |  |  |  |  |

| Address             | +0            | +1                                                    | +2                             | +3                        | Block          |  |  |  |  |

|---------------------|---------------|-------------------------------------------------------|--------------------------------|---------------------------|----------------|--|--|--|--|

| 000С4С <sub>Н</sub> | DCCR5 IR/WI W |                                                       |                                |                           |                |  |  |  |  |

| 000С54 <sub>Н</sub> |               | DCSR5 [R/W] H DTCR5 [R/W] H 0000 000000000 0000000000 |                                |                           |                |  |  |  |  |

| 000С58 <sub>Н</sub> |               | DSAR5 [R/W] W  XXXXXXXX XXXXXXXX XXXXXXXXX            |                                |                           |                |  |  |  |  |

| 000С5С <sub>н</sub> | XX            | DDAR5<br>(XXXXXX XXXXXXX                              | 5 [R/W] W<br>X XXXXXXXX XXXX   | <b>KXXX</b>               |                |  |  |  |  |

| 000С60 <sub>Н</sub> |               |                                                       | 6 [R/W] W<br>00000000 0-000000 |                           |                |  |  |  |  |

| 000С64н             |               | 6 [R/W] H<br>000                                      |                                | 86 [R/W] H<br>00 00000000 |                |  |  |  |  |

| 000С68 <sub>Н</sub> | XX            | DSAR6<br>(XXXXXX XXXXXXX                              | S [R/W] W<br>X XXXXXXXX XXXX   | «xxx                      |                |  |  |  |  |

| 000С6Сн             | XX            | DDAR6<br>(XXXXXX XXXXXXX                              | S [R/W] W<br>X XXXXXXXX XXXX   | «xxx                      |                |  |  |  |  |

| 000С70 <sub>Н</sub> |               |                                                       | 7 [R/W] W<br>00000000 0-000000 |                           |                |  |  |  |  |

| 000С74 <sub>Н</sub> |               | [R/W] H<br>000                                        |                                | R7 [R/W] H<br>00 00000000 | DMA Controller |  |  |  |  |

| 000С78 <sub>Н</sub> | XX            | DSAR7<br>(XXXXXX XXXXXXX                              | ' [R/W] W<br>K XXXXXXXX XXXX   | «xxx                      | [S]            |  |  |  |  |

| 000С7Сн             | XX            | DDAR7<br>(XXXXXX XXXXXXX                              | ' [R/W] W<br>K XXXXXXXX XXXX   | «xxx                      |                |  |  |  |  |

| 000С80 <sub>н</sub> |               |                                                       | 3 [R/W] W<br>00000000 0-000000 |                           |                |  |  |  |  |

| 000С84н             |               | B [R/W] H<br>000                                      |                                | 88 [R/W] H<br>00 00000000 |                |  |  |  |  |

| 000С88 <sub>Н</sub> | XX            | DSAR8<br>XXXXXXX XXXXXXX                              | B [R/W] W<br>K XXXXXXXX XXXX   | «XXX                      |                |  |  |  |  |

| 000С8Сн             | XX            | DDAR8                                                 | B [R/W] W                      | xxxx                      |                |  |  |  |  |

| 000С90н             |               |                                                       | ) [R/W] W<br>00000000 0-000000 |                           |                |  |  |  |  |

| 000С94н             | DCSR9<br>0    |                                                       |                                |                           |                |  |  |  |  |

| 000С98н             | XX            | 0                                                     |                                |                           |                |  |  |  |  |

| 000С9Сн             | XX            | DDAR9                                                 | R/W] W<br>X XXXXXXXX XXXX      | ······                    |                |  |  |  |  |

| Address             |                                   | Address offset val                | ue / Register name                |                                 | Block             |

|---------------------|-----------------------------------|-----------------------------------|-----------------------------------|---------------------------------|-------------------|

| Address             | +0                                | +1                                | +2                                | +3                              | BIOCK             |

| 000E3C <sub>н</sub> | _                                 | _                                 | _                                 | _                               | Reserved          |

| 000Е40н             | PDDR00 [R] B,H,W<br>XXXXXXXX      | PDDR01 [R] B,H,W<br>XXXXXXXX      | PDDR02 [R] B,H,W<br>XXXXXXXX      | PDDR03 [R] B,H,W<br>XXXXXXXX    |                   |

| 000Е44 <sub>н</sub> | PDDR04 [R] B,H,W<br>XXXXXXXX      | PDDR05 [R] B,H,W<br>XXXXXXXX      | PDDR06 [R] B,H,W<br>XXXXXXXX      | PDDR07 [R] B,H,W<br>XXXXXXXX    |                   |

| 000E48 <sub>Н</sub> | PDDR08 [R] B,H,W<br>XXXXXXXX      | PDDR09 [R] B,H,W<br>XXXXXXXX      | PDDR10 [R] B,H,W<br>XXXXXXXX      | PDDR11 [R] B,H,W<br>XXXXXXXX    | Port Direct       |

| 000Е4Сн             | PDDR12 [R] B,H,W<br>XXXXXXXX      | PDDR13 [R] B,H,W<br>-XXXXXXX      | PDDR14 [R] B,H,W<br>XXX           | PDDR15 [R] B,H,W<br>XXXXXX      | Read Register     |

| 000E50 <sub>H</sub> | _                                 | _                                 | _                                 | _                               |                   |

| 000Е54 <sub>Н</sub> | _                                 | _                                 | _                                 | _                               |                   |

| 000E58 <sub>н</sub> | PDDR16 [R] B,H,W<br>XXXXXXXX      | PDDR17 [R] B,H,W<br>XXXXXXXX      | PDDR18 [R] B,H,W<br>XXXXXXXX      | PDDR19 [R] B,H,W<br>XXXXXXXX    |                   |

| 000Е5Сн             | _                                 | _                                 | _                                 | -                               | Reserved          |

| 000E60 <sub>н</sub> | EPFR00 [R/W]<br>B,H,W<br>00000000 | EPFR01 [R/W]<br>B,H,W<br>-0-0-000 | EPFR02 [R/W]<br>B,H,W<br>0000     | EPFR03 [R/W]<br>B,H,W<br>000-0  |                   |

| 000Е64н             | EPFR04 [R/W]<br>B,H,W<br>00-0     | EPFR05 [R/W]<br>B,H,W<br>0000     | EPFR06 [R/W]<br>B,H,W<br>000-     | EPFR07 [R/W]<br>B,H,W<br>00000  |                   |

| 000E68 <sub>H</sub> | EPFR08 [R/W]<br>B,H,W<br>00000    | EPFR09 [R/W]<br>B,H,W<br>00-      | EPFR10 [R/W]<br>B,H,W<br>0000     | EPFR11 [R/W]<br>B,H,W<br>0000   |                   |

| 000Е6Сн             | EPFR12 [R/W]<br>B,H,W<br>0000     | EPFR13 [R/W]<br>B,H,W<br>00       | EPFR14 [R/W]<br>B,H,W<br>00       | EPFR15 [R/W]<br>B,H,W<br>000    |                   |

| 000Е70 <sub>н</sub> | _                                 | _                                 | _                                 | _                               |                   |

| 000E74 <sub>H</sub> | _                                 | _                                 | _                                 | _                               |                   |

| 000E78 <sub>H</sub> | _                                 | _                                 | EPFR26 [R/W]<br>B,H,W<br>00000000 | EPFR27 [R/W]<br>B,H,W<br>0      | Extended Port     |

| 000Е7С <sub>н</sub> | EPFR28 [R/W]<br>B,H,W<br>000-0-   | EPFR29 [R/W]<br>B,H,W<br>00000000 | _                                 | _                               | Function Register |

| 000Е80н             | _                                 | EPFR33 [R/W]<br>B,H,W<br>00-      | EPFR34 [R/W]<br>B,H,W<br>00-      | EPFR35 [R/W]<br>B,H,W<br>00000  |                   |

| 000Е84н             | EPFR36 [R/W]<br>B,H,W<br>000-     | _                                 | _                                 | _                               |                   |

| 000E88 <sub>H</sub> | _                                 | _                                 | EPFR42 [R/W]<br>B,H,W<br>00       | EPFR43 [R/W]<br>B,H,W<br>00000- |                   |

| 000Е8Сн             | EPFR44 [R/W]<br>B,H,W<br>-000-    | EPFR45 [R/W]<br>B,H,W<br>-0000000 | _                                 | _                               |                   |

| 000E90 <sub>н</sub> | _                                 | _                                 | _                                 | _                               |                   |

| Address             | +0                                                            | +1          | +2                                   | +3                                  | Block |  |

|---------------------|---------------------------------------------------------------|-------------|--------------------------------------|-------------------------------------|-------|--|

| 001AD0 <sub>H</sub> | PCN6 [R/W<br>00000000 0                                       | •           |                                      | S [W] H,W<br>X XXXXXXX              |       |  |

| 001AD4 <sub>Н</sub> | PDUT6 [M<br>XXXXXXXX X                                        | -           |                                      | 6 [R] H,W<br>1 11111111             |       |  |

| 001AD8 <sub>н</sub> | PCN206 [R/W] B,H,W PSDR6 [R/W] H,W000000110 00000000 00000000 |             | PPG6                                 |                                     |       |  |

| 001ADC <sub>н</sub> | PTPC6 [R/\<br>00000000 00                                     | -           | -                                    | _                                   |       |  |

| 001AE0 <sub>н</sub> | PCN7 [R/W<br>00000000 0                                       | _           |                                      | 7 [W] H,W<br>X XXXXXXX              |       |  |

| 001AE4 <sub>н</sub> | PDUT7 [M<br>XXXXXXXX X                                        |             |                                      | 7 [R] H,W<br>1 11111111             | PPG7  |  |

| 001AE8 <sub>н</sub> | PCN207 [R/V<br>000000 -                                       | - · · · · · |                                      | [R/W] H,W<br>0 00000000             |       |  |

| 001AEC <sub>н</sub> | PTPC7 [R/\<br>00000000 00                                     | -           | 1                                    | _                                   |       |  |

| 001AF0 <sub>н</sub> | PCN8 [R/W<br>00000000 0                                       | •           |                                      | B [W] H,W<br>X XXXXXXX              |       |  |

| 001AF4 <sub>н</sub> | MJ 8TUDA<br>XXXXXXXX                                          | -           | PTMR:<br>1111111                     | PPG8                                |       |  |

| 001AF8 <sub>н</sub> | PCN208 [R/V<br>000000 -                                       | - · · · · · | PSDR8 [R/W] H,W<br>00000000 00000000 |                                     |       |  |

| 001AFC <sub>н</sub> | PTPC8 [R/\<br>00000000 00                                     | -           | _                                    | _                                   |       |  |

| 001В00н             | PCN9 [R/W<br>00000000 0                                       |             |                                      | P [W] H,W<br>X XXXXXXX              |       |  |

| 001B04 <sub>Н</sub> | NJ etudq<br>XXXXXXXX                                          | <u> </u>    |                                      | PTMR9 [R] H,W<br>11111111 11111111  |       |  |

| 001B08 <sub>Н</sub> | PCN209 [R/V<br>000000 -                                       | 110         |                                      | [R/W] H,W<br>0 00000000             | PPG9  |  |

| 001B0С <sub>н</sub> | PTPC9 [R/\<br>00000000 00                                     | 000000      | _                                    | _                                   |       |  |

| 001B10 <sub>H</sub> | PCN10 [R/W<br>00000000 0                                      | •           |                                      | 0 [W] H,W<br>X XXXXXXX              | PPG10 |  |

| 001В14 <sub>Н</sub> | PDUT10 [V<br>XXXXXXXX X                                       | <u>-</u>    |                                      | PTMR10 [R] H,W<br>11111111 11111111 |       |  |

| 001В18 <sub>Н</sub> | PCN210 [R/V<br>000000 -                                       | -           |                                      | [R/W] H,W<br>0 00000000             | DDC40 |  |

| 001B1C <sub>н</sub> | PTPC10 [R/<br>00000000 00                                     |             | _                                    | _                                   | PPG10 |  |

| 001В20 <sub>Н</sub> | PCN11 [R/W<br>00000000 0                                      | -           |                                      | 1 [W] H,W<br>X XXXXXXX              | PPG11 |  |

|                                                  |                               | Disale                       |                               |                               |                    |

|--------------------------------------------------|-------------------------------|------------------------------|-------------------------------|-------------------------------|--------------------|

| Address -                                        | +0                            | +1                           | +2                            | +3                            | Block              |

| 003030 <sub>н</sub>                              |                               |                              | [R] B,H,W<br>000 00000000     |                               |                    |

| 003034н                                          |                               |                              | [R] B,H,W<br>000 00000000     |                               | RAM/ diagnosis     |

| 003038н                                          |                               |                              | Backup RAM                    |                               |                    |

| 00303Сн                                          | TAEARA[R<br>111 f             | X/W] B,H,W<br>11111111       | R/W] B,H,W<br>00000000        |                               |                    |

| 003040 <sub>н</sub>                              | TFECRA [R/W]<br>B,H,W<br>0000 | TICRA [R/W]<br>B,H,W<br>0000 | _                             | /W] B,H,W<br>00001100         | RAM/ diagnosis     |

| 003044н                                          | TSRCRA [R/W]<br>B,H,W<br>0    | _                            | _                             | TKCCRA [R/W]<br>B,H,W<br>0000 | Backup RAM         |

| 003048 <sub>H</sub><br>to<br>0030FC <sub>H</sub> |                               | -                            | _                             |                               | Reserved           |

| 003100 <sub>H</sub>                              | BUSDIGSR<br>0000000           |                              |                               |                               |                    |

| 003104 <sub>н</sub>                              | BUSDIGSR<br>0000000           | 2[R/W] H,W<br>0 000          |                               | 0[R/W] H,W<br>00000000        |                    |

| 003108 <sub>H</sub>                              |                               |                              | R0 [R] W<br>00000000 00000000 |                               |                    |

| 00310С <sub>н</sub>                              |                               |                              | R1 [R] W<br>00000000 00000000 |                               |                    |

| 003110 <sub>н</sub>                              |                               |                              | R2 [R] W<br>00000000 00000000 |                               |                    |

| 003114 <sub>H</sub>                              | _                             | _                            |                               | 3[R/W] H,W<br>0 000           | BUS diagnosis      |

| 003118 <sub>H</sub>                              | BUSDIGSR<br>0000000           | 4[R/W] H,W<br>0 000          |                               | 1[R/W] H,W<br>00000000        |                    |

| 00311С <sub>н</sub>                              | _                             | _                            | _                             | _                             |                    |

| 003120 <sub>н</sub>                              |                               |                              | R3 [R] W<br>00000000 00000000 |                               |                    |

| 003124 <sub>H</sub>                              |                               |                              |                               |                               |                    |

| 003128 <sub>Н</sub><br>to<br>003FFC <sub>Н</sub> |                               | Reserved                     |                               |                               |                    |

| 004000 <sub>H</sub><br>to<br>005FFC <sub>H</sub> |                               | Backu                        | p-RAM                         |                               | Backup RAM<br>area |

## 10. Interrupt Vector Table

This list shows the assignments of interrupt factors and interrupt vectors/interrupt control registers.

# Interrupt vector 64 pins

| Indown up 4 for 4 or                                       | Interrupt |                 | Interrupt            | Offerst          | Default               | DN               |

|------------------------------------------------------------|-----------|-----------------|----------------------|------------------|-----------------------|------------------|

| Interrupt factor                                           | Decimal   | Hexa<br>decimal | level                | Offset           | address for<br>TBR    | RN               |

| Reset                                                      | 0         | 0               | -                    | 3FC <sub>H</sub> | 000FFFFC <sub>H</sub> | -                |

| System reserved                                            | 1         | 1               | -                    | 3F8 <sub>H</sub> | 000FFFF8 <sub>H</sub> | -                |

| System reserved                                            | 2         | 2               | -                    | 3F4 <sub>H</sub> | 000FFFF4 <sub>H</sub> | -                |

| System reserved                                            | 3         | 3               | -                    | 3F0 <sub>H</sub> | 000FFFF0 <sub>H</sub> | -                |

| System reserved                                            | 4         | 4               | -                    | 3EC <sub>H</sub> | 000FFFEC <sub>H</sub> | -                |

| FPU exception                                              | 5         | 5               | -                    | 3E8 <sub>H</sub> | 000FFFE8 <sub>H</sub> | -                |

| Exception of instruction access protection violation       | 6         | 6               | -                    | 3E4 <sub>H</sub> | 000FFFE4 <sub>H</sub> | -                |

| Exception of data access protection violation              | 7         | 7               | -                    | 3E0 <sub>H</sub> | 000FFFE0 <sub>H</sub> | -                |

| Data access error interrupt                                | 8         | 8               | -                    | 3DC <sub>H</sub> | 000FFFDC <sub>H</sub> | -                |

| INTE instruction                                           | 9         | 9               | -                    | 3D8 <sub>H</sub> | 000FFFD8 <sub>H</sub> | -                |

| Instruction break                                          | 10        | 0A              | -                    | 3D4 <sub>H</sub> | 000FFFD4 <sub>H</sub> | -                |

| System reserved                                            | 11        | 0B              | -                    | 3D0 <sub>H</sub> | 000FFFD0 <sub>H</sub> | -                |

| System reserved                                            | 12        | 0C              | -                    | 3ССн             | 000FFFCC <sub>H</sub> | -                |

| System reserved                                            | 13        | 0D              | -                    | 3C8 <sub>H</sub> | 000FFFC8 <sub>H</sub> | -                |

| Exception of invalid instruction                           | 14        | 0E              |                      | 3C4 <sub>H</sub> | 000FFFC4 <sub>H</sub> | -                |

| NMI request                                                |           |                 |                      |                  |                       |                  |

| Error generation during internal bus diagnosis             |           |                 |                      |                  |                       |                  |

| XBS RAM double-bit error generation                        | 15        | 0F              | 15 (F <sub>H</sub> ) | 3C0 <sub>н</sub> | 000FFFC0 <sub>н</sub> | _                |

| Backup RAM double-bit error generation                     |           |                 | Fixed                |                  |                       |                  |

| TPU violation                                              |           |                 |                      |                  |                       |                  |

| External interrupt 0-7                                     | 16        | 10              | ICR00                | 3ВСн             | 000FFFBC <sub>H</sub> | 0                |

| External interrupt 8-15                                    |           |                 |                      |                  |                       | 7                |

| External low-voltage detection interrupt                   | 17        | 11              | ICR01                | 3B8 <sub>H</sub> | 000FFFB8 <sub>н</sub> | 1* <sup>7</sup>  |

| Reload timer 0/1/4/5                                       | 18        | 12              | ICR02                | 3B4 <sub>H</sub> | 000FFFB4 <sub>н</sub> | 2* <sup>2</sup>  |

| Reload timer 3/6/7                                         | 19        | 13              | ICR03                | 3B0 <sub>H</sub> | 000FFFB0 <sub>H</sub> | 3* <sup>2</sup>  |

| Multi-function serial interface ch.0 (reception            |           |                 |                      | 02011            | 0002011               |                  |

| completed)                                                 | 20        | 14              | ICR04                | 3AC <sub>H</sub> | 000FFFAC <sub>H</sub> | 4* <sup>1</sup>  |

| Multi-function serial interface ch <sub>.</sub> 0 (status) |           |                 |                      | 0.1011           |                       | -                |

| Multi-function serial interface                            |           |                 |                      |                  |                       | 1                |

| ch 0 (transmission completed)                              | 21        | 15              | ICR05                | 3A8 <sub>H</sub> | 000FFFA8 <sub>H</sub> | 5* <sup>1</sup>  |

| -                                                          | 22        | 16              | ICR06                | 3A4 <sub>H</sub> | 000FFFA4 <sub>H</sub> | _* <sup>6</sup>  |

| -                                                          | 23        | 17              | ICR07                | 3A0 <sub>H</sub> | 000FFFA0 <sub>H</sub> | _*6              |

| _                                                          | 24        | 18              | ICR08                | 39C <sub>H</sub> | 000FFF9C <sub>H</sub> | _*6              |

| _                                                          | 25        | 19              | ICR09                | 398 <sub>H</sub> | 000FFF98 <sub>H</sub> | _*6              |

| Multi-function serial interface                            |           |                 | 10.100               | 330n             | 30000                 |                  |

| ch,3 (reception completed)                                 |           |                 |                      |                  |                       | 4                |

| Multi-function serial interface                            | 26        | 1A              | ICR10                | 394н             | 000FFF94 <sub>н</sub> | 10* <sup>1</sup> |

| ch,3 (status)                                              |           |                 |                      |                  |                       |                  |

| Multi-function serial interface                            |           |                 |                      |                  |                       |                  |

| ch 3 (transmission completed)                              | 27        | 1B              | ICR11                | 390н             | 000FFF90 <sub>н</sub> | 11               |

| Oscillation clock           | Oscillation clock frequency vs. Internal operation clock frequency |                                    |                                  |      |       |           |                       |       |       |

|-----------------------------|--------------------------------------------------------------------|------------------------------------|----------------------------------|------|-------|-----------|-----------------------|-------|-------|

|                             |                                                                    | Internal operation clock frequency |                                  |      |       |           |                       |       |       |

|                             |                                                                    |                                    |                                  |      |       | PLL clock |                       |       |       |

|                             |                                                                    | Main Clock                         | Multiplied Multiplied Multiplied |      |       |           | Multiplied Multiplied |       |       |

|                             |                                                                    |                                    | by 1                             | by 2 | by 3  | by 4      |                       | by 19 | by 20 |

| Oscillation clock frequency | 4MHz                                                               | 2MHz                               | 4MHz                             | 8MHz | 12MHz | 16MHz     |                       | 76MHz | 80MHz |

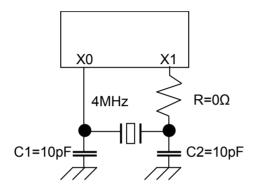

#### · Example of oscillation circuit

**Note:** As to the product with its clock supervisor's initial value is "ON", when the oscillator is unable to start within 20ms from the stop state the clock supervisor will detect the oscillation stop. As a result, the CPU moves to the fail safe operation.

Design your print circuit board so that the oscillator can start oscillation within 20ms. Moreover, it is recommended to be designed after the match evaluation of the circuit is requested to the departure pendulum maker when the oscillation circuit is composed.

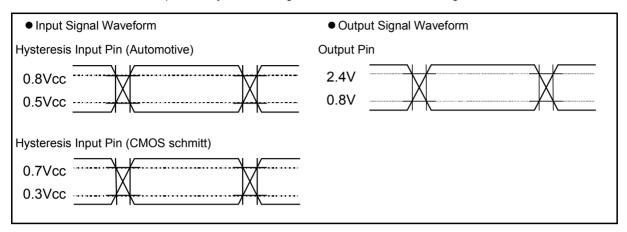

AC characteristics are specified by the following measurement reference voltage values.

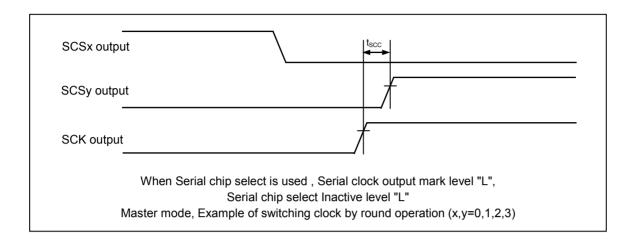

(4-1-5) Bit setting: SMR:MD2=0, SMR:MD1=1, SMR:MD0=0,

When Serial chip select is used: SCSCR:CSEN=1,

Serial clock output mark level "H": SMR,SCSFR:SCINV=0, Serial chip select Inactive level "H": SCSCR,SCSFR:CSLVL=1

(T<sub>A</sub>:-40°C to +125°C, V<sub>CC</sub>=AV<sub>CC</sub>=5.0V±10%/V<sub>CC</sub>=AV<sub>CC</sub>=3.3V±0.3V, V<sub>SS</sub>=AV<sub>SS</sub>=0.0V)

| Parameter               | Symbol | Pin name                                                                                                              | Conditions |                        | lue                     | Unit  | Remarks                                                              |

|-------------------------|--------|-----------------------------------------------------------------------------------------------------------------------|------------|------------------------|-------------------------|-------|----------------------------------------------------------------------|

| Parameter               | Symbol | Pili liaille                                                                                                          | Conditions | Min                    | Max                     | Ullit | Remarks                                                              |

| SCS↓→SCK↓<br>setup time | tcssı  | SCK1, SCK2,<br>SCK5 to SCK11<br>SCS1, SCS2,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11 |            | t <sub>cssu</sub> -50  | t <sub>CSSU</sub> +0 *1 | ns    |                                                                      |

|                         |        | SCK3, SCK4<br>SCS3,<br>SCS40 to SCS43                                                                                 |            | t <sub>CSSU</sub> -50  | t <sub>CSSU</sub> +300  | ns    |                                                                      |

| SCK↑→SCS↑<br>hold time  | tсsні  | SCK1, SCK2,<br>SCK5 to SCK11<br>SCS1, SCS2,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11 | -          | t <sub>CSHD</sub> -10  | t <sub>CSHD</sub> +50   | ns    | Internal shift<br>clock mode<br>output pin :<br>C <sub>L</sub> =50pF |

|                         |        | SCK3, SCK4<br>SCS3,<br>SCS40 to SCS43                                                                                 |            | t <sub>CSHD</sub> -300 | t <sub>CSHD</sub> +50   | ns    |                                                                      |

| SCS<br>deselect time    | tcsdi  | SCS1 to SCS3,<br>SCS40 to SCS43,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11            |            | tcsps-50               | tcsps+50                | ns    |                                                                      |

|                                   |                   | B:                                                                                                                          | 0 1111     | Val                    | ue                    |      | D                                                          |

|-----------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------|------------|------------------------|-----------------------|------|------------------------------------------------------------|

| Parameter                         | Symbol            | Pin name                                                                                                                    | Conditions | Min                    | Max                   | Unit | Remarks                                                    |

| SCS↓→SCK↑<br>setup time           | t <sub>CSSE</sub> | SCK1 to SCK11<br>SCS1 to SCS3,<br>SCS40 to SCS43,                                                                           |            | 3t <sub>CPP</sub> +30  | -                     | ns   |                                                            |

| SCK↓→SCS↑<br>hold time            | t <sub>CSHE</sub> | SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11                                                      |            | +0                     | -                     | ns   |                                                            |

| SCS<br>deselect time              | tcsde             | SCS1 to SCS3,<br>SCS40 to SCS43,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11                  | -          | 3t <sub>CPP</sub> +30  | -                     | ns   | External shift clock mode output pin:                      |

| SCS↓→SOT<br>delay time            | t <sub>DSE</sub>  | SCS1, SCS2,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11<br>SOT1, SOT2,<br>SOT5 to SOT11       |            | -                      | 40                    | ns   | C∟=50pF                                                    |

|                                   |                   | SCS3,<br>SCS40 to SCS43<br>SOT3 , SOT4                                                                                      |            | -                      | 300                   | ns   |                                                            |

| SCS↑→SOT<br>delay time            | t <sub>DEE</sub>  | SCS1 to SCS3,<br>SCS40 to SCS43,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11<br>SOT1 to SOT11 | -          | +0                     | -                     | ns   | External shift clock mode output pin: C <sub>L</sub> =50pF |

| SCK↑→SCS↓<br>clock switch<br>time | tscc              | SCK1, SCK2,<br>SCK5 to SCK11<br>SCS1, SCS2,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11       | -          | 3t <sub>CPP</sub> -10  | 3t <sub>CPP</sub> +50 | ns   | Internal shift clock mode Round operation output pin:      |

|                                   |                   | SCK3 , SCK4<br>SCS3 ,<br>SCS40 to SCS43                                                                                     |            | 3t <sub>CPP</sub> -300 | 3t <sub>CPP</sub> +50 | ns   | C <sub>L</sub> =50pF                                       |

<sup>\*1:</sup> t<sub>CSSU</sub> =SCSTR:CSSU7-0×Serial chip select timing operating clock

Please see the hardware manual for details of above-mentioned \*1,\*2, and \*3

<sup>\*2:</sup> t<sub>CSHD</sub>=SCSTR:CSHD7-0×Serial chip select timing operating clock

<sup>\*3:</sup> t<sub>CSDS</sub>=SCSTR:CSDS15-0×Serial chip select timing operating clock

Regardless of the deselect time setting, once after the serial chip select pin becomes inactive, it will take

at least five peripheral bus clock cycles to be active again

| Damanastan                        | 0                 | Dia                                                                                                                          | 0          | Val                       | lue                       | 11   | t Remarks                                                  |

|-----------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------|---------------------------|------|------------------------------------------------------------|

| Parameter                         | Symbol            | Pin name                                                                                                                     | Conditions | Min                       | Max                       | Unit | Remarks                                                    |

| SCS↑→SCK↓ setup time              | t <sub>CSSE</sub> | SCK1 to SCK11<br>SCS1 to SCS3,<br>SCS40 to SCS43,                                                                            |            | 3t <sub>CPP</sub> +3      | -                         | ns   |                                                            |

| SCK↑→SCS↓<br>hold time            | t <sub>CSHE</sub> | SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11                                                       |            | +0                        | -                         | ns   |                                                            |

| SCS<br>deselect time              | tcsde             | SCS1 to SCS3,<br>SCS40 to SCS43,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11                   | -          | 3t <sub>CPP</sub> +3<br>0 | -                         | ns   | External shift<br>clock mode<br>output pin:                |

| SCS↑→SOT<br>delay time            | t <sub>DSE</sub>  | SCS1 , SCS2,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11<br>SOT1 , SOT2,<br>SOT5 to SOT11      |            | -                         | 40                        | ns   | C <sub>L</sub> =50pF                                       |

|                                   |                   | SCS3 ,<br>SCS40 to SCS43<br>SOT3 , SOT4                                                                                      |            | -                         | 300                       | ns   |                                                            |

| SCS↓→SOT<br>delay time            | t <sub>DEE</sub>  | SCS1 to ~SCS3,<br>SCS40 to SCS43,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11<br>SOT1 to SOT11 | -          | +0                        | -                         | ns   | External shift clock mode output pin: C <sub>L</sub> =50pF |

| SCK↓→SCS↑<br>clock switch<br>time | tscc              | SCK1 , SCK2,<br>SCK5 to SCK11<br>SCS1 , SCS2,<br>SCS50 to SCS53,<br>SCS60 to SCS63,<br>SCS70 to SCS73,<br>SCS8 to SCS11      | -          | 3t <sub>CPP</sub> -10     | 3t <sub>CPP</sub> +5<br>0 | ns   | Internal shift clock mode Round operation output pin:      |

|                                   |                   | SCK3, SCK4<br>SCS3,<br>SCS40 to SCS43                                                                                        |            | 3t <sub>CPP</sub> -30     | 3t <sub>CPP</sub> +5<br>0 | ns   | CL=50PF                                                    |

<sup>\*1:</sup> t<sub>CSSU</sub> =SCSTR:CSSU7-0×Serial chip select timing operating clock

Please see the hardware manual for details of above-mentioned \*1,\*2, and \*3.

<sup>\*2:</sup>  $t_{\text{CSHD}}$ =SCSTR:CSHD7-0×Serial chip select timing operating clock

<sup>\*3:</sup> t<sub>CSDS</sub>=SCSTR:CSDS15-0×Serial chip select timing operating clock Regardless of the deselect time setting, once after the serial chip select pin becomes inactive, it will take at least five peripheral bus clock cycles to be active again

| Desa          | Saction.                                                                                        | Change Passille                                                                                                                                                                                                                                                                    |

|---------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page          | Section                                                                                         | Change Results                                                                                                                                                                                                                                                                     |

| 184           | ■ELECTRICAL CHARACTERISTICS 5.A/D Converter (1) 12-bit A/D Converter Electrical Characteristics | Added the following description.  Parameter: Power supply current I <sub>A</sub> AVCC*3  *3: The power supply current described only current value on A/D converter. The total AVcc current value must be calculated the power supply current for A/D converter and D/A converter. |

| 188           | ■ELECTRICAL CHARACTERISTICS 7.D/A Converter                                                     | Added the following description.  Parameter: Power supply current *1  *1: The power supply current described only current value on D/A converter. The total Avcc current value must be calculated the power supply current for D/A converter and A/D converter.                    |

| 187           | ■ELECTRICAL CHARACTERISTICS<br>6.Flash memory                                                   | Parameter: Erase cycle*2/Data retain time Deleted the following description. Remarks: "Temperature at writing/erasing Tj<+105°C"                                                                                                                                                   |

| 188           | ■ELECTRICAL CHARACTERISTICS 7.D/A Converter                                                     | Corrected the following description.  Parameter: Power supply current  Symbol IA Pin name AV <sub>CC</sub> Symbol IAH Pin name AV <sub>CC</sub> Symbol IA Pin name AVCC  Symbol IAH Pin name AVCC                                                                                  |

| 190           | ■EXAMPLE CHARACTERISTICS                                                                        | Corrected the following description.  Watch mode                                                                                                                                                                                                                                   |

| 192           | ■ORDERING INFORMATION                                                                           | Corrected the following description.  ORDERING INFORMATION  ORDERING INFORMATION MB91F52xxxB*1  Package  Package*2                                                                                                                                                                 |

| 198           | ■ORDERING INFORMATION                                                                           | Added the following description.  *1: It is only supported for customers who have already adopted it now. We do not recommend adopting new products.                                                                                                                               |

| 198           | ■ORDERING INFORMATION                                                                           | Corrected the following description. For details of the package, see " PACKAGE DIMENSIONS ".  *2: For details of the package, see " PACKAGE DIMENSIONS ".                                                                                                                          |

| 199 to<br>205 | ■ORDERING INFORMATION                                                                           | Added the following description.  ■ORDERING INFORMATION MB91F52xxxC                                                                                                                                                                                                                |

| -             | -                                                                                               | Company name and layout design change                                                                                                                                                                                                                                              |

| Page     | Section                   | Change Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|----------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 15       | ■Pin Assignment MB91F52xF | 100 VCC   99 PULL/WOT/SOTZ_I/IIOAN_0_0/INT3_1   98 PO06/SCS2_0/ADTGi_I/INT7_1   98 PO06/SCS2_0/ADTGi_I/INT7_1   96 PO03/SINZ_0/ITOBI_I/INT3_0   95 PO01/SOTI_0/ITOBI_I/INT3_0   95 PO01/SOTI_0/ITOBI_I/INT2_0   95 PO01/SOT |  |  |  |  |  |

|          |                           | 100 VCC   99   900(SCS_0/ADTG]_INT7_1   98   900(SCS_0/ADTG]_INT7_1   96   900(SCK_2_0/ADTG]_INT7_1   96   900(SCK_2_0/ADTG]_INT7_1   96   900(SCK_2_0/ADTG]_INT7_1   96   900(SCK_1_0/TOB]_INT7_0   93   C   92   VSS   91   91   94   900(SCK_1_0)   91   91   94   92   VSS   91   91   91   91   91   91   91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 15       | ■Pin Assignment MB91F52xF | The following note added on the bottom left of Figure.  * In a single clock product, pin 86 and pin 87 are the general-purpose ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 16       | ■Pin Assignment MB91F52xJ | The following note added on the bottom left of Figure.  * In a single clock product, pin 102 and pin 103 are the general-purpose ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 17       | ■Pin Assignment MB91F52xK | The following note added on the bottom left of Figure.  * In a single clock product, pin 121 and pin 122 are the general-purpose ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 18       | ■Pin Assignment MB91F52xL | The following note added on the bottom left of Figure.  * In a single clock product, pin 149 and pin 150 are the general-purpose ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 19 to 35 | ■PIN Description          | A List of "Pin Description" modified.  I/O Circuit Function*2 types*1  I/O Circuit Function*9 types*8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Page   | Section          | Change Results        |                  |                  |                                  |     |     |                        |

|--------|------------------|-----------------------|------------------|------------------|----------------------------------|-----|-----|------------------------|

|        |                  | (Continued) (Correct) |                  |                  |                                  |     |     |                        |

|        |                  | (33113                | ,                | Pin              | no.                              |     |     | Pin                    |

|        |                  | 64                    | 80               | 100              | 120                              | 144 | 176 | Name                   |

|        |                  |                       |                  |                  |                                  |     |     | P175                   |

|        |                  | -                     | -                | -                | -                                | -   | 28  | TRG9_1                 |

|        |                  |                       |                  |                  |                                  |     |     | P040                   |

|        |                  |                       | 13 <sup>*1</sup> | 17 *1            | 20 *1                            | 23  | 29  | A10 *2, *3, *4, *5     |

|        |                  | 11 *1                 |                  |                  |                                  |     |     | PPG23_1                |

|        |                  |                       |                  |                  |                                  |     |     | TOT7_0                 |

|        |                  |                       |                  |                  |                                  |     |     | AIN1_0                 |

|        |                  |                       |                  |                  |                                  |     |     | SIN0_1<br>P041         |

|        |                  |                       | 14*1             | 18 <sup>*1</sup> | 21 *1                            | 24  | 30  | A11 *2, *3, *4, *5     |

|        |                  | *1                    |                  |                  |                                  |     |     | SIN9 0                 |

|        |                  | 12 *1                 |                  |                  |                                  |     |     | ICU9 1                 |

|        |                  |                       |                  |                  |                                  |     |     | BIN1_0                 |

|        |                  |                       |                  |                  |                                  |     |     | INT12_0                |

|        |                  |                       |                  |                  |                                  |     |     | P042                   |

|        | ■PIN Description |                       | 15 <sup>*1</sup> | 19 <sup>*1</sup> | 22 <sup>*1</sup>                 | 25  | 31  | A12 *2, *3, *4, *5     |

|        |                  | 40 *1                 |                  |                  |                                  |     |     | SOT9_0                 |

|        |                  | 13*1                  |                  |                  |                                  |     |     | AN47<br>ICU8_1         |

| 22, 23 |                  |                       |                  |                  |                                  |     |     | TRG0_1                 |