Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | FR81S                                                                             |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, CSIO, I <sup>2</sup> C, LINbus, SPI, UART/USART                           |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 76                                                                                |

| Program Memory Size        | 1.0625MB (1.0625M x 8)                                                            |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | 64K x 8                                                                           |

| RAM Size                   | 136K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                       |

| Data Converters            | A/D 37x12b; D/A 2x8b                                                              |

| Oscillator Type            | External                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-LQFP                                                                          |

| Supplier Device Package    | 100-LQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/mb91f526fscpmc-gs-ere2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Product lineup comparison 176 pins

| Product lineup comparison 176 pins                 |                      |            | I                 | I             |             |

|----------------------------------------------------|----------------------|------------|-------------------|---------------|-------------|

|                                                    | MB91F522L            | MB91F523L  | MB91F524L         | MB91F525L     | MB91F526L   |

| System Clock                                       |                      | On chip    | PLL Clock mult    | iple method   |             |

| Minimum instruction execution time                 |                      |            | 12.5ns (80MH      | lz)           |             |

| Flash Capacity (Program)                           | (256+64)KB           | (384+64)KB | (512+64)KB        | (768+64)KB    | (1024+64)KB |

| Flash Capacity (Data)                              |                      |            | 64KB              |               |             |

| RAM Capacity                                       | (48+                 | 8)KB       | (64+8)KB          | (96+8)KB      | (128+8)KB   |

| External BUS I/F                                   |                      |            | Yes               |               |             |

| (22address/16data/4cs)                             |                      |            | 162               |               |             |

| DMA Transfer                                       |                      |            | 16ch              |               |             |

| 16-bit Base Timer                                  |                      |            | 2ch               |               |             |

| Free-run Timer                                     |                      | 1          | 6bit×3ch, 32bit   | ×3ch          |             |

| Input capture                                      |                      | 1          | 6bit×4ch, 32bit   | ×6ch          |             |

| Output Compare                                     |                      | 1          | 6bit×6ch, 32bit   | ×6ch          |             |

| 16-bit Reload Timer                                |                      |            | 8ch               |               |             |

| PPG                                                |                      |            | 16bit×48ch        |               |             |

| Up/down Counter                                    |                      |            | 2ch               |               |             |

| Clock Supervisor                                   |                      |            | Yes               |               |             |

| External Interrupt                                 |                      |            | 8ch×2units        |               |             |

| A/D converter                                      |                      | 12bit×32d  | ch (1unit), 12bit | ×16ch (1unit) |             |

| D/A converter (8bit)                               |                      |            | 2ch               |               |             |

| Multi-Function Serial Interface                    | 12ch <sup>*1</sup>   |            |                   |               |             |

| CAN                                                | 64msg×2ch/128msg×1ch |            |                   |               |             |

| Hardware Watchdog Timer                            |                      |            | Yes               |               |             |

| CRC Formation                                      |                      |            | Yes               |               |             |

| Low-voltage detection reset                        |                      |            | Yes               |               |             |

| Flash Security                                     |                      |            | Yes               |               |             |

| ECC Flash/WorkFlash                                |                      |            | Yes               |               |             |

| ECC RAM                                            |                      |            | Yes               |               |             |

| Memory Protection Function (MPU)                   |                      |            | Yes               |               |             |

| Floating point arithmetic (FPU)                    |                      |            | Yes               |               |             |

| Real Time Clock (RTC)                              |                      |            | Yes               |               |             |

| General-purpose port (#GPIOs)                      |                      |            | 152 ports         |               |             |

| SSCG                                               |                      |            | Yes               |               |             |

| Sub clock                                          |                      |            | Yes               |               |             |

| CR oscillator                                      | Yes                  |            |                   |               |             |

| NMI request function                               | Yes                  |            |                   |               |             |

| OCD (On Chip Debug)                                | Yes                  |            |                   |               |             |

| TPU (Timing Protection Unit)                       | Yes                  |            |                   |               |             |

| Key code register                                  | Yes                  |            |                   |               |             |

| Waveform generator                                 | 6ch                  |            |                   |               |             |

| Operation guaranteed temperature (T <sub>A</sub> ) |                      |            | -40°C to +125     |               |             |

| Power supply                                       |                      |            | 2.7V to 5.5V      | *2            |             |

| Package                                            |                      |            | LQP176            |               |             |

<sup>\*1:</sup> Only channel 3 and channel 4 support the I<sup>2</sup>C (fast mode/standard mode).

Only channel 5, channel 6, channel 7, channel 8, channel 10 and channel 11 support the I<sup>2</sup>C (standard mode).

<sup>\*2:</sup> The initial detection voltage of the external low voltage detection is 2.8V±8% (2.576V to 3.024V). This LVD setting and internal LVD cannot be used to reliably generate a reset before voltage dips below minimum guaranteed operation voltage, as these detection levels are below the minimum guaranteed MCU operation voltage. Below the minimum guaranteed MCU operation voltage, MCU operations are not guaranteed with the exception of LVD.

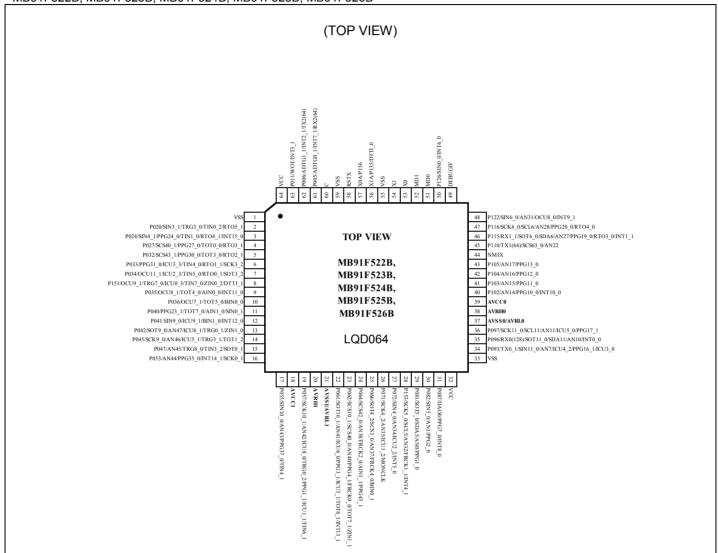

## 2. Pin Assignment

#### MB91F52xB

MB91F522B, MB91F523B, MB91F524B, MB91F525B, MB91F526B

<sup>\*</sup> In a single clock product, pin 56 and pin 57 are the general-purpose ports.

| Туре | Circuit                                                                       | Remarks                                                                                       |

|------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| J    | Digital output  Digital output  CMOS-hys input  Standby control  Analog input | Analog input, General-purpose I/O port (5V tolerant)     Output 4mA     CMOS hysteresis input |

| К    | Mode input  Control                                                           | •Mode I/O     • CMOS hysteresis input                                                         |

| L    | Digital output  TTL input                                                     | Open-drain I/O Output 25mA (Nch open-drain) TTL input                                         |

| М    | CMOS-hys input                                                                | CMOS hysteresis input     Pull-up resistor 50kΩ                                               |

| N    | Input Standby control                                                         | •Main oscillation I/O                                                                         |

| A 1.1                                            |                               | Address offset val            | ue / Register name            |                               | Divi              |  |

|--------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------|--|

| Address                                          | +0                            | +1                            | +2                            | +3                            | Block             |  |

| 000CF0 <sub>н</sub>                              |                               |                               | [R/W] W<br>0000000 0-000000   |                               |                   |  |

| 000СF4 <sub>н</sub>                              | DCSR15<br>0                   | 5 [R/W] H<br>000              |                               | [R/W] H<br>00000000           | DMA<br>Controller |  |

| 000CF8 <sub>н</sub>                              | XX                            |                               | [R/W] W<br>XXXXXXXX XXXXXX    | xx                            | [S]               |  |

| 000СFС <sub>н</sub>                              | XX                            |                               | [R/W] W<br>XXXXXXXX XXXXXX    | xx                            |                   |  |

| 000D00 <sub>H</sub><br>to<br>000DF0 <sub>H</sub> | I                             | _                             | _                             | -                             | Reserved [S]      |  |

| 000DF4 <sub>н</sub>                              | _                             | _                             | DNMIR [R/W] B<br>00           | DILVR [R/W] B<br>11111        | DMA               |  |

| 000DF8 <sub>н</sub>                              |                               | DMACR<br>0                    | [R/W] W<br>0                  |                               | Controller<br>[S] |  |

| 000DFC <sub>н</sub>                              | l                             | _                             | _                             | _                             | Reserved [S]      |  |

| 000E00 <sub>н</sub>                              | DDR00 [R/W] B,H,W<br>00000000 | DDR01 [R/W] B,H,W<br>00000000 | DDR02 [R/W] B,H,W<br>00000000 | DDR03 [R/W] B,H,W<br>00000000 | Data Direction    |  |

| 000E04 <sub>H</sub>                              | DDR04 [R/W] B,H,W<br>00000000 | DDR05 [R/W] B,H,W<br>00000000 | DDR06 [R/W] B,H,W<br>00000000 | DDR07 [R/W] B,H,W<br>00000000 | Register          |  |

| 000E08 <sub>H</sub>                              | DDR08 [R/W] B,H,W<br>00000000 | DDR09 [R/W] B,H,W<br>00000000 | DDR10 [R/W] B,H,W<br>00000000 | DDR11 [R/W] B,H,W<br>00000000 |                   |  |

| 000E0С <sub>н</sub>                              | DDR12 [R/W] B,H,W<br>00000000 | DDR13 [R/W] B,H,W<br>-0000000 | DDR14 [R/W] B,H,W             | DDR15 [R/W] B,H,W<br>000000   | Data Direction    |  |

| 000E10 <sub>H</sub>                              | _                             | _                             | _                             | _                             | Register          |  |

| 000E14 <sub>H</sub>                              | _                             | _                             | _                             | _                             |                   |  |

| 000E18 <sub>H</sub>                              | DDR16 [R/W] B,H,W<br>00000000 | DDR17 [R/W] B,H,W<br>00000000 | DDR18 [R/W] B,H,W<br>00000000 | DDR19 [R/W] B,H,W<br>00000000 |                   |  |

| 000E1C <sub>н</sub>                              | _                             | _                             | _                             | _                             | Reserved          |  |

| 000E20 <sub>H</sub>                              | PFR00 [R/W] B,H,W<br>00000000 | PFR01 [R/W] B,H,W<br>00000000 | PFR02 [R/W] B,H,W<br>00000000 | PFR03 [R/W] B,H,W<br>00000000 |                   |  |

| 000E24 <sub>H</sub>                              | PFR04 [R/W] B,H,W<br>00000000 | PFR05 [R/W] B,H,W<br>00000000 | PFR06 [R/W] B,H,W<br>00000000 | PFR07 [R/W] B,H,W<br>00000000 |                   |  |

| 000E28 <sub>Н</sub>                              | PFR08 [R/W] B,H,W<br>00000000 | PFR09 [R/W] B,H,W<br>00000000 | PFR10 [R/W] B,H,W<br>00000000 | PFR11 [R/W] B,H,W<br>00000000 | Port Function     |  |

| 000E2C <sub>н</sub>                              | PFR12 [R/W] B,H,W<br>00000000 | PFR13 [R/W] B,H,W<br>-0000000 | PFR14 [R/W] B,H,W<br>000      | PFR15 [R/W] B,H,W<br>000000   | Register          |  |

| 000E30 <sub>H</sub>                              | _                             | _                             | _                             | _                             |                   |  |

| 000E34 <sub>H</sub>                              | _                             | _                             | _                             | _                             |                   |  |

| 000E38 <sub>H</sub>                              | PFR16 [R/W] B,H,W<br>00000000 | PFR17 [R/W] B,H,W<br>00000000 | PFR18 [R/W] B,H,W<br>00000000 | PFR19 [R/W] B,H,W<br>00000000 |                   |  |

| A al al as a s                                   |                                             | Address offset value          | ue / Register name              |                                   | Disale                                                                                   |

|--------------------------------------------------|---------------------------------------------|-------------------------------|---------------------------------|-----------------------------------|------------------------------------------------------------------------------------------|

| Address                                          | +0                                          | +1                            | +2                              | +3                                | Block                                                                                    |

| 000F70 <sub>Н</sub>                              | RCRH0 [W] H,W<br>XXXXXXX                    | RCRL0 [W] B,H,W<br>XXXXXXXX   | UDCRH0 [R] H,W<br>00000000      | UDCRL0 [R] B,H,W<br>00000000      | Up/Down                                                                                  |

| 000F74 <sub>H</sub>                              | CCR0 [R/W] B,H<br>00000000 -0001000         |                               | _                               | CSR0 [R/W] B<br>00000000          | Counter 0                                                                                |

| 000F78 <sub>H</sub><br>to<br>000F7C <sub>H</sub> | <del>-</del>                                |                               |                                 | _                                 | Reserved                                                                                 |

| 000F80н                                          | RCRH1 [W] H,W                               |                               | Up/Down                         |                                   |                                                                                          |

| 000F84 <sub>н</sub>                              |                                             | R/W] B,H<br>) -0001000        | _                               | CSR1 [R/W] B<br>00000000          | Counter 1                                                                                |

| 000F88 <sub>н</sub>                              | _                                           | _                             | MSCH45 [R]<br>B,H,W<br>00000000 | MSCL45 [R/W]<br>B,H,W<br>00       | Input Capture 4,5<br>32-bit ICU<br>Cycle and pulse<br>width<br>measurement<br>control 45 |

| 000F8С <sub>н</sub>                              | _                                           | _                             | MSCH67 [R]<br>B,H,W<br>00000000 | MSCL67 [R/W]<br>B,H,W<br>00       | Input Capture 6,7<br>32-bit ICU<br>Cycle and pulse<br>width<br>measurement<br>control 67 |

| 000F90 <sub>н</sub>                              |                                             | OCCP10<br>00000000 00000000   |                                 |                                   | Output Compare                                                                           |

| 000F94 <sub>н</sub>                              |                                             | OCCP11<br>00000000 00000000   |                                 |                                   | 32-bit OCU                                                                               |

| 000F98 <sub>н</sub>                              | _                                           | _                             | OCSH1011 [R/W]<br>B,H,W<br>000  | OCSL1011 [R/W]<br>B,H,W<br>000000 | Output Compare<br>10,11<br>32-bit OCU                                                    |

| 000F9Сн                                          | _                                           | _                             | _                               | OCLS1011 [R/W]<br>B,H,W<br>0000   | OCU1011 Output level control register                                                    |

| 000FA0 <sub>н</sub>                              |                                             | CPCLR5<br>111111111 11111111  |                                 |                                   |                                                                                          |

| 000FA4 <sub>Н</sub>                              | TCDT5 [R/W] W<br>00000000 00000000 00000000 |                               |                                 |                                   | Free-run Timer 5<br>32-bit FRT                                                           |

| 000FA8н                                          | TCCSH5<br>[R/W]B,H,W<br>000                 | TCCSL5 [R/W]B,H,W<br>-1-00000 | _                               | _                                 |                                                                                          |

| 000FAC <sub>H</sub><br>to<br>000FCC <sub>H</sub> | _                                           | _                             | _                               | _                                 | Reserved                                                                                 |

| A -1 -1             | Address offset value / Register name                |                                              |                                     |                                     | BL . !             |

|---------------------|-----------------------------------------------------|----------------------------------------------|-------------------------------------|-------------------------------------|--------------------|

| Address             | +0                                                  | +1                                           | +2                                  | +3                                  | Block              |

| 001344н             | ADCOMP28/ADCOMPB28[R/W] H,W 00000000 00000000       |                                              |                                     | COMPB29[R/W] H,W                    |                    |

| 001348н             | ADCOMP30/ADCOMPB30[R/W] H,W 00000000 00000000       |                                              |                                     | COMPB31[R/W] H,W<br>00 00000000     |                    |

| 00134С <sub>н</sub> | ADTCS0[R<br>00000000                                | -                                            | · ·                                 | [R/W] B,H,W<br>00 0010              |                    |

| 001350 <sub>н</sub> | ADTCS2[R<br>00000000                                | - · · · · · · · · · · · · · · · · · · ·      | · ·                                 | [R/W] B,H,W<br>00 0010              |                    |

| 001354 <sub>Н</sub> | ADTCS4[R<br>00000000                                | -                                            | · ·                                 | [R/W] B,H,W<br>00 0010              |                    |

| 001358н             | ADTCS6[R<br>00000000                                | -                                            |                                     | [R/W] B,H,W<br>00 0010              |                    |

| 00135С <sub>н</sub> | ADTCS8[R<br>00000000                                | -                                            | · ·                                 | [R/W] B,H,W<br>00 0010              | ]                  |

| 001360н             | ADTCS10[R/W] B,H,W<br>00000000 0010                 |                                              | ADTCS11[R/W] B,H,W<br>00000000 0010 |                                     | _                  |

| 001364н             | ADTCS12[R/W] B,H,W<br>00000000 0010                 |                                              | ADTCS13[R/W] B,H,W<br>00000000 0010 |                                     |                    |

| 001368н             | ADTCS14[R/W] B,H,W<br>00000000 0010                 |                                              | ADTCS15[R/W] B,H,W<br>00000000 0010 |                                     | 12-bit A/D         |

| 00136Сн             | ADTCS16[F<br>00000000                               | -                                            | ADTCS17[R/W] B,H,W<br>00000000 0010 |                                     | converter 1/2 unit |

| 001370н             | ADTCS18[F<br>00000000                               | R/W] B,H,W<br>0 0010                         |                                     | ADTCS19[R/W] B,H,W<br>00000000 0010 |                    |

| 001374н             | =                                                   | S20[R/W] B,H,W ADTCS21[R/W] B,H,W 00000 0010 |                                     |                                     |                    |

| 001378н             | ADTCS22[R/W] B,H,W ADTCS23[R/W] B,H,W 00000000 0010 |                                              | -                                   |                                     |                    |

| 00137Сн             | ADTCS24[R/W] B,H,W ADTCS25[R/W] B,H,W 00000000 0010 |                                              |                                     |                                     |                    |

| 001380н             | ADTCS26[F<br>00000000                               | R/W] B,H,W<br>0 0010                         | ADTCS27[R/W] B,H,W<br>00000000 0010 |                                     |                    |

| 001384н             | ADTCS28[R/W] B,H,W<br>00000000 0010                 |                                              | ADTCS29[R/W] B,H,W<br>00000000 0010 |                                     |                    |

| 001388н             | ADTCS30[F<br>00000000                               | R/W] B,H,W<br>0 0010                         | ADTCS31[R/W] B,H,W<br>00000000 0010 |                                     |                    |

| 00138С <sub>н</sub> |                                                     | R] B,H,W<br>00000000                         |                                     | 1[R] B,H,W<br>0 00000000            |                    |

| 001390н             | -                                                   | [R] B,H,W<br>00000000                        |                                     | 3[R] B,H,W<br>0 00000000            |                    |

| A al alasa a a      |                                          | Address offset val                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ue / Register name                                                                            |                                                        | Disals                                                               |

|---------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------|

| Address             | +0                                       | +1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | +2                                                                                            | +3                                                     | Block                                                                |

| 001790н             | —/(TBYTE31)/<br>(LAMESR1)<br>[R/W] B,H,W | MESR1) (LAMERT1) (LAMIER1) (LAMTID1) (LAMTID1) (R/W] B,H,W (R/W] B,H,W (R/W] B,H,W (R/W] B,H,W (R/W) B |                                                                                               | Multi-UART1  *3: Reserved because CSIO mode is not set |                                                                      |

| 001794н             | BGR1[R/W] H,W<br>00000000 00000000       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | — /(ISMK1)[R/W]<br>B,H,W<br><sup>+2</sup>                                                     | — /(ISBA1)[R/W]<br>B,H,W<br>*2                         | immediately after reset.                                             |

| 001798н             | FCR11[R/W]<br>B,H,W<br>00100             | FCR01[R/W]<br>B,H,W<br>-0000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                                                                                             | R/W] B,H,W<br>00000000                                 | *4: Reserved<br>because LIN2.1<br>mode is not set                    |

| 00179Сн             | FTICR1[R/<br>00000000                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                                                                                             | _                                                      | immediately after reset.                                             |

| 0017A0 <sub>н</sub> | SCR2/(IBCR2)[R/W]<br>B,H,W<br>000000     | SMR2[R/W] B,H,W<br>000-00-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SSR2[R/W] B,H,W 0-000011                                                                      |                                                        | Multi-UART2                                                          |

| 0017А4н             | //DDD12//TDD12\\[D\M\] B H \M            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RDR02/(TDR02)[R/W] B,H,W<br>0 00000000 *1                                                     |                                                        | *1: Byte access is possible only for                                 |

| 0017А8н             | SACSR2[R/W] B,H,W<br>0000 00000000       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | STMR2[R] B,H,W<br>00000000 00000000                                                           |                                                        | access to lower 8 bits.                                              |

| 0017АСн             | STMCR2[R/W] B,H,W<br>00000000 00000000   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | — /(SCSCR2/SF                                                                                 | *2: Reserved<br>because I <sup>2</sup> C               |                                                                      |

| 0017B0 <sub>н</sub> | — /(SCSTR32)/<br>(LAMSR2)<br>[R/W] B,H,W | — /(SCSTR22)/<br>(LAMCR2)<br>[R/W] B,H,W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | — /(SCSTR12)/<br>(SFLR12)<br>[R/W] B,H,W                                                      | — /(SCSTR02)/<br>(SFLR02)<br>[R/W] B,H,W               | mode is not set<br>immediately after<br>reset.                       |

| 0017В4н             | _                                        | — /(SCSFR22)<br>[R/W] B,H,W<br>*3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | — /(SCSFR12)<br>[R/W] B,H,W<br>*3                                                             | — /(SCSFR02)<br>[R/W] B,H,W<br>*3                      | *3: Reserved<br>because CSIO<br>mode is not set<br>immediately after |

| 0017В8 <sub>н</sub> | —/(TBYTE32)/<br>(LAMESR2)<br>[R/W] B,H,W | —/(TBYTE22)/<br>(LAMERT2)<br>[R/W] B,H,W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | /(TBYTE12)/<br>(LAMIER2)<br>[R/W] B,H,W<br><sup>-3</sup> (LAMTID2)<br>[R/W] B,H,W<br>00000000 |                                                        | *4: Reserved<br>because LIN2.1<br>mode is not set                    |

| 0017ВСн             | •                                        | 2[R/W] H, W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                               | — /(ISBA2)[R/W]<br>B,H,W<br>* <sup>*2</sup>            | immediately after reset.                                             |

| 0017С0н             | FCR12[R/W]<br>B,H,W<br>00100             | FCR02[R/W]<br>B,H,W<br>-0000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00000000 00000000                                                                             |                                                        | Multi-UART2                                                          |

| 0017С4 <sub>н</sub> | FTICR2[R/<br>00000000                    | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                                                                             | _                                                      |                                                                      |

|                                                  |                                           | Address offset va |                                           |                                           |                    |

|--------------------------------------------------|-------------------------------------------|-------------------|-------------------------------------------|-------------------------------------------|--------------------|

| Address                                          | +0                                        | +1                | +2                                        | +3                                        | Block              |

| 0020BC <sub>н</sub>                              | MSGVAL80<br>00000000                      |                   |                                           | 70 [R] B,H,W<br>0 00000000                | CANO               |

| 0020C0 <sub>H</sub><br>to<br>0020FC <sub>H</sub> | _                                         |                   | _                                         |                                           | — CAN0<br>(128msb) |

| 002100н                                          | CTRLR1 [R/W] B,H,W<br>000-0001            |                   |                                           | R/W] B,H,W<br>00000000                    |                    |

| 002104н                                          | ERRCNT1<br>00000000                       |                   | _                                         | /W] B,H,W<br>00000001                     |                    |

| 002108н                                          | INTR1 [F<br>00000000                      |                   | _                                         | R/W] B,H,W<br>X00000                      |                    |

| 00210С <sub>н</sub>                              | BRPER1 [F                                 | -                 | _                                         | _                                         |                    |

| 002110 <sub>н</sub>                              | IF1CREQ1 [<br>0 0                         | _                 |                                           | [R/W] B,H,W<br>00000000                   |                    |

| 002114 <sub>н</sub>                              | IF1MSK21 [R/W] B,H,W<br>11-11111 11111111 |                   |                                           | IF1MSK11 [R/W] B,H,W<br>11111111 11111111 |                    |

| 002118 <sub>н</sub>                              | IF1ARB21 [R/W] B,H,W<br>00000000 00000000 |                   | IF1ARB11 [R/W] B,H,W<br>00000000 00000000 |                                           | (64msb)            |

| 00211С <sub>н</sub>                              | IF1MCTR1 [R/W] B,H,W<br>00000000 00000    |                   | _                                         | _                                         |                    |

| 002120 <sub>н</sub>                              | IF1DTA11 [R/W] B,H,W<br>00000000 00000000 |                   | IF1DTA21 [R/W] B,H,W<br>00000000 00000000 |                                           |                    |

| 002124 <sub>н</sub>                              | IF1DTB11 [I<br>00000000                   |                   |                                           | [R/W] B,H,W<br>0 00000000                 |                    |

| 002128н                                          | _                                         | _                 | _                                         | _                                         |                    |

| 00212C <sub>н</sub>                              | _                                         | _                 | _                                         | _                                         |                    |

| 002130 <sub>H</sub> ,<br>002134 <sub>H</sub>     |                                           | Reserved (I       | IF1 data mirror)                          |                                           |                    |

| 002138 <sub>Н</sub>                              | _                                         | _                 | _                                         | _                                         |                    |

| 00213С <sub>Н</sub>                              | _                                         | _                 | _                                         | _                                         |                    |

| 002140 <sub>н</sub>                              | IF2CREQ1 [R/W] B,H,W<br>0 00000001        |                   |                                           | [R/W] B,H,W<br>00000000                   | CAN1<br>(64msb)    |

| 002144 <sub>н</sub>                              | IF2MSK21 [<br>11-11111                    | _                 |                                           | [R/W] B,H,W<br>I 11111111                 |                    |

| 002148 <sub>н</sub>                              | IF2ARB21 [<br>00000000                    | <del>-</del>      |                                           | [R/W] B,H,W<br>0 00000000                 |                    |

| 00214С <sub>н</sub>                              | IF2MCTR1 [<br>00000000                    |                   | _                                         | _                                         |                    |

|                               | Interrupt | Interrupt number |                    |                  | Default               |    |

|-------------------------------|-----------|------------------|--------------------|------------------|-----------------------|----|

| Interrupt factor              | Decimal   | Hexa<br>decimal  | Interrupt<br>level | Offset           | address for<br>TBR    | RN |

|                               | 66        | 42               |                    | 2F4 <sub>H</sub> | 000FFEF4 <sub>H</sub> |    |

| Used with the INT instruction | 1         |                  | -                  |                  | 1                     | -  |

|                               | 255       | FF               |                    | 000н             | 000FFC00 <sub>H</sub> |    |

**Note:** It does not support a DMA transfer request caused by an interrupt generated from a peripheral to which no RN (Resource Number) is assigned.

- \*1: It does not support a DMA transfer by the status of the multi-function serial interface and I<sup>2</sup>C reception.

- \*2: Reload timer ch.4 to ch.7 do not support a DMA transfer by the interrupt.

- \*3: PPG ch.24 to ch.47 do not support a DMA transfer by the interrupt.

- \*4: The clock calibration unit does not support a DMA transfer by the interrupt.

- \*5: 32-bit Free-run timer ch.3, ch.4 and ch.5 do not support a DMA transfer by the interrupt.

- \*6: There is no resource corresponding to the interrupt level.

- \*7: It does not support a DMA transfer by the external low-voltage detection interrupt.

- \*8: REALOS is a trademark of Cypress.

| 120 pins                                                       | Interrupt number |             | Interrupt                                        |                  | Default               |     |

|----------------------------------------------------------------|------------------|-------------|--------------------------------------------------|------------------|-----------------------|-----|

| Interrupt factor                                               | Decimal          | Hexadecimal | level                                            | Offset           | address for<br>TBR    | RN  |

| Reset                                                          | 0                | 0           | -                                                | 3FC <sub>H</sub> | 000FFFFC <sub>H</sub> | -   |

| System reserved                                                | 1                | 1           | -                                                | 3F8 <sub>H</sub> | 000FFFF8 <sub>H</sub> | -   |

| System reserved                                                | 2                | 2           | -                                                | 3F4 <sub>H</sub> | 000FFFF4 <sub>H</sub> | -   |

| System reserved                                                | 3                | 3           | -                                                | 3F0 <sub>H</sub> | 000FFFF0 <sub>H</sub> | -   |

| System reserved                                                | 4                | 4           | -                                                | 3ЕСн             | 000FFFEC <sub>н</sub> | -   |

| FPU exception                                                  | 5                | 5           | -                                                | 3E8 <sub>H</sub> | 000FFFE8 <sub>H</sub> | -   |

| Exception of instruction access protection violation           | 6                | 6           | _                                                | 3E4 <sub>H</sub> | 000FFFE4 <sub>H</sub> | _   |

| Exception of data access protection violation                  | 7                | 7           | _                                                | 3E0 <sub>H</sub> | 000FFFE0 <sub>H</sub> | _   |

| Data access error interrupt                                    | 8                | 8           | -                                                |                  | 000FFFDC <sub>H</sub> | -   |

| INTE instruction                                               | 9                | 9           | -                                                |                  | 000FFFD8 <sub>H</sub> | -   |

| Instruction break                                              | 10               | 0A          | -                                                |                  | 000FFFD4 <sub>H</sub> | -   |

| System reserved                                                | 11               | 0B          | -                                                |                  | 000FFFD0 <sub>H</sub> | _   |

| System reserved                                                | 12               | 0C          | _                                                |                  | 000FFFCC <sub>H</sub> | _   |

| System reserved                                                | 13               | 0D          | _                                                |                  | 000FFFC8 <sub>H</sub> | -   |

| Exception of invalid instruction                               | 14               | 0E          | _                                                |                  | 000FFFC4 <sub>H</sub> | _   |

| NMI request                                                    |                  | 02          |                                                  | 00 ін            | 000111016             |     |

| Error generation during internal bus diagnosis                 |                  |             |                                                  |                  |                       |     |

| XBS RAM double-bit error generation                            | 15               | 0F          | 15 (F <sub>H</sub> )                             | 3C0 <sub>H</sub> | 000FFFC0 <sub>H</sub> | _   |

| Backup RAM double-bit error generation                         | 13               | OI OI       | Fixed                                            | JCOH             | OOOI I I COH          | _   |

| TPU violation                                                  |                  |             |                                                  |                  |                       |     |

| External interrupt 0-7                                         | 16               | 10          | ICR00                                            | 3DC              | 000FFFBC <sub>H</sub> | 0   |

| External interrupt 8-15                                        | 10               | 10          | ICKUU                                            | SBCH             | OUOFFFBCH             |     |

| •                                                              | 17               | 11          | ICR01                                            | 3B8 <sub>H</sub> | 000FFFB8 <sub>H</sub> | 1*  |

| External low-voltage detection interrupt                       | 18               | 12          | ICR02                                            | 204              | 000FFFB4 <sub>H</sub> | 2*  |

| Reload timer 0/1/4/5                                           |                  |             |                                                  |                  |                       | 3*  |

| Reload timer 2/3/6/7                                           | 19               | 13          | ICR03                                            | 3B0 <sub>H</sub> | 000FFFB0 <sub>H</sub> | 3"  |

| Multi-function serial interface                                |                  | 14          | ICR04                                            | 3АСн             | 000FFFAC <sub>н</sub> |     |

| ch.0 (reception completed)                                     | 20               |             |                                                  |                  |                       | 4*  |