Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 33MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 16KB (16K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

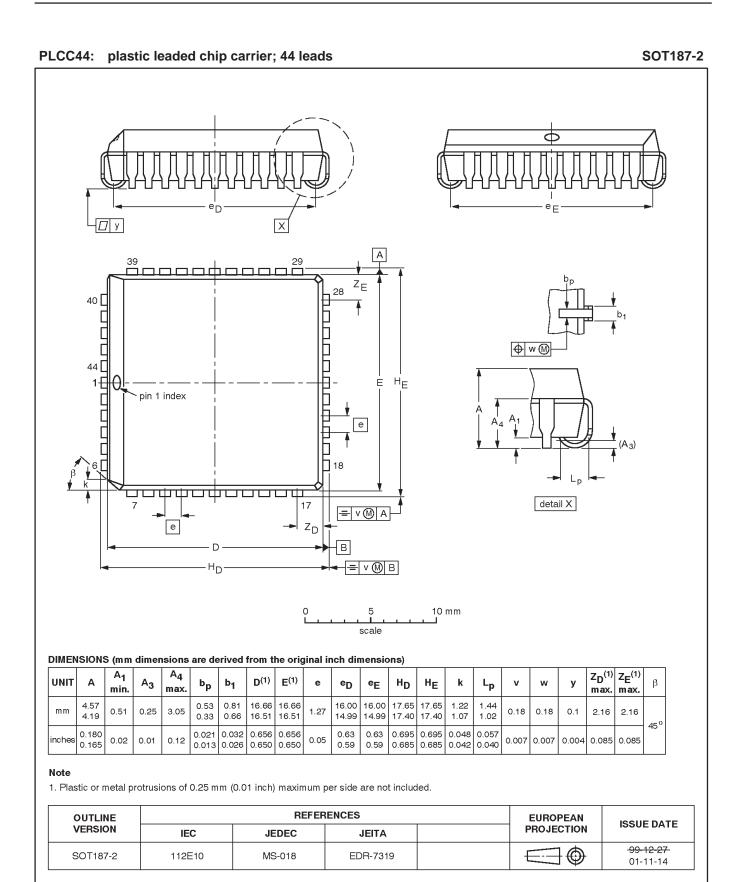

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89c51rb2ba-01-512 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# P89C51RA2/RB2/RC2/RD2xx

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

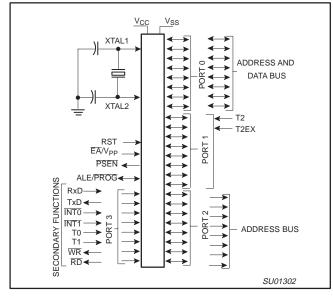

## LOGIC SYMBOL

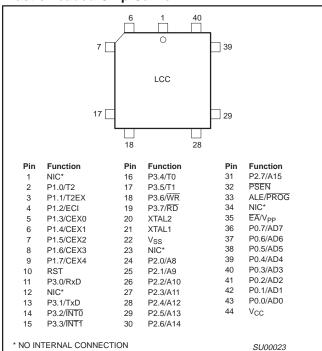

## PINNING

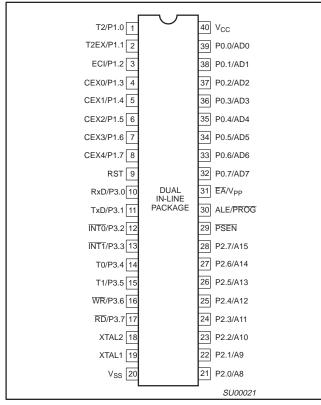

### Plastic Dual In-Line Package

### **Plastic Leaded Chip Carrier**

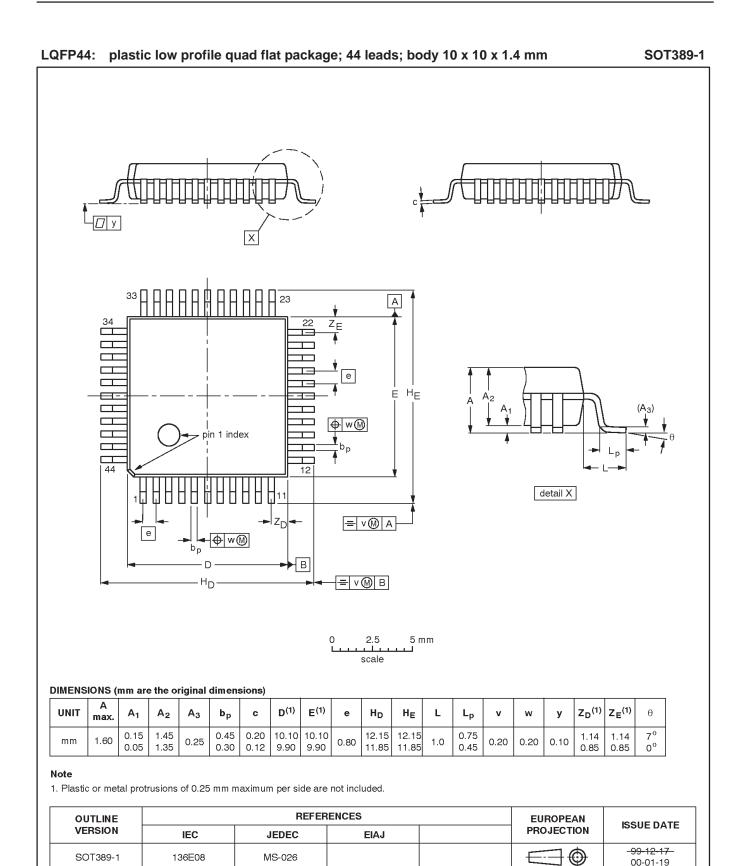

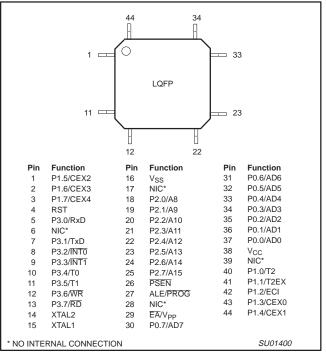

## **Plastic Quad Flat Pack**

## P89C51RA2/RB2/RC2/RD2xx

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

| Table 1. | Special Fu | nction Registers | (Continued) |

|----------|------------|------------------|-------------|

|----------|------------|------------------|-------------|

| SYMBOL                                   | DESCRIPTION                                                                               | DIRECT                                 | BIT ADDRESS, SYMBOL, OR ALTERNATIVE PORT FUNCTION |      |      |      |       |     | ION  | RESET  |                                        |

|------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------|------|------|------|-------|-----|------|--------|----------------------------------------|

| STWBOL                                   | DESCRIPTION                                                                               | ADDRESS                                | MSB                                               |      |      |      |       |     |      | LSB    | VALUE                                  |

|                                          |                                                                                           |                                        | D7                                                | D6   | D5   | D4   | D3    | D2  | D1   | D0     |                                        |

| PSW*                                     | Program Status Word                                                                       | DOH                                    | CY                                                | AC   | F0   | RS1  | RS0   | OV  | F1   | P      | 00000000B                              |

| RCAP2H#<br>RCAP2L#                       | Timer 2 Capture High<br>Timer 2 Capture Low                                               | CBH<br>CAH                             |                                                   |      |      | -    |       |     |      |        | 00H<br>00H                             |

| SADDR#<br>SADEN#                         | Slave Address<br>Slave Address Mask                                                       | A9H<br>B9H                             |                                                   |      |      |      |       |     |      |        | 00H<br>00H                             |

| SBUF                                     | Serial Data Buffer                                                                        | 99H                                    | 9F                                                | 9E   | 9D   | 9C   | 9B    | 9A  | 99   | 98     | xxxxxxxB                               |

| SCON*                                    | Serial Control                                                                            | 98H                                    | SM0/FE                                            | SM1  | SM2  | REN  | TB8   | RB8 | TI   | RI     | 00H                                    |

| SP                                       | Stack Pointer                                                                             | 81H                                    |                                                   |      |      |      |       |     |      |        | 07H                                    |

|                                          |                                                                                           |                                        | 8F                                                | 8E   | 8D   | 8C   | 8B    | 8A  | 89   | 88     |                                        |

| TCON*                                    | Timer Control                                                                             | 88H                                    | TF1                                               | TR1  | TF0  | TR0  | IE1   | IT1 | IE0  | IT0    | 00H                                    |

|                                          |                                                                                           |                                        | CF                                                | CE   | CD   | СС   | СВ    | CA  | C9   | C8     |                                        |

| T2CON*                                   | Timer 2 Control                                                                           | C8H                                    | TF2                                               | EXF2 | RCLK | TCLK | EXEN2 | TR2 | C/T2 | CP/RL2 | 00H                                    |

| T2MOD#                                   | Timer 2 Mode Control                                                                      | C9H                                    | -                                                 | -    | -    | -    | -     | -   | T2OE | DCEN   | xxxxxx00B                              |

| TH0<br>TH1<br>TH2#<br>TL0<br>TL1<br>TL2# | Timer High 0<br>Timer High 1<br>Timer High 2<br>Timer Low 0<br>Timer Low 1<br>Timer Low 2 | 8CH<br>8DH<br>CDH<br>8AH<br>8BH<br>CCH |                                                   |      |      |      |       |     |      |        | 00H<br>00H<br>00H<br>00H<br>00H<br>00H |

| TMOD                                     | Timer Mode                                                                                | 89H                                    | GATE                                              | C/T  | M1   | MO   | GATE  | C/T | M1   | MO     | 00H                                    |

| WDTRST                                   | Watchdog Timer Reset                                                                      | A6H                                    |                                                   |      |      |      |       |     |      |        |                                        |

\* SFRs are bit addressable.

# SFRs are modified from or added to the 80C51 SFRs.

Reserved bits.

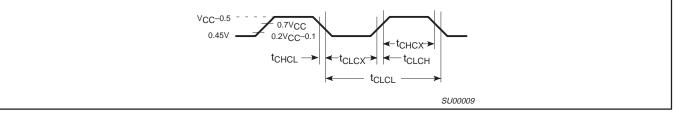

#### **OSCILLATOR CHARACTERISTICS**

XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier. The pins can be configured for use as an on-chip oscillator.

To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected. Minimum and maximum high and low times specified in the data sheet must be observed.

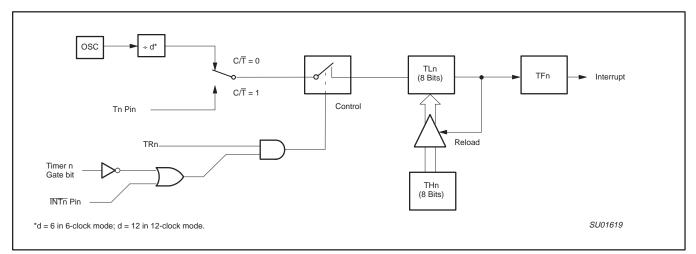

This device is configured at the factory to operate using 12 clock periods per machine cycle, referred to in this datasheet as "12-clock mode". It may be optionally configured on commercially available Flash programming equipment or via ISP or via software to operate at 6 clocks per machine cycle, referred to in this datasheet as "6-clock mode". (This yields performance equivalent to twice that of standard 80C51 family devices). Also see next page.

P89C51RA2/RB2/RC2/RD2xx

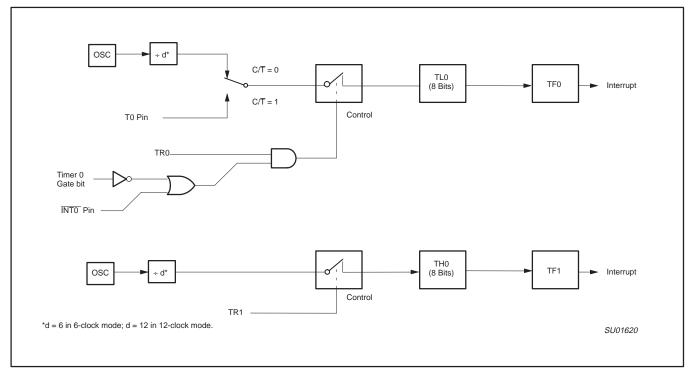

Figure 5. Timer/Counter 0 Mode 3: Two 8-Bit Counters

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

### TIMER 2 OPERATION

#### Timer 2

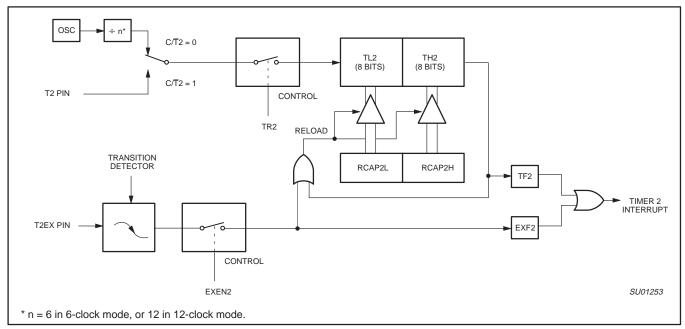

Timer 2 is a 16-bit Timer/Counter which can operate as either an event timer or an event counter, as selected by C/T2 in the special function register T2CON (see Figure 6). Timer 2 has three operating modes: Capture, Auto-reload (up or down counting), and Baud Rate Generator, which are selected by bits in the T2CON as shown in Table 3.

### **Capture Mode**

In the capture mode there are two options which are selected by bit EXEN2 in T2CON. If EXEN2=0, then timer 2 is a 16-bit timer or counter (as selected by C/T2 in T2CON) which, upon overflowing sets bit TF2, the timer 2 overflow bit. This bit can be used to generate an interrupt (by enabling the Timer 2 interrupt bit in the IE register). If EXEN2= 1, Timer 2 operates as described above, but with the added feature that a 1- to -0 transition at external input T2EX causes the current value in the Timer 2 registers, TL2 and TH2, to be captured into registers RCAP2L and RCAP2H, respectively. In addition, the transition at T2EX causes bit EXF2 in T2CON to be set, and EXF2 like TF2 can generate an interrupt (which vectors to the same location as Timer 2 overflow interrupt. The Timer 2 interrupt service routine can interrogate TF2 and EXF2 to determine which event caused the interrupt). The capture mode is illustrated in Figure 7 (There is no reload value for TL2 and TH2 in this mode. Even when a capture event occurs from T2EX, the counter keeps on counting T2EX pin transitions or osc/6 pulses (osc/12 in 12-clock mode).).

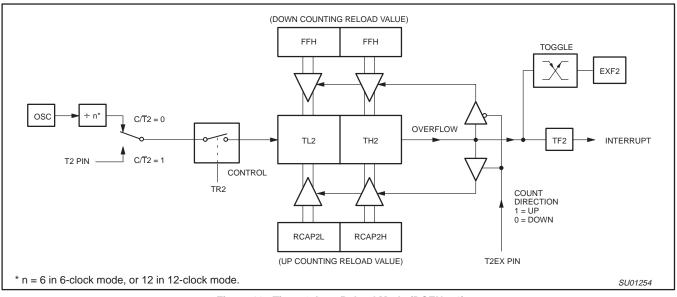

### Auto-Reload Mode (Up or Down Counter)

In the 16-bit auto-reload mode, Timer 2 can be configured (as either a timer or counter [C/T2 in T2CON]) then programmed to count up or down. The counting direction is determined by bit DCEN (Down

Counter Enable) which is located in the T2MOD register (see Figure 8). When reset is applied the DCEN=0 which means Timer 2 will default to counting up. If DCEN bit is set, Timer 2 can count up or down depending on the value of the T2EX pin.

P89C51RA2/RB2/RC2/RD2xx

Figure 9 shows Timer 2 which will count up automatically since DCEN=0. In this mode there are two options selected by bit EXEN2 in T2CON register. If EXEN2=0, then Timer 2 counts up to 0FFFFH and sets the TF2 (Overflow Flag) bit upon overflow. This causes the Timer 2 registers to be reloaded with the 16-bit value in RCAP2L and RCAP2H. The values in RCAP2L and RCAP2H are preset by software means.

If EXEN2=1, then a 16-bit reload can be triggered either by an overflow or by a 1-to-0 transition at input T2EX. This transition also sets the EXF2 bit. The Timer 2 interrupt, if enabled, can be generated when either TF2 or EXF2 are 1.

In Figure 10 DCEN=1 which enables Timer 2 to count up or down. This mode allows pin T2EX to control the direction of count. When a logic 1 is applied at pin T2EX Timer 2 will count up. Timer 2 will overflow at 0FFFFH and set the TF2 flag, which can then generate an interrupt, if the interrupt is enabled. This timer overflow also causes the 16-bit value in RCAP2L and RCAP2H to be reloaded into the timer registers TL2 and TH2.

When a logic 0 is applied at pin T2EX this causes Timer 2 to count down. The timer will underflow when TL2 and TH2 become equal to the value stored in RCAP2L and RCAP2H. Timer 2 underflow sets the TF2 flag and causes 0FFFFH to be reloaded into the timer registers TL2 and TH2.

The external flag EXF2 toggles when Timer 2 underflows or overflows. This EXF2 bit can be used as a 17th bit of resolution if needed. The EXF2 flag does not generate an interrupt in this mode of operation.

|        | (MSI     | 3)                |                      |                               |                              |                |              |               | (LSB)                          |                                                     |

|--------|----------|-------------------|----------------------|-------------------------------|------------------------------|----------------|--------------|---------------|--------------------------------|-----------------------------------------------------|

|        | Т        | F2 E              | XF2                  | RCLK                          | TCLK                         | EXEN2          | TR2          | C/T2          | CP/RL2                         |                                                     |

| Symbol | Position | Name a            | Ind Sig              | nificance                     |                              |                |              |               |                                |                                                     |

| TF2    | T2CON.7  |                   |                      | w flag set by<br>LK or TCLK   |                              | overflow and   | d must be cl | eared by so   | oftware. TF2                   | will not be set                                     |

| EXF2   | T2CON.6  | EXEN2<br>interrup | = 1. Wh<br>t routine | nen Timer 2                   | interrupt is<br>st be cleare | enabled, EX    | F2 = 1 will  | cause the C   | PU to vector                   | ition on T2EX and<br>to the Timer 2<br>t in up/down |

| RCLK   | T2CON.5  |                   |                      |                               |                              |                |              |               | ow pulses for<br>eceive clock. | r its receive clock                                 |

| TCLK   | T2CON.4  |                   |                      |                               |                              |                |              |               | ow pulses fo<br>transmit cloc  | r its transmit cloc<br>k.                           |

| EXEN2  | T2CON.3  |                   | on on T2             | EX if Timer                   |                              |                |              |               |                                | of a negative<br>ses Timer 2 to                     |

| TR2    | T2CON.2  | Start/sto         | op contr             | ol for Timer                  | 2. A logic 1                 | starts the til | mer.         |               |                                |                                                     |

| C/T2   | T2CON.1  | Timer o           | 0 = Ir               |                               | r (OSĆ/6 in                  | 6-clock mod    |              | 2 in 12-cloc  | k mode)                        |                                                     |

| CP/RL2 | T2CON.0  | cleared           | , auto-re<br>= 1. Wł | eloads will o<br>nen either R | ccur either                  | with Timer 2   | overflows of | or negative t | ransitions at                  | EXEN2 = 1. When<br>T2EX when<br>ced to auto-reload  |

|        |          |                   |                      |                               |                              |                |              |               |                                | SU0125                                              |

Figure 6. Timer/Counter 2 (T2CON) Control Register

P89C51RA2/RB2/RC2/RD2xx

Figure 9. Timer 2 in Auto-Reload Mode (DCEN = 0)

Figure 10. Timer 2 Auto Reload Mode (DCEN = 1)

## 80C51 8-bit Flash microcontroller family

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

| S     | CON    | Addres                                                                                                                                           | s = 98H                                   |           |                      |                      |                      |                       |                      |                       |                       | Reset Value = 00H                                                       |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------|----------------------|----------------------|----------------------|-----------------------|----------------------|-----------------------|-----------------------|-------------------------------------------------------------------------|

|       |        | Bit Add                                                                                                                                          | ressable                                  | 7         | 6                    | 5                    | 4                    | 3                     | 2                    | 1                     | 0                     | _                                                                       |

|       |        |                                                                                                                                                  |                                           | SM0       | SM1                  | SM2                  | REN                  | TB8                   | RB8                  | ТΙ                    | RI                    |                                                                         |

| Where | e SM0, | SM1 spe                                                                                                                                          | cify the serial po                        | ort mode  | e, as foll           | ows:                 |                      |                       |                      |                       |                       | -                                                                       |

| SM0   | SM1    | Mode                                                                                                                                             | Description                               | E         | Baud Ra              | ate                  |                      |                       |                      |                       |                       |                                                                         |

| 0     | 0      | 0                                                                                                                                                | shift register                            |           | f <sub>OSC</sub> /12 | 2 (12-cl             | ock mod              | le) or f <sub>O</sub> | <sub>SC</sub> /6 (6- | clock m               | node)                 |                                                                         |

| 0     | 1      | 1                                                                                                                                                | 8-bit UART                                |           | variable             | Э                    |                      |                       |                      |                       |                       |                                                                         |

| 1     | 0      | 2                                                                                                                                                | 9-bit UART                                |           | f <sub>OSC</sub> /64 | 4 or f <sub>OS</sub> | <sub>C</sub> /32 (12 | 2-clock r             | node) o              | r f <sub>OSC</sub> /3 | 32 or f <sub>OS</sub> | <sub>SC</sub> /16 (6-clock mode)                                        |

| 1     | 1      | 3                                                                                                                                                | 9-bit UART                                |           | variable             | Э                    |                      |                       |                      |                       |                       |                                                                         |

| SM2   | acti   | vated if th                                                                                                                                      |                                           | data bit  | (RB8) is             |                      |                      |                       |                      |                       |                       | M2 is set to 1, then RI will not be tivated if a valid stop bit was not |

| REN   | Ena    | ables seria                                                                                                                                      | al reception. Set                         | t by soft | ware to              | enable               | receptio             | on. Clea              | r by soft            | ware to               | o disable             | e reception.                                                            |

| ГВ8   | The    | 9th data                                                                                                                                         | bit that will be t                        | ransmitt  | ed in M              | odes 2               | and 3. S             | Set or cl             | ear by s             | oftware               | as desi               | ired.                                                                   |

| RB8   |        | In Modes 2 and 3, is the 9th data bit that was received. In Mode 1, it SM2=0, RB8 is the stop bit that was received. In Mode 0, RB8 is not used. |                                           |           |                      |                      |                      |                       |                      |                       |                       |                                                                         |

| ті    |        |                                                                                                                                                  | errupt flag. Set b<br>ny serial transmi   |           |                      |                      |                      |                       | e in Mo              | de 0, or              | r at the l            | beginning of the stop bit in the other                                  |

| RI    |        |                                                                                                                                                  | rrupt flag. Set by<br>ay serial reception |           |                      |                      |                      |                       |                      |                       | halfway               | v through the stop bit time in the othe                                 |

SU01626

| Figure 12. | Serial | Port ( | Control | (SCON) | Register |

|------------|--------|--------|---------|--------|----------|

|------------|--------|--------|---------|--------|----------|

|               | Baud Rate     |              | 4          | SMOD | Timer 1 |      |              |  |

|---------------|---------------|--------------|------------|------|---------|------|--------------|--|

| Mode          | 12-clock mode | 6-clock mode | fosc       | SWOD | C/T     | Mode | Reload Value |  |

| Mode 0 Max    | 1.67 MHz      | 3.34 MHz     | 20 MHz     | Х    | Х       | Х    | Х            |  |

| Mode 2 Max    | 625 k         | 1250 k       | 20 MHz     | 1    | Х       | Х    | Х            |  |

| Mode 1, 3 Max | 104.2 k       | 208.4 k      | 20 MHz     | 1    | 0       | 2    | FFH          |  |

| Mode 1, 3     | 19.2 k        | 38.4 k       | 11.059 MHz | 1    | 0       | 2    | FDH          |  |

|               | 9.6 k         | 19.2 k       | 11.059 MHz | 0    | 0       | 2    | FDH          |  |

|               | 4.8 k         | 9.6 k        | 11.059 MHz | 0    | 0       | 2    | FAH          |  |

|               | 2.4 k         | 4.8 k        | 11.059 MHz | 0    | 0       | 2    | F4H          |  |

|               | 1.2 k         | 2.4 k        | 11.059 MHz | 0    | 0       | 2    | E8H          |  |

|               | 137.5         | 275          | 11.986 MHz | 0    | 0       | 2    | 1DH          |  |

|               | 110           | 220          | 6 MHz      | 0    | 0       | 2    | 72H          |  |

|               | 110           | 220          | 12 MHz     | 0    | 0       | 1    | FEEBH        |  |

Figure 13. Timer 1 Generated Commonly Used Baud Rates

#### More About Mode 0

Serial data enters and exits through RxD. TxD outputs the shift clock. 8 bits are transmitted/received: 8 data bits (LSB first). The baud rate is fixed a 1/12 the oscillator frequency (12-clock mode) or 1/6 the oscillator frequency (6-clock mode).

Figure 14 shows a simplified functional diagram of the serial port in Mode 0, and associated timing.

Transmission is initiated by any instruction that uses SBUF as a destination register. The "write to SBUF" signal at S6P2 also loads a 1 into the 9th position of the transmit shift register and tells the TX Control block to commence a transmission. The internal timing is such that one full machine cycle will elapse between "write to SBUF" and activation of SEND.

SEND enables the output of the shift register to the alternate output function line of P3.0 and also enable SHIFT CLOCK to the alternate output function line of P3.1. SHIFT CLOCK is low during S3, S4, and S5 of every machine cycle, and high during S6, S1, and S2. At

S6P2 of every machine cycle in which SEND is active, the contents of the transmit shift are shifted to the right one position.

As data bits shift out to the right, zeros come in from the left. When the MSB of the data byte is at the output position of the shift register, then the 1 that was initially loaded into the 9th position, is just to the left of the MSB, and all positions to the left of that contain zeros. This condition flags the TX Control block to do one last shift and then deactivate SEND and set T1. Both of these actions occur at S1P1 of the 10th machine cycle after "write to SBUF."

Reception is initiated by the condition REN = 1 and R1 = 0. At S6P2 of the next machine cycle, the RX Control unit writes the bits 1111110 to the receive shift register, and in the next clock phase activates RECEIVE.

RECEIVE enable SHIFT CLOCK to the alternate output function line of P3.1. SHIFT CLOCK makes transitions at S3P1 and S6P1 of every machine cycle. At S6P2 of every machine cycle in which RECEIVE is active, the contents of the receive shift register are

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

shifted to the left one position. The value that comes in from the right is the value that was sampled at the P3.0 pin at S5P2 of the same machine cycle.

As data bits come in from the right, 1s shift out to the left. When the 0 that was initially loaded into the rightmost position arrives at the leftmost position in the shift register, it flags the RX Control block to do one last shift and load SBUF. At S1P1 of the 10th machine cycle after the write to SCON that cleared RI, RECEIVE is cleared as RI is set.

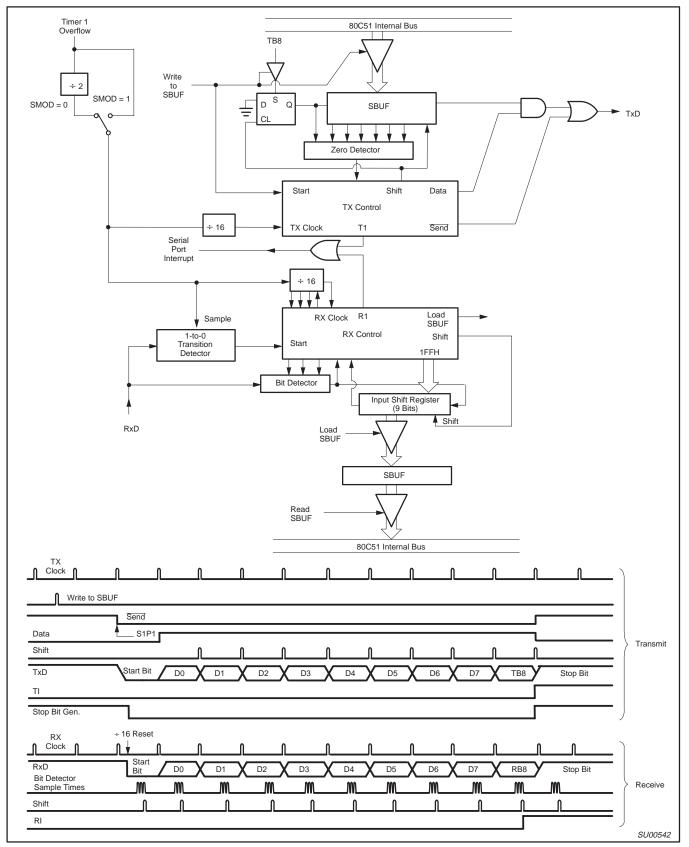

#### More About Mode 1

Ten bits are transmitted (through TxD), or received (through RxD): a start bit (0), 8 data bits (LSB first), and a stop bit (1). On receive, the stop bit goes into RB8 in SCON. In the 80C51 the baud rate is determined by the Timer 1 or Timer 2 overflow rate.

Figure 15 shows a simplified functional diagram of the serial port in Mode 1, and associated timings for transmit receive.

Transmission is initiated by any instruction that uses SBUF as a destination register. The "write to SBUF" signal also loads a 1 into the 9th bit position of the transmit shift register and flags the TX Control unit that a transmission is requested. Transmission actually commences at S1P1 of the machine cycle following the next rollover in the divide-by-16 counter. (Thus, the bit times are synchronized to the divide-by-16 counter, not to the "write to SBUF" signal.)

The transmission begins with activation of SEND which puts the start bit at TxD. One bit time later, DATA is activated, which enables the output bit of the transmit shift register to TxD. The first shift pulse occurs one bit time after that.

As data bits shift out to the right, zeros are clocked in from the left. When the MSB of the data byte is at the output position of the shift register, then the 1 that was initially loaded into the 9th position is just to the left of the MSB, and all positions to the left of that contain zeros. This condition flags the TX Control unit to do one last shift and then deactivate SEND and set TI. This occurs at the 10th divide-by-16 rollover after "write to SBUF."

Reception is initiated by a detected 1-to-0 transition at RxD. For this purpose RxD is sampled at a rate of 16 times whatever baud rate has been established. When a transition is detected, the divide-by-16 counter is immediately reset, and 1FFH is written into the input shift register. Resetting the divide-by-16 counter aligns its rollovers with the boundaries of the incoming bit times.

The 16 states of the counter divide each bit time into 16ths. At the 7th, 8th, and 9th counter states of each bit time, the bit detector samples the value of RxD. The value accepted is the value that was seen in at least 2 of the 3 samples. This is done for noise rejection. If the value accepted during the first bit time is not 0, the receive circuits are reset and the unit goes back to looking for another 1-to-0 transition. This is to provide rejection of false start bits. If the start bit proves valid, it is shifted into the input shift register, and reception of the rest of the frame will proceed.

As data bits come in from the right, 1s shift out to the left. When the start bit arrives at the leftmost position in the shift register (which in mode 1 is a 9-bit register), it flags the RX Control block to do one last shift, load SBUF and RB8, and set RI. The signal to load SBUF and RB8, and to set RI, will be generated if, and only if, the following conditions are met at the time the final shift pulse is generated.: 1. R1 = 0, and

2. Either SM2 = 0, or the received stop bit = 1.

If either of these two conditions is not met, the received frame is irretrievably lost. If both conditions are met, the stop bit goes into RB8, the 8 data bits go into SBUF, and RI is activated. At this time,

whether the above conditions are met or not, the unit goes back to looking for a 1-to-0 transition in RxD.

P89C51RA2/RB2/RC2/RD2xx

#### More About Modes 2 and 3

Eleven bits are transmitted (through TxD), or received (through RxD): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). On transmit, the 9th data bit (TB8) can be assigned the value of 0 or 1. On receive, the 9the data bit goes into RB8 in SCON. The baud rate is programmable to either 1/32 or 1/64 (12-clock mode) or 1/16 or 1/32 the oscillator frequency (6-clock mode) the oscillator frequency in Mode 2. Mode 3 may have a variable baud rate generated from Timer 1 or Timer 2.

Figures 16 and 17 show a functional diagram of the serial port in Modes 2 and 3. The receive portion is exactly the same as in Mode 1. The transmit portion differs from Mode 1 only in the 9th bit of the transmit shift register.

Transmission is initiated by any instruction that uses SBUF as a destination register. The "write to SBUF" signal also loads TB8 into the 9th bit position of the transmit shift register and flags the TX Control unit that a transmission is requested. Transmission commences at S1P1 of the machine cycle following the next rollover in the divide-by-16 counter. (Thus, the bit times are synchronized to the divide-by-16 counter, not to the "write to SBUF" signal.)

The transmission begins with activation of SEND, which puts the start bit at TxD. One bit time later, DATA is activated, which enables the output bit of the transmit shift register to TxD. The first shift pulse occurs one bit time after that. The first shift clocks a 1 (the stop bit) into the 9th bit position of the shift register. Thereafter, only zeros are clocked in. Thus, as data bits shift out to the right, zeros are clocked in from the left. When TB8 is at the output position of the shift register, then the stop bit is just to the left of TB8, and all positions to the left of that contain zeros. This condition flags the TX Control unit to do one last shift and then deactivate SEND and set TI. This occurs at the 11th divide-by-16 rollover after "write to SUBF."

Reception is initiated by a detected 1-to-0 transition at RxD. For this purpose RxD is sampled at a rate of 16 times whatever baud rate has been established. When a transition is detected, the divide-by-16 counter is immediately reset, and 1FFH is written to the input shift register.

At the 7th, 8th, and 9th counter states of each bit time, the bit detector samples the value of R-D. The value accepted is the value that was seen in at least 2 of the 3 samples. If the value accepted during the first bit time is not 0, the receive circuits are reset and the unit goes back to looking for another 1-to-0 transition. If the start bit proves valid, it is shifted into the input shift register, and reception of the rest of the frame will proceed.

As data bits come in from the right, 1s shift out to the left. When the start bit arrives at the leftmost position in the shift register (which in Modes 2 and 3 is a 9-bit register), it flags the RX Control block to do one last shift, load SBUF and RB8, and set RI.

The signal to load SBUF and RB8, and to set RI, will be generated if, and only if, the following conditions are met at the time the final shift pulse is generated.

1. RI = 0, and

2. Either SM2 = 0, or the received 9th data bit = 1.

If either of these conditions is not met, the received frame is irretrievably lost, and RI is not set. If both conditions are met, the received 9th data bit goes into RB8, and the first 8 data bits go into SBUF. One bit time later, whether the above conditions were met or not, the unit goes back to looking for a 1-to-0 transition at the RxD input.

# 80C51 8-bit Flash microcontroller family

Figure 17. Serial Port Mode 3

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

#### Enhanced UART

In addition to the standard operation the UART can perform framing error detect by looking for missing stop bits, and automatic address recognition. The UART also fully supports multiprocessor communication as does the standard 80C51 UART.

When used for framing error detect the UART looks for missing stop bits in the communication. A missing bit will set the FE bit in the SCON register. The FE bit shares the SCON.7 bit with SM0 and the function of SCON.7 is determined by PCON.6 (SMOD0) (see Figure 18). If SMOD0 is set then SCON.7 functions as FE. SCON.7 functions as SM0 when SMOD0 is cleared. When used as FE SCON.7 can only be cleared by software. Refer to Figure 19.

#### Automatic Address Recognition

Automatic Address Recognition is a feature which allows the UART to recognize certain addresses in the serial bit stream by using hardware to make the comparisons. This feature saves a great deal of software overhead by eliminating the need for the software to examine every serial address which passes by the serial port. This feature is enabled by setting the SM2 bit in SCON. In the 9 bit UART modes, mode 2 and mode 3, the Receive Interrupt flag (RI) will be automatically set when the received byte contains either the "Given" address or the "Broadcast" address. The 9-bit mode requires that the 9th information bit is a 1 to indicate that the received information is an address and not data. Automatic address recognition is shown in Figure 20.

The 8 bit mode is called Mode 1. In this mode the RI flag will be set if SM2 is enabled and the information received has a valid stop bit following the 8 address bits and the information is either a Given or Broadcast address.

Mode 0 is the Shift Register mode and SM2 is ignored.

Using the Automatic Address Recognition feature allows a master to selectively communicate with one or more slaves by invoking the Given slave address or addresses. All of the slaves may be contacted by using the Broadcast address. Two special Function Registers are used to define the slave's address, SADDR, and the address mask, SADEN. SADEN is used to define which bits in the SADDR are to b used and which bits are "don't care". The SADEN mask can be logically ANDed with the SADDR to create the "Given" address which the master will use for addressing each of the slaves. Use of the Given address allows multiple slaves to be recognized while excluding others. The following examples will help to show the versatility of this scheme:

| Slave 0 | SADDR | = | 1100 0000        |

|---------|-------|---|------------------|

|         | SADEN | = | <u>1111 1101</u> |

|         | Given | = | 1100 00X0        |

| Slave 1 | SADDR | = | 1100 0000        |

|---------|-------|---|------------------|

|         | SADEN | = | <u>1111 1110</u> |

|         | Given | = | 1100 000X        |

In the above example SADDR is the same and the SADEN data is used to differentiate between the two slaves. Slave 0 requires a 0 in bit 0 and it ignores bit 1. Slave 1 requires a 0 in bit 1 and bit 0 is ignored. A unique address for Slave 0 would be 1100 0010 since slave 1 requires a 0 in bit 1. A unique address for slave 1 would be 1100 0001 since a 1 in bit 0 will exclude slave 0. Both slaves can be selected at the same time by an address which has bit 0 = 0 (for slave 0) and bit 1 = 0 (for slave 1). Thus, both could be addressed with 1100 0000.

P89C51RA2/RB2/RC2/RD2xx

In a more complex system the following could be used to select slaves 1 and 2 while excluding slave 0:

| Slave 0 | SADDR | = | 1100 0000        |

|---------|-------|---|------------------|

|         | SADEN | = | <u>1111 1001</u> |

|         | Given | = | 1100 0XX0        |

| Slave 1 | SADDR | = | 1110 0000        |

|         | SADEN | = | <u>1111 1010</u> |

|         | Given | = | 1110 0X0X        |

| Slave 2 | SADDR | = | 1110 0000        |

|         | SADEN | = | <u>1111 1100</u> |

|         | Given | = | 1110 00XX        |

In the above example the differentiation among the 3 slaves is in the lower 3 address bits. Slave 0 requires that bit 0 = 0 and it can be uniquely addressed by 1110 0110. Slave 1 requires that bit 1 = 0 and it can be uniquely addressed by 1110 and 0101. Slave 2 requires that bit 2 = 0 and its unique address is 1110 0011. To select Slaves 0 and 1 and exclude Slave 2 use address 1110 0100, since it is necessary to make bit 2 = 1 to exclude slave 2.

The Broadcast Address for each slave is created by taking the logical OR of SADDR and SADEN. Zeros in this result are trended as don't-cares. In most cases, interpreting the don't-cares as ones, the broadcast address will be FF hexadecimal.

Upon reset SADDR (SFR address 0A9H) and SADEN (SFR address 0B9H) are leaded with 0s. This produces a given address of all "don't cares" as well as a Broadcast address of all "don't cares". This effectively disables the Automatic Addressing mode and allows the microcontroller to use standard 80C51 type UART drivers which do not make use of this feature.

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

#### **Interrupt Priority Structure**

The P89C51RA2/RB2/RC2/RD2xx has a 7 source four-level interrupt structure (see Table 7).

There are 3 SFRs associated with the four-level interrupt. They are the IE, IP, and IPH. (See Figures 21, 22, and 23.) The IPH (Interrupt Priority High) register makes the four-level interrupt structure possible. The IPH is located at SFR address B7H. The structure of the IPH register and a description of its bits is shown in Figure 23.

The function of the IPH SFR, when combined with the IP SFR, determines the priority of each interrupt. The priority of each interrupt is determined as shown in the following table:

| PRIORI | TY BITS |                            |  |

|--------|---------|----------------------------|--|

| IPH.x  | IP.x    |                            |  |

| 0      | 0       | Level 0 (lowest priority)  |  |

| 0      | 1       | Level 1                    |  |

| 1      | 0       | Level 2                    |  |

| 1      | 1       | Level 3 (highest priority) |  |

The priority scheme for servicing the interrupts is the same as that for the 80C51, except there are four interrupt levels rather than two as on the 80C51. An interrupt will be serviced as long as an interrupt of equal or higher priority is not already being serviced. If an interrupt of equal or higher level priority is being serviced, the new interrupt will wait until it is finished before being serviced. If a lower priority level interrupt is being serviced, it will be stopped and the new interrupt serviced. When the new interrupt is finished, the lower priority level interrupt that was stopped will be completed.

P89C51RA2/RB2/RC2/RD2xx

### Table 7.Interrupt Table

| SOURCE | POLLING PRIORITY | REQUEST BITS        | HARDWARE CLEAR?                       | VECTOR ADDRESS |

|--------|------------------|---------------------|---------------------------------------|----------------|

| X0     | 1                | IE0                 | N (L) <sup>1</sup> Y (T) <sup>2</sup> | 03H            |

| ТО     | 2                | TP0                 | Y                                     | 0BH            |

| X1     | 3                | IE1                 | N (L) Y (T)                           | 13H            |

| T1     | 4                | TF1                 | Y                                     | 1BH            |

| PCA    | 5                | CF, CCFn<br>n = 0–4 | Ν                                     | 33H            |

| SP     | 6                | RI, TI              | N                                     | 23H            |

| T2     | 7                | TF2, EXF2           | N                                     | 2BH            |

NOTES:

1. L = Level activated

2. T = Transition activated

|      | _         | 7      | 6                          | 5                        | 4         | 3                          | 2   | 1   | 0         |

|------|-----------|--------|----------------------------|--------------------------|-----------|----------------------------|-----|-----|-----------|

|      | IE (0A8H) | EA     | EC                         | ET2                      | ES        | ET1                        | EX1 | ET0 | EX0       |

|      |           |        | Bit = 1 ena<br>Bit = 0 dis | ables the i<br>ables it. | nterrupt. |                            |     |     |           |

| BIT  | SYMBOL    | FUNC   | TION                       |                          |           |                            |     |     |           |

| IE.7 | EA        |        |                            |                          |           | rrupts are<br>earing its e |     |     | each inte |

| IE.6 | EC        | PCA ii | nterrupt ei                | nable bit                | -         | -                          |     |     |           |

| IE.5 | ET2       | Timer  | 2 interrup                 | t enable b               | it.       |                            |     |     |           |

| IE.4 | ES        | Serial | Port inter                 | upt enabl                | e bit.    |                            |     |     |           |

| IE.3 | ET1       | Timer  | 1 interrup                 | t enable b               | it.       |                            |     |     |           |

| IE.2 | EX1       | Exterr | al interrup                | ot 1 enable              | e bit.    |                            |     |     |           |

| IE.1 | ET0       | Timer  | 0 interrup                 | t enable b               | it.       |                            |     |     |           |

| IE.0 | EX0       | Exterr | al interrup                | ot 0 enable              | e bit.    |                            |     |     |           |

2002 Jul 18

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

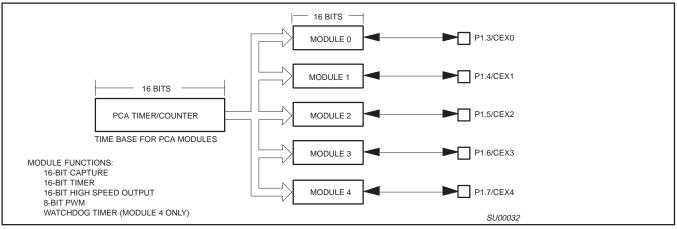

### Programmable Counter Array (PCA)

The Programmable Counter Array available on the P89C51RA2/RB2/RC2/RD2xx is a special 16-bit Timer that has five 16-bit capture/compare modules associated with it. Each of the modules can be programmed to operate in one of four modes: rising and/or falling edge capture, software timer, high-speed output, or pulse width modulator. Each module has a pin associated with it in port 1. Module 0 is connected to P1.3 (CEX0), module 1 to P1.4 (CEX1), etc. The basic PCA configuration is shown in Figure 25.

The PCA timer is a common time base for all five modules and can be programmed to run at: 1/6 the oscillator frequency, 1/2 the oscillator frequency, the Timer 0 overflow, or the input on the ECI pin (P1.2). The timer count source is determined from the CPS1 and CPS0 bits in the CMOD SFR as follows (see Figure 28):

#### CPS1 CPS0 PCA Timer Count Source

- 0 0 1/6 oscillator frequency (6-clock mode); 1/12 oscillator frequency (12-clock mode) 0 1 1/2 oscillator frequency (6-clock mode); 1/4 oscillator frequency (12-clock mode)

- 1 0 Timer 0 overflow

- 1 1 External Input at ECI pin

In the CMOD SFR are three additional bits associated with the PCA. They are CIDL which allows the PCA to stop during idle mode, WDTE which enables or disables the watchdog function on module 4, and ECF which when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows. These functions are shown in Figure 26.

The watchdog timer function is implemented in module 4 (see Figure 35).

The CCON SFR contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (refer to Figure 29). To run the PCA the CR bit (CCON.6) must be set by software. The PCA is shut off by clearing this bit. The CF bit (CCON.7) is set when

the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set, The CF bit can only be cleared by software. Bits 0 through 4 of the CCON register are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software. The PCA interrupt system shown in Figure 27.

P89C51RA2/RB2/RC2/RD2xx

Each module in the PCA has a special function register associated with it. These registers are: CCAPM0 for module 0, CCAPM1 for module 1, etc. (see Figure 30). The registers contain the bits that control the mode that each module will operate in. The ECCF bit (CCAPMn.0 where n=0, 1, 2, 3, or 4 depending on the module) enables the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated module. PWM (CCAPMn.1) enables the pulse width modulation mode. The TOG bit (CCAPMn.2) when set causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the module's capture/compare register. The match bit MAT (CCAPMn.3) when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the module's capture/compare register.

The next two bits CAPN (CCAPMn.4) and CAPP (CCAPMn.5) determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPP bit enables the positive edge. If both bits are set both edges will be enabled and a capture will occur for either transition. The last bit in the register ECOM (CCAPMn.6) when set enables the comparator function. Figure 31 shows the CCAPMn settings for the various PCA functions.

There are two additional registers associated with each of the PCA modules. They are CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a capture occurs or a compare should occur. When a module is used in the PWM mode these registers are used to control the duty cycle of the output.

Figure 25. Programmable Counter Array (PCA)

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

# P89C51RA2/RB2/RC2/RD2xx

| Table 9. | Intel-Hex Records | Used by In-S | ystem Programming |

|----------|-------------------|--------------|-------------------|

|----------|-------------------|--------------|-------------------|

| RECORD TYPE | COMMAND/DATA FUNCTION         Program Data       :nnaaaa00ddddcc         Where:       nn       = number of bytes (hex) in record         aaaa       = memory address of first byte in record         dddd       = data bytes         cc       = checksum         Example:       :10008000AF5F67F0602703E0322CFA92007780C3FD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 00          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 01          | <pre>End of File (EOF), no operation    :xxxxxx01cc Where:    xxxxxx = required field, but value is a "don't care"    cc = checksum Example:    :00000001FF</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| 03          | <pre>Miscellaneous Write Functions<br/>immxxx03ffssddcc<br/>Where:<br/>nn = number of bytes (hex) in record<br/>xxxx = required field, but value is a "don't care"<br/>03 = Write Function<br/>04 = data input (as needed)<br/>05 = selection code<br/>06 = data input (as needed)<br/>07 = checksum<br/>Subfunction Code = 01 (Erase 8K/16K Code Blocks)<br/>07 = checksum<br/>Subfunction Code = 01 (Erase 8K/16K Code Blocks)<br/>07 = 01<br/>08 = block code as shown below:<br/>08 block 0, 0K to 8K, 00H<br/>09 block 1, 8K to 16k, 20H (RB2, RC2, RD2)<br/>00 block 3, 32k to 46k, 80H (RD2 only)<br/>00 block 3, 32k to 46k, 80H (RD2 only)<br/>00 block 3, 32k to 46k, 80H (RD2 only)<br/>01 block 3, 32k to 46k, 80H (RD2 only)<br/>01 block 4, 48k to 64k, COH (RD2 only)<br/>01 ff = 04<br/>03 = don't care<br/>Example:<br/>020000030400F7 erase boot vector and status byte<br/>Subfunction Code = 06 (Program Security Bits)<br/>01 program security bit 1 (inhibit writing to Flash)<br/>01 program security bit 2 (inhibit Flash verify)<br/>02 program security bit 3 (disable external memory)<br/>Example:<br/>02 program security bit 3<br/>Subfunction Code = 06 (Program Status Byte or Boot Vector)<br/>01 ff = 06<br/>05 ss = 00 program status byte or Boot Vector)<br/>02 program becurity bit 3<br/>Subfunction Code = 06 (Program Status Byte or Boot Vector)<br/>03 sr = 00 program status byte<br/>04 program boot vector<br/>05 program boot vector<br/>05 program boot vector with 0FCH<br/>Example 1:<br/>030000030601FCF7 program FX2 bit (select 12-clock mode)</pre> |  |  |  |  |  |  |  |

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

#### In Application Programming Method

Several In Application Programming (IAP) calls are available for use by an application program to permit selective erasing and programming of Flash sectors. All calls are made through a common interface, PGM\_MTP. The programming functions are selected by setting up the microcontroller's registers before making a call to PGM\_MTP at FFF0H. The oscillator frequency is an integer number rounded down to the nearest megahertz. For example, set R0 to 11 for 11.0592 MHz. Results are returned in the registers. The IAP calls are shown in Table 10.

#### Using the Watchdog Timer (WDT)

The P89C51Rx2 devices support the use of the WDT in IAP. The user specifies that the WDT is to be fed by setting the most significant bit of the function parameter passed in R1 prior to calling PGM\_MTP. The WDT function is only supported for Block Erase when using Quick Block Erase. The Quick Block Erase is specified by performing a Block Erase with register R0 = 0. Requesting a WDT feed during IAP should only be performed in applications that use the WDT since the process of feeding the WDT will start the WDT if the WDT was not running.

P89C51RA2/RB2/RC2/RD2xx

| Tab | ole ' | 10. |  | calls |

|-----|-------|-----|--|-------|

|-----|-------|-----|--|-------|

| IAP CALL                              | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROGRAM BYTE                          | <pre>Input Parameter:<br/>R0 = osc freq (integer)<br/>R1 = 02h or R1= 82h (WDT feed)<br/>DPTR = address of byte to program<br/>ACC = byte to program<br/>Return Parameter:<br/>ACC = 00 if pass, !=00 if fail</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ERASE 4K CODE BLOCK<br>(New function) | Input Parameter:<br>R0 = osc freq (integer)<br>R1 = 0Ch or R1 = 8Ch (WDT feed)<br>DPH = address of 4k code block<br>DPH = 00H , 4k block 0, 0k~4k<br>DPH = 10H , 4k block 1, 4k~8k<br>DPH = 20H , 4k block 2, 8k~12k<br>DPH = 30H , 4k block 3, 12k~16k<br>DPH = 40H , 4k block 4, 16k~20k<br>DPH = 50H , 4k block 5, 20k~24k<br>DPH = 60H , 4k block 6, 24k~28k<br>DPH = 70H , 4k block 8, 32k~32k<br>DPH = 80H , 4k block 8, 32k~36k<br>DPH = 90H , 4k block 10, 40k~44k<br>DPH = 80H , 4k block 11, 44k~48k<br>DPH = 80H , 4k block 12, 48k~52k<br>DPH = D0H , 4k block 14, 56k~60k<br>DPH = F0H , 4k block 15, 60k~64k<br>DPL = 00h<br>Return Parameter:<br>ACC = 00 if pass, !=00 if fail |

| ERASE 8K / 16K CODE<br>BLOCK          | <pre>Input Parameter:<br/>R0 = osc freq (integer)<br/>R1 = 01h or R1 = 81h (WDT feed)<br/>DPH = address of code block<br/>DPH = 00H , block 0 , 0k~8k<br/>DPH = 20H , block 1 , 8k~16k<br/>DPH = 40H , block 2 , 16~32k<br/>DPH = 80H , block 3 , 32k~48k<br/>DPH = C0H , block 4 , 48k~64k<br/>DPL = 00h<br/>Return Parameter:<br/>ACC = 00 if pass , !=0 if fail</pre>                                                                                                                                                                                                                                                                                                                       |

| ERASE STATUS BYTE &<br>BOOT VECTOR    | Input Parameter:<br>R0 = osc freq (integer)<br>R1 = 04h or R1 = 84h (WDT feed)<br>DPH = 00h<br>DPL = don't care<br>Return Parameter:<br>ACC = 00 if pass , !=0 if fail                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### 2002 Jul 18

## 80C51 8-bit Flash microcontroller family

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

### **ABSOLUTE MAXIMUM RATINGS1**, 2, 3

| PARAMETER                                                                                    | RATING                 | UNIT |

|----------------------------------------------------------------------------------------------|------------------------|------|

| Operating temperature under bias                                                             | 0 to +70 or -40 to +85 | °C   |

| Storage temperature range                                                                    | -65 to +150            | °C   |

| Voltage on EA/V <sub>PP</sub> pin to V <sub>SS</sub>                                         | 0 to +13.0             | V    |

| Voltage on any other pin to $V_{SS}$                                                         | -0.5 to +6.5           | V    |

| Maximum I <sub>OL</sub> per I/O pin                                                          | 15                     | mA   |

| Power dissipation (based on package heat transfer limitations, not device power consumption) | 1.5                    | W    |

NOTES:

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the AC and DC Electrical Characteristics section of this specification is not implied.

This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum. Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted. 2.

3.

P89C51RA2/RB2/RC2/RD2xx

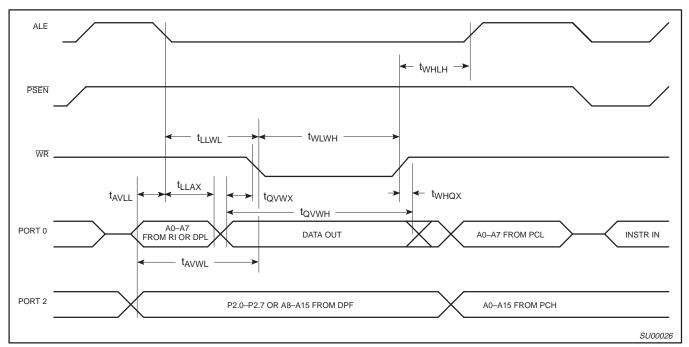

Figure 44. External Data Memory Write Cycle

Figure 45. Shift Register Mode Timing

Figure 46. External Clock Drive

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

P89C51RA2/RB2/RC2/RD2xx

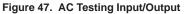

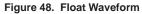

Figure 49.  $I_{CC}$  vs. FREQ Valid only within frequency specifications of the device under test

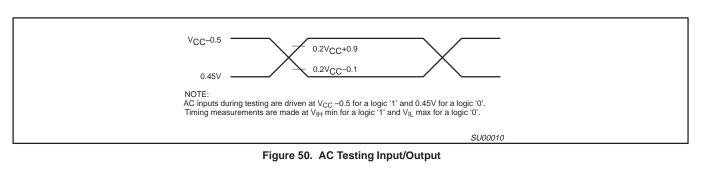

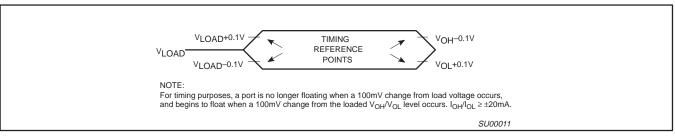

## 80C51 8-bit Flash microcontroller family

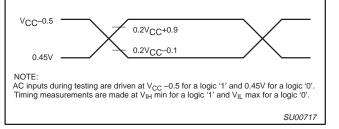

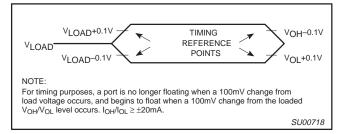

Figure 51. Float Waveform

# 80C51 8-bit Flash microcontroller family

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

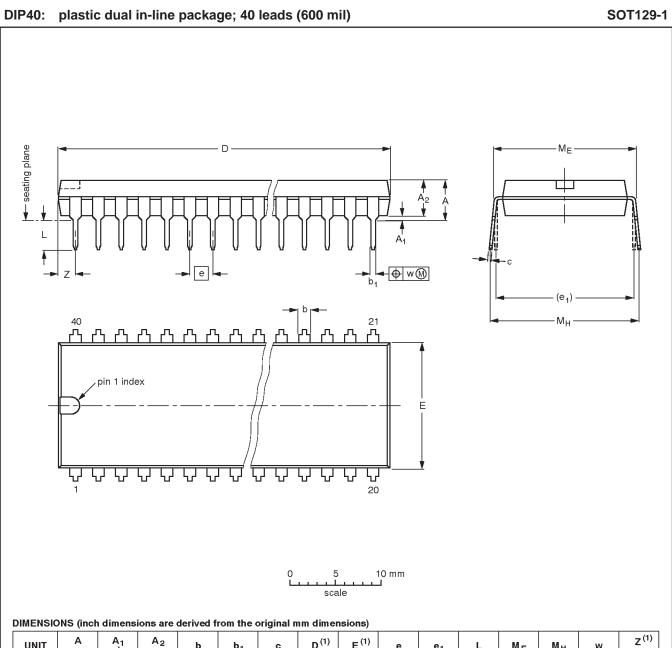

| UN   | П   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | с              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | ME             | M <sub>H</sub> | w     | Z <sup>(1)</sup><br>max. |

|------|-----|-----------|------------------------|------------------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|----------------|----------------|-------|--------------------------|

| m    | m   | 4.7       | 0.51                   | 4.0                    | 1.70<br>1.14   | 0.53<br>0.38   | 0.36<br>0.23   | 52.50<br>51.50   | 14.1<br>13.7     | 2.54 | 15.24          | 3.60<br>3.05 | 15.80<br>15.24 | 17.42<br>15.90 | 0.254 | 2.25                     |

| incł | hes | 0.19      | 0.020                  | 0.16                   | 0.067<br>0.045 | 0.021<br>0.015 | 0.014<br>0.009 | 2.067<br>2.028   | 0.56<br>0.54     | 0.10 | 0.60           | 0.14<br>0.12 | 0.62<br>0.60   | 0.69<br>0.63   | 0.01  | 0.089                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| Γ | OUTLINE  |        | REFER  | EUROPEAN  | ISSUE DATE |            |                                  |  |

|---|----------|--------|--------|-----------|------------|------------|----------------------------------|--|

|   | VERSION  | IEC    | JEDEC  | EIAJ      |            | PROJECTION | ISSUE DATE                       |  |

|   | SOT129-1 | 051G08 | MO-015 | SC-511-40 |            |            | <del>-95-01-14</del><br>99-12-27 |  |

## 80C51 8-bit Flash microcontroller family

## 80C51 8-bit Flash microcontroller family