Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 33MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 512 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LQFP                                                                    |

| Supplier Device Package    | 44-LQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/p89c51rc2fbd-01-55 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 80C51 8-bit Flash microcontroller family 8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

## P89C51RA2/RB2/RC2/RD2xx

#### DESCRIPTION

The P89C51RA2/RB2/RC2/RD2xx contains a non-volatile 8KB/16KB/32KB/64KB Flash program memory that is both parallel programmable and serial In-System and In-Application Programmable. In-System Programming (ISP) allows the user to download new code while the microcontroller sits in the application. In-Application Programming (IAP) means that the microcontroller fetches new program code and reprograms itself while in the system. This allows for remote programming over a modem link. A default serial loader (boot loader) program in ROM allows serial In-System programming of the Flash memory via the UART without the need for a loader in the Flash code. For In-Application Programming, the user program erases and reprograms the Flash memory by use of standard routines contained in ROM.

The device supports 6-clock/12-clock mode selection by programming a Flash bit using parallel programming or In-System Programming. In addition, an SFR bit (X2) in the clock control register (CKCON) also selects between 6-clock/12-clock mode.

Additionally, when in 6-clock mode, peripherals may use either 6 clocks per machine cycle or 12 clocks per machine cycle. This choice is available individually for each peripheral and is selected by bits in the CKCON register.

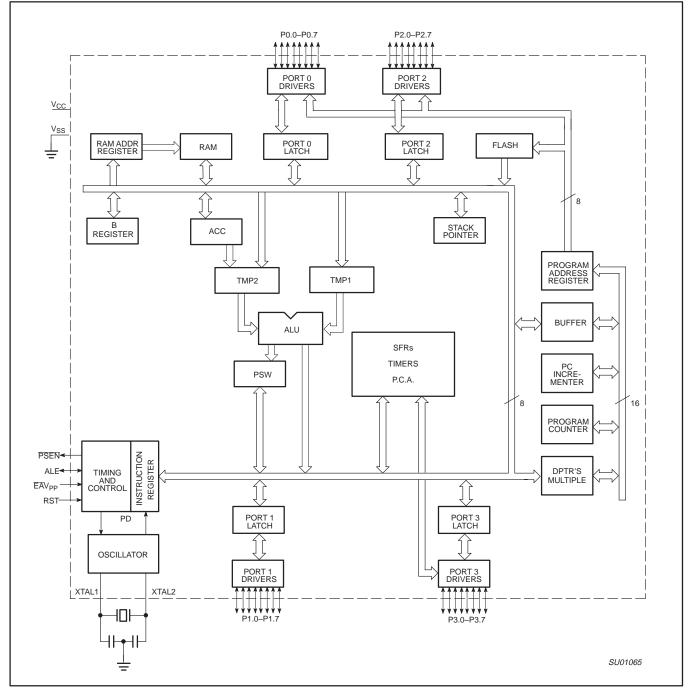

This device is a Single-Chip 8-Bit Microcontroller manufactured in an advanced CMOS process and is a derivative of the 80C51 microcontroller family. The instruction set is 100% compatible with the 80C51 instruction set.

The device also has four 8-bit I/O ports, three 16-bit timer/event counters, a multi-source, four-priority-level, nested interrupt structure, an enhanced UART and on-chip oscillator and timing circuits.

The added features of the P89C51RA2/RB2/RC2/RD2xx make it a powerful microcontroller for applications that require pulse width modulation, high-speed I/O and up/down counting capabilities such as motor control.

#### **FEATURES**

- 80C51 Central Processing Unit

- On-chip Flash Program Memory with In-System Programming (ISP) and In-Application Programming (IAP) capability

- Boot ROM contains low level Flash programming routines for downloading via the UART

- Can be programmed by the end-user application (IAP)

- Parallel programming with 87C51 compatible hardware interface to programmer

- Supports 6-clock/12-clock mode via parallel programmer (default clock mode after ChipErase is 12-clock)

- 6-clock/12-clock mode Flash bit erasable and programmable via ISP

- 6-clock/12-clock mode programmable "on-the-fly" by SFR bit

- Peripherals (PCA, timers, UART) may use either 6-clock or 12-clock mode while the CPU is in 6-clock mode

- Speed up to 20 MHz with 6-clock cycles per machine cycle (40 MHz equivalent performance); up to 33 MHz with 12 clocks per machine cycle

- Fully static operation

- RAM expandable externally to 64 kbytes

- Four interrupt priority levels

- Seven interrupt sources

- Four 8-bit I/O ports

- Full-duplex enhanced UART

- Framing error detection

- Automatic address recognition

- Power control modes

- Clock can be stopped and resumed

- Idle mode

- Power down mode

- Programmable clock-out pin

- Second DPTR register

- Asynchronous port reset

- Low EMI (inhibit ALE)

- Programmable Counter Array (PCA)

- PWM

- Capture/compare

# 80C51 8-bit Flash microcontroller family

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

## SELECTION TABLE

| Туре        |      | Mem | ory | _     |             | Tim          | ers          |              | Iı           | Ser<br>nterf |     | 5   |              |          |                             |                     |                                    |                                     |                           |                                                |                                  |                                  |

|-------------|------|-----|-----|-------|-------------|--------------|--------------|--------------|--------------|--------------|-----|-----|--------------|----------|-----------------------------|---------------------|------------------------------------|-------------------------------------|---------------------------|------------------------------------------------|----------------------------------|----------------------------------|

|             | RAM  | ROM | ОТР | Flash | # of Timers | PWM          | PCA          | MD           | UART         | 12C          | CAN | SPI | ADC bits/ch. | I/O Pins | Interrupts<br>(Ext.)/Levels | Program<br>Security | Default Clock<br>Rate <sup>1</sup> | Optional<br>Clock Rate <sup>1</sup> | Reset active<br>low/high? | Max.<br>Freq.<br>at 6-clk<br>/ 12-clk<br>(MHz) | Freq.<br>Range<br>at 3V<br>(MHz) | Freq.<br>Range<br>at 5V<br>(MHz) |

| P89C51RD2xx | 1K   | -   | -   | 64K   | 4           | $\checkmark$ | V            |              | $\checkmark$ | -            | -   | -   | -            | 32       | 7(2)/4                      | $\checkmark$        | 12-clk                             | 6-clk                               | н                         | 20/33                                          | -                                | 0-20/33                          |

| P89C51RC2xx | 512B | -   | -   | 32K   | 4           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -   | -   | -            | 32       | 7(2)/4                      | V                   | 12-clk                             | 6-clk                               | н                         | 20/33                                          | -                                | 0-20/33                          |

| P89C51RB2xx | 512B | -   | -   | 16K   | 4           | $\checkmark$ | V            |              | $\checkmark$ | -            | -   | -   | -            | 32       | 7(2)/4                      | $\checkmark$        | 12-clk                             | 6-clk                               | Н                         | 20/33                                          | -                                | 0-20/33                          |

| P89C51RA2xx | 512B | -   | -   | 8K    | 4           | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | -            | -   | -   | -            | 32       | 7(2)/4                      | $\checkmark$        | 12-clk                             | 6-clk                               | Н                         | 20/33                                          | -                                | 0-20/33                          |

#### NOTE:

1. P89C51Rx2Hxx devices have a 6-clk default clock rate (12-clk optional). Please also see Device Comparison Table.

### **DEVICE COMPARISON TABLE**

| ltem                       | 1st generation of Rx2 devices                                                                                                          | 2nd generation of Rx2 devices (this data sheet)                                                                                                            | Difference                                                                           |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Type description           | P89C51Rx2 <b>H</b> xx(x)                                                                                                               | P89C51Rx2xx(x)                                                                                                                                             | No more letter 'H'                                                                   |

| Programming algo-<br>rithm | When using a parallel programmer,<br>be sure to select<br>P89C51Rx2 <b>H</b> xx(x) devices                                             | When using a parallel programmer, be<br>sure to select P89C51Rx2xx(x) de-<br>vices (no more letter 'H')                                                    | Different programming algorithm due to process change                                |

| Clock mode (I)             | 6-clk default, OTP configuration bit<br>to program to 12-clk mode using<br>parallel programmer (cannot be<br>programmed back to 6-clk) | <b>12-clk default, Flash</b> configuration bit<br>to program to <b>6-clk</b> mode using paral-<br>lel programmer or ISP ( <b>can</b> be repro-<br>grammed) | More flexibility for the end user,<br>more compatibility to older<br>P89C51Rx+ parts |

| Clock mode (II)            | N/A                                                                                                                                    | 6-clock/12-clock mode programmable<br>"on the fly" by SFR bit X2 (CKCON.0)                                                                                 | Clock mode can be changed by software                                                |

| Peripheral clock<br>modes  | N/A                                                                                                                                    | Peripherals can be run in 12-clk mode while CPU runs in 6-clk mode                                                                                         | More flexibility, lower power con-<br>sumption                                       |

| Flash block structure      | Two 8-Kbyte blocks<br>1–3 16-Kbyte blocks                                                                                              | 2–16 4-Kbyte blocks                                                                                                                                        | More flexibility                                                                     |

## **ORDERING INFORMATION**

|     | PART ORDER          | MEM   | ORY    | TEMPERATURE               | VOLTAGE   | FREQUEN         | ICY (MHz)        |          |

|-----|---------------------|-------|--------|---------------------------|-----------|-----------------|------------------|----------|

|     | NUMBER <sup>1</sup> | FLASH | RAM    | RANGE (°C)<br>AND PACKAGE | RANGE     | 6-CLOCK<br>MODE | 12-CLOCK<br>MODE | DWG #    |

| 1.  | P89C51RA2BA/01      | 8 KB  | 512 B  | 0 to +70, PLCC            | 4.5–5.5 V | 0 to 20 MHz     | 0 to 33 MHz      | SOT187-2 |

| 2.  | P89C51RA2BBD/01     | 8 KB  | 512 B  | 0 to +70, LQFP            | 4.5–5.5 V | 0 to 20 MHz     | 0 to 33 MHz      | SOT389-1 |

| 3.  | P89C51RB2BA/01      | 16 KB | 512 B  | 0 to +70, PLCC            | 4.5–5.5 V | 0 to 20 MHz     | 0 to 33 MHz      | SOT187-2 |

| 4.  | P89C51RB2BBD/01     | 16 KB | 512 B  | 0 to +70, LQFP            | 4.5–5.5 V | 0 to 20 MHz     | 0 to 33 MHz      | SOT389-1 |

| 5.  | P89C51RC2BN/01      | 32 KB | 512 B  | 0 to +70, PDIP            | 4.5–5.5 V | 0 to 20 MHz     | 0 to 33 MHz      | SOT129-1 |

| 6.  | P89C51RC2BA/01      | 32 KB | 512 B  | 0 to +70, PLCC            | 4.5–5.5 V | 0 to 20 MHz     | 0 to 33 MHz      | SOT187-2 |

| 7.  | P89C51RC2FA/01      | 32 KB | 512 B  | -40 to +85, PLCC          | 4.5–5.5 V | 0 to 20 MHz     | 0 to 33 MHz      | SOT187-2 |

| 8.  | P89C51RC2BBD/01     | 32 KB | 512 B  | 0 to +70, LQFP            | 4.5–5.5 V | 0 to 20 MHz     | 0 to 33 MHz      | SOT389-1 |

| 9.  | P89C51RC2FBD/01     | 32 KB | 512 B  | -40 to +85, LQFP          | 4.5–5.5 V | 0 to 20 MHz     | 0 to 33 MHz      | SOT389-1 |

| 10. | P89C51RD2BN/01      | 64 KB | 1024 B | 0 to +70, PDIP            | 4.5–5.5 V | 0 to 20 MHz     | 0 to 33 MHz      | SOT129-1 |

| 11. | P89C51RD2BA/01      | 64 KB | 1024 B | 0 to +70, PLCC            | 4.5–5.5 V | 0 to 20 MHz     | 0 to 33 MHz      | SOT187-2 |

| 12. | P89C51RD2BBD/01     | 64 KB | 1024 B | 0 to +70, LQFP            | 4.5–5.5 V | 0 to 20 MHz     | 0 to 33 MHz      | SOT389-1 |

| 13. | P89C51RD2FA/01      | 64 KB | 1024 B | -40 to +85, PLCC          | 4.5–5.5 V | 0 to 20 MHz     | 0 to 33 MHz      | SOT187-2 |

#### NOTE:

1. The Part Marking will not include the "/01".

P89C51RA2/RB2/RC2/RD2xx

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

## **BLOCK DIAGRAM – CPU ORIENTED**

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

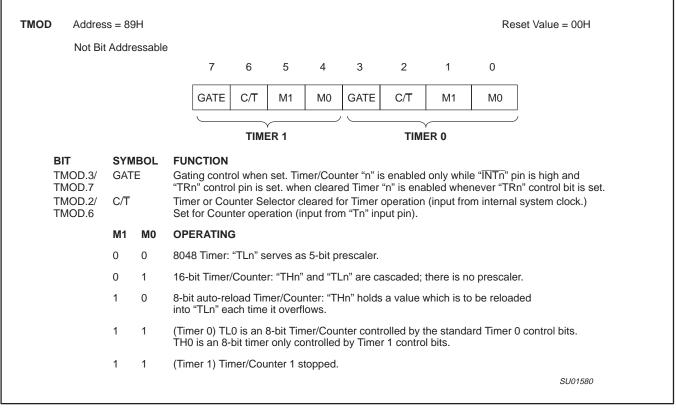

## TIMER 0 AND TIMER 1 OPERATION

#### Timer 0 and Timer 1

The "Timer" or "Counter" function is selected by control bits C/T in the Special Function Register TMOD. These two Timer/Counters have four operating modes, which are selected by bit-pairs (M1, M0) in TMOD. Modes 0, 1, and 2 are the same for both Timers/Counters. Mode 3 is different. The four operating modes are described in the following text.

#### Mode 0

Putting either Timer into Mode 0 makes it look like an 8048 Timer, which is an 8-bit Counter with a divide-by-32 prescaler. Figure 2 shows the Mode 0 operation.

In this mode, the Timer register is configured as a 13-bit register. As the count rolls over from all 1s to all 0s, it sets the Timer interrupt flag TFn. The counted input is enabled to the Timer when TRn = 1 and either GATE = 0 or  $\overline{INTn}$  = 1. (Setting GATE = 1 allows the Timer to be controlled by external input  $\overline{INTn}$ , to facilitate pulse width measurements). TRn is a control bit in the Special Function Register TCON (Figure 3).

The 13-bit register consists of all 8 bits of THn and the lower 5 bits of TLn. The upper 3 bits of TLn are indeterminate and should be ignored. Setting the run flag (TRn) does not clear the registers.

Mode 0 operation is the same for Timer 0 as for Timer 1. There are two different GATE bits, one for Timer 1 (TMOD.7) and one for Timer 0 (TMOD.3).

#### Mode 1

Mode 1 is the same as Mode 0, except that the Timer register is being run with all 16 bits.

P89C51RA2/RB2/RC2/RD2xx

#### Mode 2

Mode 2 configures the Timer register as an 8-bit Counter (TLn) with automatic reload, as shown in Figure 4. Overflow from TLn not only sets TFn, but also reloads TLn with the contents of THn, which is preset by software. The reload leaves THn unchanged.

Mode 2 operation is the same for Timer 0 as for Timer 1.

#### Mode 3

Timer 1 in Mode 3 simply holds its count. The effect is the same as setting TR1 = 0.

Timer 0 in Mode 3 establishes TL0 and TH0 as two separate counters. The logic for Mode 3 on Timer 0 is shown in Figure 5. TL0 uses the Timer 0 control bits:  $C/\overline{T}$ , GATE, TR0, and TF0 as well as pin INT0. TH0 is locked into a timer function (counting machine cycles) and takes over the use of TR1 and TF1 from Timer 1. Thus, TH0 now controls the "Timer 1" interrupt.

Mode 3 is provided for applications requiring an extra 8-bit timer on the counter. With Timer 0 in Mode 3, an 80C51 can look like it has three Timer/Counters. When Timer 0 is in Mode 3, Timer 1 can be turned on and off by switching it out of and into its own Mode 3, or can still be used by the serial port as a baud rate generator, or in fact, in any application not requiring an interrupt.

Figure 1. Timer/Counter 0/1 Mode Control (TMOD) Register

# 80C51 8-bit Flash microcontroller family

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

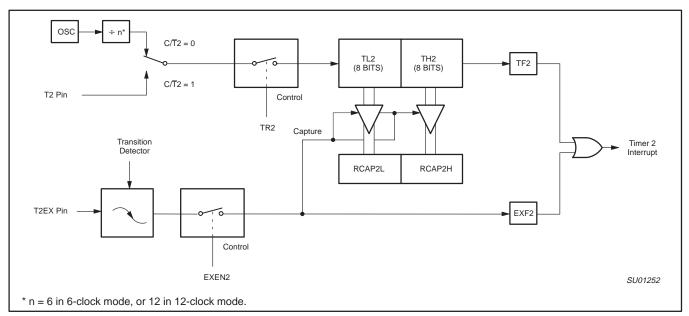

## Table 3. Timer 2 Operating Modes

| RCLK + TCLK | CP/RL2 | TR2 | MODE                |

|-------------|--------|-----|---------------------|

| 0           | 0      | 1   | 16-bit Auto-reload  |

| 0           | 1      | 1   | 16-bit Capture      |

| 1           | Х      | 1   | Baud rate generator |

| Х           | Х      | 0   | (off)               |

Figure 7. Timer 2 in Capture Mode

| Not implemented, reserved for future use.* |  |  |  |  |  |  |  |  |  |  |

|--------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|                                            |  |  |  |  |  |  |  |  |  |  |

|                                            |  |  |  |  |  |  |  |  |  |  |

|                                            |  |  |  |  |  |  |  |  |  |  |

Figure 8. Timer 2 Mode (T2MOD) Control Register

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

When Timer 2 is in the baud rate generator mode, one should not try to read or write TH2 and TL2. As a baud rate generator, Timer 2 is incremented every state time (osc/2) or asynchronously from pin T2; under these conditions, a read or write of TH2 or TL2 may not be accurate. The RCAP2 registers may be read, but should not be written to, because a write might overlap a reload and cause write and/or reload errors. The timer should be turned off (clear TR2) before accessing the Timer 2 or RCAP2 registers.

Table 4 shows commonly used baud rates and how they can be obtained from Timer 2.

### Summary of Baud Rate Equations

Timer 2 is in baud rate generating mode. If Timer 2 is being clocked through pin T2 (P1.0) the baud rate is:

Baud Rate =  $\frac{\text{Timer 2 Overflow Rate}}{16}$

If Timer 2 is being clocked internally, the baud rate is:

Baud Rate =

$$\frac{f_{OSC}}{[n^* \times [65536 - (RCAP2H, RCAP2L)]]}$$

\* n = 16 in 6-clock mode

32 in 12-clock mode

P89C51RA2/RB2/RC2/RD2xx

Where f<sub>OSC</sub>= Oscillator Frequency

To obtain the reload value for RCAP2H and RCAP2L, the above equation can be rewritten as:

$$\text{RCAP2H}, \text{RCAP2L} = 65536 - \left(\frac{f_{OSC}}{n^* \times \text{Baud Rate}}\right)$$

#### **Timer/Counter 2 Set-up**

Except for the baud rate generator mode, the values given for T2CON do not include the setting of the TR2 bit. Therefore, bit TR2 must be set, separately, to turn the timer on. see Table 5 for set-up of Timer 2 as a timer. Also see Table 6 for set-up of Timer 2 as a counter.

## Table 5. Timer 2 as a Timer

|                                                         | T20                          | ON                           |

|---------------------------------------------------------|------------------------------|------------------------------|

| MODE                                                    | INTERNAL CONTROL<br>(Note 1) | EXTERNAL CONTROL<br>(Note 2) |

| 16-bit Auto-Reload                                      | 00H                          | 08H                          |

| 16-bit Capture                                          | 01H                          | 09H                          |

| Baud rate generator receive and transmit same baud rate | 34H                          | 36H                          |

| Receive only                                            | 24H                          | 26H                          |

| Transmit only                                           | 14H                          | 16H                          |

#### Table 6. Timer 2 as a Counter

|             | ТМ                           | OD                           |  |

|-------------|------------------------------|------------------------------|--|

| MODE        | INTERNAL CONTROL<br>(Note 1) | EXTERNAL CONTROL<br>(Note 2) |  |

| 16-bit      | 02H                          | 0AH                          |  |

| Auto-Reload | 03H                          | 0BH                          |  |

NOTES:

1. Capture/reload occurs only on timer/counter overflow.

2. Capture/reload occurs on timer/counter overflow and a 1-to-0 transition on T2EX (P1.1) pin except when Timer 2 is used in the baud rate generator mode.

# 80C51 8-bit Flash microcontroller family

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

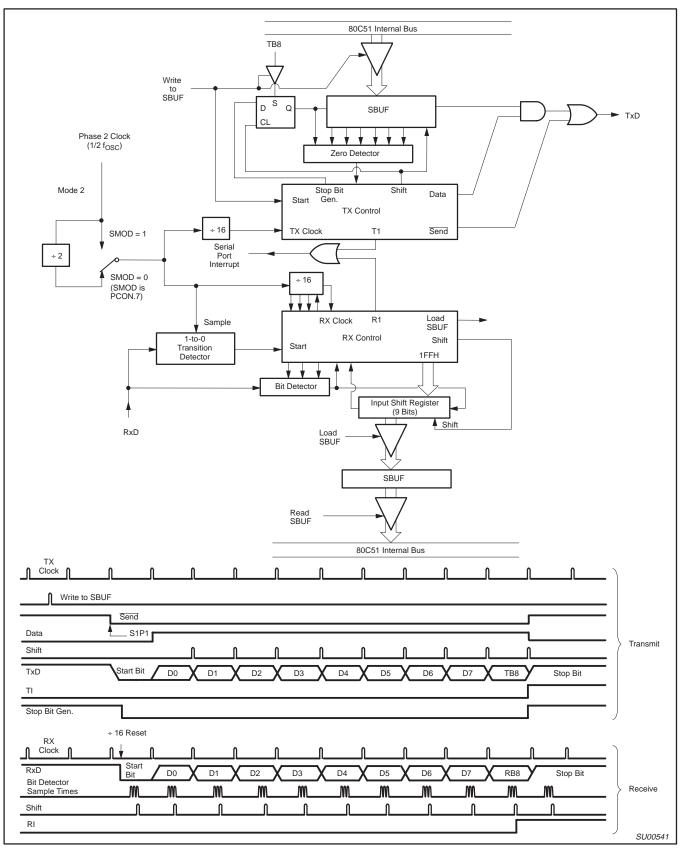

Figure 16. Serial Port Mode 2

# P89C51RA2/RB2/RC2/RD2xx

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

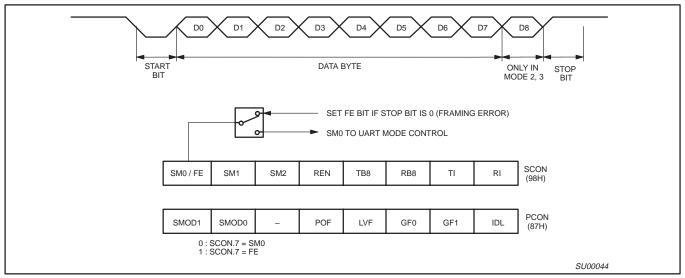

Figure 19. UART Framing Error Detection

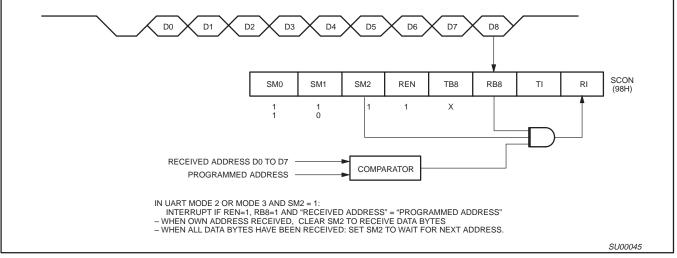

Figure 20. UART Multiprocessor Communication, Automatic Address Recognition

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

#### **Interrupt Priority Structure**

The P89C51RA2/RB2/RC2/RD2xx has a 7 source four-level interrupt structure (see Table 7).

There are 3 SFRs associated with the four-level interrupt. They are the IE, IP, and IPH. (See Figures 21, 22, and 23.) The IPH (Interrupt Priority High) register makes the four-level interrupt structure possible. The IPH is located at SFR address B7H. The structure of the IPH register and a description of its bits is shown in Figure 23.

The function of the IPH SFR, when combined with the IP SFR, determines the priority of each interrupt. The priority of each interrupt is determined as shown in the following table:

| PRIORI | TY BITS |                            |

|--------|---------|----------------------------|

| IPH.x  | IP.x    |                            |

| 0      | 0       | Level 0 (lowest priority)  |

| 0      | 1       | Level 1                    |

| 1      | 0       | Level 2                    |

| 1      | 1       | Level 3 (highest priority) |

The priority scheme for servicing the interrupts is the same as that for the 80C51, except there are four interrupt levels rather than two as on the 80C51. An interrupt will be serviced as long as an interrupt of equal or higher priority is not already being serviced. If an interrupt of equal or higher level priority is being serviced, the new interrupt will wait until it is finished before being serviced. If a lower priority level interrupt is being serviced, it will be stopped and the new interrupt serviced. When the new interrupt is finished, the lower priority level interrupt that was stopped will be completed.

P89C51RA2/RB2/RC2/RD2xx

## Table 7.Interrupt Table

| SOURCE | POLLING PRIORITY | REQUEST BITS        | HARDWARE CLEAR?                       | VECTOR ADDRESS |

|--------|------------------|---------------------|---------------------------------------|----------------|

| X0     | 1                | IE0                 | N (L) <sup>1</sup> Y (T) <sup>2</sup> | 03H            |

| ТО     | 2                | TP0                 | Y                                     | 0BH            |

| X1     | 3                | IE1                 | N (L) Y (T)                           | 13H            |

| T1     | 4                | TF1                 | Y                                     | 1BH            |

| PCA    | 5                | CF, CCFn<br>n = 0–4 | Ν                                     | 33H            |

| SP     | 6                | RI, TI              | N                                     | 23H            |

| T2     | 7                | TF2, EXF2           | N                                     | 2BH            |

NOTES:

1. L = Level activated

2. T = Transition activated

|      | _         | 7      | 6                                                                                                                                                                   | 5                        | 4         | 3   | 2   | 1   | 0   |  |  |  |

|------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------|-----|-----|-----|-----|--|--|--|

|      | IE (0A8H) | EA     | EC                                                                                                                                                                  | ET2                      | ES        | ET1 | EX1 | ET0 | EX0 |  |  |  |

|      |           |        | Bit = 1 ena<br>Bit = 0 dis                                                                                                                                          | ables the i<br>ables it. | nterrupt. |     |     |     |     |  |  |  |

| BIT  | SYMBOL    | FUNC   | TION                                                                                                                                                                |                          |           |     |     |     |     |  |  |  |

| IE.7 | EA        |        | Slobal disable bit. If EA = 0, all interrupts are disabled. If EA = 1, each interrupt can be individually nabled or disabled by setting or clearing its enable bit. |                          |           |     |     |     |     |  |  |  |

| IE.6 | EC        | PCA ii | nterrupt ei                                                                                                                                                         | nable bit                | -         | -   |     |     |     |  |  |  |

| IE.5 | ET2       | Timer  | Timer 2 interrupt enable bit.                                                                                                                                       |                          |           |     |     |     |     |  |  |  |

| IE.4 | ES        | Serial | Port inter                                                                                                                                                          | upt enabl                | e bit.    |     |     |     |     |  |  |  |

| IE.3 | ET1       | Timer  | 1 interrup                                                                                                                                                          | t enable b               | it.       |     |     |     |     |  |  |  |

| IE.2 | EX1       | Exterr | al interrup                                                                                                                                                         | ot 1 enable              | e bit.    |     |     |     |     |  |  |  |

| IE.1 | ET0       | Timer  | Timer 0 interrupt enable bit.                                                                                                                                       |                          |           |     |     |     |     |  |  |  |

| IE.0 | EX0       | Exterr | al interrup                                                                                                                                                         | ot 0 enable              | e bit.    |     |     |     |     |  |  |  |

2002 Jul 18

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

#### Reduced EMI Mode

The AO bit (AUXR.0) in the AUXR register when set disables the ALE output unless the CPU needs to perform an off-chip memory access.

#### **Reduced EMI Mode**

#### AUXR (8EH)

| 7                | 6 | 5            | 4 | 3 | 2 | 1      | 0  | _ |

|------------------|---|--------------|---|---|---|--------|----|---|

| -                | - | -            | - | - | - | EXTRAM | AO |   |

| AUXR.1<br>AUXR.0 |   | EXTRAN<br>AO | 1 |   |   |        |    | - |

See more detailed description in Figure 38.

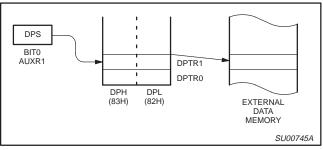

#### **Dual DPTR**

The dual DPTR structure (see Figure 24) is a way by which the chip will specify the address of an external data memory location. There are two 16-bit DPTR registers that address the external memory, and a single bit called DPS = AUXR1/bit0 that allows the program code to switch between them.

- New Register Name: AUXR1#

- SFR Address: A2H

- Reset Value: xxxxxx0B

DPTR1

#### AUXR1 (A2H)

| 7             | 6                                                              | 5      | 4 3 2 |     | 2 | 1 | 0   |  |  |

|---------------|----------------------------------------------------------------|--------|-------|-----|---|---|-----|--|--|

| -             | -                                                              | ENBOOT | -     | GF2 | 0 | - | DPS |  |  |

| Where:<br>DPS | Where:<br>DPS = AUXR1/bit0 = Switches between DPTR0 and DPTR1. |        |       |     |   |   |     |  |  |

|               | Select Reg DPS                                                 |        |       |     |   |   |     |  |  |

|               | DPTR0 0                                                        |        |       |     |   |   |     |  |  |

The DPS bit status should be saved by software when switching between DPTR0 and DPTR1.

The GF2 bit is a general purpose user-defined flag. Note that bit 2 is not writable and is always read as a zero. This allows the DPS bit to

1

be quickly toggled simply by executing an INC AUXR1 instruction without affecting the GF2 bit.

P89C51RA2/RB2/RC2/RD2xx

The ENBOOT bit determines whether the BOOTROM is enabled or disabled. This bit will automatically be set if the status byte is non zero during reset or  $\overrightarrow{\text{PSEN}}$  is pulled low, ALE floats high, and EA > V<sub>IH</sub> on the falling edge of reset. Otherwise, this bit will be cleared during reset.

Figure 24.

#### **DPTR Instructions**

The instructions that refer to DPTR refer to the data pointer that is currently selected using the AUXR1/bit 0 register. The six instructions that use the DPTR are as follows:

| INC DPTR          | Increments the data pointer by 1          |

|-------------------|-------------------------------------------|

| MOV DPTR, #data16 | Loads the DPTR with a 16-bit constant     |

| MOV A, @ A+DPTR   | Move code byte relative to DPTR to ACC    |

| MOVX A, @ DPTR    | Move external RAM (16-bit address) to ACC |

| MOVX @ DPTR , A   | Move ACC to external RAM (16-bit address) |

| JMP @ A + DPTR    | Jump indirect relative to DPTR            |

The data pointer can be accessed on a byte-by-byte basis by specifying the low or high byte in an instruction which accesses the SFRs. See *Application Note AN458* for more details.

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

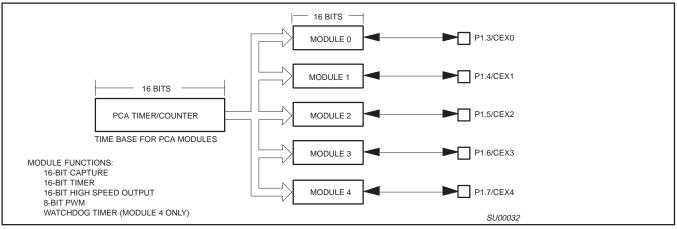

## Programmable Counter Array (PCA)

The Programmable Counter Array available on the P89C51RA2/RB2/RC2/RD2xx is a special 16-bit Timer that has five 16-bit capture/compare modules associated with it. Each of the modules can be programmed to operate in one of four modes: rising and/or falling edge capture, software timer, high-speed output, or pulse width modulator. Each module has a pin associated with it in port 1. Module 0 is connected to P1.3 (CEX0), module 1 to P1.4 (CEX1), etc. The basic PCA configuration is shown in Figure 25.

The PCA timer is a common time base for all five modules and can be programmed to run at: 1/6 the oscillator frequency, 1/2 the oscillator frequency, the Timer 0 overflow, or the input on the ECI pin (P1.2). The timer count source is determined from the CPS1 and CPS0 bits in the CMOD SFR as follows (see Figure 28):

#### CPS1 CPS0 PCA Timer Count Source

- 0 0 1/6 oscillator frequency (6-clock mode); 1/12 oscillator frequency (12-clock mode) 0 1 1/2 oscillator frequency (6-clock mode); 1/4 oscillator frequency (12-clock mode)

- 1 0 Timer 0 overflow

- 1 1 External Input at ECI pin

In the CMOD SFR are three additional bits associated with the PCA. They are CIDL which allows the PCA to stop during idle mode, WDTE which enables or disables the watchdog function on module 4, and ECF which when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows. These functions are shown in Figure 26.

The watchdog timer function is implemented in module 4 (see Figure 35).

The CCON SFR contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (refer to Figure 29). To run the PCA the CR bit (CCON.6) must be set by software. The PCA is shut off by clearing this bit. The CF bit (CCON.7) is set when

the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set, The CF bit can only be cleared by software. Bits 0 through 4 of the CCON register are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software. The PCA interrupt system shown in Figure 27.

P89C51RA2/RB2/RC2/RD2xx

Each module in the PCA has a special function register associated with it. These registers are: CCAPM0 for module 0, CCAPM1 for module 1, etc. (see Figure 30). The registers contain the bits that control the mode that each module will operate in. The ECCF bit (CCAPMn.0 where n=0, 1, 2, 3, or 4 depending on the module) enables the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated module. PWM (CCAPMn.1) enables the pulse width modulation mode. The TOG bit (CCAPMn.2) when set causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the module's capture/compare register. The match bit MAT (CCAPMn.3) when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the module's capture/compare register.

The next two bits CAPN (CCAPMn.4) and CAPP (CCAPMn.5) determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPP bit enables the positive edge. If both bits are set both edges will be enabled and a capture will occur for either transition. The last bit in the register ECOM (CCAPMn.6) when set enables the comparator function. Figure 31 shows the CCAPMn settings for the various PCA functions.

There are two additional registers associated with each of the PCA modules. They are CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a capture occurs or a compare should occur. When a module is used in the PWM mode these registers are used to control the duty cycle of the output.

Figure 25. Programmable Counter Array (PCA)

SU01320

## 80C51 8-bit Flash microcontroller family

## P89C51RA2/RB2/RC2/RD2xx

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

| CCAPMn | Address | CCA<br>CCA<br>CCA<br>CCA<br>CCA                                                                                                                                                                                    | PM1 0DE<br>PM2 0D0<br>PM3 0DE | SH<br>CH<br>DH |              |               |              |             | R            | eset Value = X000 0000E |

|--------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------|--------------|---------------|--------------|-------------|--------------|-------------------------|

|        | Not Bi  | t Addressa                                                                                                                                                                                                         | able                          |                |              |               |              |             |              |                         |

|        |         | -                                                                                                                                                                                                                  | ECOMn                         | CAPPn          | CAPNn        | MATn          | TOGn         | PWMn        | ECCFn        |                         |

|        | Bit:    | 7                                                                                                                                                                                                                  | 6                             | 5              | 4            | 3             | 2            | 1           | 0            | 7                       |

| Symbol | Fund    | tion                                                                                                                                                                                                               |                               |                |              |               |              |             |              |                         |

| _      | Not i   | Not implemented, reserved for future use*.                                                                                                                                                                         |                               |                |              |               |              |             |              |                         |

| ECOMn  | Enab    | le Compa                                                                                                                                                                                                           | rator. ECOM                   | n = 1 enabl    | es the com   | parator fund  | ction.       |             |              |                         |

| CAPPn  | Capt    | ure Positiv                                                                                                                                                                                                        | e, CAPPn =                    | 1 enables      | positive edg | je capture.   |              |             |              |                         |

| CAPNn  | Capt    | ure Negati                                                                                                                                                                                                         | ve, CAPNn :                   | = 1 enables    | negative e   | dge capture   | ).           |             |              |                         |

| MATn   |         | Match. When MATn = 1, a match of the PCA counter with this module's compare/capture register causes the CCFn bit in CCON to be set, flagging an interrupt.                                                         |                               |                |              |               |              |             |              |                         |

| TOGn   |         | le. When T<br>toggle.                                                                                                                                                                                              | 「OGn = 1, a                   | match of th    | e PCA cour   | nter with thi | s module's   | compare/ca  | apture regis | ter causes the CEXn     |

|        | Pulse   | e Width Mo                                                                                                                                                                                                         | dulation Mo                   | de. PWMn       | = 1 enables  | the CEXn      | pin to be us | sed as a pu | lse width me | odulated output.        |

| PWMn   |         | Pulse Width Modulation Mode. PWMn = 1 enables the CEXn pin to be used as a pulse width modulated output.<br>Enable CCF interrupt. Enables compare/capture flag CCFn in the CCON register to generate an interrupt. |                               |                |              |               |              |             |              |                         |

\*User software should not write 1s to reserved bits. These bits may be used in future 8051 family products to invoke new features In that case, the reset or inactive value of the new bit will be 0, and its active value will be 1. The value read from a reserved bit is indeterminate.

Figure 30. CCAPMn: PCA Modules Compare/Capture Registers

| - | ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMn | ECCFn | MODULE FUNCTION                                   |

|---|-------|-------|-------|------|------|------|-------|---------------------------------------------------|

| Х | 0     | 0     | 0     | 0    | 0    | 0    | 0     | No operation                                      |

| Х | Х     | 1     | 0     | 0    | 0    | 0    | Х     | 16-bit capture by a positive-edge trigger on CEXn |

| Х | Х     | 0     | 1     | 0    | 0    | 0    | Х     | 16-bit capture by a negative trigger on CEXn      |

| Х | Х     | 1     | 1     | 0    | 0    | 0    | Х     | 16-bit capture by a transition on CEXn            |

| Х | 1     | 0     | 0     | 1    | 0    | 0    | Х     | 16-bit Software Timer                             |

| Х | 1     | 0     | 0     | 1    | 1    | 0    | Х     | 16-bit High Speed Output                          |

| Х | 1     | 0     | 0     | 0    | 0    | 1    | 0     | 8-bit PWM                                         |

| Х | 1     | 0     | 0     | 1    | Х    | 0    | Х     | Watchdog Timer                                    |

Figure 31. PCA Module Modes (CCAPMn Register)

#### PCA Capture Mode

To use one of the PCA modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated. Refer to Figure 32.

#### 16-bit Software Timer Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (see Figure 33).

#### **High Speed Output Mode**

In this mode the CEX output (on port 1) associated with the PCA module will toggle each time a match occurs between the PCA

counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set (see Figure 34).

#### Pulse Width Modulator Mode

All of the PCA modules can be used as PWM outputs. Figure 35 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. the allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

| IAP CALL                        | PARAMETER                                                                                                                                                                                              |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READ DEVICE ID #1               | Input Parameter:<br>R0 = osc freq (integer)<br>R1 = 00h or R1 = 80h (WDT feed)<br>DPH = 00h<br>DPL = 01h - read device ID #1<br>Return Parameter:<br>ACC = value of byte read                          |

| READ DEVICE ID #2               | Input Parameter:<br>R0 = osc freq (integer)<br>R1 = 00h or R1 = 80h (WDT feed)<br>DPH = 00h<br>DPL = 02h - read device ID #2<br>Return Parameter:<br>ACC = value of byte read                          |

| READ SECURITY BITS              | Input Parameter:<br>R0 = osc freq (integer)<br>R1 = 07h or R1 = 87h (WDT feed)<br>DPH = 00h<br>DPL = 00h - read lock byte<br>Return Parameter:<br>ACC = value of byte read                             |

| READ STATUS BYTE                | Input Parameter:<br>R0 = osc freq (integer)<br>R1 = 07h or R1 = 87h (WDT feed)<br>DPH = 00h<br>DPL = 01h - read status byte<br>Return Parameter:<br>ACC = value of byte read                           |

| READ BOOT VECTOR                | Input Parameter:<br>R0 = osc freq (integer)<br>R1 = 07h or R1 = 87h (WDT feed)<br>DPH = 00h<br>DPL = 02h - read boot vector<br>Return Parameter:<br>ACC = value of byte read                           |

| READ CONFIG<br>(New function)   | Input Parameter:<br>R0 = osc freq (integer)<br>R1 = 00h or R1 = 80h (WDT feed)<br>DPH = 00h<br>DPL = 03h - read config byte<br>Return Parameter:<br>ACC = value of byte read                           |

| READ REVISION<br>(New function) | <pre>Input Parameter:<br/>R0 = osc freq (integer)<br/>R1 = 00h or R1 = 80h (WDT feed)<br/>DPH = 00h<br/>DPL = 80h - read revision of ROM Code<br/>Return Parameter:<br/>ACC = value of byte read</pre> |

# 80C51 8-bit Flash microcontroller family

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

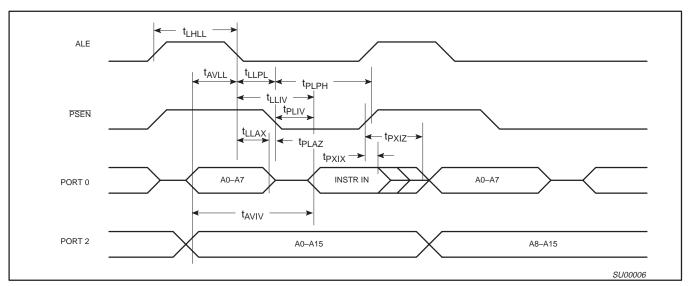

# AC ELECTRICAL CHARACTERISTICS (12-CLOCK MODE) $T_{amb} = 0 \ ^{\circ}C \ to \ +70 \ ^{\circ}C \ or \ -40 \ ^{\circ}C \ to \ +85 \ ^{\circ}C; \ V_{CC} = 5 \ V \pm 10\%, \ V_{SS} = 0 \ V^{1, \ 2, \ 3}$

|                     |        |                                          | VARIABL                  | VARIABLE CLOCK <sup>4</sup>          |     |     | 1         |

|---------------------|--------|------------------------------------------|--------------------------|--------------------------------------|-----|-----|-----------|

| SYMBOL              | FIGURE | PARAMETER                                | MIN                      | MAX                                  | MIN | MAX |           |

| 1/t <sub>CLCL</sub> | 42     | Oscillator frequency                     | 0                        | 33                                   |     |     | MHz       |

| t <sub>LHLL</sub>   | 42     | ALE pulse width                          | 2t <sub>CLCL</sub> -40   |                                      | 21  |     | ns        |

| t <sub>AVLL</sub>   | 42     | Address valid to ALE low                 | t <sub>CLCL</sub> -25    |                                      | 5   |     | ns        |

| t <sub>LLAX</sub>   | 42     | Address hold after ALE low               | t <sub>CLCL</sub> -25    |                                      | 5   |     | ns        |

| t <sub>LLIV</sub>   | 42     | ALE low to valid instruction in          |                          | 4t <sub>CLCL</sub> –65               |     | 55  | ns        |

| t <sub>LLPL</sub>   | 42     | ALE low to PSEN low                      | t <sub>CLCL</sub> –25    |                                      | 5   |     | ns        |

| t <sub>PLPH</sub>   | 42     | PSEN pulse width                         | 3t <sub>CLCL</sub> -45   |                                      | 45  |     | ns        |

| t <sub>PLIV</sub>   | 42     | PSEN low to valid instruction in         |                          | 3t <sub>CLCL</sub> -60               |     | 30  | ns        |

| t <sub>PXIX</sub>   | 42     | Input instruction hold after PSEN        | 0                        |                                      | 0   |     | ns        |

| t <sub>PXIZ</sub>   | 42     | Input instruction float after PSEN       |                          | t <sub>CLCL</sub> -25                |     | 5   | ns        |

| t <sub>AVIV</sub>   | 42     | Address to valid instruction in          |                          | 5t <sub>CLCL</sub> -80               |     | 70  | ns        |

| t <sub>PLAZ</sub>   | 42     | PSEN low to address float                |                          | 10                                   |     | 10  | ns        |

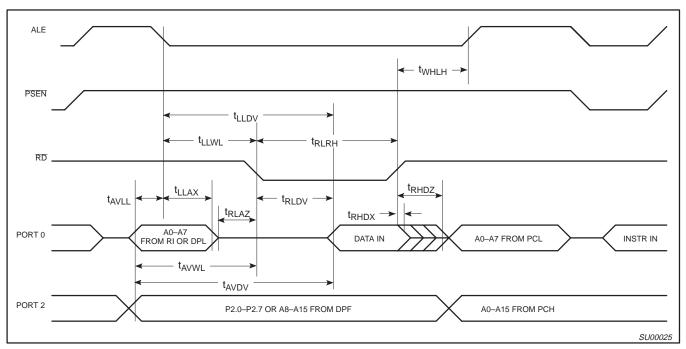

| Data Mem            | ory    | •                                        | •                        |                                      |     |     | · · · · · |

| t <sub>RLRH</sub>   | 43, 44 | RD pulse width                           | 6t <sub>CLCL</sub> -100  |                                      | 82  |     | ns        |

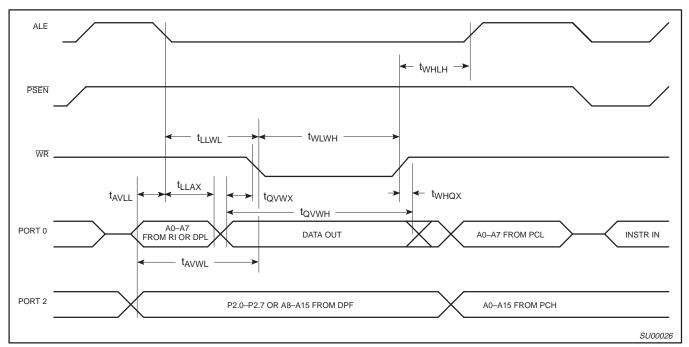

| t <sub>WLWH</sub>   | 43, 44 | WR pulse width                           | 6t <sub>CLCL</sub> -100  |                                      | 82  |     | ns        |

| t <sub>RLDV</sub>   | 43, 44 | RD low to valid data in                  |                          | 5t <sub>CLCL</sub> –90               |     | 60  | ns        |

| t <sub>RHDX</sub>   | 43, 44 | Data hold after RD                       | 0                        |                                      | 0   |     | ns        |

| t <sub>RHDZ</sub>   | 43, 44 | Data float after RD                      |                          | 2t <sub>CLCL</sub> -28               |     | 32  | ns        |

| t <sub>LLDV</sub>   | 43, 44 | ALE low to valid data in                 |                          | 8t <sub>CLCL</sub> -150              |     | 90  | ns        |

| t <sub>AVDV</sub>   | 43, 44 | Address to valid data in                 |                          | 9t <sub>CLCL</sub> -165              |     | 105 | ns        |

| t <sub>LLWL</sub>   | 43, 44 | ALE low to RD or WR low                  | 3t <sub>CLCL</sub> -50   | 3t <sub>CLCL</sub> +50               | 40  | 140 | ns        |

| t <sub>AVWL</sub>   | 43, 44 | Address valid to WR low or RD low        | 4t <sub>CLCL</sub> -75   |                                      | 45  |     | ns        |

| t <sub>QVWX</sub>   | 43, 44 | Data valid to WR transition              | t <sub>CLCL</sub> -30    |                                      | 0   |     | ns        |

| t <sub>WHQX</sub>   | 43, 44 | Data hold after WR                       | t <sub>CLCL</sub> -25    |                                      | 5   |     | ns        |

| t <sub>QVWH</sub>   | 44     | Data valid to WR high                    | 7t <sub>CLCL</sub> -130  |                                      | 80  |     | ns        |

| t <sub>RLAZ</sub>   | 43, 44 | RD low to address float                  |                          | 0                                    |     | 0   | ns        |

| t <sub>WHLH</sub>   | 43, 44 | RD or WR high to ALE high                | t <sub>CLCL</sub> -25    | t <sub>CLCL</sub> +25                | 5   | 55  | ns        |

| External C          | lock   | •                                        | •                        | •                                    |     |     |           |

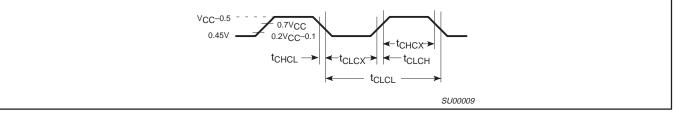

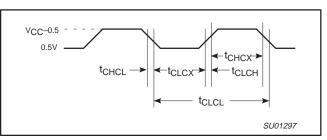

| t <sub>CHCX</sub>   | 46     | High time                                | 17                       | t <sub>CLCL</sub> -t <sub>CLCX</sub> |     |     | ns        |

| t <sub>CLCX</sub>   | 46     | Low time                                 | 17                       | t <sub>CLCL</sub> -t <sub>CHCX</sub> |     |     | ns        |

| t <sub>CLCH</sub>   | 46     | Rise time                                |                          | 5                                    |     |     | ns        |

| t <sub>CHCL</sub>   | 46     | Fall time                                |                          | 5                                    |     |     | ns        |

| Shift Regi          | ster   | •                                        | ·                        |                                      |     | •   |           |

| t <sub>XLXL</sub>   | 45     | Serial port clock cycle time             | 12t <sub>CLCL</sub>      |                                      | 360 |     | ns        |

| t <sub>QVXH</sub>   | 45     | Output data setup to clock rising edge   | 10t <sub>CLCL</sub> -133 |                                      | 167 |     | ns        |

| t <sub>XHQX</sub>   | 45     | Output data hold after clock rising edge | 2t <sub>CLCL</sub> -80   |                                      | 50  |     | ns        |

| t <sub>XHDX</sub>   | 45     | Input data hold after clock rising edge  | 0                        |                                      | 0   |     | ns        |

| t <sub>XHDV</sub>   | 45     | Clock rising edge to input data valid    |                          | 10t <sub>CLCL</sub> -133             |     | 167 | ns        |

NOTES:

Parameters are valid over operating temperature range unless otherwise specified.

Load capacitance for port 0, ALE, and PSEN = 100 pF, load capacitance for all other outputs = 80 pF.

3. Interfacing the microcontroller to devices with float times up to 45 ns is permitted. This limited bus contention will not cause damage to Port 0 drivers.

4. Parts are tested to 3.5 MHz, but guaranteed to operate down to 0 Hz.

# 80C51 8-bit Flash microcontroller family

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

# AC ELECTRICAL CHARACTERISTICS (6-CLOCK MODE) $T_{amb} = 0 \ ^{\circ}C \ to \ +70 \ ^{\circ}C \ or \ -40 \ ^{\circ}C \ to \ +85 \ ^{\circ}C; \ V_{CC} = 5 \ V \pm 10\%, \ V_{SS} = 0 \ V^{1, 2, 3}$

|                     |        |                                          | VARIABL                   | E CLOCK <sup>4</sup>                 | 20 MHz | 1   |     |

|---------------------|--------|------------------------------------------|---------------------------|--------------------------------------|--------|-----|-----|

| SYMBOL              | FIGURE | PARAMETER                                | MIN                       | MAX                                  | MIN    | MAX |     |

| 1/t <sub>CLCL</sub> | 42     | Oscillator frequency                     | 0                         | 20                                   |        |     | MHz |

| t <sub>LHLL</sub>   | 42     | ALE pulse width                          | t <sub>CLCL</sub> -40     |                                      | 10     |     | ns  |

| t <sub>AVLL</sub>   | 42     | Address valid to ALE low                 | 0.5t <sub>CLCL</sub> -20  |                                      | 5      |     | ns  |

| t <sub>LLAX</sub>   | 42     | Address hold after ALE low               | 0.5t <sub>CLCL</sub> -20  |                                      | 5      |     | ns  |

| t <sub>LLIV</sub>   | 42     | ALE low to valid instruction in          |                           | 2t <sub>CLCL</sub> -65               |        | 35  | ns  |

| t <sub>LLPL</sub>   | 42     | ALE low to PSEN low                      | 0.5t <sub>CLCL</sub> -20  |                                      | 5      |     | ns  |

| t <sub>PLPH</sub>   | 42     | PSEN pulse width                         | 1.5t <sub>CLCL</sub> -45  |                                      | 30     |     | ns  |

| t <sub>PLIV</sub>   | 42     | PSEN low to valid instruction in         |                           | 1.5t <sub>CLCL</sub> -60             |        | 15  | ns  |

| t <sub>PXIX</sub>   | 42     | Input instruction hold after PSEN        | 0                         |                                      | 0      |     | ns  |

| t <sub>PXIZ</sub>   | 42     | Input instruction float after PSEN       |                           | 0.5t <sub>CLCL</sub> -20             |        | 5   | ns  |

| t <sub>AVIV</sub>   | 42     | Address to valid instruction in          |                           | 2.5t <sub>CLCL</sub> -80             |        | 45  | ns  |

| t <sub>PLAZ</sub>   | 42     | PSEN low to address float                |                           | 10                                   |        | 10  | ns  |

| Data Mem            | ory    | •                                        | •                         |                                      |        |     |     |

| t <sub>RLRH</sub>   | 43, 44 | RD pulse width                           | 3t <sub>CLCL</sub> -100   |                                      | 50     |     | ns  |

| t <sub>WLWH</sub>   | 43, 44 | WR pulse width                           | 3t <sub>CLCL</sub> -100   |                                      | 50     |     | ns  |

| t <sub>RLDV</sub>   | 43, 44 | RD low to valid data in                  |                           | 2.5t <sub>CLCL</sub> -90             |        | 35  | ns  |

| t <sub>RHDX</sub>   | 43, 44 | Data hold after RD                       | 0                         |                                      | 0      |     | ns  |

| t <sub>RHDZ</sub>   | 43, 44 | Data float after RD                      |                           | t <sub>CLCL</sub> -20                |        | 5   | ns  |

| t <sub>LLDV</sub>   | 43, 44 | ALE low to valid data in                 |                           | 4t <sub>CLCL</sub> -150              |        | 50  | ns  |

| t <sub>AVDV</sub>   | 43, 44 | Address to valid data in                 |                           | 4.5t <sub>CLCL</sub> -165            |        | 60  | ns  |

| t <sub>LLWL</sub>   | 43, 44 | ALE low to RD or WR low                  | 1.5t <sub>CLCL</sub> -50  | 1.5t <sub>CLCL</sub> +50             | 25     | 125 | ns  |

| t <sub>AVWL</sub>   | 43, 44 | Address valid to WR low or RD low        | 2t <sub>CLCL</sub> -75    |                                      | 25     |     | ns  |

| t <sub>QVWX</sub>   | 43, 44 | Data valid to WR transition              | 0.5t <sub>CLCL</sub> -25  |                                      | 0      |     | ns  |

| t <sub>WHQX</sub>   | 43, 44 | Data hold after WR                       | 0.5t <sub>CLCL</sub> -20  |                                      | 5      |     | ns  |

| t <sub>QVWH</sub>   | 44     | Data valid to $\overline{WR}$ high       | 3.5t <sub>CLCL</sub> -130 |                                      | 45     |     | ns  |

| t <sub>RLAZ</sub>   | 43, 44 | RD low to address float                  |                           | 0                                    |        | 0   | ns  |

| t <sub>WHLH</sub>   | 43, 44 | RD or WR high to ALE high                | 0.5t <sub>CLCL</sub> -20  | 0.5t <sub>CLCL</sub> +20             | 5      | 45  | ns  |

| External C          | lock   | •                                        | •                         | •                                    |        |     |     |

| t <sub>CHCX</sub>   | 46     | High time                                | 20                        | t <sub>CLCL</sub> -t <sub>CLCX</sub> |        |     | ns  |

| t <sub>CLCX</sub>   | 46     | Low time                                 | 20                        | t <sub>CLCL</sub> -t <sub>CHCX</sub> |        |     | ns  |

| t <sub>CLCH</sub>   | 46     | Rise time                                |                           | 5                                    |        |     | ns  |

| t <sub>CHCL</sub>   | 46     | Fall time                                |                           | 5                                    |        |     | ns  |

| Shift Regi          | ster   | •                                        | •                         |                                      |        |     |     |

| t <sub>XLXL</sub>   | 45     | Serial port clock cycle time             | 6t <sub>CLCL</sub>        |                                      | 300    |     | ns  |

| t <sub>QVXH</sub>   | 45     | Output data setup to clock rising edge   | 5t <sub>CLCL</sub> -133   |                                      | 117    |     | ns  |

| t <sub>XHQX</sub>   | 45     | Output data hold after clock rising edge | t <sub>CLCL</sub> -30     |                                      | 20     |     | ns  |

| t <sub>XHDX</sub>   | 45     | Input data hold after clock rising edge  | 0                         |                                      | 0      | 1   | ns  |

| t <sub>XHDV</sub>   | 45     | Clock rising edge to input data valid    |                           | 5t <sub>CLCL</sub> -133              | i      | 117 | ns  |

NOTES:

Parameters are valid over operating temperature range unless otherwise specified.

Load capacitance for port 0, ALE, and PSEN = 100 pF, load capacitance for all other outputs = 80 pF.

3. Interfacing the microcontroller to devices with float times up to 45 ns is permitted. This limited bus contention will not cause damage to Port 0 drivers.

4. Parts are tested to 2 MHz, but are guaranteed to operate down to 0 Hz.

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

#### **EXPLANATION OF THE AC SYMBOLS**

Each timing symbol has five characters. The first character is always 't' (= time). The other characters, depending on their positions, indicate the name of a signal or the logical status of that signal. The designations are:

- A Address

- C Clock

- D Input data

- H Logic level high

- I Instruction (program memory contents)

- L Logic level low, or ALE

- P PSEN

- Q Output data

- R RD signal

- t Time

- V Valid

- $\mathsf{W}-\ \overline{\mathsf{W}\mathsf{R}}\ \text{signal}$

- X No longer a valid logic level

- Z Float

- **Examples:**  $t_{AVLL}$  = Time for address valid to ALE low.

$t_{LLPL}$  = Time for ALE low to  $\overline{PSEN}$  low.

Figure 42. External Program Memory Read Cycle

Figure 43. External Data Memory Read Cycle

## P89C51RA2/RB2/RC2/RD2xx

P89C51RA2/RB2/RC2/RD2xx

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

Figure 44. External Data Memory Write Cycle

Figure 45. Shift Register Mode Timing

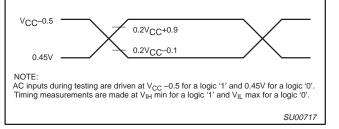

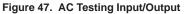

Figure 46. External Clock Drive

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

P89C51RA2/RB2/RC2/RD2xx

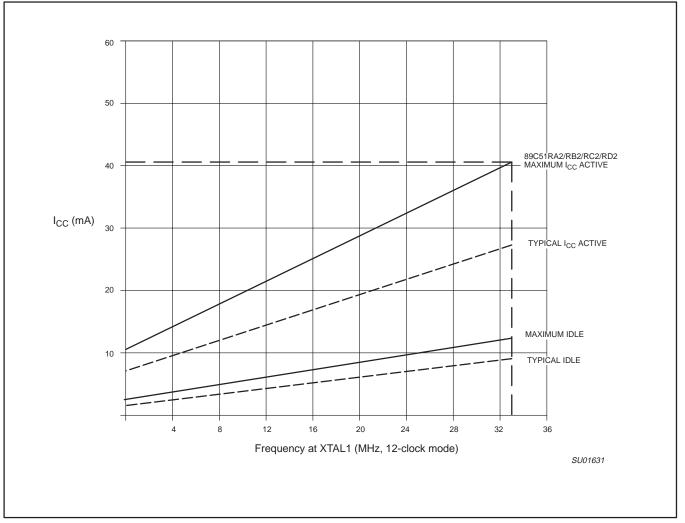

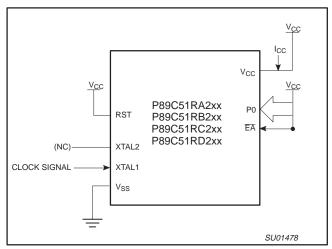

Figure 49.  $I_{CC}$  vs. FREQ Valid only within frequency specifications of the device under test

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

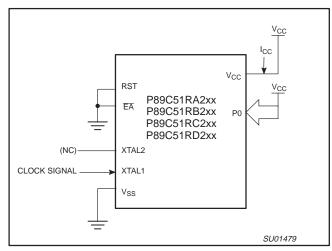

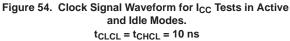

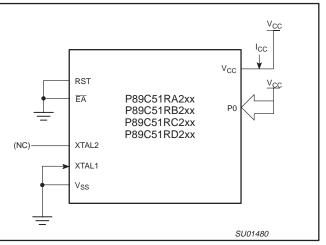

Figure 53.  $I_{CC}$  Test Condition, Idle Mode,  $T_{amb}$  = 25 °C. All other pins are disconnected

P89C51RA2/RB2/RC2/RD2xx

8KB/16KB/32KB/64KB ISP/IAP Flash with 512B/512B/512B/1KB RAM

# P89C51RA2/RB2/RC2/RD2xx

Data sheet status

| Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2]</sup> | Definitions                                                                                                                                                                                                                                                                                                            |

|----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective data                   | Development                      | This data sheet contains data from the objective specification for product development.<br>Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                                         |

| Preliminary data                 | Qualification                    | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.                                     |

| Product data                     | Production                       | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Changes will be communicated according to the Customer Product/Process Change Notification (CPCN) procedure SNW-SQ-650A. |

[1] Please consult the most recently issued data sheet before initiating or completing a design.

[2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

### Definitions

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

Application information - Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes - Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### Contact information

For additional information please visit http://www.semiconductors.philips.com.

Fax: +31 40 27 24825

© Koninklijke Philips Electronics N.V. 2002 All rights reserved. Printed in U.S.A.

Date of release: 07-02

For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com

Document order number:

9397 750 10129

Let's make things better.