Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                       |

|----------------------------|----------------------------------------------------------------|

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 100MHz                                                         |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART               |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                      |

| Data Converters            | A/D 17x10b; D/A 1x10b                                          |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 28-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 28-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f362-gm |

|                            |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR | Definition | 11.6. | MAC0BL: MAC0 B Low Byte                       | 124 |

|-----|------------|-------|-----------------------------------------------|-----|

|     |            |       | MAC0ACC3: MAC0 Accumulator Byte 3             |     |

|     |            |       | MAC0ACC2: MAC0 Accumulator Byte 2             |     |

| SFR | Definition | 11.9. | MAC0ACC1: MAC0 Accumulator Byte 1             | 125 |

| SFR | Definition | 11.10 | ). MAC0ACC0: MAC0 Accumulator Byte 0          | 126 |

| SFR | Definition | 11.11 | . MAC0OVR: MAC0 Accumulator Overflow          | 126 |

| SFR | Definition | 11.12 | 2. MAC0RNDH: MAC0 Rounding Register High Byte | 126 |

| SFR | Definition | 11.13 | 3. MAC0RNDL: MAC0 Rounding Register Low Byte  | 127 |

| SFR | Definition | 12.1. | VDM0CN: VDD Monitor Control                   | 131 |

|     |            |       | RSTSRC: Reset Source                          |     |

|     |            |       | PSCTL: Program Store Read/Write Control       |     |

|     |            |       | FLKEY: Flash Lock and Key                     |     |

|     |            |       | FLSCL: Flash Memory Control                   |     |

|     |            |       | CCH0CN: Cache Control                         |     |

|     |            |       | CCH0TN: Cache Tuning                          |     |

|     |            |       | CCH0LC: Cache Lock Control                    |     |

|     |            |       | CCH0MA: Cache Miss Accumulator                |     |

|     |            |       | FLSTAT: Flash Status                          |     |

|     |            |       | EMI0CN: External Memory Interface Control     |     |

|     |            |       | EMI0CF: External Memory Configuration         |     |

|     |            |       | EMI0TC: External Memory Timing Control        |     |

|     |            |       | OSCICL: Internal Oscillator Calibration.      |     |

|     |            |       | OSCICN: Internal Oscillator Control           |     |

|     |            |       | OSCLCN: Internal L-F Oscillator Control       |     |

| SFR | Definition | 16.4. | CLKSEL: System Clock Selection                | 173 |

| SFR | Definition | 16.5. | OSCXCN: External Oscillator Control           | 174 |

|     |            |       | PLL0CN: PLL Control                           |     |

|     |            |       | PLL0DIV: PLL Pre-divider                      |     |

|     |            |       | PLLOMUL: PLL Clock Scaler                     |     |

|     |            |       | PLLOFLT: PLL Filter                           |     |

|     |            |       | XBR0: Port I/O Crossbar Register 0            |     |

|     |            |       | XBR1: Port I/O Crossbar Register 1            |     |

|     |            |       | P0: Port0                                     |     |

| SFR | Definition | 17.4. | P0MDIN: Port0 Input Mode                      | 190 |

|     |            |       | P0MDOUT: Port0 Output Mode                    |     |

|     |            |       | P0SKIP: Port0 Skip                            |     |

|     |            |       | P0MAT: Port0 Match                            |     |

|     |            |       | P0MASK: Port0 Mask                            |     |

|     |            |       | P1: Port1                                     |     |

|     |            |       | ). P1MDIN: Port1 Input Mode                   |     |

|     |            |       | P1MDOUT: Port1 Output Mode                    |     |

|     |            |       | 2. P1SKIP: Port1 Skip                         |     |

|     |            |       | 3. P1MAT: Port1 Match                         |     |

| SFR | Definition | 17.14 | I. P1MASK: Port1 Mask                         | 194 |

| SFR | Definition | 17.15 | 5. P2: Port2                                  | 194 |

### SFR Definition 5.6. ADC0CN: ADC0 Control

| R/W       | R/W                         | R/W           | R/W             | R/W            | R/W            | R/W           | R/W           | Reset Valu  |

|-----------|-----------------------------|---------------|-----------------|----------------|----------------|---------------|---------------|-------------|

| AD0EN     | AD0TM                       | AD0INT        | AD0BUSY         | <b>ADOWINT</b> | AD0CM2         | AD0CM1        | AD0CM0        | 0000000     |

| Bit7      | Bit6                        | Bit5          | Bit4            | Bit3           | Bit2           | Bit1          | Bit0          |             |

| Bit 7:    | AD0EN: AD0                  | C0 Enable     | Bit.            |                |                |               |               |             |

|           | 0: ADC0 Disa                | abled. ADC    | C0 is in low-p  | ower shutde    | own.           |               |               |             |

|           | 1: ADC0 Ena                 |               |                 |                |                | ersions.      |               |             |

| Bit 6:    | AD0TM: AD0                  | C0 Track N    | lode Bit.       |                |                |               |               |             |

|           | 0: Normal Tra               | ack Mode:     | When ADC0       | is enabled,    | tracking is    | continuous    | unless a coi  | nversion is |

|           | in progress.                |               |                 |                |                |               |               |             |

|           | 1: Low-powe                 |               |                 |                |                | ) bits (see b | elow).        |             |

| Bit 5:    | AD0INT: AD0                 |               | •               |                | -              |               |               |             |

|           | 0: ADC0 has                 |               |                 |                | since the las  | st time AD0I  | NT was clea   | ared.       |

|           | 1: ADC0 has                 | •             |                 | ersion.        |                |               |               |             |

| Bit 4:    | ADOBUSY: A                  | ADC0 Busy     | Bit.            |                |                |               |               |             |

|           | Read:                       |               |                 |                |                |               |               |             |

|           | 0: ADC0 con                 |               |                 |                | i is not curre | enuy in prog  | ress. ADOIN   | vi is set t |

|           | 1: ADC0 con                 | -             | edge of ADC     | DU31.          |                |               |               |             |

|           | Write:                      |               | in progress.    |                |                |               |               |             |

|           | 0: No Effect.               |               |                 |                |                |               |               |             |

|           | 1: Initiates A              | DC0 Conve     | ersion if AD0   | CM2-0 = 00     | 00b            |               |               |             |

| Bit 3:    | ADOWINT: A                  |               |                 |                |                |               |               |             |

|           | 0: ADC0 Wir                 |               |                 |                |                | d since this  | flag was las  | t cleared.  |

|           | 1: ADC0 Wir                 |               |                 |                |                |               | U             |             |

| Bits 2–0: | AD0CM2-0:                   | ADC0 Star     | rt of Convers   | ion Mode S     | elect.         |               |               |             |

|           | When AD0TI                  | M = 0:        |                 |                |                |               |               |             |

|           | 000: ADC0 c                 | onversion     | initiated on e  | very write c   | f '1' to AD0   | BUSY.         |               |             |

|           | 001: ADC0 c                 |               |                 |                |                |               |               |             |

|           | 010: ADC0 c                 |               |                 |                |                |               |               |             |

|           | 011: ADC0 c                 |               |                 |                |                |               |               |             |

|           | 100: ADC0 c                 |               |                 |                |                | NVSTR.        |               |             |

|           | 101: ADC0 c                 |               | initiated on o  | vertiow of I   | imer 3.        |               |               |             |

|           | 11x: Reserve                | -             |                 |                |                |               |               |             |

|           | When AD0TI<br>000: Tracking |               | on write of '1' |                | SV and last    |               | eks followo   | hy con-     |

|           | versio                      | -             |                 |                |                |               |               |             |

|           | 001: Tracking               |               | on overflow o   | f Timer 0 ar   | nd lasts 3 S   | AR clocks f   | ollowed by a  | conversio   |

|           | 010: Tracking               | •             |                 |                |                |               | •             |             |

|           | 011: Tracking               | •             |                 |                |                |               |               |             |

|           | 100: ADC0 ti<br>edge.       |               |                 |                |                |               |               |             |

|           | 101: Tracking               |               |                 | (T) 0          |                |               | مالمين مالمين |             |

|           |                             | n initiateo o | n overtiow o    | t limer i ar   | nd lasts X S   | AR CIOCKS T   | ollowen nv r  | CONVERSION  |

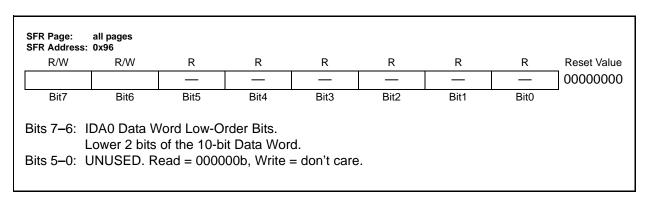

### SFR Definition 6.3. IDA0L: IDA0 Data Word LSB

### **Table 6.1. IDAC Electrical Characteristics**

-40 to +85 °C,  $V_{DD}$  = 3.0 V Full-scale output current set to 2 mA unless otherwise specified.

| Parameter                                                  | Conditions                                                                                           | Min | Тур                 | Max                   | Units          |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|---------------------|-----------------------|----------------|

|                                                            | Static Performance                                                                                   |     |                     |                       |                |

| Resolution                                                 |                                                                                                      |     | 10                  |                       | bits           |

| Integral Nonlinearity                                      |                                                                                                      | —   | ±0.5                | ±2                    | LSB            |

| Differential Nonlinearity                                  | Guaranteed Monotonic                                                                                 | —   | ±0.5                | ±1                    | LSB            |

| Output Compliance Range                                    |                                                                                                      | —   | —                   | V <sub>DD</sub> - 1.2 | V              |

| Offset Error                                               |                                                                                                      | —   | 0                   | —                     | LSB            |

| Full Scale Error                                           | 2 mA Full Scale Output Current                                                                       | -15 | 0                   | 15                    | LSB            |

| Full Scale Error Tempco                                    |                                                                                                      | —   | 30                  | —                     | ppm/°C         |

| V <sub>DD</sub> Power Supply<br>Rejection Ratio            |                                                                                                      | —   | 6.5                 | —                     | µA/V           |

|                                                            | Dynamic Performance                                                                                  | •   |                     |                       |                |

| Output Settling Time to 1/2<br>LSB                         | IDA0H:L = 0x3FF to 0x000                                                                             | —   | 5                   | _                     | μs             |

| Startup Time                                               |                                                                                                      | —   | 5                   | —                     | μs             |

| Gain Variation                                             | 1 mA Full Scale Output Current<br>0.5 mA Full Scale Output Current                                   | _   | ±1<br>±1            | _                     | %<br>%         |

|                                                            | Power Consumption                                                                                    |     |                     |                       |                |

| Power Supply Current (V <sub>DD</sub><br>supplied to IDAC) | 2 mA Full Scale Output Current<br>1 mA Full Scale Output Current<br>0.5 mA Full Scale Output Current |     | 2140<br>1140<br>640 |                       | μΑ<br>μΑ<br>μΑ |

| R/W  | R/W                                        | R/W                                                        | R/W                                                       | R/W                                                                          | R/W                                                                  | R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R/W                                                   | Reset Valu                               |

|------|--------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------|

| Bit7 | Bit6                                       | Bit5                                                       | Bit4                                                      | Bit3                                                                         | Bit2                                                                 | Bit1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit0                                                  | 0000000                                  |

|      | a 3 byte SFI<br>LAST is the                | •                                                          |                                                           | GE is the fire                                                               | st entry, SF                                                         | RNEXT is t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       | , and SFR-                               |

|      | LAST is the<br>Stack, and v<br>rupts cause | third entry.<br>vill not caus<br>pushes and                | The SFR st<br>e the stack<br>I pops of th                 | GE is the firs<br>ack bytes m<br>to 'push' or<br>e SFR Page                  | st entry, SF<br>ay be used<br>'pop'. Only<br>e Stack.                | RNEXT is the contract of the c | he second<br>ontext in th<br>and return               | , and SFR-<br>le SFR Page<br>from inter- |

|      | LAST is the Stack, and v                   | third entry.<br>vill not caus<br>pushes and<br>s the SFR P | The SFR st<br>e the stack<br>d pops of th<br>rage contair | GE is the firs<br>ack bytes m<br>to 'push' or<br>e SFR Page<br>ned in the se | st entry, SF<br>hay be used<br>'pop'. Only<br>e Stack.<br>econd byte | RNEXT is the alter the contract interrupts a of the SFR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | he second<br>ontext in th<br>and return<br>Stack. Thi | , and SFR-<br>le SFR Page<br>from inter- |

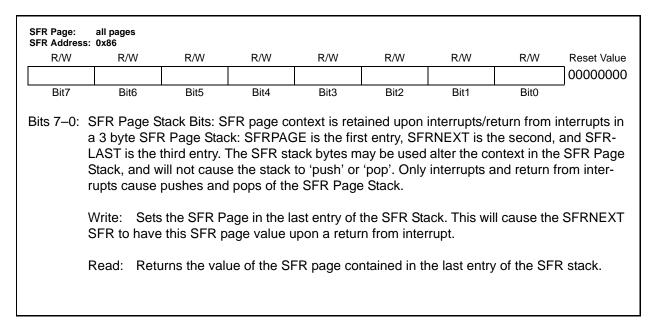

### SFR Definition 9.3. SFRNEXT: SFR Next Register

### SFR Definition 9.4. SFRLAST: SFR Last Register

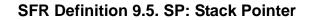

### 9.4.7. Register Descriptions

Following are descriptions of SFRs related to the operation of the CIP-51 System Controller. Reserved bits should not be set to logic '1'. Future product versions may use these bits to implement new features in which case the reset value of the bit will be logic '0', selecting the feature's default state. Detailed descriptions of the remaining SFRs are included in the sections of the data sheet associated with their corresponding system function.

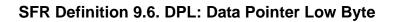

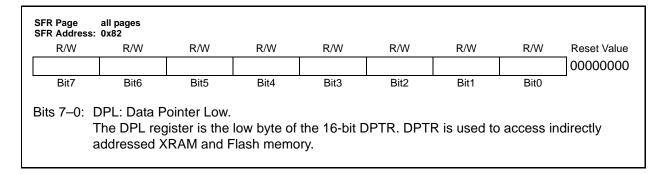

### SFR Definition 9.7. DPH: Data Pointer High Byte

### SFR Definition 9.11. PCON: Power Control

| R/W     | R/W                                                                                               | R/W                                                         | R/W                                               | R/W                        | R/W            | R/W                    | R/W         | Reset Value |

|---------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------|----------------------------|----------------|------------------------|-------------|-------------|

| Reserve | d Reserved                                                                                        | Reserved                                                    | Reserved                                          | Reserved                   | Reserved       | STOP                   | IDLE        | 00000000    |

| Bit7    | Bit6                                                                                              | Bit5                                                        | Bit4                                              | Bit3                       | Bit2           | Bit1                   | Bit0        |             |

| Bit 0:  | Writing a '1'<br>1: CIP-51 for<br>IDLE: IDLE I<br>Writing a '1'<br>1: CIP-51 for<br>and all perip | rced into po<br>Mode Selec<br>to this bit w<br>rced into ID | wer-down r<br>t.<br>ill place the<br>LE mode. (\$ | node. (Turn<br>CIP-51 into | s off oscillat | tor).<br>e. This bit v | vill always | read '0'.   |

### 13.2.1. Summary of Flash Security Options

The level of Flash security depends on the Flash access method. The three Flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages. Table 13.1 summarizes the Flash security features of the C8051F36x devices.

| Action                                                                        | C2 Debug      | User Firmware e  | xecuting from: |

|-------------------------------------------------------------------------------|---------------|------------------|----------------|

|                                                                               | Interface     | an unlocked page | a locked page  |

| Read, Write or Erase unlocked pages<br>(except page with Lock Byte)           | Permitted     | Permitted        | Permitted      |

| Read, Write or Erase locked pages<br>(except page with Lock Byte)             | Not Permitted | FEDR             | Permitted      |

| Read or Write page containing Lock Byte<br>(if no pages are locked)           | Permitted     | Permitted        | Permitted      |

| Read or Write page containing Lock Byte<br>(if any page is locked)            | Not Permitted | FEDR             | Permitted      |

| Read contents of Lock Byte<br>(if no pages are locked)                        | Permitted     | Permitted        | Permitted      |

| Read contents of Lock Byte<br>(if any page is locked)                         | Not Permitted | FEDR             | Permitted      |

| Erase page containing Lock Byte<br>(if no pages are locked)                   | Permitted     | FEDR             | FEDR           |

| Erase page containing Lock Byte - Unlock all pages<br>(if any page is locked) | Only C2DE     | FEDR             | FEDR           |

| Lock additional pages<br>(change '1's to '0's in the Lock Byte)               | Not Permitted | FEDR             | FEDR           |

| Unlock individual pages<br>(change '0's to '1's in the Lock Byte)             | Not Permitted | FEDR             | FEDR           |

| Read, Write or Erase Reserved Area                                            | Not Permitted | FEDR             | FEDR           |

| Table 13.1. Flash Sec | urity Summary |

|-----------------------|---------------|

|-----------------------|---------------|

C2DE - C2 Device Erase (Erases all Flash pages including the page containing the Lock Byte) FEDR - Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is '1' after reset)

All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

Locking any Flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

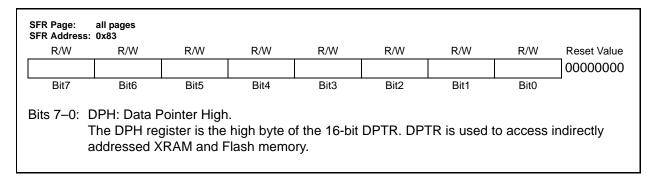

### 13.4. Flash Read Timing

On reset, the C8051F36x Flash read timing is configured for operation with system clocks up to 25 MHz. If the system clock will not be increased above 25 MHz, then the Flash timing registers may be left at their reset value.

For every Flash read or fetch, the system provides an internal Flash read strobe to the Flash memory. The Flash read strobe lasts for one or two system clock cycles, based on the FLRT bits (FLSCL.4 and FLSCL.5). If the system clock is greater than 25 MHz, the FLRT bit must be changed to the appropriate setting. Otherwise, data read or fetched from Flash may not represent the actual contents of Flash. When the Flash read strobe is asserted, Flash memory is active. When it is de-asserted, Flash memory is in a low power state.

The recommended procedure for updating FLRT is:

- Step 1. Select SYSCLK to 25 MHz or less.

- Step 2. Disable the prefetch engine (CHPFEN = '0' in CCH0CN register).

- Step 3. Set the FLRT bits to the appropriate setting for the SYSCLK.

- Step 4. Enable the prefetch engine (CHPFEN = '1' in CCH0CN register).

### SFR Definition 13.3. FLSCL: Flash Memory Control

|                     |        |         | Lock Status |

|---------------------|--------|---------|-------------|

|                     | TAG 0  | SLOT 0  | UNLOCKED    |

|                     | TAG 1  | SLOT 1  | UNLOCKED    |

| Cache Push          | TAG 2  | SLOT 2  | UNLOCKED    |

| Operations          |        |         | UNLOCKED    |

| Decrement<br>CHSLOT |        |         | 1           |

|                     |        |         |             |

|                     | TAG 26 | SLOT 26 | UNLOCKED    |

| CHSLOT = 27         | TAG 27 | SLOT 27 | UNLOCKED    |

| $\perp$             | TAG 28 | SLOT 28 | LOCKED      |

| Cache Pop           | TAG 29 | SLOT 29 | LOCKED      |

| Operations          | TAG 30 | SLOT 30 | LOCKED      |

| Increment           | TAG 31 | SLOT 31 | LOCKED      |

| CHSLOT              |        |         | -           |

Figure 14.3. Cache Lock Operation

| R/W    | R/W                         | R/W           | R/W           | R/W            | R/W         | R/W            | R/W         | Reset Value |

|--------|-----------------------------|---------------|---------------|----------------|-------------|----------------|-------------|-------------|

| CHWRE  | N CHRDEN                    | CHPFEN        | CHFLSH        | CHRETI         | CHISR       | CHMOVC         | CHBLKW      | 11100110    |

| Bit7   | Bit6                        | Bit5          | Bit4          | Bit3           | Bit2        | Bit1           | Bit0        |             |

| Bit 7: | CHWREN: C                   | Cache Write   | Enable.       |                |             |                |             |             |

|        | This bit enab               |               |               |                |             |                |             |             |

|        | locks.                      |               |               | <b>U</b>       | except dur  | ing Flash writ | tes/erasure | s or cache  |

|        | 1: Writes to                |               |               | wed.           |             |                |             |             |

| Bit 6: | CHRDEN: C                   |               |               |                |             |                |             |             |

|        |                             |               |               |                |             | he cache me    |             |             |

|        |                             |               |               |                |             | refetch engin  | e.          |             |

|        | 1: Instruction              |               |               | cache (whe     | en availabl | e).            |             |             |

| Bit 5: | CHPFEN: C                   |               |               |                |             |                |             |             |

|        | This bit enab               |               | •             | э.             |             |                |             |             |

|        | 0: Prefetch e               | •             |               |                |             |                |             |             |

| Bit 4: | 1: Prefetch e<br>CHFLSH: Ca | •             | ableu.        |                |             |                |             |             |

| Dit 4. |                             |               | is hit cloars | the cache (    | contents ]  | This bit alway | e roade 'O' |             |

| Bit 3: | CHRETI: Ca                  |               |               |                | Jointenito. | nis bit alway  | 316003 0.   |             |

| Dit 0. | This bit enab               |               |               |                | ess to he   | cached         |             |             |

|        | 0: Destinatio               |               |               |                |             |                |             |             |

|        | 1: RETI dest                |               |               |                |             |                |             |             |

| Bit 2: | CHISR: Cac                  | he ISR Ena    | ble.          |                |             |                |             |             |

|        | This bit allow              | vs instructio | ns which ar   | e part of an   | Interrupt S | Service Routi  | ne (ISR) to | be cached   |

|        | 0: Instruction              | ns in ISRs w  | ill not be lo | aded into ca   | ache mem    | ory.           |             |             |

|        | 1: Instruction              | ns in ISRs c  | an be cach    | ed.            |             |                |             |             |

| Bit 1: | CHMOVC: C                   | Cache MOV     | C Enable.     |                |             |                |             |             |

|        |                             |               |               |                |             | be loaded inte | o the cache | e memory.   |

|        | 0: Data requ                |               |               |                |             |                |             |             |

|        |                             |               |               | ctions will be | e loaded ir | nto cache me   | mory.       |             |

| Bit 0: | CHBLKW: B                   |               |               |                |             |                |             |             |

|        | This bit allow              |               |               |                |             |                |             |             |

|        | 0: Each byte                |               |               |                |             |                |             |             |

|        | 1: Flash byte               | es are writte | n in groups   | s of four (for | code space  | ce writes).    |             |             |

### SFR Definition 14.1. CCH0CN: Cache Control

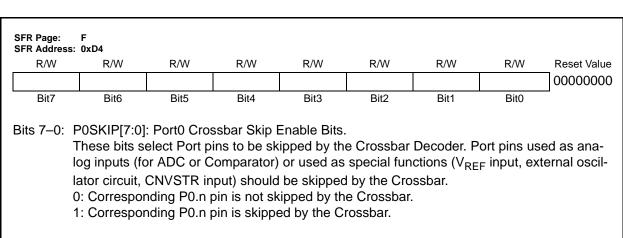

### SFR Definition 17.6. P0SKIP: Port0 Skip

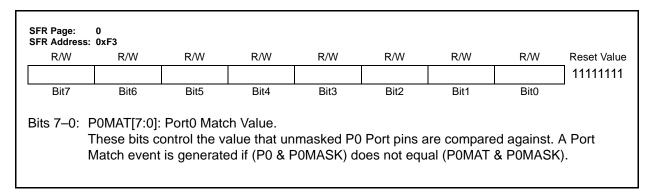

### SFR Definition 17.7. P0MAT: Port0 Match

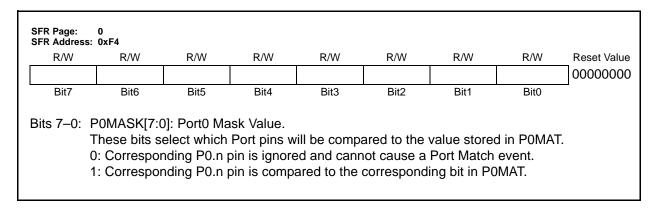

### SFR Definition 17.8. P0MASK: Port0 Mask

|                                                           |                              |                      | Freq                             | uency: 11.059         | 2 MHz                                        |                  |                                  |

|-----------------------------------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|----------------------------------------------|------------------|----------------------------------|

|                                                           | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

| ×                                                         | 230400                       | 0.00%                | 48                               | SYSCLK                | XX <b>2</b>                                  | 1                | 0xE8                             |

| Cloc                                                      | 115200                       | 0.00%                | 96                               | SYSCLK                | XX                                           | 1                | 0xD0                             |

| Timer Clock<br>Osc.                                       | 57600                        | 0.00%                | 192                              | SYSCLK                | XX                                           | 1                | 0xA0                             |

| Time<br>Osc.                                              | 28800                        | 0.00%                | 384                              | SYSCLK                | XX                                           | 1                | 0x40                             |

| and<br>nal                                                | 14400                        | 0.00%                | 768                              | SYSCLK/12             | 00                                           | 0                | 0xE0                             |

| -K a<br>xter                                              | 9600                         | 0.00%                | 1152                             | SYSCLK/12             | 00                                           | 0                | 0xD0                             |

| SCI                                                       | 2400                         | 0.00%                | 4608                             | SYSCLK/12             | 00                                           | 0                | 0x40                             |

| SYSCLK and 7<br>from External (                           | 1200                         | 0.00%                | 9216                             | SYSCLK/48             | 10                                           | 0                | 0xA0                             |

| sc.                                                       | 230400                       | 0.00%                | 48                               | EXTCLK/8              | 11                                           | 0                | 0xFD                             |

| LK from Internal Osc.,<br>Clock from External O           | 115200                       | 0.00%                | 96                               | EXTCLK/8              | 11                                           | 0                | 0xFA                             |

| n Exte                                                    | 57600                        | 0.00%                | 192                              | EXTCLK/8              | 11                                           | 0                | 0xF4                             |

| om Ir<br>k fron                                           | 28800                        | 0.00%                | 384                              | EXTCLK/8              | 11                                           | 0                | 0xE8                             |

| Cloc                                                      | 14400                        | 0.00%                | 768                              | EXTCLK/8              | 11                                           | 0                | 0xD0                             |

| SYSCLK from Internal Osc.,<br>Timer Clock from External O | 9600                         | 0.00%                | 1152                             | EXTCLK/8              | 11                                           | 0                | 0xB8                             |

| Notes:                                                    |                              | ad T1M bit dafin     | itione con he                    | found in Section      | 01.1                                         |                  |                                  |

# Table 19.5. Timer Settings for Standard Baud RatesUsing an External 11.0592 MHz Oscillator

1. SCA1–SCA0 and T1M bit definitions can be found in Section 21.1.

**2.** X = Don't care.

### 20.6. SPI Special Function Registers

SPI0 is accessed and controlled through four special function registers in the system controller: SPI0CN Control Register, SPI0DAT Data Register, SPI0CFG Configuration Register, and SPI0CKR Clock Rate Register. The four special function registers related to the operation of the SPI0 Bus are described in the following figures.

| R                 | R/W                                                                                                | R/W                                                                           | R/W                                                                      | R                                                                      | R                                        | R                            | R              | Reset Value |

|-------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------|------------------------------|----------------|-------------|

| SPIBSY            | MSTEN                                                                                              | CKPHA                                                                         | CKPOL                                                                    | SLVSEL                                                                 | NSSIN                                    | SRMT                         | RXBMT          | 00000111    |

| Bit7              | Bit6                                                                                               | Bit5                                                                          | Bit4                                                                     | Bit3                                                                   | Bit2                                     | Bit1                         | Bit0           | -           |

| Bit 7:            | SPIBSY: SPI<br>This bit is se                                                                      |                                                                               |                                                                          | PI transfer is                                                         | in progress                              | s (Master o                  | r slave Mod    | e).         |

| Bit 6:            | MSTEN: Mas<br>0: Disable m                                                                         | aster mode                                                                    | . Operate i                                                              |                                                                        | e.                                       |                              |                |             |

| Bit 5:            | 1: Enable ma<br>CKPHA: SPI<br>This bit contr                                                       | 0 Clock Ph<br>rols the SPI                                                    | ase.<br>0 clock pha                                                      | ise.                                                                   |                                          |                              |                |             |

| Bit 4:            | 0: Data cente<br>1: Data cente<br>CKPOL: SPI<br>This bit contr<br>0: SCK line I                    | ered on sec<br>0 Clock Pol<br>rols the SPI                                    | ond edge c<br>arity.<br>0 clock pol                                      | of SCK perio                                                           | od.*                                     |                              |                |             |

| iit 3:            | 1: SCK line h<br>SLVSEL: Sla<br>This bit is set<br>is cleared to                                   | ave Selecter<br>t to logic '1'<br>logic '0' wh                                | d Flag (read<br>whenever t<br>en NSS is l                                | he NSS pin<br>high (slave i                                            | not selected                             | d). This bit o               | does not ind   | icate the   |

| Bit 2:            | instantaneou<br>NSSIN: NSS<br>This bit mimi                                                        | Instantane                                                                    | ous Pin Inp<br>Intaneous v                                               | out (read on<br>alue that is                                           | ly).<br>present on                       |                              |                |             |

| Bit 1:            | the register is<br>SRMT: Shift<br>This bit will b<br>and there is<br>receive buffe<br>the transmit | Register Er<br>be set to log<br>no new info<br>er. It returns<br>buffer or by | npty (Valid<br>ic '1' when<br>mation ava<br>to logic '0'<br>a transitior | in Slave Mo<br>all data has<br>ailable to re<br>when a data<br>on SCK. | de, read or<br>been trans<br>ad from the | sferred in/ou<br>transmit bu | uffer or write | e to the    |

| Bit O:            | NOTE: SRM<br>RXBMT: Rec<br>This bit will b<br>information.<br>this bit will re<br><b>NOTE:</b> RXB | ceive Buffer<br>be set to log<br>If there is no<br>eturn to logi              | Empty (Va<br>ic '1' when<br>ew informat<br>c '0'.                        | lid in Slave<br>the receive<br>ion available                           | buffer has                               | been read a                  |                |             |

| <b>lote:</b> In s | lave mode, da<br>sampled one                                                                       |                                                                               |                                                                          |                                                                        |                                          |                              |                |             |

### SFR Definition 20.1. SPI0CFG: SPI0 Configuration

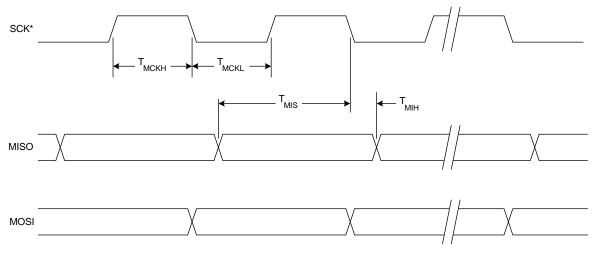

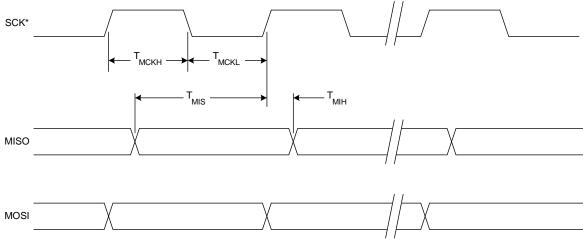

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

### Figure 20.9. SPI Master Timing (CKPHA = 1)

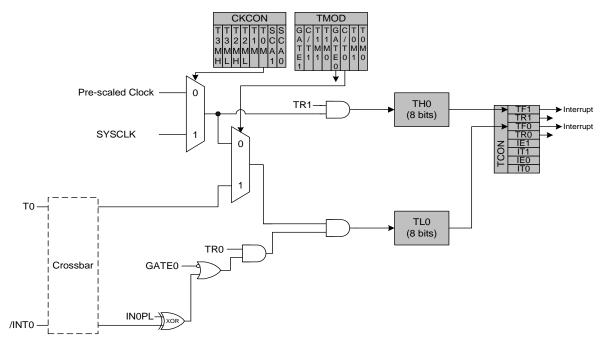

### 21.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and/or UART, and/or initiate ADC conversions. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

Figure 21.3. T0 Mode 3 Block Diagram

| R/W       | s: 0x8E<br>R/W                                                                                                                                 | R/W                            | R/W      | R/W         | R/W          | R/W         | R/W          | Reset Valu |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------|-------------|--------------|-------------|--------------|------------|--|--|--|--|

| ТЗМН      | T3ML                                                                                                                                           | T2MH                           | T2ML     | T1M         | T0M          | SCA1        | SCA0         | 0000000    |  |  |  |  |

| Bit7      | Bit6                                                                                                                                           | Bit5                           | Bit4     | Bit3        | Bit2         | Bit1        | Bit0         |            |  |  |  |  |

| Bit 7:    |                                                                                                                                                | · 2 Liah But                   | Clock So | loct        |              |             |              |            |  |  |  |  |

| י זוכ     | T3MH: Timer 3 High Byte Clock Select.<br>This bit selects the clock supplied to the Timer 3 high byte if Timer 3 is configured in split 8      |                                |          |             |              |             |              |            |  |  |  |  |

|           | bit timer mode. T3MH is ignored if Time 3 is in any other mode.                                                                                |                                |          |             |              |             |              |            |  |  |  |  |

|           | 0: Timer 3 hig                                                                                                                                 |                                |          |             |              |             | R3CN.        |            |  |  |  |  |

|           | 1: Timer 3 hig                                                                                                                                 |                                |          |             |              |             |              |            |  |  |  |  |

| Bit 6:    | T3ML: Timer                                                                                                                                    |                                |          |             |              |             |              |            |  |  |  |  |

|           | This bit selec                                                                                                                                 |                                |          |             | f Timer 3 is | configured  | in split 8-b | it timer   |  |  |  |  |

|           |                                                                                                                                                |                                |          |             |              |             | ·            |            |  |  |  |  |

|           | mode, this bit selects the clock supplied to the lower 8-bit timer.<br>0: Timer 3 low byte uses the clock defined by the T3XCLK bit in TMR3CN. |                                |          |             |              |             |              |            |  |  |  |  |

|           | 1: Timer 3 low byte uses the system clock.                                                                                                     |                                |          |             |              |             |              |            |  |  |  |  |

| Bit 5:    | T2MH: Timer                                                                                                                                    |                                |          |             |              |             |              |            |  |  |  |  |

|           | This bit selects the clock supplied to the Timer 2 high byte if Timer 2 is configured in split 8                                               |                                |          |             |              |             |              |            |  |  |  |  |

|           | bit timer mod                                                                                                                                  |                                |          |             |              |             |              |            |  |  |  |  |

|           | 0: Timer 2 hig                                                                                                                                 |                                |          | •           | the T2XCL    | K bit in TM | R2CN.        |            |  |  |  |  |

|           | 1: Timer 2 hi                                                                                                                                  |                                |          |             |              |             |              |            |  |  |  |  |

| Bit 4:    | T2ML: Timer 2 Low Byte Clock Select.                                                                                                           |                                |          |             |              |             |              |            |  |  |  |  |

|           | This bit selects the clock supplied to Timer 2. If Timer 2 is configured in split 8-bit timer                                                  |                                |          |             |              |             |              |            |  |  |  |  |

|           | mode, this bit selects the clock supplied to the lower 8-bit timer.                                                                            |                                |          |             |              |             |              |            |  |  |  |  |

|           | 0: Timer 2 low byte uses the clock defined by the T2XCLK bit in TMR2CN.                                                                        |                                |          |             |              |             |              |            |  |  |  |  |

| Bit 3:    | 1: Timer 2 low byte uses the system clock.                                                                                                     |                                |          |             |              |             |              |            |  |  |  |  |

| DIL J.    | T1M: Timer 1 Clock Select.<br>This select the clock source supplied to Timer 1. T1M is ignored when C/T1 is set to                             |                                |          |             |              |             |              |            |  |  |  |  |

|           | logic '1'.                                                                                                                                     |                                |          |             |              |             |              |            |  |  |  |  |

|           | 0: Timer 1 uses the clock defined by the prescale bits, SCA1–SCA0.                                                                             |                                |          |             |              |             |              |            |  |  |  |  |

|           | 1: Timer 1 uses the system clock.                                                                                                              |                                |          |             |              |             |              |            |  |  |  |  |

| Bit 2:    | T0M: Timer 0 Clock Select.                                                                                                                     |                                |          |             |              |             |              |            |  |  |  |  |

|           | This bit selects the clock source supplied to Timer 0. TOM is ignored when C/T0 is set to                                                      |                                |          |             |              |             |              |            |  |  |  |  |

|           | logic '1'.                                                                                                                                     |                                |          |             |              |             |              |            |  |  |  |  |

|           | 0: Counter/Timer 0 uses the clock defined by the prescale bits, SCA1–SCA0.                                                                     |                                |          |             |              |             |              |            |  |  |  |  |

|           | 1: Counter/Timer 0 uses the system clock.                                                                                                      |                                |          |             |              |             |              |            |  |  |  |  |

| 3its 1–0: | SCA1–SCA0: Timer 0/1 Prescale Bits.                                                                                                            |                                |          |             |              |             |              |            |  |  |  |  |

|           | These bits control the division of the clock supplied to Timer 0 and/or Timer 1 if configured                                                  |                                |          |             |              |             |              |            |  |  |  |  |

|           | to use presca                                                                                                                                  | aled clock in                  | puts.    |             |              |             |              |            |  |  |  |  |

|           | SCA1                                                                                                                                           | SCA0                           |          | Pr          | escaled Clo  | ock         |              |            |  |  |  |  |

|           | 0                                                                                                                                              | 0                              | Syste    | m clock div | ided by 12   |             |              |            |  |  |  |  |

|           | 0 1 System clock divided by 4                                                                                                                  |                                |          |             |              |             |              |            |  |  |  |  |

|           | 0                                                                                                                                              | 1 0 System clock divided by 48 |          |             |              |             |              |            |  |  |  |  |

|           |                                                                                                                                                | 0                              | Syste    | m clock div | ided by 48   |             |              |            |  |  |  |  |

### SFR Definition 21.3. CKCON: Clock Control

### 21.3.2. 8-bit Timers with Auto-Reload

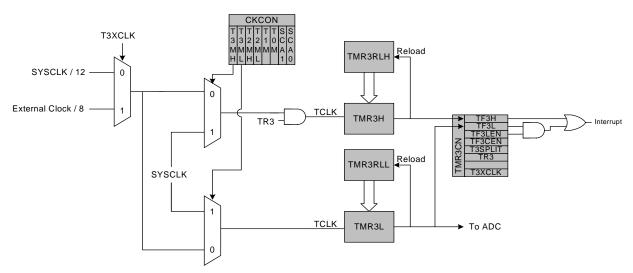

When T3SPLIT is set, Timer 3 operates as two 8-bit timers (TMR3H and TMR3L). Both 8-bit timers operate in auto-reload mode as shown in Figure 21.7. TMR3RLL holds the reload value for TMR3L; TMR3RLH holds the reload value for TMR3H. The TR3 bit in TMR3CN handles the run control for TMR3H. TMR3L is always running when configured for 8-bit Mode.

Each 8-bit timer may be configured to use SYSCLK, SYSCLK divided by 12, or the external oscillator clock source divided by 8. The Timer 3 Clock Select bits (T3MH and T3ML in CKCON) select either SYSCLK or the clock defined by the Timer 3 External Clock Select bit (T3XCLK in TMR3CN), as follows:

| T3MH | T3XCLK | TMR3H Clock      |

|------|--------|------------------|

|      |        | Source           |

| 0    | 0      | SYSCLK/12        |

| 0    | 1      | External Clock/8 |

| 1    | Х      | SYSCLK           |

| T3ML | T3XCLK | TMR3L Clock      |

|------|--------|------------------|

|      |        | Source           |

| 0    | 0      | SYSCLK/12        |

| 0    | 1      | External Clock/8 |

| 1    | Х      | SYSCLK           |

The TF3H bit is set when TMR3H overflows from 0xFF to 0x00; the TF3L bit is set when TMR3L overflows from 0xFF to 0x00. When Timer 3 interrupts are enabled, an interrupt is generated each time TMR3H overflows. If Timer 3 interrupts are enabled and TF3LEN (TMR3CN.5) is set, an interrupt is generated each time either TMR3L or TMR3H overflows. When TF3LEN is enabled, software must check the TF3H and TF3L flags to determine the source of the Timer 3 interrupt. The TF3H and TF3L interrupt flags are not cleared by hardware and must be manually cleared by software.

Figure 21.7. Timer 3 8-Bit Mode Block Diagram

| R/W                                           | R/W                                                                                                                                                                                     | R/W          | R/W          | R/W           | R/W           | R           | R/W             | Reset Value |  |  |  |  |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|---------------|---------------|-------------|-----------------|-------------|--|--|--|--|

| TF3H                                          | TF3L                                                                                                                                                                                    | TF3LEN       | TF3CEN       | T3SPLIT       | TR3           | _           | T3XCLK          | 0000000     |  |  |  |  |

| Bit7                                          | Bit6                                                                                                                                                                                    | Bit5         | Bit4         | Bit3          | Bit2          | Bit1        | Bit0            | 3           |  |  |  |  |

| Bit 7:                                        | TF3H: Time                                                                                                                                                                              | r 3 High Byt | e Overflow   | Flag.         |               |             |                 |             |  |  |  |  |

|                                               | Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode,                                                                                                 |              |              |               |               |             |                 |             |  |  |  |  |

|                                               | this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is                                                                                             |              |              |               |               |             |                 |             |  |  |  |  |

|                                               | enabled, set                                                                                                                                                                            |              |              |               |               |             |                 |             |  |  |  |  |

|                                               | TF3H is not automatically cleared by hardware and must be cleared by software.                                                                                                          |              |              |               |               |             |                 |             |  |  |  |  |

| Bit 6:                                        | TF3L: Timer                                                                                                                                                                             |              |              | •             |               | o == /      | 0 00 14/        |             |  |  |  |  |

|                                               | Set by hard                                                                                                                                                                             |              |              |               |               |             |                 |             |  |  |  |  |

|                                               | set, an inter                                                                                                                                                                           |              | -            |               |               |             | •               |             |  |  |  |  |

|                                               | will set wher<br>ically cleared                                                                                                                                                         |              |              | s regardless  |               | er s mode   | . This bit is n | iot automa  |  |  |  |  |

| Bit 5:                                        | TF3LEN: Tir                                                                                                                                                                             | •            |              | ot Enable     |               |             |                 |             |  |  |  |  |

| Dit J.                                        |                                                                                                                                                                                         |              | •            |               | errunts If T  | F3I FN is a | set and Time    | r 3 inter-  |  |  |  |  |

|                                               | This bit enables/disables Timer 3 Low Byte interrupts. If TF3LEN is set and Timer 3 inter-<br>rupts are enabled, an interrupt will be generated when the low byte of Timer 3 overflows. |              |              |               |               |             |                 |             |  |  |  |  |

|                                               | 0: Timer 3 L                                                                                                                                                                            |              |              |               |               |             |                 |             |  |  |  |  |

|                                               | 1: Timer 3 L                                                                                                                                                                            |              | •            |               |               |             |                 |             |  |  |  |  |

| Bit 4:                                        |                                                                                                                                                                                         |              |              |               | apture Enal   | ole.        |                 |             |  |  |  |  |

|                                               | TF3CEN: Timer 3 Low-Frequency Oscillator Capture Enable.<br>This bit enables/disables Timer 3 Low-Frequency Oscillator Capture Mode. If TF3CEN is set                                   |              |              |               |               |             |                 |             |  |  |  |  |

|                                               | and Timer 3                                                                                                                                                                             | interrupts a | are enabled  | , an interrup | t will be ge  | nerated or  | a rising edg    | ge of the   |  |  |  |  |

|                                               | and Timer 3 interrupts are enabled, an interrupt will be generated on a rising edge of the low-frequency oscillator output, and the current 16-bit timer value in TMR3H:TMR3L will be   |              |              |               |               |             |                 |             |  |  |  |  |

|                                               | copied to TMR3RLH:TMR3RLL. See Section "16. Oscillators" on page 168 for more details                                                                                                   |              |              |               |               |             |                 |             |  |  |  |  |

|                                               | 0: Timer 3 L                                                                                                                                                                            |              |              | •             |               |             |                 |             |  |  |  |  |

|                                               | 1: Timer 3 L                                                                                                                                                                            | •            | •            | •             | enabled.      |             |                 |             |  |  |  |  |