Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 100MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1K x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                       |

| Data Converters            | A/D 17x10b; D/A 1x10b                                           |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 28-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 28-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f362-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 18.3.SMBus Operation                                                                                                              | 201                                                                                                                                                       |

|----|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 18.3.1.Arbitration                                                                                                                |                                                                                                                                                           |

|    | 18.3.2.Clock Low Extension                                                                                                        |                                                                                                                                                           |

|    | 18.3.3.SCL Low Timeout                                                                                                            |                                                                                                                                                           |

|    | 18.3.4.SCL High (SMBus Free) Timeout                                                                                              |                                                                                                                                                           |

|    | 18.4.Using the SMBus                                                                                                              |                                                                                                                                                           |

|    | 18.4.1.SMBus Configuration Register                                                                                               |                                                                                                                                                           |

|    | 18.4.2.SMB0CN Control Register                                                                                                    |                                                                                                                                                           |

|    | 18.4.3.Data Register                                                                                                              |                                                                                                                                                           |

|    | 18.5.SMBus Transfer Modes                                                                                                         | 210                                                                                                                                                       |

|    | 18.5.1.Master Transmitter Mode                                                                                                    |                                                                                                                                                           |

|    | 18.5.2.Master Receiver Mode                                                                                                       |                                                                                                                                                           |

|    | 18.5.3.Slave Receiver Mode                                                                                                        |                                                                                                                                                           |

|    | 18.5.4.Slave Transmitter Mode                                                                                                     |                                                                                                                                                           |

|    | 18.6.SMBus Status Decoding                                                                                                        |                                                                                                                                                           |

| 10 | .UART0                                                                                                                            |                                                                                                                                                           |

| 19 | 19.1.Enhanced Baud Rate Generation                                                                                                |                                                                                                                                                           |

|    |                                                                                                                                   |                                                                                                                                                           |

|    | 19.2.Operational Modes<br>19.2.1.8-Bit UART                                                                                       | 219                                                                                                                                                       |

|    | 19.2.1.8-Bit UART                                                                                                                 |                                                                                                                                                           |

|    | 19.3.Multiprocessor Communications                                                                                                |                                                                                                                                                           |

| 20 |                                                                                                                                   |                                                                                                                                                           |

| 20 | . Enhanced Serial Peripheral Interface (SPI0)                                                                                     | ZJZ                                                                                                                                                       |

|    |                                                                                                                                   |                                                                                                                                                           |

|    | 20.1.Signal Descriptions                                                                                                          | 233                                                                                                                                                       |

|    | 20.1.Signal Descriptions<br>20.1.1.Master Out, Slave In (MOSI)                                                                    | 233<br>233                                                                                                                                                |

|    | 20.1.Signal Descriptions<br>20.1.1.Master Out, Slave In (MOSI)<br>20.1.2.Master In, Slave Out (MISO)                              | 233<br>233<br>233                                                                                                                                         |

|    | 20.1.Signal Descriptions<br>20.1.1.Master Out, Slave In (MOSI)<br>20.1.2.Master In, Slave Out (MISO)<br>20.1.3.Serial Clock (SCK) | 233<br>233<br>233<br>233                                                                                                                                  |

|    | 20.1.Signal Descriptions                                                                                                          | 233<br>233<br>233<br>233<br>233                                                                                                                           |

|    | 20.1.Signal Descriptions                                                                                                          | 233<br>233<br>233<br>233<br>233<br>233                                                                                                                    |

|    | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>233<br>236                                                                                                      |

|    | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236                                                                                                      |

|    | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236                                                                                               |

| 24 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | <ul> <li>233</li> <li>233</li> <li>233</li> <li>233</li> <li>233</li> <li>236</li> <li>236</li> <li>236</li> <li>236</li> <li>239</li> <li>245</li> </ul> |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236<br>236                                                                                        |

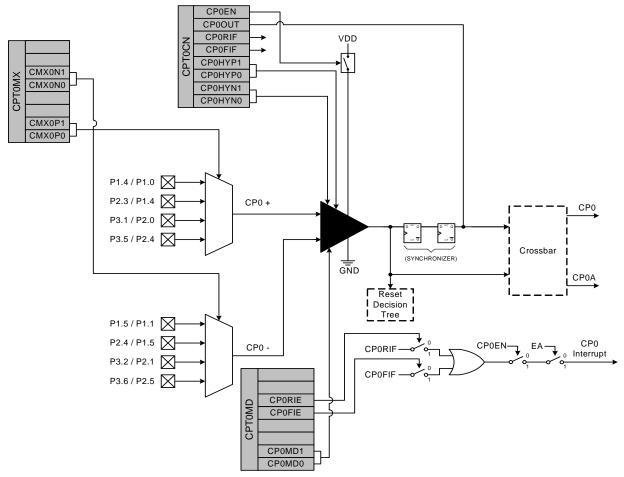

Figure 1.12. Comparator0 Block Diagram

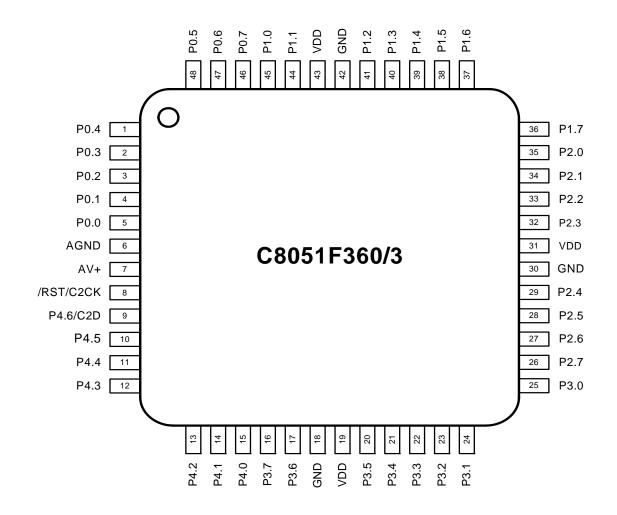

Figure 4.1. TQFP-48 Pinout Diagram (Top View)

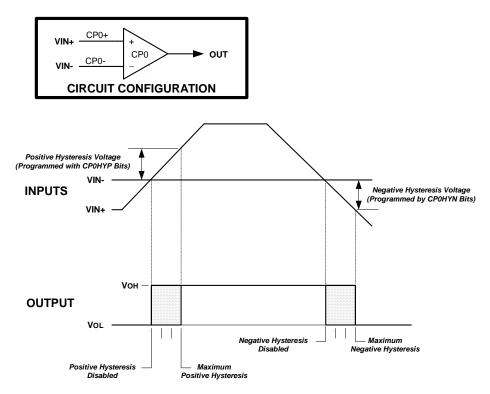

Figure 8.3. Comparator Hysteresis Plot

The Comparator hysteresis is software-programmable via the Comparator Control registers CPT0CN and CPT1CN. The user can program both the amount of hysteresis voltage (referred to the input voltage) and the positive and negative-going symmetry of this hysteresis around the threshold voltage.

The Comparator hysteresis is programmed using Bits3–0 in the Comparator Control registers CPT0CN and CPT1CN (shown in SFR Definition 8.1 and SFR Definition 8.4). The amount of negative hysteresis voltage is determined by the settings of the CP0HYN and CP1HYN bits. As shown in Figure 8.3, settings of 20, 10 or 5 mV of negative hysteresis can be programmed, or negative hysteresis can be disabled. In a similar way, the amount of positive hysteresis is determined by the setting the CP0HYP and CP1HYP bits.

Comparator interrupts can be generated on both rising-edge and falling-edge output transitions. (For Interrupt enable and priority control, see Section "10. Interrupt Handler" on page 107). The CP0FIF or CP1FIF flag is set to logic '1' upon a Comparator falling-edge occurrence, and the CP0RIF or CP1RIF flag is set to logic '1' upon the Comparator rising-edge occurrence. Once set, these bits remain set until cleared by software. The Comparator rising-edge interrupt mask is enabled by setting CP0RIE or CP1RIE to a logic '1'. The Comparator falling-edge interrupt mask is enabled by setting CP0FIE or CP1FIE to a logic '1'.

The output state of the Comparator can be obtained at any time by reading the CP0OUT or CP1OUT bit. The Comparator is enabled by setting the CP0EN or CP1EN bit to logic '1', and is disabled by clearing this bit to logic '0'.

Note that false rising edges and falling edges can be detected when the comparator is first powered on or if changes are made to the hysteresis or response time control bits. Therefore, it is recommended that the rising-edge and falling-edge flags be explicitly cleared to logic '0' a short time after the comparator is enabled or its mode bits have been changed. This Power Up Time is specified in Table 8.1 on page 79.

#### 9.3. Instruction Set

The instruction set of the CIP-51 System Controller is fully compatible with the standard MCS-51<sup>™</sup> instruction set; standard 8051 development tools can be used to develop software for the CIP-51. All CIP-51 instructions are the binary and functional equivalent of their MCS-51<sup>™</sup> counterparts, including opcodes, addressing modes and effect on PSW flags. However, instruction timing is different than that of the standard 8051.

#### 9.3.1. Instruction and CPU Timing

In many 8051 implementations, a distinction is made between machine cycles and clock cycles, with machine cycles varying from 2 to 12 clock cycles in length. However, the CIP-51 implementation is based solely on clock cycle timing. All instruction timings are specified in terms of clock cycles.

Due to the pipelined architecture of the CIP-51, most instructions execute in the same number of clock cycles as there are program bytes in the instruction. Conditional branch instructions take one less clock cycle to complete when the branch is not taken as opposed to when the branch is taken. Table 9.1 is the CIP-51 Instruction Set Summary, which includes the mnemonic, number of bytes, and number of clock cycles for each instruction.

#### 9.3.2. MOVX Instruction and Program Memory

In the CIP-51, the MOVX instruction serves three purposes: accessing on-chip XRAM, accessing off-chip XRAM, and accessing on-chip program Flash memory. The Flash access feature provides a mechanism for user software to update program code and use the program memory space for non-volatile data storage (see Section "13. Flash Memory" on page 135). The External Memory Interface provides a fast access to off-chip XRAM (or memory-mapped peripherals) via the MOVX instruction. Refer to Section "15. External Data Memory Interface and On-Chip XRAM" on page 152 for details.

| Mnemonic       | Description                              | Bytes | Clock<br>Cycles |

|----------------|------------------------------------------|-------|-----------------|

|                | Arithmetic Operations                    |       | •               |

| ADD A, Rn      | Add register to A                        | 1     | 1               |

| ADD A, direct  | Add direct byte to A                     | 2     | 2               |

| ADD A, @Ri     | Add indirect RAM to A                    | 1     | 2               |

| ADD A, #data   | Add immediate to A                       | 2     | 2               |

| ADDC A, Rn     | Add register to A with carry             | 1     | 1               |

| ADDC A, direct | Add direct byte to A with carry          | 2     | 2               |

| ADDC A, @Ri    | Add indirect RAM to A with carry         | 1     | 2               |

| ADDC A, #data  | Add immediate to A with carry            | 2     | 2               |

| SUBB A, Rn     | Subtract register from A with borrow     | 1     | 1               |

| SUBB A, direct | Subtract direct byte from A with borrow  | 2     | 2               |

| SUBB A, @Ri    | Subtract indirect RAM from A with borrow | 1     | 2               |

| SUBB A, #data  | Subtract immediate from A with borrow    | 2     | 2               |

| INC A          | Increment A                              | 1     | 1               |

| INC Rn         | Increment register                       | 1     | 1               |

| INC direct     | Increment direct byte                    | 2     | 2               |

| INC @Ri        | Increment indirect RAM                   | 1     | 2               |

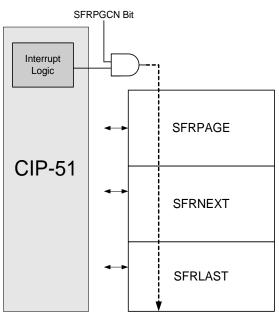

Figure 9.3. SFR Page Stack

Automatic hardware switching of the SFR Page on interrupts may be enabled or disabled as desired using the SFR Automatic Page Control Enable Bit located in the SFR Page Control Register (SFR0CN). This function defaults to 'enabled' upon reset. In this way, the autoswitching function will be enabled unless disabled in software.

A summary of the SFR locations (address and SFR page) is provided in Table 9.2. in the form of an SFR memory map. Each memory location in the map has an SFR page row, denoting the page in which that SFR resides. Note that certain SFR's are accessible from ALL SFR pages, and are denoted by the background shading in the table. For example, the Port I/O registers P0, P1, P2, and P3 all have a shaded background, indicating these SFR's are accessible from all SFR pages regardless of the SFRPAGE register value.

#### 11.2. Integer and Fractional Math

MAC0 is capable of interpreting the 16-bit inputs stored in MAC0A and MAC0B as signed integers or as signed fractional numbers. When the MAC0FM bit (MAC0CF.1) is cleared to '0', the inputs are treated as 16-bit, 2's complement, integer values. After the operation, the accumulator will contain a 40-bit, 2's complement, integer value. Figure 11.2 shows how integers are stored in the SFRs.

#### MAC0A and MAC0B Bit Weighting

|                                     | High Byte       |                 |     |     |                | Low Byte |    |                |                |    |                |                |                |    |

|-------------------------------------|-----------------|-----------------|-----|-----|----------------|----------|----|----------------|----------------|----|----------------|----------------|----------------|----|

| -(2 <sup>15</sup> ) 2 <sup>14</sup> | 2 <sup>13</sup> | 2 <sup>12</sup> | 211 | 210 | 2 <sup>9</sup> | 28       | 27 | 2 <sup>6</sup> | 2 <sup>5</sup> | 24 | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 20 |

| MAC0 Accumulator Bit Weighting |  |

|--------------------------------|--|

|--------------------------------|--|

| MACOOVR                                                             | MAC0ACC3 : MAC0ACC2 : MAC0ACC1 : MAC0ACC0              |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|--|--|--|--|

| -(2 <sup>39</sup> ) 2 <sup>38</sup> 2 <sup>33</sup> 2 <sup>32</sup> | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$ |  |  |  |  |  |  |  |  |

#### Figure 11.2. Integer Mode Data Representation

When the MACOFM bit is set to '1', the inputs are treated at 16-bit, 2's complement, fractional values. The decimal point is located between bits 15 and 14 of the data word. After the operation, the accumulator will contain a 40-bit, 2's complement, fractional value, with the decimal point located between bits 31 and 30. Figure 11.3 shows how fractional numbers are stored in the SFRs.

#### MAC0A, and MAC0B Bit Weighting

|    |     |     | High            | Byte |     |     |     |     |     |      | Low  | Byte                    |                  |                  |                  |  |

|----|-----|-----|-----------------|------|-----|-----|-----|-----|-----|------|------|-------------------------|------------------|------------------|------------------|--|

| -1 | 2-1 | 2-2 | 2 <sup>-3</sup> | 2-4  | 2-5 | 2-6 | 2-7 | 2-8 | 2-9 | 2-10 | 2-11 | <b>2</b> <sup>-12</sup> | 2 <sup>-13</sup> | 2 <sup>-14</sup> | 2 <sup>-15</sup> |  |

#### MAC0 Accumulator Bit Weighting

| MAC0OVR                                          |    | MA | C0AC | C3 :            | MAC0            | ACC2 : I | MAC0             | ACC1             | : MA             | C0AC | C0               |

|--------------------------------------------------|----|----|------|-----------------|-----------------|----------|------------------|------------------|------------------|------|------------------|

| -(2 <sup>8</sup> ) 2 <sup>7</sup> 2 <sup>2</sup> | 21 | 20 | 2-1  | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 22       | 2 <sup>-27</sup> | 2 <sup>-28</sup> | 2 <sup>-29</sup> | 2-30 | 2 <sup>-31</sup> |

#### MACORND Bit Weighting

|      |   |     |                 |                 |     |     |     | Low Byte |     |                 |      |                  |                         |                  |      |      |

|------|---|-----|-----------------|-----------------|-----|-----|-----|----------|-----|-----------------|------|------------------|-------------------------|------------------|------|------|

| * -2 | 1 | 2-1 | 2 <sup>-2</sup> | 2 <sup>-3</sup> | 2-4 | 2-5 | 2-6 | 2-7      | 2-8 | 2 <sup>-9</sup> | 2-10 | 2 <sup>-11</sup> | <b>2</b> <sup>-12</sup> | 2 <sup>-13</sup> | 2-14 | 2-15 |

\* The MACORND register contains the 16 LSBs of a two's complement number. The MACON Flag can be used to determine the sign of the MACORND register.

#### Figure 11.3. Fractional Mode Data Representation

|                     |        |         | Lock Status |

|---------------------|--------|---------|-------------|

|                     | TAG 0  | SLOT 0  | UNLOCKED    |

|                     | TAG 1  | SLOT 1  | UNLOCKED    |

| Cache Push          | TAG 2  | SLOT 2  | UNLOCKED    |

| Operations          |        |         | UNLOCKED    |

| Decrement<br>CHSLOT |        |         | 1           |

|                     |        |         |             |

|                     | TAG 26 | SLOT 26 | UNLOCKED    |

| CHSLOT = 27         | TAG 27 | SLOT 27 | UNLOCKED    |

| $\perp$             | TAG 28 | SLOT 28 | LOCKED      |

| Cache Pop           | TAG 29 | SLOT 29 | LOCKED      |

| Operations          | TAG 30 | SLOT 30 | LOCKED      |

| Increment           | TAG 31 | SLOT 31 | LOCKED      |

| CHSLOT              |        |         | -           |

Figure 14.3. Cache Lock Operation

| R         | R/W           | R/W                                   | R/W            | R                     | R/W             | R/W      | R/W         | Reset Value |

|-----------|---------------|---------------------------------------|----------------|-----------------------|-----------------|----------|-------------|-------------|

| XTLVLD    | XOSCME        | 02 XOSCMD1                            | XOSCMD0        | Reserved              | XFCN2           | XFCN1    | XFCN0       | 0000000     |

| Bit7      | Bit6          | Bit5                                  | Bit4           | Bit3                  | Bit2            | Bit1     | Bit0        |             |

| Bit 7:    | XTLVLD: C     | Crystal Oscilla                       | tor Valid Fla  | g.                    |                 |          |             |             |

|           | (Valid only   | when XOS                              | CMD = 11x.)    | -                     |                 |          |             |             |

|           | •             | Oscillator is u                       |                | •                     |                 |          |             |             |

|           |               | Oscillator is ru                      |                |                       |                 |          |             |             |

| Bits 6–4: |               | 2–0: External                         |                | ode Bits.             |                 |          |             |             |

|           |               | nal Oscillator                        |                |                       |                 |          |             |             |

|           |               | nal CMOS Clo                          |                | مرط مانينام م         |                 |          |             |             |

|           |               | nal CMOS Clo<br>scillator Mode        |                | th divide by          | z stage.        |          |             |             |

|           |               | citor Oscillato                       |                |                       |                 |          |             |             |

|           | •             | al Oscillator N                       |                |                       |                 |          |             |             |

|           | •             | al Oscillator N                       |                | vide by 2 sta         | ne              |          |             |             |

| Bit 3:    |               | D. Read = $0b$                        |                |                       | 90.             |          |             |             |

|           |               | External Osc                          |                |                       | l Bits.         |          |             |             |

|           |               | ee table belov                        |                | ,                     |                 |          |             |             |

| Γ         | XFCN          | Crystal (XO                           | SCMD = 11x     | () RC (XO             | SCMD = 10       | 00) C (X | OSCMD =     | 101)        |

|           | 000           | f ≤ 3                                 | 2 kHz          | f ≤                   | 25 kHz          | KI       | actor = 0.8 | 37          |

|           | 001           | 32 kHz <                              | f ≤ 84 kHz     | 25 kHz                | < f ≤ 50 k⊢     | lz K     | Factor = 2. | 6           |

|           | 010           | 84 kHz < f                            | ≤ 225 kHz      | 50 kHz                | < f ≤ 100 kl    | Hz K     | Factor = 7. | 7           |

|           | 011           | 225 kHz <                             | f ≤ 590 kHz    | 100 kHz               | < f ≤ 200 k     | Hz K     | Factor = 22 | 2           |

|           | 100           | 590 kHz <                             | f ≤ 1.5 MHz    | 200 kHz               | < f ≤ 400 k     | Hz K     | Factor = 6  | 5           |

|           | 101           | 1.5 MHz <                             | ≲f≤4 MHz       | 400 kHz               | < f ≤ 800 k     | Hz K     | Factor = 18 | 30          |

|           | 110           | 4 MHz < f                             | ≤ 10 MHz       | 800 kHz               | < f ≤ 1.6 M     | Hz K     | Factor = 66 | 64          |

|           | 111           | 10 MHz <                              | f ≤ 30 MHz     | 1.6 MHz               | $< f \le 3.2 M$ | IHz K F  | actor = 15  | 90          |

| COVETA    |               | ircuit from Fig                       |                | ntion 1. VOS          |                 | v)       |             |             |

| CRISIA    |               | FCN value to                          |                |                       |                 | ^)       |             |             |

|           |               | om Figure 16                          |                |                       |                 |          |             |             |

|           |               | CN value to                           |                |                       | ,               |          |             |             |

|           |               | <b>)<sup>3</sup>)/(R * C)</b> , wh    |                |                       |                 |          |             |             |

|           | •             | icy of oscillati                      |                |                       |                 |          |             |             |

|           |               | tor value in p                        |                |                       |                 |          |             |             |

|           |               | resistor value                        |                |                       |                 |          |             |             |

| C MODE    | (Circuit fror | n Figure 16.1                         | , Option 3; X  | (OSCMD = <sup>2</sup> | 10x)            |          |             |             |

|           |               | Factor (KF) for                       | or the oscilla | tion frequen          | cy desired:     |          |             |             |

|           | f = KF/(C *   | <sup>r</sup> V <sub>DD</sub> ), where |                |                       |                 |          |             |             |

|           | f = frequen   | cy of oscillati                       | on in MHz      |                       |                 |          |             |             |

|           |               | tor value on X                        |                |                       |                 |          |             |             |

|           |               | er Supply on                          | MOLL in Male   | 1-                    |                 |          |             |             |

#### SFR Definition 16.5. OSCXCN: External Oscillator Control

### 16.8. Phase-Locked Loop (PLL)

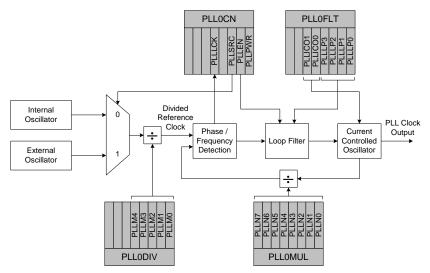

A Phase-Locked-Loop (PLL) is included, which is used to multiply the internal oscillator or an external clock source to achieve higher CPU operating frequencies. The PLL circuitry is designed to produce an output frequency between 25 MHz and 100 MHz, from a divided reference frequency between 5 MHz and 30 MHz. A block diagram of the PLL is shown in Figure 16.3.

Figure 16.3. PLL Block Diagram

#### 16.8.1. PLL Input Clock and Pre-divider

The PLL circuitry can derive its reference clock from either the internal oscillator or an external clock source. The PLLSRC bit (PLL0CN.2) controls which clock source is used for the reference clock (see SFR Definition 16.6). If PLLSRC is set to '0', the internal oscillator source is used. Note that the internal oscillator divide factor (as specified by bits IFCN1-0 in register OSCICN) will also apply to this clock. When PLL-SRC is set to '1', an external oscillator source will be used. The external oscillator should be active and settled before it is selected as a reference clock for the PLL circuit. The reference clock is divided down prior to the PLL circuit, according to the contents of the PLLM4-0 bits in the PLL Pre-divider Register (PLL0DIV), shown in SFR Definition 16.7.

#### 16.8.2. PLL Multiplication and Output Clock

The PLL circuitry will multiply the divided reference clock by the multiplication factor stored in the PLL0MUL register shown in SFR Definition 16.8. To accomplish this, it uses a feedback loop consisting of a phase/frequency detector, a loop filter, and a current-controlled oscillator (ICO). It is important to configure the loop filter and the ICO for the correct frequency ranges. The PLLLP3–0 bits (PLL0FLT.3–0) should be set according to the divided reference clock frequency. Likewise, the PLLICO1–0 bits (PLL0FLT.5–4) should be set according to the desired output frequency range. SFR Definition 16.9 describes the proper settings to use for the PLLLP3–0 and PLLICO1–0 bits. When the PLL is locked and stable at the desired frequency, the PLLLCK bit (PLL0CN.5) will be set to a '1'. The resulting PLL frequency will be set according to the equation:

PLL Frequency = Reference Frequency  $\times \frac{PLLN}{PLLM}$

Where "Reference Frequency" is the selected source clock frequency, PLLN is the PLL Multiplier, and PLLM is the PLL Pre-divider.

|            |   |   |         | P | 0        |   |   |   |   |   |         | F | <b>'</b> 1 |   |   |   |      |       |         | Р        | 2        |     |      |    |   |    |                       | Р   | 3         |           |                              |    |

|------------|---|---|---------|---|----------|---|---|---|---|---|---------|---|------------|---|---|---|------|-------|---------|----------|----------|-----|------|----|---|----|-----------------------|-----|-----------|-----------|------------------------------|----|

|            |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   | av | 93.1-<br>aila<br>48-p | ble | on        | ava<br>on | 5-P3<br>ilab<br>48-p<br>only | le |

|            |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| PIN I/O    | 0 | 1 | 2       | 3 | 4        | 5 | 6 | 7 | 0 | 1 | 2       | 3 | 4          | 5 | 6 | 7 | 0    | 1     | 2       | 3        | 4        | 5   | 6    | 7  | 0 | 1  | 2                     | 3   | 4         | 5         | 6                            | 7  |

| TX0<br>RX0 |   |   |         |   |          |   | I |   |   |   |         |   |            |   |   |   | (32- | pin   | and     | 28-p     | oin p    | ack | ages | 5) |   |    |                       |     |           |           |                              |    |

| кло<br>ТХ0 |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| RX0        |   |   |         | I |          |   |   |   |   |   |         |   |            |   |   |   | (48- | pin   | pack    | kage     | e)       |     |      |    |   |    |                       |     |           |           |                              |    |

| SCK        |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| MISO       |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| MOSI       |   |   |         | 1 |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| NSS*       |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   | (*4- | Wire  | e SP    |          | alv)     |     |      |    |   |    |                       |     |           |           |                              |    |

| SDA        |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   | ( +- | vviid | 5 01    | 101      | пу)      |     |      |    |   |    |                       |     |           |           |                              |    |

| SCL        |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| CP0        |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| CP0A       |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| CP1        |   |   |         |   |          |   |   |   |   |   |         | 1 |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| CP1A       |   |   |         |   |          |   |   |   |   |   | _       |   | 1          |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| /SYSCLK    |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| CEX0       |   |   |         |   |          |   |   |   |   |   | _       |   |            |   | 1 |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| CEX1       |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   | 1 |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| CEX2       |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| CEX3       | 1 |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| CEX4       |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| CEX5       |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| ECI        |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| то         |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

| T1         |   |   |         |   |          |   |   |   |   |   |         |   |            |   |   |   |      |       |         |          |          |     |      |    |   |    |                       |     |           |           |                              |    |

|            | 0 | 0 | 0<br>P( |   | 0<br>P[0 |   | 0 | 0 | 1 | 1 | 0<br>P1 |   | 0<br>IP[0  |   | 0 | 0 | 0    | 0     | 0<br>P2 | 0<br>SKI | 0<br>P[0 |     | 0    | 0  | 0 | 0  | 0<br>P3               |     | 0<br>P[0: | 0<br>7]   | 0                            | 0  |

Figure 17.4. Crossbar Priority Decoder with Port Pins Skipped

Registers XBR0 and XBR1 are used to assign the digital I/O resources to the physical I/O Port pins. Note that when the SMBus is selected, the Crossbar assigns both pins associated with the SMBus (SDA and SCL); when the UART is selected, the Crossbar assigns both pins associated with the UART (TX and RX). UART0 pin assignments are fixed for bootloading purposes: UART TX0 is always assigned to P0.1 (C8051F360/3) or P0.4 (C8051F361/2/4/5/6/7/8/9); UART RX0 is always assigned to P0.2 (C8051F361/2/4/5/6/7/8/9). Standard Port I/Os appear contiguously starting at P0.0 after prioritized functions and skipped pins are assigned.

**Important Note:** The SPI can be operated in either 3-wire or 4-wire modes, depending on the state of the NSSMD1-NSSMD0 bits in register SPI0CN. According to the SPI mode, the NSS signal may or may not be routed to a Port pin.

|      | : 0xB0                        | ,                                                           | essable)                                      |                              |             |          |      |            |

|------|-------------------------------|-------------------------------------------------------------|-----------------------------------------------|------------------------------|-------------|----------|------|------------|

| R/W  | R/W                           | R/W                                                         | R/W                                           | R/W                          | R/W         | R/W      | R/W  | Reset Valu |

| P3.7 | P3.6                          | P3.5                                                        | P3.4                                          | P3.3                         | P3.2        | P3.1     | P3.0 | 11111111   |

| Bit7 | Bit6                          | Bit5                                                        | Bit4                                          | Bit3                         | Bit2        | Bit1     | Bit0 |            |

|      | 0: Logic Low<br>1: Logic High | n Output (hi                                                | igh impedar                                   |                              | sponding P3 | BMDOUT.n | ,    | roodo Dort |

|      | 0: Logic Low                  | n Output (hi<br>ys reads '0'<br>nfigured as<br>s logic low. | igh impedar<br>i if selected<br>digital input | nce if corres<br>as analog i | sponding P3 | BMDOUT.n | ,    | reads Port |

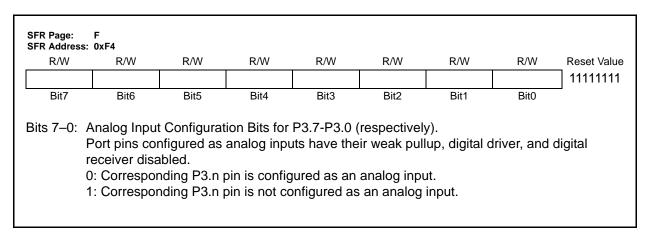

### SFR Definition 17.21. P3: Port3

#### SFR Definition 17.22. P3MDIN: Port3 Input Mode

#### 18.4.1. SMBus Configuration Register

The SMBus Configuration register (SMB0CF) is used to enable the SMBus Master and/or Slave modes, select the SMBus clock source, and select the SMBus timing and timeout options. When the ENSMB bit is set, the SMBus is enabled for all master and slave events. Slave events may be disabled by setting the INH bit. With slave events inhibited, the SMBus interface will still monitor the SCL and SDA pins; however, the interface will NACK all received addresses and will not generate any slave interrupts. When the INH bit is set, all slave events will be inhibited following the next START (interrupts will continue for the duration of the current transfer).

| SMBCS1 | SMBCS0 | SMBus Clock Source         |

|--------|--------|----------------------------|

| 0      | 0      | Timer 0 Overflow           |

| 0      | 1      | Timer 1 Overflow           |

| 1      | 0      | Timer 2 High Byte Overflow |

| 1      | 1      | Timer 2 Low Byte Overflow  |

#### Table 18.1. SMBus Clock Source Selection

The SMBCS1–0 bits select the SMBus clock source, which is used only when operating as a master or when the Free Timeout detection is enabled. When operating as a master, overflows from the selected source determine the absolute minimum SCL low and high times as defined in Equation 18.1. Note that the selected clock source may be shared by other peripherals so long as the timer is left running at all times. For example, Timer 1 overflows may generate the SMBus and UART baud rates simultaneously. Timer configuration is covered in Section "21. Timers" on page 245.

$$T_{HighMin} = T_{LowMin} = \frac{1}{f_{ClockSourceOverflow}}$$

#### Equation 18.1. Minimum SCL High and Low Times

The selected clock source should be configured to establish the minimum SCL High and Low times as per Equation 18.1. When the interface is operating as a master (and SCL is not driven or extended by any other devices on the bus), the typical SMBus bit rate is approximated by Equation 18.2.

#### 18.4.2. SMB0CN Control Register

SMB0CN is used to control the interface and to provide status information (see SFR Definition 18.2). The higher four bits of SMB0CN (MASTER, TXMODE, STA, and STO) form a status vector that can be used to jump to service routines. MASTER and TXMODE indicate the master/slave state and transmit/receive modes, respectively.

STA and STO indicate that a START and/or STOP has been detected or generated since the last SMBus interrupt. STA and STO are also used to generate START and STOP conditions when operating as a master. Writing a '1' to STA will cause the SMBus interface to enter Master Mode and generate a START when the bus becomes free (STA is not cleared by hardware after the START is generated). Writing a '1' to STO while in Master Mode will cause the interface to generate a STOP and end the current transfer after the next ACK cycle. If STO and STA are both set (while in Master Mode), a STOP followed by a START will be generated.

As a receiver, writing the ACK bit defines the outgoing ACK value; as a transmitter, reading the ACK bit indicates the value received on the last ACK cycle. ACKRQ is set each time a byte is received, indicating that an outgoing ACK value is needed. When ACKRQ is set, software should write the desired outgoing value to the ACK bit before clearing SI. A NACK will be generated if software does not write the ACK bit before clearing SI. SDA will reflect the defined ACK value immediately following a write to the ACK bit; however SCL will remain low until SI is cleared. If a received slave address is not acknowledged, further slave events will be ignored until the next START is detected.

The ARBLOST bit indicates that the interface has lost an arbitration. This may occur anytime the interface is transmitting (master or slave). A lost arbitration while operating as a slave indicates a bus error condition. ARBLOST is cleared by hardware each time SI is cleared.

The SI bit (SMBus Interrupt Flag) is set at the beginning and end of each transfer, after each byte frame, or when an arbitration is lost; see Table 18.3 for more details.

**Important Note About the SI Bit:** The SMBus interface is stalled while SI is set; thus SCL is held low, and the bus is stalled until software clears SI.

Table 18.3 lists all sources for hardware changes to the SMB0CN bits. Refer to Table 18.4 for SMBus status decoding using the SMB0CN register.

| SFR Definition | 18.2. SN | ABOCN: SME | Bus Control |

|----------------|----------|------------|-------------|

|----------------|----------|------------|-------------|

| SFR Address | R                                                                                           | R/W         | R/W          | R                         | R                | R/W           | R/W           | Reset Value    |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------------------|-------------|--------------|---------------------------|------------------|---------------|---------------|----------------|--|--|--|--|--|

| MASTER      | RTXMODE                                                                                     | STA         | STO          | ACKRQ                     | ARBLOST          | ACK           | SI            | 00000000       |  |  |  |  |  |

| Bit7        | Bit6                                                                                        | Bit5        | Bit4         | Bit3                      | Bit2             | Bit1          | Bit0          |                |  |  |  |  |  |

| Bit 7:      | MASTER: SM                                                                                  | Bus Maste   | er/Slave In  | dicator.                  |                  |               |               |                |  |  |  |  |  |

|             | This read-only                                                                              |             |              |                           | s operating a    | s a master    |               |                |  |  |  |  |  |

|             | 0: SMBus ope<br>1: SMBus ope                                                                | -           |              |                           |                  |               |               |                |  |  |  |  |  |

| Bit 6:      | TXMODE: SM                                                                                  | -           |              |                           |                  |               |               |                |  |  |  |  |  |

|             | This read-only                                                                              |             |              |                           | s operating a    | s a transm    | itter.        |                |  |  |  |  |  |

|             | 0: SMBus in F                                                                               |             |              |                           |                  |               |               |                |  |  |  |  |  |

|             | 1: SMBus in T                                                                               |             |              |                           |                  |               |               |                |  |  |  |  |  |

| Bit 5:      | STA: SMBus :<br>Write:                                                                      | Start Flag. |              |                           |                  |               |               |                |  |  |  |  |  |

|             | 0: No Start ge                                                                              | nerated     |              |                           |                  |               |               |                |  |  |  |  |  |

|             | 1: When operation                                                                           |             | master, a S  | START cond                | dition is transn | nitted if the | e bus is fre  | e (If the bus  |  |  |  |  |  |

|             |                                                                                             |             |              |                           | STOP is rece     |               |               |                |  |  |  |  |  |

|             |                                                                                             |             | e as an acti | ive Master,               | a repeated S     | TART will b   | be generat    | ted after the  |  |  |  |  |  |

|             | next ACK cy                                                                                 | /cle.       |              |                           |                  |               |               |                |  |  |  |  |  |

|             | Read:                                                                                       | ropostod    | Start datas  | tod                       |                  |               |               |                |  |  |  |  |  |

|             | 0: No Start or<br>1: Start or rep                                                           | •           |              |                           |                  |               |               |                |  |  |  |  |  |

| Bit 4:      | STO: SMBus                                                                                  |             |              |                           |                  |               |               |                |  |  |  |  |  |

|             | Write:                                                                                      |             |              |                           |                  |               |               |                |  |  |  |  |  |

|             | 0: No STOP c                                                                                |             |              |                           |                  |               |               |                |  |  |  |  |  |

|             | 1: Setting STO                                                                              |             |              |                           |                  |               |               |                |  |  |  |  |  |

|             | •                                                                                           |             |              | -                         | ed, hardware     |               | -             |                |  |  |  |  |  |

|             |                                                                                             | O are set,  | , a STOP c   | ondition is               | transmitted fo   | nowed by a    | asiari        | condition.     |  |  |  |  |  |

|             | Read:<br>0: No Stop condition detected.                                                     |             |              |                           |                  |               |               |                |  |  |  |  |  |

|             | 1: Stop condit                                                                              |             |              | ve Mode) o                | or pending (if i | in Master N   | Mode).        |                |  |  |  |  |  |

| Bit 3:      | ACKRQ: SME                                                                                  |             |              |                           |                  |               | ,             |                |  |  |  |  |  |

|             | This read-only bit is set to logic '1' when the SMBus has received a byte and needs the ACK |             |              |                           |                  |               |               |                |  |  |  |  |  |

| D'L O       | bit to be writte                                                                            |             |              |                           | e value.         |               |               |                |  |  |  |  |  |

| Bit 2:      | ARBLOST: SM<br>This read-only                                                               |             |              |                           |                  | visition      | while oper    | oting oc o     |  |  |  |  |  |

|             | transmitter. A                                                                              |             |              |                           |                  |               |               | aling as a     |  |  |  |  |  |

| Bit 1:      | ACK: SMBus                                                                                  |             |              |                           |                  |               |               |                |  |  |  |  |  |

|             | This bit define                                                                             |             |              | level and r               | ecords incomi    | ing ACK le    | vels. It sh   | ould be writ   |  |  |  |  |  |

|             | ten each time                                                                               |             |              |                           |                  |               |               |                |  |  |  |  |  |

|             | 0: A "not ackn                                                                              | •           | has been r   | eceived (if i             | n Transmitter    | Mode) OF      | R will be tra | ansmitted (if  |  |  |  |  |  |

|             | in Receiver                                                                                 | ,           | a haan raa   | aived (if in <sup>-</sup> |                  | ada) OP v     | ill be tree   | omittad (if in |  |  |  |  |  |

|             | 1: An "acknow<br>Receiver Me                                                                | -           | S DEGUIEC    | eiveu (II II)             |                  | UUE) UK W     | m be trans    | smilled (II If |  |  |  |  |  |

| Bit 0:      | SI: SMBus Int                                                                               | ,           | a.           |                           |                  |               |               |                |  |  |  |  |  |

|             | This bit is set                                                                             | •           | -            | ne conditior              | ns listed in Tab | ole 18.3. S   | I must be     | cleared by     |  |  |  |  |  |

|             | software. Whi                                                                               | •           |              |                           |                  |               |               |                |  |  |  |  |  |

|                                                           |                              |                      | Freq                             | uency: 11.059         | 2 MHz                                        |                  |                                  |

|-----------------------------------------------------------|------------------------------|----------------------|----------------------------------|-----------------------|----------------------------------------------|------------------|----------------------------------|

|                                                           | Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1–SCA0<br>(pre-scale select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

| ×                                                         | 230400                       | 0.00%                | 48                               | SYSCLK                | XX <b>2</b>                                  | 1                | 0xE8                             |

| Cloc                                                      | 115200                       | 0.00%                | 96                               | SYSCLK                | XX                                           | 1                | 0xD0                             |

| Timer Clock<br>Osc.                                       | 57600                        | 0.00%                | 192                              | SYSCLK                | XX                                           | 1                | 0xA0                             |

| Time<br>Osc.                                              | 28800                        | 0.00%                | 384                              | SYSCLK                | XX                                           | 1                | 0x40                             |

| and<br>nal                                                | 14400                        | 0.00%                | 768                              | SYSCLK/12             | 00                                           | 0                | 0xE0                             |

| -K a<br>xter                                              | 9600                         | 0.00%                | 1152                             | SYSCLK/12             | 00                                           | 0                | 0xD0                             |

| ЗCI                                                       | 2400                         | 0.00%                | 4608                             | SYSCLK/12             | 00                                           | 0                | 0x40                             |

| SYSCLK and 7<br>from External (                           | 1200                         | 0.00%                | 9216                             | SYSCLK/48             | 10                                           | 0                | 0xA0                             |

| sc.                                                       | 230400                       | 0.00%                | 48                               | EXTCLK/8              | 11                                           | 0                | 0xFD                             |

| LK from Internal Osc.,<br>Clock from External O           | 115200                       | 0.00%                | 96                               | EXTCLK/8              | 11                                           | 0                | 0xFA                             |

| n Exte                                                    | 57600                        | 0.00%                | 192                              | EXTCLK/8              | 11                                           | 0                | 0xF4                             |

| om Ir<br>k fron                                           | 28800                        | 0.00%                | 384                              | EXTCLK/8              | 11                                           | 0                | 0xE8                             |

| Cloc                                                      | 14400                        | 0.00%                | 768                              | EXTCLK/8              | 11                                           | 0                | 0xD0                             |

| SYSCLK from Internal Osc.,<br>Timer Clock from External O | 9600                         | 0.00%                | 1152                             | EXTCLK/8              | 11                                           | 0                | 0xB8                             |

| Notes:                                                    |                              | ad T1M bit dafin     | itiana aan ha                    | found in Section      | 01.1                                         |                  |                                  |

# Table 19.5. Timer Settings for Standard Baud RatesUsing an External 11.0592 MHz Oscillator

1. SCA1–SCA0 and T1M bit definitions can be found in Section 21.1.

**2.** X = Don't care.

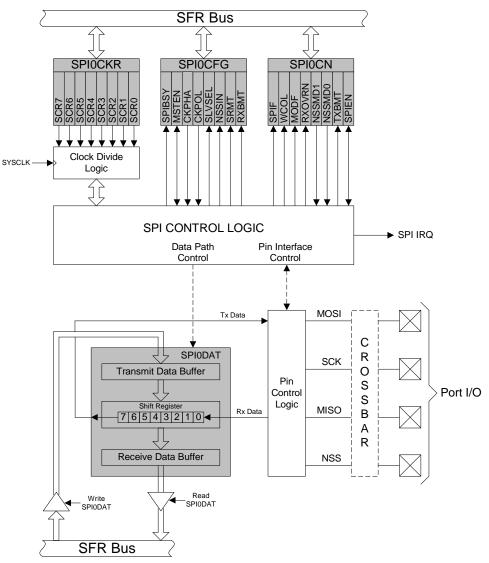

### 20. Enhanced Serial Peripheral Interface (SPI0)

The Enhanced Serial Peripheral Interface (SPI0) provides access to a flexible, full-duplex synchronous serial bus. SPI0 can operate as a master or slave device in both 3-wire or 4-wire modes, and supports multiple masters and slaves on a single SPI bus. The slave-select (NSS) signal can be configured as an input to select SPI0 in slave mode, or to disable Master Mode operation in a multi-master environment, avoiding contention on the SPI bus when more than one master attempts simultaneous data transfers. NSS can also be configured as a chip-select output in master mode, or disabled for 3-wire operation. Additional general purpose port I/O pins can be used to select multiple slave devices in master mode.

| SFR Definition | 20.2. | SPI0CN: | SPI0 | Control |

|----------------|-------|---------|------|---------|

|----------------|-------|---------|------|---------|

| R/W       | R/W                                                                                      | R/W                                                                                  | R/W                                                       | R/W                                                           | R/W                           | R             | R/W          | Reset Value |

|-----------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|-------------------------------|---------------|--------------|-------------|

| SPIF      | WCOL                                                                                     | MODF                                                                                 | RXOVRN                                                    | NSSMD1                                                        | NSSMD0                        | TXBMT         | SPIEN        | 00000110    |

| Bit7      | Bit6                                                                                     | Bit5                                                                                 | Bit4                                                      | Bit3                                                          | Bit2                          | Bit1          | Bit0         |             |

| Bit 7:    | SPIF: SPI0 I<br>This bit is se<br>setting this b                                         | t to logic '1<br>it causes th                                                        | ' by hardwa<br>ne CPU to v                                | ector to the                                                  | SPI0 interr                   | upt service   |              |             |

| Bit 6:    | automatically<br>WCOL: Write<br>This bit is se<br>the SPI0 dat<br>cleared by se          | e Collision I<br>t to logic '1<br>a register v                                       | -lag.<br>' by hardwa                                      | re (and gen                                                   | erates a SF                   | PIO interrup  |              |             |

| Bit 5:    | MODF: Mod<br>This bit is se<br>collision is do<br>matically cle                          | e Fault Flag<br>t to logic '1'<br>etected (NS                                        | by hardwa<br>S is low, M                                  | STEN = 1,                                                     | and NSSM                      | D[1:0] = 01)  | ,            |             |

| Bit 4:    | RXOVRN: R<br>This bit is se<br>fer still holds<br>shifted into the<br>be cleared b       | t to logic '1'<br>unread da<br>he SPI0 shi                                           | by hardwa<br>ta from a pr                                 | re (and gen<br>evious tran                                    | erates a SP<br>sfer and the   | last bit of t | he current   | transfer is |

| Bits 3–2: | NSSMD1–N<br>Selects betw<br>(See Section<br>00: 3-Wire S<br>01: 4-Wire S<br>1x: 4-Wire S | SSMD0: SI<br>veen the fol<br>20.2 and 3<br>lave or 3-w<br>lave or Mul<br>ingle-Maste | lowing NSS<br>Section 20.3<br>ire Master I<br>ti-Master M | operation r<br>3).<br>Vode. NSS<br>ode (Defau<br>SS signal is | signal is no<br>lt). NSS is a | lways an ir   | put to the o |             |

| Bit 1:    | TXBMT: Tran<br>This bit will b<br>data in the tr<br>indicating that                      | nsmit Buffe<br>be set to log<br>ansmit buff                                          | r Empty.<br>Jic '0' when<br>er is transfe                 | new data h<br>rred to the \$                                  | SPI shift reg                 | ister, this b |              |             |

| Bit O:    | SPIEN: SPIC<br>This bit enable<br>0: SPI disable                                         | ) Enable.<br>bles/disable                                                            |                                                           |                                                               |                               |               |              |             |

| SFR Page:<br>SFR Addres | all pages<br>s: 0x88                                                                                                            | (bit add      | ressable) |               |               |              |              |               |  |  |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------|-----------|---------------|---------------|--------------|--------------|---------------|--|--|--|--|--|

| R/W                     | R/W                                                                                                                             | R/W           | R/W       | R/W           | R/W           | R/W          | R/W          | Reset Value   |  |  |  |  |  |

| TF1                     | TR1                                                                                                                             | TF0           | TR0       | IE1           | IT1           | IE0          | IT0          | 0000000       |  |  |  |  |  |

| Bit7                    | Bit6                                                                                                                            | Bit5          | Bit4      | Bit3          | Bit2          | Bit1         | Bit0         |               |  |  |  |  |  |

| Bit 7:                  | TF1: Timer 2                                                                                                                    |               |           |               |               |              |              |               |  |  |  |  |  |

|                         | Set by hard                                                                                                                     |               |           |               | •             |              | •            |               |  |  |  |  |  |

|                         | matically cle                                                                                                                   |               |           | ectors to the | Timer 1 inte  | errupt serv  | ice routine  |               |  |  |  |  |  |

|                         | 0: No Timer                                                                                                                     |               |           |               |               |              |              |               |  |  |  |  |  |

| Bit 6:                  | 1: Timer 1 h<br>TR1: Timer                                                                                                      |               |           |               |               |              |              |               |  |  |  |  |  |

| 511 0.                  | 0: Timer 1 d                                                                                                                    |               | 101.      |               |               |              |              |               |  |  |  |  |  |

|                         | 1: Timer 1 e                                                                                                                    |               |           |               |               |              |              |               |  |  |  |  |  |

| Bit 5:                  | TF0: Timer (                                                                                                                    |               | Flag.     |               |               |              |              |               |  |  |  |  |  |

|                         | Set by hard                                                                                                                     |               |           | rflows. This  | flag can be   | e cleared b  | v software   | but is auto-  |  |  |  |  |  |

|                         | matically cle                                                                                                                   |               |           |               | •             |              | •            |               |  |  |  |  |  |

|                         | 0: No Timer                                                                                                                     |               |           |               |               |              |              |               |  |  |  |  |  |

|                         | 1: Timer 0 h                                                                                                                    | as overflow   | ed.       |               |               |              |              |               |  |  |  |  |  |