Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 100MHz                                                          |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, WDT                                                   |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1K x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                       |

| Data Converters            | -                                                               |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 28-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 28-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f365-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

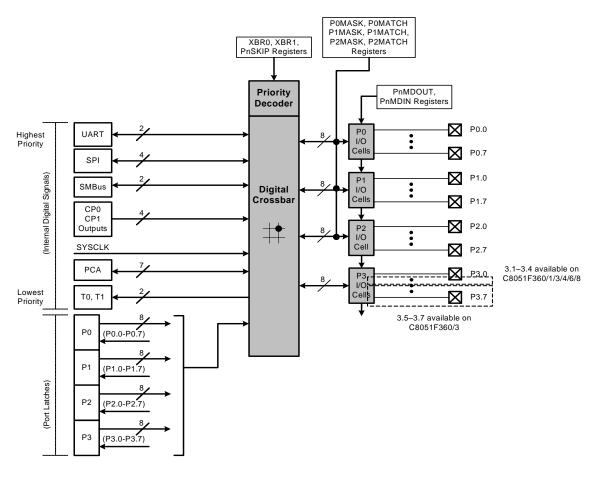

The Digital Crossbar allows mapping of internal digital system resources to Port I/O pins. (See Figure 1.8.) On-chip counter/timers, serial buses, HW interrupts, comparator output, and other digital signals in the controller can be configured to appear on the Port I/O pins specified in the Crossbar Control registers. This allows the user to select the exact mix of general purpose Port I/O and digital resources needed for the particular application.

#### 1.5. Serial Ports

The C8051F36x Family includes an SMBus/I<sup>2</sup>C interface, a full-duplex UART with enhanced baud rate configuration, and an Enhanced SPI interface. Each of the serial buses is fully implemented in hardware and makes extensive use of the CIP-51's interrupts, thus requiring very little CPU intervention.

#### 1.6. Programmable Counter Array

An on-chip Programmable Counter/Timer Array (PCA) is included in addition to the four 16-bit general purpose counter/timers. The PCA consists of a dedicated 16-bit counter/timer time base with three programmable capture/compare modules. The PCA clock is derived from one of six sources: the system clock divided by 12, the system clock divided by 4, Timer 0 overflows, an External Clock Input (ECI), the system clock, or the external oscillator clock source divided by 8. The external clock source selection is useful for

| R       | R                 | R                         | R/W                                                             | R/W                             | R/W        | R/W               | R/W          | Reset Valu |

|---------|-------------------|---------------------------|-----------------------------------------------------------------|---------------------------------|------------|-------------------|--------------|------------|

| -       | -                 | -                         | AMX0N4                                                          | AMX0N3                          | AMX0N2     | AMX0N1            | AMX0N0       | 0000000    |

| Bit7    | Bit6              | Bit5                      | Bit4                                                            | Bit3                            | Bit2       | Bit1              | Bit0         |            |

| ∘s7_5·I | INUSED R          | ead – 000                 | b; Write = do                                                   | n't care                        |            |                   |              |            |

|         |                   |                           | legative Inpu                                                   |                                 |            |                   |              |            |

|         |                   |                           | s selected as                                                   | -                               | •          | •                 | -            |            |

| r       | node. For al      | l other Ne                | gative Input                                                    | selections,                     | ADC0 opera | ates in Diffe     | erential mod | e.         |

| Г       |                   | AMX0N4                    | L-0                                                             |                                 |            | ative Input       |              |            |

| -       |                   | 00000 <sup>(1</sup>       |                                                                 |                                 | -          | .0 <sup>(1)</sup> |              |            |

| -       |                   | 000001 <sup>(1</sup>      |                                                                 |                                 |            | .1 <sup>(1)</sup> |              |            |

| -       |                   | 00001                     |                                                                 |                                 |            | .2 <sup>(1)</sup> |              |            |

| ŀ       |                   | 00010                     |                                                                 |                                 |            | .2 <sup>(1)</sup> |              |            |

| ŀ       |                   | 00011                     |                                                                 |                                 |            | 1.4               |              |            |

| -       |                   | 00100                     |                                                                 |                                 |            | 1.5               |              |            |

| -       |                   | 00110                     |                                                                 |                                 |            | 1.6               |              |            |

| _       |                   | 00111                     |                                                                 |                                 | P          | 1.7               |              |            |

|         |                   | 01000                     |                                                                 |                                 |            | 2.0               |              |            |

| _       |                   | 01001                     |                                                                 |                                 |            | 2.1               |              |            |

| -       |                   | 01010                     |                                                                 |                                 |            | 2.2               |              |            |

| -       |                   | 01011<br>01100            |                                                                 |                                 |            | 2.3<br>2.4        |              |            |

|         |                   | 01100                     |                                                                 |                                 |            | 2.4               |              |            |

| -       |                   | 01110                     |                                                                 |                                 |            | 2.6               |              |            |

|         |                   | 01111                     |                                                                 |                                 | P2         | 2.7               |              |            |

|         |                   | 10000                     |                                                                 |                                 |            | 3.0               |              |            |

|         |                   | 10001 <sup>(2</sup>       | 2)                                                              |                                 | P3.        | .1 <sup>(2)</sup> |              |            |

|         |                   | 10010 <sup>(2</sup>       |                                                                 |                                 | P3.        | 2 <sup>(2)</sup>  |              |            |

|         |                   | 10011 <sup>(2</sup>       | 2)                                                              |                                 | P3.        | .3 <sup>(2)</sup> |              |            |

| F       |                   | 10100 <sup>(2</sup>       | 2)                                                              |                                 | P3.        | 4 <sup>(2)</sup>  |              |            |

| F       |                   | 10101–11                  |                                                                 |                                 |            | RVED              |              |            |

|         |                   | 11110                     |                                                                 |                                 |            | REF               |              |            |

|         |                   | 11111                     |                                                                 |                                 | GI         | ND                |              |            |

|         | RESE<br>2. Only a | RVED on C<br>applies to C | 8051F361/2/6<br>28051F360 (4<br>8051F360/1/6<br>/9 (28-pin) dev | 8-pin) device<br>5/8 (48-pin ar |            |                   | ERVED        |            |

| Interrupt Source              | Interrupt<br>Vector | Priority<br>Order | Pending Flag                           | Bit addressable? | Cleared by HW? | Enable<br>Flag    | Priority<br>Control |

|-------------------------------|---------------------|-------------------|----------------------------------------|------------------|----------------|-------------------|---------------------|

| Programmable Counter<br>Array | 0x005B              | 11                | CF (PCA0CN.7)<br>CCFn (PCA0CN.n)       | Y                | Ν              | EPCA0<br>(EIE1.4) | PPCA0<br>(EIP1.4)   |

| Comparator0                   | 0x0063              | 12                | CP0FIF (CPT0CN.4)<br>CP0RIF (CPT0CN.5) | Ν                | Ν              | ECP0<br>(EIE1.5)  | PCP0<br>(EIP1.5)    |

| Comparator1                   | 0x006B              | 13                | CP1FIF (CPT1CN.4)<br>CP1RIF (CPT1CN.5) | Ν                | Ν              | ECP1<br>(EIE1.6)  | PCP1<br>(EIP1.6)    |

| Timer 3 Overflow              | 0x0073              | 14                | TF3H (TMR3CN.7)<br>TF3L (TMR3CN.6)     | Ν                | Ν              | ET3<br>(EIE1.7)   | PT3<br>(EIP1.7)     |

| RESERVED                      | 0x007B              | 15                | N/A                                    | N/A              | N/A            | N/A               | N/A                 |

| Port Match                    | 0x0083              | 16                | N/A                                    | N/A              | N/A            | EMAT<br>(EIE2.1)  | PMAT<br>(EIP2.1)    |

### Table 10.1. Interrupt Summary (Continued)

#### **10.4.** Interrupt Register Descriptions

The SFRs used to enable the interrupt sources and set their priority level are described below. Refer to the data sheet section associated with a particular on-chip peripheral for information regarding valid interrupt conditions for the peripheral and the behavior of its interrupt-pending flag(s).

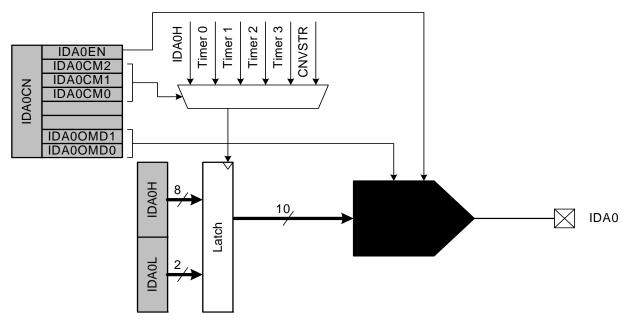

#### 12.1. Power-On Reset

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until V<sub>DD</sub> settles above V<sub>RST</sub>. A delay occurs before the device is released from reset; the delay decreases as the V<sub>DD</sub> ramp time increases (V<sub>DD</sub> ramp time is defined as how fast V<sub>DD</sub> ramps from 0 V to V<sub>RST</sub>). Figure 12.2. plots the power-on and V<sub>DD</sub> Monitor reset timing. For ramp times less than 1 ms, the power-on reset delay (T<sub>PORDe-lav</sub>) is typically less than 0.3 ms.

**Note:** The maximum  $V_{DD}$  ramp time is 1 ms; slower ramp times may cause the device to be released from reset before  $V_{DD}$  reaches the  $V_{RST}$  level.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic '1'. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000) software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset. The V<sub>DD</sub> Monitor is enabled following a power-on reset.

Figure 12.2. Power-On and V<sub>DD</sub> Monitor Reset Timing

| R                | R                                                                                                        | R/W                                                                                            | R/W                                                                                               | R                                                                                   | R/W                                                             | R/W                                                                        | R                                                               | Reset Value                                           |

|------------------|----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------|

| _                | FERROR                                                                                                   | CORSEF                                                                                         | SWRSF                                                                                             | WDTRSF                                                                              | MCDRSF                                                          | PORSF                                                                      | PINRSF                                                          | Variable                                              |

| Bit7             | Bit6                                                                                                     | Bit5                                                                                           | Bit4                                                                                              | Bit3                                                                                | Bit2                                                            | Bit1                                                                       | Bit0                                                            |                                                       |

| Note:Fo          | r bits that act a<br>read-modify-<br>C0RSEF, SV                                                          | write instru                                                                                   | ctions reac                                                                                       | l and modify                                                                        |                                                                 |                                                                            |                                                                 |                                                       |

| Bit 7:<br>Bit 6: | UNUSED. R<br>FERROR: FI                                                                                  |                                                                                                |                                                                                                   | t care.                                                                             |                                                                 |                                                                            |                                                                 |                                                       |

|                  | 0: Source of<br>1: Source of                                                                             | last reset w                                                                                   | as not a F                                                                                        |                                                                                     |                                                                 | ror.                                                                       |                                                                 |                                                       |

| Bit 5:           | CORSEF: Co<br>0: <b>Read:</b> Source.<br>1: <b>Read:</b> Source.                                         | urce of last                                                                                   | reset was                                                                                         | not Compar                                                                          | ator0. Write                                                    |                                                                            |                                                                 |                                                       |

| Bit 4:           | (active-low).<br>SWRSF: Sof<br>0: <b>Read:</b> Sof                                                       | urce of last                                                                                   | reset was                                                                                         | not a write t                                                                       |                                                                 |                                                                            |                                                                 |                                                       |

| Bit 3:           | 1: <b>Read:</b> Sou<br>WDTRSF: W<br>0: Source of<br>1: Source of                                         | /atchdog Tir<br>last reset w                                                                   | mer Reset<br>as not a W                                                                           | Flag.<br>/DT timeout                                                                |                                                                 | it. Write: F                                                               | orces a syst                                                    | em reset.                                             |

| Bit 2:           | MCDRSF: M<br>0: <b>Read:</b> So                                                                          | lissing Cloc                                                                                   | <pre>C Detector reset was</pre>                                                                   | Flag.                                                                               | g Clock Det                                                     | ector timed                                                                | out. <b>Write:</b> N                                            | lissing                                               |

| Bit 1:           | 1: <b>Read:</b> Sou<br>Detector e<br>PORSF: Pow<br>This bit is se<br>Monitor as a<br><b>and stabiliz</b> | urce of last<br>nabled; trigg<br>ver-On Res<br>t anytime a<br>reset sourc<br><b>ed may cau</b> | reset was a<br>gers a rese<br>et Force al<br>power-on<br>e. <b>Note: w</b><br><b>ise a syst</b> e | et if a missin<br>nd Flag.<br>reset occurs<br>r <b>riting '1' to</b><br>em reset. S | g clock cond<br>b. Writing thi<br>this bit bel<br>ee register V | dition is def<br>s bit enable<br><b>ore the V<sub>E</sub></b><br>/DM0CN (i | ected.<br>es/disables t<br>p <b>D Monitor</b> i<br>SFR Definiti | the V <sub>DD</sub><br>i <b>s enabled</b><br>on 12.1) |

| Bit 0:           | 0: Read: Las<br>reset sourd<br>1: Read: Las<br>indetermin<br>PINRSF: HW<br>0: Source of<br>1: Source of  | ce.<br>st reset was<br>ate. <b>Write:</b><br>/ Pin Reset<br>last reset w                       | a power-c<br>V <sub>DD</sub> Monit<br>Flag.<br>as <u>not RS</u>                                   | n or V <sub>DD</sub> Mo<br>or is a reset<br>T pin.                                  | onitor reset;                                                   |                                                                            |                                                                 | or is not a                                           |

#### SFR Definition 12.2. RSTSRC: Reset Source

#### **Table 13.2. Flash Electrical Characteristics**

$V_{DD}$  = 2.7 to 3.6 V; –40 to +85 °C.

| Parameter            | Conditions                             | Min  | Тур    | Max | Units       |

|----------------------|----------------------------------------|------|--------|-----|-------------|

| Flash Size           | C8051F360/1/2/3/4/5/6/7                |      | 32768* |     | Bytes       |

| F18511 5126          | C8051F368/9                            |      | 16384  |     | Dytes       |

| Endurance            |                                        | 20 k | 250 k  |     | Erase/Write |

| Erase Cycle Time     |                                        | 8    | 10     | 12  | ms          |

| Write Cycle Time     |                                        | 37   | 47     | 57  | μs          |

| *Note: 1024 Bytes at | location 0x7C00 to 0x7FFF are reserved |      |        |     | ·           |

| R/W       | R/W            | R/W           | R/W          | R/W           | R/W          | R/W         | R/W          | Reset Value   |

|-----------|----------------|---------------|--------------|---------------|--------------|-------------|--------------|---------------|

|           | CHMS           | SCTL          |              | CHALGM        | CHFIXM       | CHM         | ISTH         | 00000100      |

| Bit7      | Bit6           | Bit5          | Bit4         | Bit3          | Bit2         | Bit1        | Bit0         |               |

| Bits 7–4: | CHMSCTL: (     | Cache Miss    | Penalty A    | ccumulator    | Bits 4–1).   |             |              |               |

|           | These are bi   |               | •            |               | · ,          | To read the | ese bits, th | ney must firs |

|           | be latched by  |               |              |               |              |             |              |               |

|           | 14.4).         | -             |              |               |              |             |              |               |

| Bit 3:    | CHALGM: C      | ache Algor    | ithm Selec   | t.            |              |             |              |               |

|           | This bit seled | cts the cach  | ne replacer  | nent algorith | m.           |             |              |               |

|           | 0: Cache use   | es Rebound    | d algorithm  |               |              |             |              |               |

|           | 1: Cache use   | es Pseudo-    | random alg   | gorithm.      |              |             |              |               |

| Bit 2:    | CHFIXM: Ca     | che Fix MC    | OVC Enabl    | e.            |              |             |              |               |

|           | This bit force | s MOVC w      | rites to the | cache mem     | ory to use s | lot 0.      |              |               |

|           | 0: MOVC da     | ta is written | according    | to the curre  | nt algorithm | selected b  | y the CHA    | ALGM bit.     |

|           | 1: MOVC da     | ta is always  | s written to | cache slot 0  |              |             |              |               |

| Bits 1–0: | CHMSTH: C      |               |              |               |              |             |              |               |

|           | These bits de  |               | •            |               | data will be | cached.     |              |               |

|           |                |               |              |               |              |             |              |               |

### SFR Definition 14.2. CCH0TN: Cache Tuning

Rev. 1.1

#### 15.4.2. Non-multiplexed Configuration

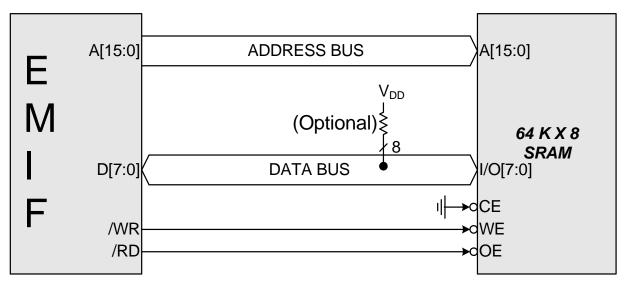

In Non-multiplexed mode, the Data Bus and the Address Bus pins are not shared. An example of a Non-multiplexed Configuration is shown in Figure 15.2. See Section "15.6.1. Non-multiplexed Mode" on page 161 for more information about Non-multiplexed operation.

Figure 15.2. Non-multiplexed Configuration Example

To shut down the PLL, the system clock should be switched to the internal oscillator or a stable external clock source, using the CLKSEL register. Next, disable the PLL by setting PLLEN (PLL0CN.1) to '0'. Finally, the PLL can be powered off, by setting PLLPWR (PLL0CN.0) to '0'. Note that the PLLEN and PLL-PWR bits can be cleared at the same time.

| R/W       | R/W           | R/W          | R             | R/W             | R/W          | R/W     | R/W    | Reset Value |

|-----------|---------------|--------------|---------------|-----------------|--------------|---------|--------|-------------|

| _         | -             | -            | PLLLCK        | Reserved        | PLLSRC       | PLLEN   | PLLPWR | 0000000     |

| Bit7      | Bit6          | Bit5         | Bit4          | Bit3            | Bit2         | Bit1    | Bit0   | -           |

| Bits 7–5: | UNUSED. R     | ead = 000    | o. Write = do | on't care.      |              |         |        |             |

| Bit 4:    | PLLLCK: PL    | L Lock Fla   | g.            |                 |              |         |        |             |

|           | 0: PLL Frequ  | lency is no  | t locked.     |                 |              |         |        |             |

|           | 1: PLL Frequ  | lency is loo | cked.         |                 |              |         |        |             |

| Bit 3:    | RESERVED      | . Read = 0   | b. Must Writ  | e 0b.           |              |         |        |             |

| Bit 2:    | PLLSRC: PL    | L Referen    | ce Clock So   | urce Select E   | Bit.         |         |        |             |

|           | 0: PLL Refer  | ence Cloc    | < Source is I | Internal Oscil  | lator.       |         |        |             |

|           | 1: PLL Refer  | ence Cloc    | < Source is I | External Osci   | llator.      |         |        |             |

| Bit 1:    | PLLEN: PLL    | Enable Bit   |               |                 |              |         |        |             |

|           | 0: PLL is hel | d in reset.  |               |                 |              |         |        |             |

|           | 1: PLL is ena | abled. PLL   | PWR must b    | be '1'.         |              |         |        |             |

| Bit 0:    | PLLPWR: PI    | L Power E    | nable.        |                 |              |         |        |             |

|           | 0: PLL bias   | generator is | s de-activate | ed. No static j | power is cor | nsumed. |        |             |

|           |               |              |               |                 |              |         |        |             |

### SFR Definition 16.6. PLL0CN: PLL Control

#### SFR Definition 16.7. PLL0DIV: PLL Pre-divider

| SFR Page:<br>SFR Address:<br>R/W | F<br>0xA9<br>R/W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W                                        | R/W                                           | R/W                                        | R/W   | R/W   | R/W   | Reset Value |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------------------|--------------------------------------------|-------|-------|-------|-------------|

| _                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                                          | PLLM4                                         | PLLM3                                      | PLLM2 | PLLM1 | PLLM0 | 00000001    |

| Bit7                             | Bit6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit5                                       | Bit4                                          | Bit3                                       | Bit2  | Bit1  | Bit0  | _           |

| Bits 4–0: F<br>T<br>v            | INUSED. Republic Repu | LL Referen<br>elect the pro<br>ference clo | ce Clock Pr<br>e-divide valı<br>ck will be di | e-divider.<br>ue of the PL<br>vided by the |       |       |       | •           |

|      | : 0xB0                        | ,                                                                      | essable)                                  |                              |             |          |      |            |

|------|-------------------------------|------------------------------------------------------------------------|-------------------------------------------|------------------------------|-------------|----------|------|------------|

| R/W  | R/W                           | R/W                                                                    | R/W                                       | R/W                          | R/W         | R/W      | R/W  | Reset Valu |

| P3.7 | P3.6                          | P3.5                                                                   | P3.4                                      | P3.3                         | P3.2        | P3.1     | P3.0 | 11111111   |

| Bit7 | Bit6                          | Bit5                                                                   | Bit4                                      | Bit3                         | Bit2        | Bit1     | Bit0 |            |

|      | 0: Logic Low<br>1: Logic High | <sup>y</sup> Output.<br>n Output (hi                                   | igh impedar                               | nce if corres                |             | BMDOUT.n | ,    | raada Dart |

|      | 0: Logic Low                  | Output.<br>n Output (hi<br>ys reads '0'<br>nfigured as<br>s logic low. | gh impedar<br>if selected<br>digital inpu | nce if corres<br>as analog i | sponding P3 | BMDOUT.n | ,    | reads Port |

### SFR Definition 17.21. P3: Port3

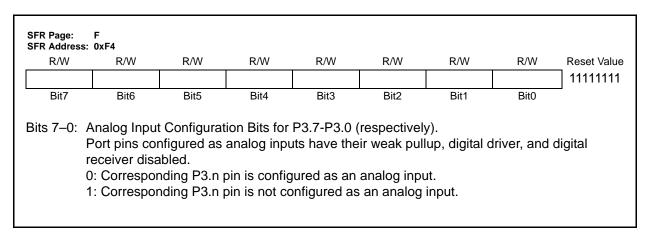

#### SFR Definition 17.22. P3MDIN: Port3 Input Mode

| SFR Addres<br>R/W | R/W                                        | R                                                         | R/W                                                  | R/W                                                 | R/W                                                                | R/W           | R/W            | Reset Value |

|-------------------|--------------------------------------------|-----------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------|---------------|----------------|-------------|

| ENSME             |                                            | BUSY                                                      | EXTHOLD                                              | SMBTOE                                              | SMBFTE                                                             | SMBCS1        | SMBCS0         | 0000000     |

| Bit7              | Bit6                                       | Bit5                                                      | Bit4                                                 | Bit3                                                | Bit2                                                               | Bit1          | Bit0           | ]           |

|                   |                                            |                                                           |                                                      |                                                     |                                                                    |               |                |             |

| Bit 7:            | ENSMB: SM                                  | IBus Enable                                               | Э.                                                   |                                                     |                                                                    |               |                |             |

|                   | This bit enab                              |                                                           |                                                      | s interface.                                        | When enal                                                          | oled, the int | erface const   | antly mon-  |

|                   | itors the SD                               |                                                           |                                                      |                                                     |                                                                    |               |                |             |

|                   | 0: SMBus in                                |                                                           |                                                      |                                                     |                                                                    |               |                |             |

|                   | 1: SMBus in                                |                                                           |                                                      |                                                     |                                                                    |               |                |             |

| Bit 6:            | INH: SMBus                                 |                                                           |                                                      |                                                     |                                                                    |               |                |             |

|                   | When this bi                               |                                                           | -                                                    |                                                     | -                                                                  |               | •              |             |

|                   | occur. This e                              | •                                                         | emoves the                                           | SMBus sla                                           | ve from the                                                        | bus. Maste    | r Mode inter   | rupts are   |

|                   | not affected.                              |                                                           |                                                      |                                                     |                                                                    |               |                |             |

|                   | 0: SMBus S                                 |                                                           |                                                      |                                                     |                                                                    |               |                |             |

|                   | 1: SMBus S                                 |                                                           |                                                      |                                                     |                                                                    |               |                |             |

| Bit 5:            | BUSY: SMB                                  |                                                           |                                                      |                                                     |                                                                    |               |                | - I         |

|                   | This bit is se                             | -                                                         | •                                                    |                                                     | ransier is in                                                      | progress.     | t is cleared t | o logic u   |

| D:+ 4.            | when a STC                                 |                                                           |                                                      |                                                     | naian Frah                                                         |               |                |             |

| Bit 4:            | EXTHOLD:                                   |                                                           | •                                                    |                                                     |                                                                    |               |                |             |

|                   | This bit cont                              |                                                           | •                                                    |                                                     | -                                                                  | 10.           |                |             |

|                   | 0: SDA Exte<br>1: SDA Exte                 | •                                                         |                                                      |                                                     |                                                                    |               |                |             |

| Bit 3:            | SMBTOE: S                                  |                                                           |                                                      |                                                     |                                                                    |               |                |             |

| DIL J.            | This bit enal                              |                                                           |                                                      |                                                     |                                                                    | 1' the SME    | Rus forces Ti  | mer 3 to    |

|                   | reload while                               |                                                           |                                                      |                                                     | -                                                                  |               |                |             |

|                   | figured to Sp                              | -                                                         |                                                      |                                                     |                                                                    | -             |                |             |

|                   | Timer 3 sho                                |                                                           | • •                                                  | •                                                   |                                                                    |               |                | -           |

|                   | service routi                              |                                                           | -                                                    |                                                     | •                                                                  | .5 113, and 1 |                | monupi      |

| Bit 2:            | SMBFTE: S                                  |                                                           |                                                      |                                                     |                                                                    |               |                |             |

| 511 2.            | When this b                                |                                                           |                                                      |                                                     |                                                                    | free if SCL   | and SDA rer    | nain high   |

|                   | for more tha                               |                                                           | •                                                    |                                                     |                                                                    |               |                |             |

|                   |                                            |                                                           |                                                      | •                                                   |                                                                    |               |                |             |

| Bits 1–0:         | SMBCS1-S                                   |                                                           | IBUS CIOCK                                           | Source Sel                                          | ection.                                                            |               |                |             |

| Bits 1–0:         |                                            | MBCS0: SN                                                 |                                                      |                                                     |                                                                    | sed to gene   | rate the SMI   | Bus bit     |

| Bits 1–0:         | These two b                                | MBCS0: SN<br>its select th                                | e SMBus cl                                           | ock source                                          | which is us                                                        | -             |                | Bus bit     |

| Bits 1–0:         | These two b<br>rate. The se                | MBCS0: SN<br>its select th                                | e SMBus clo<br>e should be                           | ock source<br>e configured                          | which is us<br>according                                           | -             |                | Bus bit     |

| Bits 1–0:         | These two b                                | MBCS0: SN<br>its select th                                | e SMBus clo<br>e should be<br>SMI                    | ock source<br>configured<br>Bus Clock               | which is us<br>according<br><b>Source</b>                          | -             |                | Bus bit     |

| Bits 1–0:         | These two b<br>rate. The se<br>SMBCS1<br>0 | MBCS0: SN<br>its select th<br>lected devic                | e SMBus clo<br>ce should be<br>SMI                   | ock source<br>configured<br>Bus Clock<br>īmer 0 Ove | which is us<br>according<br>Source<br>rflow                        | -             |                | Bus bit     |

| Bits 1–0:         | These two b<br>rate. The se                | MBCS0: SN<br>its select th<br>lected devic<br>SMBCS0      | e SMBus clo<br>e should be<br>SMI<br>T<br>T          | ock source<br>configured<br>Bus Clock<br>imer 0 Ove | which is us<br>according<br>Source<br>rflow<br>rflow               | -             |                | Bus bit     |

| Bits 1–0:         | These two b<br>rate. The se<br>SMBCS1<br>0 | MBCS0: SN<br>its select th<br>lected devic<br>SMBCS0<br>0 | e SMBus clo<br>e should be<br>SMI<br>T<br>T<br>Timer | ock source<br>configured<br>Bus Clock<br>īmer 0 Ove | which is us<br>according<br>Source<br>rflow<br>rflow<br>e Overflow | -             |                | 3us bit     |

### SFR Definition 18.1. SMB0CF: SMBus Clock/Configuration

#### 18.4.2. SMB0CN Control Register

SMB0CN is used to control the interface and to provide status information (see SFR Definition 18.2). The higher four bits of SMB0CN (MASTER, TXMODE, STA, and STO) form a status vector that can be used to jump to service routines. MASTER and TXMODE indicate the master/slave state and transmit/receive modes, respectively.

STA and STO indicate that a START and/or STOP has been detected or generated since the last SMBus interrupt. STA and STO are also used to generate START and STOP conditions when operating as a master. Writing a '1' to STA will cause the SMBus interface to enter Master Mode and generate a START when the bus becomes free (STA is not cleared by hardware after the START is generated). Writing a '1' to STO while in Master Mode will cause the interface to generate a STOP and end the current transfer after the next ACK cycle. If STO and STA are both set (while in Master Mode), a STOP followed by a START will be generated.

As a receiver, writing the ACK bit defines the outgoing ACK value; as a transmitter, reading the ACK bit indicates the value received on the last ACK cycle. ACKRQ is set each time a byte is received, indicating that an outgoing ACK value is needed. When ACKRQ is set, software should write the desired outgoing value to the ACK bit before clearing SI. A NACK will be generated if software does not write the ACK bit before clearing SI. SDA will reflect the defined ACK value immediately following a write to the ACK bit; however SCL will remain low until SI is cleared. If a received slave address is not acknowledged, further slave events will be ignored until the next START is detected.

The ARBLOST bit indicates that the interface has lost an arbitration. This may occur anytime the interface is transmitting (master or slave). A lost arbitration while operating as a slave indicates a bus error condition. ARBLOST is cleared by hardware each time SI is cleared.

The SI bit (SMBus Interrupt Flag) is set at the beginning and end of each transfer, after each byte frame, or when an arbitration is lost; see Table 18.3 for more details.

**Important Note About the SI Bit:** The SMBus interface is stalled while SI is set; thus SCL is held low, and the bus is stalled until software clears SI.

Table 18.3 lists all sources for hardware changes to the SMB0CN bits. Refer to Table 18.4 for SMBus status decoding using the SMB0CN register.

#### 18.4.3. Data Register

The SMBus Data register SMB0DAT holds a byte of serial data to be transmitted or one that has just been received. Software may safely read or write to the data register when the SI flag is set. Software should not attempt to access the SMB0DAT register when the SMBus is enabled and the SI flag is cleared to logic '0', as the interface may be in the process of shifting a byte of data into or out of the register.

Data in SMB0DAT is always shifted out MSB first. After a byte has been received, the first bit of received data is located at the MSB of SMB0DAT. While data is being shifted out, data on the bus is simultaneously being shifted in. SMB0DAT always contains the last data byte present on the bus. In the event of lost arbitration, the transition from master transmitter to slave receiver is made with the correct data or address in SMB0DAT.

| R/W    | R/W                                                       | R/W                        | R/W                       | R/W          | R/W        | R/W           | R/W        | Reset Value |

|--------|-----------------------------------------------------------|----------------------------|---------------------------|--------------|------------|---------------|------------|-------------|

|        |                                                           |                            |                           |              |            |               |            | 0000000     |

| Bit7   | Bit6                                                      | Bit5                       | Bit4                      | Bit3         | Bit2       | Bit1          | Bit0       |             |

| -<br>1 | SMB0DAT: \$<br>The SMB0D<br>face or a by<br>from or write | OAT register te that has j | contains a<br>ust been re | ceived on th | ne SMBus s | erial interfa | ce. The CF | PU can read |

#### SFR Definition 18.3. SMB0DAT: SMBus Data

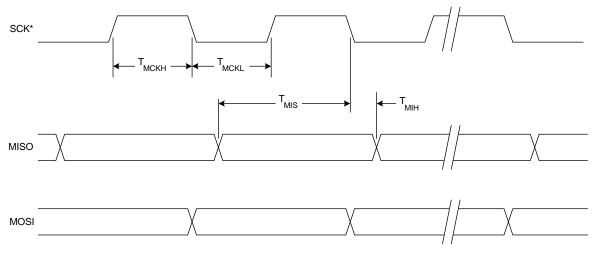

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

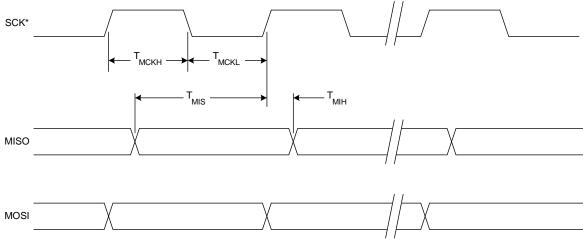

\* SCK is shown for CKPOL = 0. SCK is the opposite polarity for CKPOL = 1.

### Figure 20.9. SPI Master Timing (CKPHA = 1)

#### 21.1.4. Mode 3: Two 8-bit Counter/Timers (Timer 0 Only)

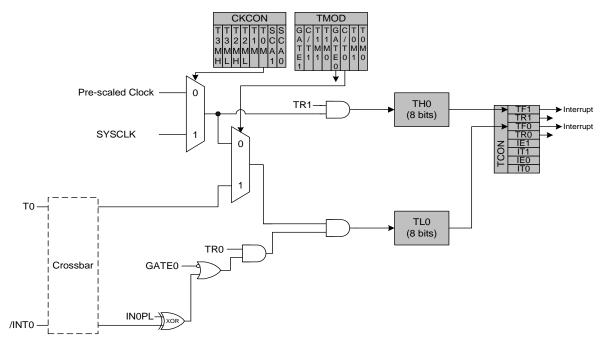

In Mode 3, Timer 0 is configured as two separate 8-bit counter/timers held in TL0 and TH0. The counter/timer in TL0 is controlled using the Timer 0 control/status bits in TCON and TMOD: TR0, C/T0, GATE0 and TF0. TL0 can use either the system clock or an external input signal as its timebase. The TH0 register is restricted to a timer function sourced by the system clock or prescaled clock. TH0 is enabled using the Timer 1 run control bit TR1. TH0 sets the Timer 1 overflow flag TF1 on overflow and thus controls the Timer 1 interrupt.

Timer 1 is inactive in Mode 3. When Timer 0 is operating in Mode 3, Timer 1 can be operated in Modes 0, 1 or 2, but cannot be clocked by external signals nor set the TF1 flag and generate an interrupt. However, the Timer 1 overflow can be used to generate baud rates for the SMBus and/or UART, and/or initiate ADC conversions. While Timer 0 is operating in Mode 3, Timer 1 run control is handled through its mode settings. To run Timer 1 while Timer 0 is in Mode 3, set the Timer 1 Mode as 0, 1, or 2. To disable Timer 1, configure it for Mode 3.

Figure 21.3. T0 Mode 3 Block Diagram

| R/W              | R/W                                                                                                                                                                                         | R/W          | R/W          | R/W           | R/W           | R            | R/W             | Reset Value |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|---------------|---------------|--------------|-----------------|-------------|

| TF3H             | TF3L                                                                                                                                                                                        | TF3LEN       | TF3CEN       | T3SPLIT       | TR3           | _            | T3XCLK          | 0000000     |

| Bit7             | Bit6                                                                                                                                                                                        | Bit5         | Bit4         | Bit3          | Bit2          | Bit1         | Bit0            | 3           |

| Bit 7:           | TF3H: Timer 3 High Byte Overflow Flag.                                                                                                                                                      |              |              |               |               |              |                 |             |

|                  | Set by hardware when the Timer 3 high byte overflows from 0xFF to 0x00. In 16 bit mode,                                                                                                     |              |              |               |               |              |                 |             |

|                  | this will occur when Timer 3 overflows from 0xFFFF to 0x0000. When the Timer 3 interrupt is                                                                                                 |              |              |               |               |              |                 |             |

|                  | enabled, setting this bit causes the CPU to vector to the Timer 3 interrupt service routine.<br>TF3H is not automatically cleared by hardware and must be cleared by software.              |              |              |               |               |              |                 |             |

|                  |                                                                                                                                                                                             |              |              |               | and must l    | be cleared   | by software     | •           |

| Bit 6:           | TF3L: Timer                                                                                                                                                                                 |              |              | •             |               | o == /       | 0 00 14/        |             |

|                  | Set by hard                                                                                                                                                                                 |              |              |               |               |              |                 |             |

|                  | set, an interrupt will be generated if TF3LEN is set and Timer 3 interrupts are enabled. TF3L will set when the low byte overflows regardless of the Timer 3 mode. This bit is not automat  |              |              |               |               |              |                 |             |

|                  | ically cleared                                                                                                                                                                              |              |              | s regardless  |               | er s mode    | . This bit is n | iot automa  |

| Bit 5:           | TF3LEN: Tir                                                                                                                                                                                 | •            |              | ot Enable     |               |              |                 |             |

| DIL J.           |                                                                                                                                                                                             |              | •            |               | errunts If T  | F3I FN is a  | set and Time    | r 3 inter-  |

|                  | This bit enables/disables Timer 3 Low Byte interrupts. If TF3LEN is set and Timer 3 inter-<br>rupts are enabled, an interrupt will be generated when the low byte of Timer 3 overflows.     |              |              |               |               |              |                 |             |

|                  | 0: Timer 3 Low Byte interrupts disabled.                                                                                                                                                    |              |              |               |               |              |                 |             |

|                  | 1: Timer 3 L                                                                                                                                                                                |              | •            |               |               |              |                 |             |

| Bit 4:           | TF3CEN: Ti                                                                                                                                                                                  |              |              |               | apture Enal   | ole.         |                 |             |

|                  | This bit enables/disables Timer 3 Low-Frequency Oscillator Capture Mode. If TF3CEN is se                                                                                                    |              |              |               |               |              |                 |             |

|                  | and Timer 3 interrupts are enabled, an interrupt will be generated on a rising edge of the                                                                                                  |              |              |               |               |              |                 |             |

|                  | low-frequency oscillator output, and the current 16-bit timer value in TMR3H:TMR3L will be                                                                                                  |              |              |               |               |              |                 |             |

|                  | copied to TMR3RLH:TMR3RLL. See Section "16. Oscillators" on page 168 for more details                                                                                                       |              |              |               |               |              |                 |             |

|                  | 0: Timer 3 Low-Frequency Oscillator Capture disabled.                                                                                                                                       |              |              |               |               |              |                 |             |

|                  | 1: Timer 3 L                                                                                                                                                                                | •            | •            | •             | enabled.      |              |                 |             |

| Bit 3:<br>Bit 2: | T3SPLIT: Ti                                                                                                                                                                                 | •            |              |               |               |              |                 |             |

|                  | When this b                                                                                                                                                                                 |              | •            |               |               | vith auto-re | eload.          |             |

|                  | 0: Timer 3 o                                                                                                                                                                                |              |              |               |               |              |                 |             |

|                  | 1: Timer 3 o                                                                                                                                                                                | •            |              | to-reload tir | ners.         |              |                 |             |

| DIL Z.           | TR3: Timer                                                                                                                                                                                  |              | -            | n 9 hit mod   | o thio hit or | oblog/dig    |                 |             |

|                  | This bit enal<br>TMR3L is al                                                                                                                                                                |              |              |               |               | 100165/0150  |                 | i oniy,     |

|                  | 0: Timer 3 d                                                                                                                                                                                | •            |              | oue.          |               |              |                 |             |

|                  | 1: Timer 3 e                                                                                                                                                                                |              |              |               |               |              |                 |             |

| Bit 1:           | UNUSED. R                                                                                                                                                                                   |              | Vrite = don' | t care.       |               |              |                 |             |

| Bit 0:           | T3XCLK: Tir                                                                                                                                                                                 |              |              |               |               |              |                 |             |

|                  | This bit sele                                                                                                                                                                               | cts the exte | rnal clock s | ource for Ti  | mer 3. If Tir | mer 3 is in  | 8-bit mode,     | this bit    |

|                  | This bit selects the external clock source for Timer 3. If Timer 3 is in 8-bit mode, this bit selects the external oscillator clock source for both timer bytes. However, the Timer 3 Clock |              |              |               |               |              |                 |             |

|                  | Select bits (T3MH and T3ML in register CKCON) may still be used to select between the                                                                                                       |              |              |               |               |              |                 |             |

|                  | external clos                                                                                                                                                                               |              | -            |               |               |              |                 |             |

|                  | 0: Timer 3 e                                                                                                                                                                                | xternal cloc | k selection  | is the syste  | m clock divi  | ded by 12    |                 |             |

|                  |                                                                                                                                                                                             |              |              |               |               |              |                 |             |

|                  |                                                                                                                                                                                             | xternal cloc |              | is the exterr |               | •            |                 | e external  |

#### SFR Definition 21.13. TMR3CN: Timer 3 Control

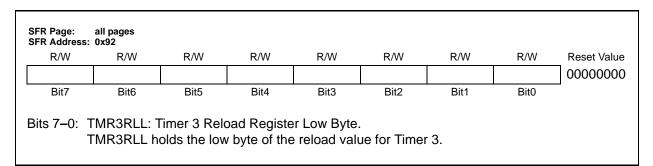

#### SFR Definition 21.14. TMR3RLL: Timer 3 Reload Register Low Byte

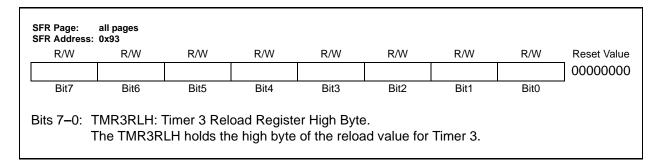

#### SFR Definition 21.15. TMR3RLH: Timer 3 Reload Register High Byte

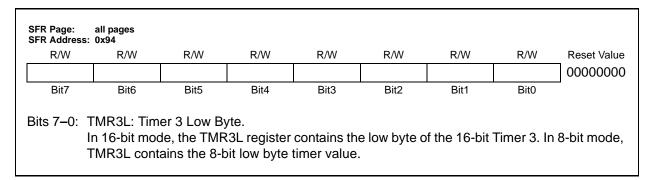

#### SFR Definition 21.16. TMR3L: Timer 3 Low Byte

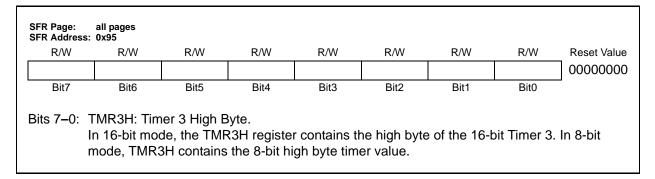

### SFR Definition 21.17. TMR3H Timer 3 High Byte

#### 23.3. C2D Port Pin Requirements

#### Problem

The C2D debugging port pin (shared with P4.6 for C8051F360/3 and P3.0 for C8051F361/2/4/5/6/7/8/9) behaves differently on "REV A" devices than specified in the data sheet.

On "REV A" devices, a C2D port pin that is pulled low by the associated port pin driver will disrupt debugging capability. In order to communicate with the device through the C2 interface, the value in the port latch associated C2D port pin must be '1'.

#### Workaround

To workaround this problem, add a strong pull-up resistor to the C2D port pin to ensure the pin will be high unless explicitly driven low. Furthermore, the port pin should be left in open-drain mode with a '1' in the appropriate port latch (PnMDOUT bit = '0', Pn bit = '1') when not in use. This will allow the debugging software to transfer data via the C2D pin as often as possible.

Rev. 1.1

This behavior has been corrected on "REV B" of this device.

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

http://www.silabs.com