Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                       |

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 50MHz                                                          |

| Connectivity               | SMBus (2-Wire/I²C), SPI, UART/USART                            |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 25                                                             |

| Program Memory Size        | 32KB (32K x 8)                                                 |

| Program Memory Type        | FLASH                                                          |

| EEPROM Size                | -                                                              |

| RAM Size                   | 1K x 8                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                    |

| Data Converters            | A/D 17x10b; D/A 1x10b                                          |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 28-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 28-QFN (5x5)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f367-gm |

| 40.0.0.40.4.0.DOWE Maintanana                              | 4 4 4 |

|------------------------------------------------------------|-------|

| 13.3.2.16.4.2 PSWE Maintenance                             |       |

| 13.3.3.System Clock                                        |       |

| 13.4.Flash Read Timing                                     |       |

| 14. Branch Target Cache                                    |       |

| 14.1.Cache and Prefetch Operation                          |       |

| 14.2.Cache and Prefetch Optimization                       | 146   |

| 15. External Data Memory Interface and On-Chip XRAM        | 152   |

| 15.1.Accessing XRAM                                        |       |

| 15.1.1.16-Bit MOVX Example                                 |       |

| 15.1.2.8-Bit MOVX Example                                  |       |

| 15.2.Configuring the External Memory Interface             | 153   |

| 15.3.Port Configuration                                    | 153   |

| 15.4.Multiplexed and Non-multiplexed Selection             |       |

| 15.4.1.Multiplexed Configuration                           |       |

| 15.4.2.Non-multiplexed Configuration                       |       |

| 15.5.Memory Mode Selection                                 | 158   |

| 15.5.1.Internal XRAM Only                                  |       |

| 15.5.2.Split Mode without Bank Select                      | 158   |

| 15.5.3.Split Mode with Bank Select                         | 158   |

| 15.5.4.External Only                                       | 159   |

| 15.6.Timing                                                | 159   |

| 15.6.1.Non-multiplexed Mode                                | 161   |

| 15.6.2.Multiplexed Mode                                    | 164   |

| 16. Oscillators                                            | 168   |

| 16.1.Programmable Internal High-Frequency (H-F) Oscillator | 168   |

| 16.1.1. Internal Oscillator Suspend Mode                   | 169   |

| 16.2.Programmable Internal Low-Frequency (L-F) Oscillator  | 170   |

| 16.2.1.Calibrating the Internal L-F Oscillator             |       |

| 16.3.External Oscillator Drive Circuit                     |       |

| 16.4.System Clock Selection                                | 172   |

| 16.5.External Crystal Example                              | 175   |

| 16.6.External RC Example                                   | 176   |

| 16.7.External Capacitor Example                            |       |

| 16.8.Phase-Locked Loop (PLL)                               |       |

| 16.8.1.PLL Input Clock and Pre-divider                     | 177   |

| 16.8.2.PLL Multiplication and Output Clock                 |       |

| 16.8.3.Powering on and Initializing the PLL                |       |

| 17. Port Input/Output                                      |       |

| 17.1.Priority Crossbar Decoder                             | 184   |

| 17.2.Port I/O Initialization                               |       |

| 17.3.General Purpose Port I/O                              |       |

| 18. SMBus                                                  |       |

| 18.1.Supporting Documents                                  |       |

| 18.2.SMBus Configuration                                   |       |

5

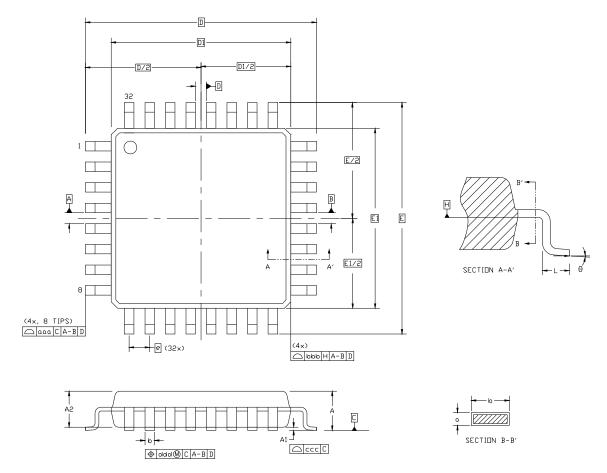

Figure 4.4. LQFP-32 Package Diagram

Table 4.3. LQFP-32 Package Dimensions

| Dimension | Min  | Nom       | Max  |

|-----------|------|-----------|------|

| А         | _    | _         | 1.60 |

| A1        | 0.05 | _         | 0.15 |

| A2        | 1.35 | 1.40      | 1.45 |

| b         | 0.30 | 0.37      | 0.45 |

| С         | 0.09 | _         | 0.20 |

| D         |      | 9.00 BSC. |      |

| D1        |      | 7.00 BSC. |      |

| е         |      | 0.80 BSC. |      |

| Min            | Nom       | Max                                          |  |  |  |

|----------------|-----------|----------------------------------------------|--|--|--|

|                | 9.00 BSC. |                                              |  |  |  |

|                |           |                                              |  |  |  |

| 0.45 0.60 0.75 |           |                                              |  |  |  |

|                | 0.20      |                                              |  |  |  |

|                | 0.20      |                                              |  |  |  |

|                | 0.10      |                                              |  |  |  |

|                | 0.20      |                                              |  |  |  |

| 0°             | 3.5°      | 7°                                           |  |  |  |

|                | 0.45      | 9.00 BSC. 7.00 BSC. 0.45 0.60 0.20 0.10 0.20 |  |  |  |

#### Notes:

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MS-026, variation BBA.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020B specification for Small Body Components.

#### 5.4. **Programmable Window Detector**

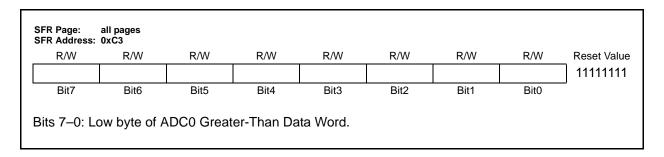

The ADC Programmable Window Detector continuously compares the ADC0 output registers to user-programmed limits, and notifies the system when a desired condition is detected. This is especially effective in an interrupt-driven system, saving code space and CPU bandwidth while delivering faster system response times. The window detector interrupt flag (AD0WINT in register ADC0CN) can also be used in polled mode. The ADC0 Greater-Than (ADC0GTH, ADC0GTL) and Less-Than (ADC0LTH, ADC0LTL) registers hold the comparison values. The window detector flag can be programmed to indicate when measured data is inside or outside of the user-programmed limits, depending on the contents of the ADC0 Less-Than and ADC0 Greater-Than registers.

#### SFR Definition 5.7. ADC0GTH: ADC0 Greater-Than Data High Byte

| R/W  | Reset Valu |

|------|------|------|------|------|------|------|------|------------|

|      |      |      |      |      |      |      |      | 11111111   |

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | _          |

#### SFR Definition 5.8. ADC0GTL: ADC0 Greater-Than Data Low Byte

Table 9.2. Special Function Register (SFR) Memory Map

| ADDRESS | SFR Page | 0(8)   | 1(9)             | 2(A)               | 3(B)               | 4(C)               | 5(D)               | 6(E)                | 7(F)                |

|---------|----------|--------|------------------|--------------------|--------------------|--------------------|--------------------|---------------------|---------------------|

| F8      | 0<br>F   | SPI0CN | PCA0L            | PCA0H              | PCA0CPL0           | PCA0CPH0           | PCA0CPL4           | PCA0CPH4            | VDM0CN              |

| F0      | 0<br>F   | В      | MAC0BL<br>P0MDIN | MAC0BH<br>P1MDIN   | P0MAT<br>P2MDIN    | P0MASK<br>P3MDIN   | PCA0CPL5           | PCA0CPH5            | -<br>EMI0TC         |

| E8      | 0<br>F   | ADC0CN | PCA0CPL1         | PCA0CPH1           | PCA0CPL2           | PCA0CPH2           | PCA0CPL3           | PCA0CPH3            | RSTSRC              |

| E0      | 0<br>F   | ACC    | P1MAT<br>XBR0    | P1MASK<br>XBR1     |                    | IT01CF             | -<br>SFR0CN        | EIE1                | EIE2                |

| D8      | 0<br>F   | PCA0CN | PCA0MD           | PCA0CPM0           | PCA0CPM1           | PCA0CPM2           | PCA0CPM3           | PCA0CPM4            | PCA0CPM5            |

| D0      | 0<br>F   | PSW    | REF0CN           | MAC0ACC0<br>CCH0LC | MAC0ACC1<br>CCH0MA | MAC0ACC2<br>P0SKIP | MAC0ACC3<br>P1SKIP | MAC0OVR<br>P2SKIP   | MAC0CF<br>P3SKIP    |

| C8      | 0<br>F   | TMR2CN | -<br>CCH0TN      | TMR2RLL            | TMR2RLH            | TMR2L              | TMR2H              | -<br>EIP1           | MAC0STA<br>EIP2     |

| C0      | 0<br>F   | SMB0CN | SMB0CF           | SMB0DAT            | ADC0GTL            | ADC0GTH            | ADC0LTL            | ADC0LTH             | -<br>EMI0CF         |

| В8      | 0<br>F   | IP     | IDA0CN           | AMX0N              | AMX0P              | ADC0CF             | ADC0L              | ADC0H               | -<br>OSCICL         |

| В0      | 0<br>F   | P3     | P2MAT<br>PLL0MUL | P2MASK<br>PLL0FLT  | -<br>PLL0CN        | -                  | P4                 | FLSCL<br>OSCXCN     | FLKEY<br>OSCICN     |

| A8      | 0<br>F   | ΙΕ     | -<br>PLL0DIV     | EMI0CN             | -                  | -<br>FLSTAT        | -<br>OSCLCN        | MACORNDL<br>P4MDOUT | MACORNDH<br>P3MDOUT |

| A0      | 0<br>F   | P2     | SPI0CFG          | SPI0CKR            | SPI0DAT            | MAC0AL<br>P0MDOUT  | MAC0AH<br>P1MDOUT  | -<br>P2MDOUT        | SFRPAGE             |

| 98      | 0<br>F   | SCON0  | SBUF0            | CPT1CN             | CPT0CN             | CPT1MD             | CPT0MD             | CPT1MX              | CPT0MX              |

| 90      | 0<br>F   | P1     | TMR3CN           | TMR3RLL            | TMR3RLH            | TMR3L              | TMR3H              | IDA0L               | IDA0H               |

| 88      | 0<br>F   | TCON   | TMOD             | TL0                | TL1                | TH0                | TH1                | CKCON               | PSCTL<br>CLKSEL     |

| 80      | 0<br>F   | P0     | SP               | DPL                | DPH                | -<br>CCH0CN        | SFRNEXT            | SFRLAST             | PCON                |

|         |          | 0(8)   | 1(9)             | 2(A)               | 3(B)               | 4(C)               | 5(D)               | 6(E)                | 7(F)                |

bit-addressable shaded SFRs are accessible on all SFR Pages regardless of the contents of SFRPAGE

### SFR Definition 10.3. EIE1: Extended Interrupt Enable 1

| SFR Page:<br>SFR Addres | all pages                                                                                                                                                                                                                                                        |                                                                                                                                                                                              |                                          |                                         |                           |            |       |             |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------|---------------------------|------------|-------|-------------|

| R/W                     | R/W                                                                                                                                                                                                                                                              | R/W                                                                                                                                                                                          | R/W                                      | R/W                                     | R/W                       | R/W        | R/W   | Reset Value |

| ET3                     | ECP1                                                                                                                                                                                                                                                             | ECP0                                                                                                                                                                                         | EPCA0                                    | EADC0                                   | EWADC0                    | _          | ESMB0 | 00000000    |

| Bit7                    | Bit6                                                                                                                                                                                                                                                             | Bit5                                                                                                                                                                                         | Bit4                                     | Bit3                                    | Bit2                      | Bit1       | Bit0  | _           |

| Bit 7:                  | ET3: Enable<br>This bit sets<br>0: Disable Ti                                                                                                                                                                                                                    | the maskin<br>mer 3 inter                                                                                                                                                                    | g of the Tin<br>rupts.                   |                                         | •                         |            |       |             |

| Bit 6:                  | 1: Enable interrupt requests generated by the TF3L or TF3H flags.  ECP1: Enable Comparator1 (CP1) Interrupt.  This bit sets the masking of the CP1 interrupt.  0: Disable CP1 interrupts.  1: Enable interrupt requests generated by the CP1RIF or CP1FIF flags. |                                                                                                                                                                                              |                                          |                                         |                           |            |       |             |

| Bit 5:                  | ECP0: Enab<br>This bit sets<br>0: Disable C                                                                                                                                                                                                                      | ECP0: Enable Comparator (CP0) Interrupt.  This bit sets the masking of the CP0 interrupt.  0: Disable CP0 interrupts.  1: Enable interrupt requests generated by the CP0RIF or CP0FIF flags. |                                          |                                         |                           |            |       |             |

| Bit 4:                  |                                                                                                                                                                                                                                                                  | ible Prograi<br>the maskin<br>I PCA0 inte                                                                                                                                                    | mmable Co<br>g of the PC<br>errupts.     | unter Array<br>A0 interrup              | (PCA0) Inter<br>ts.       |            | , c.  |             |

| Bit 3:                  | EADC0: Ena<br>This bit sets<br>0: Disable A                                                                                                                                                                                                                      | able ADC0 (<br>the maskin<br>DC0 Conve                                                                                                                                                       | Conversion<br>g of the AD<br>ersion Comp | Complete CO Converblete interru         | nterrupt.<br>sion Complet | -          | t.    |             |

| Bit 2:                  | EWADC0: E<br>This bit sets<br>0: Disable A                                                                                                                                                                                                                       | nable ADC<br>the maskin<br>DC0 Windo                                                                                                                                                         | 0 Window 0<br>g of the AD<br>w Compari   | Comparison<br>C0 Windov<br>son interrup | Interrupt.  / Comparisor  | interrupt. |       |             |

| Bit 1:<br>Bit 0:        | UNUSED. R<br>ESMB0: Ena<br>This bit sets<br>0: Disable al<br>1: Enable int                                                                                                                                                                                       | able SMBus<br>the maskin<br>I SMB0 inte                                                                                                                                                      | s (SMB0) In<br>g of the SM<br>errupts.   | terrupt.<br>IB0 interrup                |                           | _          |       |             |

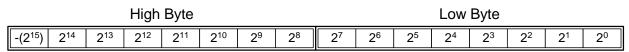

#### 11.2. Integer and Fractional Math

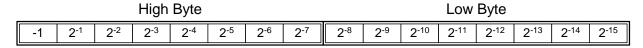

MAC0 is capable of interpreting the 16-bit inputs stored in MAC0A and MAC0B as signed integers or as signed fractional numbers. When the MAC0FM bit (MAC0CF.1) is cleared to '0', the inputs are treated as 16-bit, 2's complement, integer values. After the operation, the accumulator will contain a 40-bit, 2's complement, integer value. Figure 11.2 shows how integers are stored in the SFRs.

#### MACOA and MACOB Bit Weighting

MAC0 Accumulator Bit Weighting

Figure 11.2. Integer Mode Data Representation

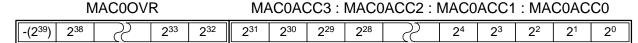

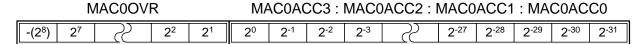

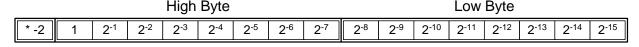

When the MACOFM bit is set to '1', the inputs are treated at 16-bit, 2's complement, fractional values. The decimal point is located between bits 15 and 14 of the data word. After the operation, the accumulator will contain a 40-bit, 2's complement, fractional value, with the decimal point located between bits 31 and 30. Figure 11.3 shows how fractional numbers are stored in the SFRs.

MAC0A, and MAC0B Bit Weighting

#### MAC0 Accumulator Bit Weighting

#### MACORND Bit Weighting

<sup>\*</sup> The MACORND register contains the 16 LSBs of a two's complement number. The MACON Flag can be used to determine the sign of the MACORND register.

Figure 11.3. Fractional Mode Data Representation

#### SFR Definition 11.2. MACOSTA: MACO Status

SFR Page: SFR Address: 0xCF R R R R R/W R/W R/W R/W Reset Value MAC0HO MAC0Z MAC0SO MAC0N 00000100 Bit Bit3 Bit2 Bit7 Bit6 Bit5 Bit4 Bit1 Bit0 Addressable

Bits 7–4: UNUSED: Read = 0000b, Write = don't care.

Bit 3: MAC0HO: Hard Overflow Flag.

This bit is set to '1' whenever an overflow out of the MACOOVR register occurs during a MAC operation (i.e. when MACOOVR changes from 0x7F to 0x80 or from 0x80 to 0x7F). The hard overflow flag must be cleared in software by directly writing it to '0', or by resetting the MAC logic using the MACOCA bit in register MACOCF.

Bit 2: MAC0Z: Zero Flag.

This bit is set to '1' if a MACO operation results in an Accumulator value of zero. If the result is non-zero, this bit will be cleared to '0'.

Bit 1: MAC0SO: Soft Overflow Flag.

This bit is set to '1' when a MAC operation causes an overflow into the sign bit (bit 31) of the MAC0 Accumulator. If the overflow condition is corrected after a subsequent MAC operation, this bit is cleared to '0'.

Bit 0: MACON: Negative Flag.

If the MAC Accumulator result is negative, this bit will be set to '1'. If the result is positive or zero, this flag will be cleared to '0'.

zero, triis hag will be cleared to 0.

Note: The contents of this register should not be changed by software during the first two MAC0 pipeline

stages.

#### SFR Definition 11.3. MACOAH: MACO A High Byte

SFR Page: SFR Address: 0xA5 R R R R R R R R Reset Value 00000000 Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

Bits 7-0: High Byte (bits 15-8) of MAC0 A Register.

#### 12.1. Power-On Reset

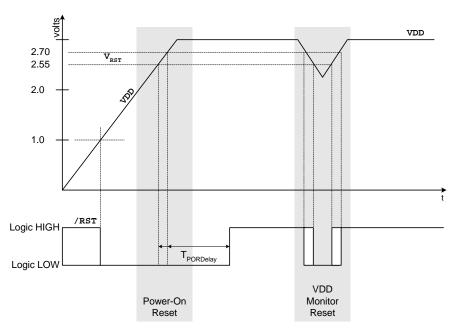

During power-up, the device is held in a reset state and the  $\overline{RST}$  pin is driven low until  $V_{DD}$  settles above  $V_{RST}$ . A delay occurs before the device is released from reset; the delay decreases as the  $V_{DD}$  ramp time increases ( $V_{DD}$  ramp time is defined as how fast  $V_{DD}$  ramps from 0 V to  $V_{RST}$ ). Figure 12.2. plots the power-on and  $V_{DD}$  Monitor reset timing. For ramp times less than 1 ms, the power-on reset delay ( $T_{PORDe-lav}$ ) is typically less than 0.3 ms.

**Note:** The maximum  $V_{DD}$  ramp time is 1 ms; slower ramp times may cause the device to be released from reset before  $V_{DD}$  reaches the  $V_{RST}$  level.

On exit from a power-on reset, the PORSF flag (RSTSRC.1) is set by hardware to logic '1'. When PORSF is set, all of the other reset flags in the RSTSRC Register are indeterminate (PORSF is cleared by all other resets). Since all resets cause program execution to begin at the same location (0x0000) software can read the PORSF flag to determine if a power-up was the cause of reset. The content of internal data memory should be assumed to be undefined after a power-on reset. The V<sub>DD</sub> Monitor is enabled following a power-on reset.

Figure 12.2. Power-On and V<sub>DD</sub> Monitor Reset Timing

SILICON LABS

#### 12.2. Power-Fail Reset/V<sub>DD</sub> Monitor

When a power-down transition or power irregularity causes  $V_{DD}$  to drop below  $V_{RST}$ , the power supply monitor will drive the  $\overline{RST}$  pin low and hold the CIP-51 in a reset state (see Figure 12.2). When  $V_{DD}$  returns to a level above  $V_{RST}$ , the CIP-51 will be released from the reset state. Note that even though internal data memory contents are not altered by the power-fail reset, it is impossible to determine if  $V_{DD}$  dropped below the level required for data retention. If the PORSF flag reads '1', the data may no longer be valid. The  $V_{DD}$  Monitor is enabled after power-on resets; however its defined state (enabled/disabled) is not altered by any other reset source. For example, if the  $V_{DD}$  Monitor is disabled and a software reset is performed, the  $V_{DD}$  Monitor will still be disabled after the reset. To protect the integrity of Flash contents, the VDD Monitor must be enabled and selected as a reset source if software contains routines which erase or write Flash memory. If the VDD Monitor is not enabled, any erase or write performed on Flash memory will cause a Flash Error device reset.

The  $V_{DD}$  Monitor must be enabled before it is selected as a reset source. Selecting the  $V_{DD}$  Monitor as a reset source before it is enabled and stabilized may cause a system reset. The procedure for configuring the  $V_{DD}$  Monitor as a reset source is shown below:

- Step 1. Enable the  $V_{DD}$  Monitor (VDMEN bit in VDM0CN = '1').

- Step 2. Wait for the VDD Monitor to stabilize (approximately 5 µs).

Note: This delay should be omitted if software contains routines which erase or write Flash memory.

- Step 3. Select the  $V_{DD}$  Monitor as a reset source (PORSF bit in RSTSRC = '1').

See Table 12.1 for complete electrical characteristics of the V<sub>DD</sub> Monitor.

Note: Software should take care not to inadvertently disable the VDD Monitor as a reset source when writing to RSTSRC to enable other reset sources or to trigger a software reset. All writes to RSTSRC should explicitly set PORSF to '1' to keep the VDD Monitor enabled as a reset source.

erases will be disabled until the next system reset. Flash writes and erases will also be disabled if a Flash write or erase is attempted before the key codes have been written properly. The Flash lock resets after each write or erase; the key codes must be written again before a following Flash operation can be performed. The FLKEY register is detailed in SFR Definition 13.2.

#### 13.1.2. Erasing Flash Pages From Software

The Flash memory can be programmed by software using the MOVX write instruction with the address and data byte to be programmed provided as normal operands. Before writing to Flash memory using MOVX, Flash write operations must be enabled by: (1) the PSWE and PSEE bits must be set to '1' (this directs the MOVX writes to target Flash memory); and (2) Writing the Flash key codes in sequence to the Flash Lock register (FLKEY). The PSWE bit remains set until cleared by software.

A write to Flash memory can clear bits to logic '0' but cannot set them; only an erase operation can set bits to logic '1' in Flash. A byte location to be programmed should be erased before a new value is written. The Flash memory is organized in 1024-byte pages. The erase operation applies to an entire page (setting all bytes in the page to 0xFF). To erase an entire 1024-byte page, perform the following steps:

- Step 1. Disable interrupts (recommended).

- Step 2. Write the first key code to FLKEY: 0xA5.

- Step 3. Write the second key code to FLKEY: 0xF1.

- Step 4. Set PSEE (PSCTL.1) to enable Flash erases.

- Step 5. Set PSWE (PSCTL.0) to redirect MOVX commands to write to Flash.

- Step 6. Use the MOVX instruction to write a data byte to any location within the page to be erased.

- Step 7. Clear PSEE to disable Flash erases.

- Step 8. Clear the PSWE bit to redirect MOVX commands to the XRAM data space.

- Step 9. Re-enable interrupts.

#### 13.1.3. Writing Flash Memory From Software

Bytes in Flash memory can be written one byte at a time, or in small blocks. The CHBLKW bit in register CCH0CN (SFR Definition 14.1) controls whether a single byte or a block of bytes is written to Flash during a write operation. When CHBLKW is cleared to '0', the Flash will be written one byte at a time. When CHBLKW is set to '1', the Flash will be written in blocks of four bytes for addresses in code space. Block writes are performed in the same amount of time as single byte writes, which can save time when storing large amounts of data to Flash memory.

For single-byte writes to Flash, bytes are written individually, and the Flash write is performed after each MOVX write instruction. The recommended procedure for writing Flash in single bytes is as follows:

- Step 1. Disable interrupts.

- Step 2. Clear CHBLKW (register CCH0CN) to select single-byte write mode.

- Step 3. Write the first key code to FLKEY: 0xA5.

- Step 4. Write the second key code to FLKEY: 0xF1.

- Step 5. Set PSWE (register PSCTL) to redirect MOVX commands to write to Flash.

- Step 6. Clear the PSEE bit (register PSCTL).

- Step 7. Use the MOVX instruction to write a data byte to the desired location (repeat as necessary).

- Step 8. Clear the PSWE bit to redirect MOVX commands to the XRAM data space.

- Step 9. Re-enable interrupts.

#### 13.2.1. Summary of Flash Security Options

The level of Flash security depends on the Flash access method. The three Flash access methods that can be restricted are reads, writes, and erases from the C2 debug interface, user firmware executing on unlocked pages, and user firmware executing on locked pages. Table 13.1 summarizes the Flash security features of the C8051F36x devices.

Table 13.1. Flash Security Summary

| Action                                                                     | C2 Debug      | User Firmware e  | xecuting from: |

|----------------------------------------------------------------------------|---------------|------------------|----------------|

|                                                                            | Interface     | an unlocked page | a locked page  |

| Read, Write or Erase unlocked pages (except page with Lock Byte)           | Permitted     | Permitted        | Permitted      |

| Read, Write or Erase locked pages (except page with Lock Byte)             | Not Permitted | FEDR             | Permitted      |

| Read or Write page containing Lock Byte (if no pages are locked)           | Permitted     | Permitted        | Permitted      |

| Read or Write page containing Lock Byte (if any page is locked)            | Not Permitted | FEDR             | Permitted      |

| Read contents of Lock Byte (if no pages are locked)                        | Permitted     | Permitted        | Permitted      |

| Read contents of Lock Byte (if any page is locked)                         | Not Permitted | FEDR             | Permitted      |

| Erase page containing Lock Byte (if no pages are locked)                   | Permitted     | FEDR             | FEDR           |

| Erase page containing Lock Byte - Unlock all pages (if any page is locked) | Only C2DE     | FEDR             | FEDR           |

| Lock additional pages<br>(change '1's to '0's in the Lock Byte)            | Not Permitted | FEDR             | FEDR           |

| Unlock individual pages (change '0's to '1's in the Lock Byte)             | Not Permitted | FEDR             | FEDR           |

| Read, Write or Erase Reserved Area                                         | Not Permitted | FEDR             | FEDR           |

C2DE - C2 Device Erase (Erases all Flash pages including the page containing the Lock Byte)

FEDR - Not permitted; Causes Flash Error Device Reset (FERROR bit in RSTSRC is '1' after reset)

- All prohibited operations that are performed via the C2 interface are ignored (do not cause device reset).

- Locking any Flash page also locks the page containing the Lock Byte.

- Once written to, the Lock Byte cannot be modified except by performing a C2 Device Erase.

- If user code writes to the Lock Byte, the Lock does not take effect until the next device reset.

### 15. External Data Memory Interface and On-Chip XRAM

For C8051F36x devices, 1k Bytes of RAM are included on-chip and mapped into the external data memory space (XRAM). Additionally, an External Memory Interface (EMIF) is available on the C8051F360/3 devices, which can be used to access off-chip data memories and memory-mapped devices connected to the GPIO ports. The external memory space may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using the MOVX indirect addressing mode using R0 or R1. If the MOVX instruction is used with an 8-bit address operand (such as @R1), then the high byte of the 16-bit address is provided by the External Memory Interface Control Register (EMIOCN, shown in SFR Definition 15.1). Note: the MOVX instruction can also be used for writing to the FLASH memory. See Section "13. Flash Memory" on page 135 for details. The MOVX instruction accesses XRAM by default.

#### 15.1. Accessing XRAM

The XRAM memory space is accessed using the MOVX instruction. The MOVX instruction has two forms, both of which use an indirect addressing method. The first method uses the Data Pointer, DPTR, a 16-bit register which contains the effective address of the XRAM location to be read from or written to. The second method uses R0 or R1 in combination with the EMI0CN register to generate the effective XRAM address. Examples of both of these methods are given below.

#### **15.1.1. 16-Bit MOVX Example**

The 16-bit form of the MOVX instruction accesses the memory location pointed to by the contents of the DPTR register. The following series of instructions reads the value of the byte at address 0x1234 into the accumulator A:

```

MOV DPTR, \#1234h ; load DPTR with 16-bit address to read (0x1234) MOVX A, @DPTR ; load contents of 0x1234 into accumulator A

```

The above example uses the 16-bit immediate MOV instruction to set the contents of DPTR. Alternately, the DPTR can be accessed through the SFR registers DPH, which contains the upper 8-bits of DPTR, and DPL, which contains the lower 8-bits of DPTR.

#### 15.1.2. 8-Bit MOVX Example

The 8-bit form of the MOVX instruction uses the contents of the EMI0CN SFR to determine the upper 8-bits of the effective address to be accessed and the contents of R0 or R1 to determine the lower 8-bits of the effective address to be accessed. The following series of instructions read the contents of the byte at address 0x1234 into the accumulator A.

```

MOV EMIOCN, #12h ; load high byte of address into EMIOCN MOV R0, #34h ; load low byte of address into R0 (or R1) MOVX a, @R0 ; load contents of 0x1234 into accumulator A

```

#### 15.2. Configuring the External Memory Interface

Configuring the External Memory Interface consists of five steps:

- 1. Configure the Output Modes of the associated port pins as either push-pull or open-drain (push-pull is most common), and skip the associated pins in the crossbar.

- 2. Configure Port latches to "park" the EMIF pins in a dormant state (usually by setting them to logic '1').

- 3. Select Multiplexed mode or Non-multiplexed mode.

- 4. Select the memory mode (on-chip only, split mode without bank select, split mode with bank select, or off-chip only).

- 5. Set up timing to interface with off-chip memory or peripherals.

Each of these five steps is explained in detail in the following sections. The Port selection, Multiplexed mode selection, and Mode bits are located in the EMIOCF register shown in SFR Definition 15.2.

#### 15.3. Port Configuration

The External Memory Interface appears on Ports 1, 2 (non-multiplexed mode only), 3, and 4 when it is used for off-chip memory access. When the EMIF is used in multiplexed mode, the Crossbar should be configured to skip over the ALE control line (P0.0) using the P0SKIP register. The other control lines, /RD (P4.4) and /WR (P4.5), are not available on the Crossbar and do not need to be skipped. For more information about configuring the Crossbar, see Section "17.3. General Purpose Port I/O" on page 189. The EMIF pinout is shown in Table 15.1 on page 154.

The External Memory Interface claims the associated Port pins for memory operations ONLY during the execution of an off-chip MOVX instruction. Once the MOVX instruction has completed, control of the Port pins reverts to the Port latches or to the Crossbar settings for those pins. See Section "17. Port Input/Output" on page 182 for more information about the Crossbar and Port operation and configuration. The Port latches should be explicitly configured to 'park' the External Memory Interface pins in a dormant state, most commonly by setting them to a logic '1'.

During the execution of the MOVX instruction, the External Memory Interface will explicitly disable the drivers on all Port pins that are acting as Inputs (Data[7:0] during a READ operation, for example). The Output mode of the Port pins (whether the pin is configured as Open-Drain or Push-Pull) is unaffected by the External Memory Interface operation, and remains controlled by the PnMDOUT registers. In most cases, the output modes of all EMIF pins should be configured for push-pull mode.

SILICON LABS

#### 16.1.1. Internal Oscillator Suspend Mode

When software writes a logic '1' to SUSPEND (OSCICN.5), the internal oscillator is suspended. If the system clock is derived from the internal oscillator, the input clock to the peripheral or CIP-51 will be stopped until one of the following events occur:

- Port 0 Match Event.

- Port 1 Match Event.

- Port 2 Match Event.

- · Comparator 0 enabled and output is logic '0'.

- Comparator 1 enabled and output is logic '0'.

When one of the internal oscillator awakening events occur, the internal oscillator, CIP-51, and affected peripherals resume normal operation, regardless of whether the event also causes an interrupt. The CPU resumes execution at the instruction following the write to SUSPEND.

**Note:** Before entering SUSPEND mode, SYSCLK should be switched to run off of the internal oscillator and not the PLL. When the CPU wakes due to the awakening event, the PLL must be reinitialized before switching back to it as the SYSCLK source.

#### SFR Definition 16.1. OSCICL: Internal Oscillator Calibration.

| SFR Page:<br>SFR Address: | F<br>0xBF |      |      |      |      |      |      |             |

|---------------------------|-----------|------|------|------|------|------|------|-------------|

| R/W                       | R/W       | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value |

|                           |           |      |      |      |      |      |      | Variable    |

| Bit7                      | Bit6      | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | _           |

Bits 7-0: OSCICL: Internal Oscillator Calibration Register.

This register calibrates the internal oscillator period. The reset value for OSCICL defines the internal oscillator base frequency. The reset value is factory calibrated to generate an internal oscillator frequency of 24.5 MHz.

#### SFR Definition 17.21. P3: Port3

| SFR Page:<br>SFR Addre | all pages<br>ss: 0xB0 | (bit addr | essable) |      |      |      |      |             |

|------------------------|-----------------------|-----------|----------|------|------|------|------|-------------|

| R/W                    | R/W                   | R/W       | R/W      | R/W  | R/W  | R/W  | R/W  | Reset Value |

| P3.7                   | P3.6                  | P3.5      | P3.4     | P3.3 | P3.2 | P3.1 | P3.0 | 11111111    |

| Bit7                   | Bit6                  | Bit5      | Bit4     | Bit3 | Bit2 | Bit1 | Bit0 | <u> </u>    |

Bits 7-0: P3.[7:0]

Write - Output appears on I/O pins per Crossbar Registers.

0: Logic Low Output.

1: Logic High Output (high impedance if corresponding P3MDOUT.n bit = 0).

Read - Always reads '0' if selected as analog input in register P3MDIN. Directly reads Port

pin when configured as digital input.

0: P3.n pin is logic low.1: P3.n pin is logic high.

#### SFR Definition 17.22. P3MDIN: Port3 Input Mode

| SFR F | Page:<br>Address: | F<br>0xF4 |      |      |      |      |      |      |             |

|-------|-------------------|-----------|------|------|------|------|------|------|-------------|

| F     | R/W               | R/W       | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value |

|       |                   |           |      |      |      |      |      |      | 11111111    |

|       | 3it7              | Bit6      | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | <del></del> |

Bits 7-0: Analog Input Configuration Bits for P3.7-P3.0 (respectively).

Port pins configured as analog inputs have their weak pullup, digital driver, and digital receiver disabled.

0: Corresponding P3.n pin is configured as an analog input.

1: Corresponding P3.n pin is not configured as an analog input.

#### 18.5.4. Slave Transmitter Mode

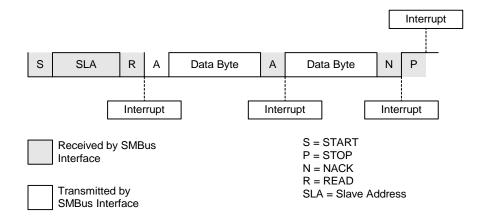

Serial data is transmitted on SDA and the clock is received on SCL. When slave events are enabled (INH = 0), the interface enters Slave Receiver Mode (to receive the slave address) when a START followed by a slave address and direction bit (READ in this case) is received. Upon entering Slave Transmitter Mode, an interrupt is generated and the ACKRQ bit is set. Software responds to the received slave address with an ACK, or ignores the received slave address with a NACK. If the received slave address is ignored, slave interrupts will be inhibited until a START is detected. If the received slave address is acknowledged, data should be written to SMB0DAT to be transmitted. The interface enters Slave Transmitter Mode, and transmits one or more bytes of data. After each byte is transmitted, the master sends an acknowledge bit; if the acknowledge bit is an ACK, SMB0DAT should be written with the next data byte. If the acknowledge bit is a NACK, SMB0DAT should not be written to before SI is cleared (Note: an error condition may be generated if SMB0DAT is written following a received NACK while in Slave Transmitter Mode). The interface exits Slave Transmitter Mode after receiving a STOP. Note that the interface will switch to Slave Receiver Mode if SMB0DAT is not written following a Slave Transmitter interrupt. Figure 18.8 shows a typical Slave Transmitter sequence. Two transmitted data bytes are shown, though any number of bytes may be transmitted. Notice that the 'data byte transferred' interrupts occur **after** the ACK cycle in this mode.

Figure 18.8. Typical Slave Transmitter Sequence

#### 19.2. Operational Modes

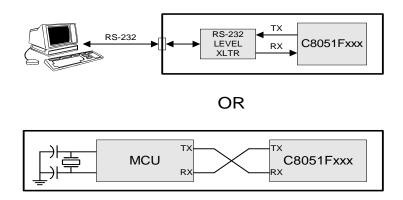

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown below.

Figure 19.3. UART Interconnect Diagram

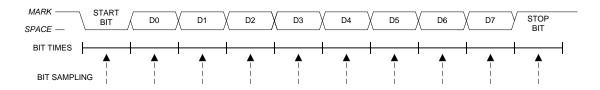

#### 19.2.1. 8-Bit UART

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic '1'. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic '0', and if MCE0 is logic '1', the stop bit must be logic '1'. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 19.4. 8-Bit UART Timing Diagram

#### 21.1. Timer 0 and Timer 1

Each timer is implemented as a 16-bit register accessed as two separate bytes: a low byte (TL0 or TL1) and a high byte (TH0 or TH1). The Counter/Timer Control register (TCON) is used to enable Timer 0 and Timer 1 as well as indicate status. Timer 0 interrupts can be enabled by setting the ET0 bit in the IE register (Section "10.4. Interrupt Register Descriptions" on page 109); Timer 1 interrupts can be enabled by setting the ET1 bit in the IE register (Section 10.4). Both counter/timers operate in one of four primary modes selected by setting the Mode Select bits T1M1–T0M0 in the Counter/Timer Mode register (TMOD). Each timer can be configured independently. Each operating mode is described below.

#### 21.1.1. Mode 0: 13-bit Counter/Timer

Timer 0 and Timer 1 operate as 13-bit counter/timers in Mode 0. The following describes the configuration and operation of Timer 0. However, both timers operate identically, and Timer 1 is configured in the same manner as described for Timer 0.

The TH0 register holds the eight MSBs of the 13-bit counter/timer. TL0 holds the five LSBs in bit positions TL0.4–TL0.0. The three upper bits of TL0 (TL0.7–TL0.5) are indeterminate and should be masked out or ignored when reading. As the 13-bit timer register increments and overflows from 0x1FFF (all ones) to 0x0000, the timer overflow flag TF0 (TCON.5) is set and an interrupt will occur if Timer 0 interrupts are enabled.

The C/T0 bit (TMOD.2) selects the counter/timer's clock source. When C/T0 is set to logic '1', high-to-low transitions at the selected Timer 0 input pin (T0) increment the timer register (Refer to Section "17.1. Priority Crossbar Decoder" on page 184 for information on selecting and configuring external I/O pins). Clearing C/T selects the clock defined by the T0M bit (CKCON.3). When T0M is set, Timer 0 is clocked by the system clock. When T0M is cleared, Timer 0 is clocked by the source selected by the Clock Scale bits in CKCON (see SFR Definition 21.3).

Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic '0' or the input signal /INT0 is active as defined by bit IN0PL in register IT01CF (see SFR Definition 10.7). Setting GATE0 to '1' allows the timer to be controlled by the external input signal /INT0 (see Section "10.4. Interrupt Register Descriptions" on page 109), facilitating pulse width measurements

| TR0             | GATE0 | /INT0 | Counter/Timer |

|-----------------|-------|-------|---------------|

| 0               | X     | Х     | Disabled      |

| 1               | 0     | Х     | Enabled       |

| 1               | 1     | 0     | Disabled      |

| 1               | 1     | 1     | Enabled       |

| Note: X = Don't | Care  |       |               |

Setting TR0 does not force the timer to reset. The timer registers should be loaded with the desired initial value before the timer is enabled.

TL1 and TH1 form the 13-bit register for Timer 1 in the same manner as described above for TL0 and TH0. Timer 1 is configured and controlled using the relevant TCON and TMOD bits just as with Timer 0. The input signal /INT1 is used with Timer 1; the /INT1 polarity is defined by bit IN1PL in register IT01CF (see SFR Definition 10.7).

SILICON LABS

Figure 23.2. Device Package - LQFP 32

Figure 23.3. Device Package - QFN 28

#### 23.2. CPL C Instruction Behavior

#### **Problem**

On Revision A and Revision B devices, a bug in the CPU causes an execution failure for the "CPL C" (Complement Carry bit) instruction under a narrow set of conditions involving an instruction order dependency. The probability of failure is increased at higher temperatures, lower power supply voltage, and higher system clock frequencies.

The failure mode is as follows: if the Carry bit contains a 1 prior to the execution phase of the "CPL C" opcode, the Carry bit will remain a 1 after the execution phase of the opcode has completed. If the Carry

SILICON LABS

#### 23.3. C2D Port Pin Requirements

#### **Problem**

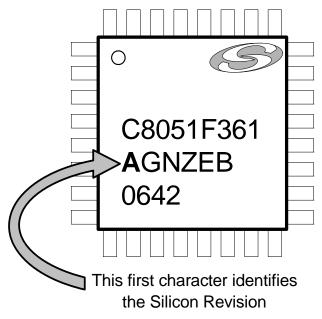

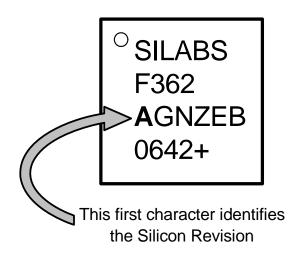

The C2D debugging port pin (shared with P4.6 for C8051F360/3 and P3.0 for C8051F361/2/4/5/6/7/8/9) behaves differently on "REV A" devices than specified in the data sheet.

On "REV A" devices, a C2D port pin that is pulled low by the associated port pin driver will disrupt debugging capability. In order to communicate with the device through the C2 interface, the value in the port latch associated C2D port pin must be '1'.

#### Workaround

To workaround this problem, add a strong pull-up resistor to the C2D port pin to ensure the pin will be high unless explicitly driven low. Furthermore, the port pin should be left in open-drain mode with a '1' in the appropriate port latch (PnMDOUT bit = '0', Pn bit = '1') when not in use. This will allow the debugging software to transfer data via the C2D pin as often as possible.

This behavior has been corrected on "REV B" of this device.