Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                        |

|----------------------------|-----------------------------------------------------------------|

| Core Processor             | 8051                                                            |

| Core Size                  | 8-Bit                                                           |

| Speed                      | 50MHz                                                           |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART                |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                      |

| Number of I/O              | 25                                                              |

| Program Memory Size        | 16KB (16K x 8)                                                  |

| Program Memory Type        | FLASH                                                           |

| EEPROM Size                | -                                                               |

| RAM Size                   | 1K x 8                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                     |

| Data Converters            | A/D 17x10b; D/A 1x10b                                           |

| Oscillator Type            | Internal                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                               |

| Mounting Type              | Surface Mount                                                   |

| Package / Case             | 28-VFQFN Exposed Pad                                            |

| Supplier Device Package    | 28-QFN (5x5)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f369-gmr |

|                            |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|    | 18.3.SMBus Operation                                                                                                              | 201                                                                                                                                                       |

|----|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | 18.3.1.Arbitration                                                                                                                |                                                                                                                                                           |

|    | 18.3.2.Clock Low Extension                                                                                                        |                                                                                                                                                           |

|    | 18.3.3.SCL Low Timeout                                                                                                            |                                                                                                                                                           |

|    | 18.3.4.SCL High (SMBus Free) Timeout                                                                                              |                                                                                                                                                           |

|    | 18.4.Using the SMBus                                                                                                              |                                                                                                                                                           |

|    | 18.4.1.SMBus Configuration Register                                                                                               |                                                                                                                                                           |

|    | 18.4.2.SMB0CN Control Register                                                                                                    |                                                                                                                                                           |

|    | 18.4.3.Data Register                                                                                                              |                                                                                                                                                           |

|    | 18.5.SMBus Transfer Modes                                                                                                         | 210                                                                                                                                                       |

|    | 18.5.1.Master Transmitter Mode                                                                                                    |                                                                                                                                                           |

|    | 18.5.2.Master Receiver Mode                                                                                                       |                                                                                                                                                           |

|    | 18.5.3.Slave Receiver Mode                                                                                                        |                                                                                                                                                           |

|    | 18.5.4.Slave Transmitter Mode                                                                                                     |                                                                                                                                                           |

|    | 18.6.SMBus Status Decoding                                                                                                        |                                                                                                                                                           |

| 10 | .UART0                                                                                                                            |                                                                                                                                                           |

| 19 | 19.1.Enhanced Baud Rate Generation                                                                                                |                                                                                                                                                           |

|    |                                                                                                                                   |                                                                                                                                                           |

|    | 19.2.Operational Modes<br>19.2.1.8-Bit UART                                                                                       | 219                                                                                                                                                       |

|    | 19.2.1.8-Bit UART                                                                                                                 |                                                                                                                                                           |

|    | 19.3.Multiprocessor Communications                                                                                                |                                                                                                                                                           |

| 20 |                                                                                                                                   |                                                                                                                                                           |

| 20 | . Enhanced Serial Peripheral Interface (SPI0)                                                                                     | ZJZ                                                                                                                                                       |

|    |                                                                                                                                   |                                                                                                                                                           |

|    | 20.1.Signal Descriptions                                                                                                          | 233                                                                                                                                                       |

|    | 20.1.Signal Descriptions<br>20.1.1.Master Out, Slave In (MOSI)                                                                    | 233<br>233                                                                                                                                                |

|    | 20.1.Signal Descriptions<br>20.1.1.Master Out, Slave In (MOSI)<br>20.1.2.Master In, Slave Out (MISO)                              | 233<br>233<br>233                                                                                                                                         |

|    | 20.1.Signal Descriptions<br>20.1.1.Master Out, Slave In (MOSI)<br>20.1.2.Master In, Slave Out (MISO)<br>20.1.3.Serial Clock (SCK) | 233<br>233<br>233<br>233                                                                                                                                  |

|    | 20.1.Signal Descriptions                                                                                                          | 233<br>233<br>233<br>233<br>233                                                                                                                           |

|    | 20.1.Signal Descriptions                                                                                                          | 233<br>233<br>233<br>233<br>233<br>233                                                                                                                    |

|    | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>233<br>236                                                                                                      |

|    | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236                                                                                                      |

|    | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236                                                                                               |

| 24 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | <ul> <li>233</li> <li>233</li> <li>233</li> <li>233</li> <li>233</li> <li>236</li> <li>236</li> <li>236</li> <li>236</li> <li>239</li> <li>245</li> </ul> |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236                                                                                        |

| 21 | <ul> <li>20.1.Signal Descriptions</li></ul>                                                                                       | 233<br>233<br>233<br>233<br>233<br>236<br>236<br>236<br>236<br>236                                                                                        |

# List of Tables

| 1.  | System Overview                                                           |      |

|-----|---------------------------------------------------------------------------|------|

|     | Table 1.1. Product Selection Guide                                        | 19   |

| 2.  | Absolute Maximum Ratings                                                  |      |

|     | Table 2.1. Absolute Maximum Ratings                                       | 32   |

| 3.  | Global Electrical Characteristics                                         |      |

|     | Table 3.1. Global Electrical Characteristics                              | 33   |

|     | Table 3.2. Index to Electrical Characteristics Tables                     | 35   |

| 4.  | Pinout and Package Definitions                                            |      |

|     | Table 4.1. Pin Definitions for the C8051F36x                              | 36   |

|     | Table 4.2. TQFP-48 Package Dimensions                                     | 40   |

|     | Table 4.3. LQFP-32 Package Dimensions                                     | 42   |

|     | Table 4.4. QFN-28 Package Dimensions                                      | . 44 |

| 5.  | 10-Bit ADC (ADC0, C8051F360/1/2/6/7/8/9)                                  |      |

|     | Table 5.1. ADC0 Electrical Characteristics                                | 62   |

| 6.  | 10-Bit Current Mode DAC (IDA0, C8051F360/1/2/6/7/8/9)                     |      |

|     | Table 6.1. IDAC Electrical Characteristics                                | 66   |

| 7.  | Voltage Reference (C8051F360/1/2/6/7/8/9)                                 |      |

|     | Table 7.1. Voltage Reference Electrical Characteristics                   | 69   |

| 8.  | Comparators                                                               |      |

|     | Table 8.1. Comparator Electrical Characteristics                          | 79   |

| 9.  | CIP-51 Microcontroller                                                    |      |

|     | Table 9.1. CIP-51 Instruction Set Summary                                 | 82   |

|     | Table 9.2. Special Function Register (SFR) Memory Map                     | 96   |

|     | Table 9.3. Special Function Registers                                     | 97   |

| 10  | . Interrupt Handler                                                       |      |

|     | Table 10.1. Interrupt Summary                                             | 108  |

| 11. | . Multiply And Accumulate (MAC0)                                          |      |

|     | Table 11.1. MAC0 Rounding (MAC0SAT = 0)                                   | 120  |

| 12  | .Reset Sources                                                            |      |

|     | Table 12.1. Reset Electrical Characteristics                              | 134  |

| 13  | . Flash Memory                                                            |      |

|     | Table 13.1. Flash Security Summary                                        |      |

|     | Table 13.2. Flash Electrical Characteristics                              | 144  |

|     | Branch Target Cache                                                       |      |

| 15  | External Data Memory Interface and On-Chip XRAM                           |      |

|     | Table 15.1. EMIF Pinout (C8051F360/3)                                     |      |

|     | Table 15.2. AC Parameters for External Memory Interface                   | 167  |

| 16  | Oscillators                                                               |      |

|     | Table 16.1. Internal High Frequency Oscillator Electrical Characteristics |      |

|     | Table 16.2. Internal Low Frequency Oscillator Electrical Characteristics  |      |

|     | Table 16.3. PLL Frequency Characteristics                                 |      |

|     | Table 16.4. PLL Lock Timing Characteristics                               | 181  |

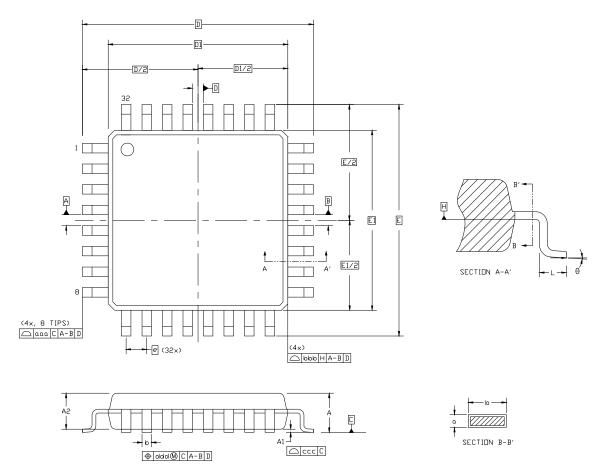

Figure 4.4. LQFP-32 Package Diagram

| Dimension | Min       | Nom       | Max  | Dimension | Min       | Nom        | Max  |  |

|-----------|-----------|-----------|------|-----------|-----------|------------|------|--|

| А         |           | —         | 1.60 | E         | 9.00 BSC. |            |      |  |

| A1        | 0.05      | _         | 0.15 | E1        | 7.00 BSC. |            |      |  |

| A2        | 1.35      | 1.40      | 1.45 | L         | 0.45      | 0.60       | 0.75 |  |

| b         | 0.30      | 0.37      | 0.45 | aaa       | 0.20      |            |      |  |

| С         | 0.09      |           | 0.20 | bbb       | 0.20      |            |      |  |

| D         |           | 9.00 BSC. |      | CCC       |           | 0.10       |      |  |

| D1        | 7.00 BSC. |           |      | ddd       | 0.20      |            |      |  |

| е         |           | 0.80 BSC. |      | θ         | 0°        | 0° 3.5° 7° |      |  |

#### Table 4.3. LQFP-32 Package Dimensions

Notes:

1. All dimensions shown are in millimeters (mm) unless otherwise noted.

2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to JEDEC outline MS-026, variation BBA.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020B specification for Small Body Components.

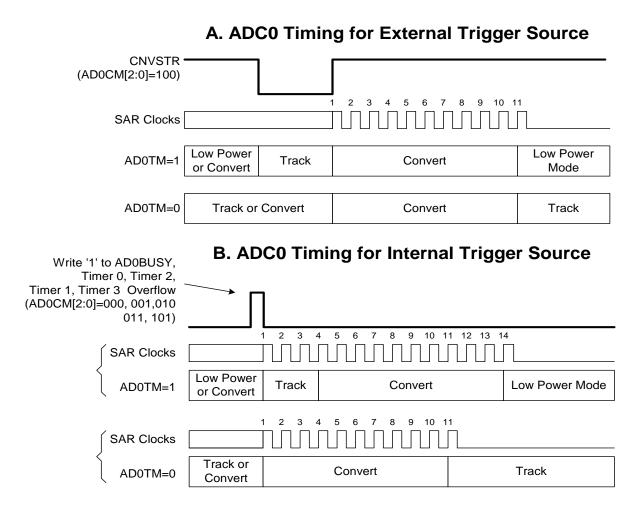

#### 5.3.2. Tracking Modes

According to Table 5.1, each ADC0 conversion must be preceded by a minimum tracking time for the converted result to be accurate. The AD0TM bit in register ADC0CN controls the ADC0 track-and-hold mode. In its default state, the ADC0 input is continuously tracked, except when a conversion is in progress. When the AD0TM bit is logic '1', ADC0 operates in low-power track-and-hold mode. In this mode, each conversion is preceded by a tracking period of 3 SAR clocks (after the start-of-conversion signal). When the CNVSTR signal is used to initiate conversions in low-power tracking mode, ADC0 tracks only when CNVSTR is low; conversion begins on the rising edge of CNVSTR (see Figure 5.4). Tracking can also be disabled (shutdown) when the device is in low power standby or sleep modes. Low-power track-and-hold mode is also useful when AMUX settings are frequently changed, due to the settling time requirements described in Section "5.3.3. Settling Time Requirements" on page 53.

# Figure 5.4. 10-Bit ADC Track and Conversion Example Timing

# SFR Definition 5.6. ADC0CN: ADC0 Control

| R/W       | R/W                                                                                                                         | R/W           | R/W             | R/W            | R/W            | R/W           | R/W           | Reset Valu  |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|----------------|----------------|---------------|---------------|-------------|--|--|--|--|

| AD0EN     | AD0TM                                                                                                                       | AD0INT        | AD0BUSY         | <b>ADOWINT</b> | AD0CM2         | AD0CM1        | AD0CM0        | 0000000     |  |  |  |  |

| Bit7      | Bit6                                                                                                                        | Bit5          | Bit4            | Bit3           | Bit2           | Bit1          | Bit0          |             |  |  |  |  |

| Bit 7:    | AD0EN: AD0                                                                                                                  | C0 Enable     | Bit.            |                |                |               |               |             |  |  |  |  |

|           | 0: ADC0 Disa                                                                                                                | abled. ADC    | C0 is in low-p  | ower shutde    | own.           |               |               |             |  |  |  |  |

|           |                                                                                                                             |               |                 |                |                | ersions.      |               |             |  |  |  |  |

| Bit 6:    | 1: ADC0 Enabled. ADC0 is active and ready for data conversions.<br>AD0TM: ADC0 Track Mode Bit.                              |               |                 |                |                |               |               |             |  |  |  |  |

|           | 0: Normal Tra                                                                                                               | ack Mode:     | When ADC0       | is enabled,    | tracking is    | continuous    | unless a coi  | nversion is |  |  |  |  |

|           | in progress.                                                                                                                |               |                 |                |                |               |               |             |  |  |  |  |

|           | 1: Low-powe                                                                                                                 |               |                 |                |                | ) bits (see b | elow).        |             |  |  |  |  |

| Bit 5:    | AD0INT: AD0                                                                                                                 |               | •               | •              | -              |               |               |             |  |  |  |  |

|           | 0: ADC0 has                                                                                                                 |               |                 |                | since the las  | st time AD0I  | NT was clea   | ared.       |  |  |  |  |

|           | 1: ADC0 has                                                                                                                 | •             |                 | ersion.        |                |               |               |             |  |  |  |  |

| Bit 4:    | ADOBUSY: A                                                                                                                  | ADC0 Busy     | Bit.            |                |                |               |               |             |  |  |  |  |

|           | Read:<br>0: ADC0 conversion is complete or a conversion is not currently in progress. AD0INT is set to                      |               |                 |                |                |               |               |             |  |  |  |  |

|           |                                                                                                                             |               |                 |                | i is not curre | enuy in prog  | ress. ADOIN   | vi is set t |  |  |  |  |

|           | 1: ADC0 con                                                                                                                 | -             | edge of ADC     | DU31.          |                |               |               |             |  |  |  |  |

|           | Write:                                                                                                                      |               | in progress.    |                |                |               |               |             |  |  |  |  |

|           | 0: No Effect.                                                                                                               |               |                 |                |                |               |               |             |  |  |  |  |

|           | 1: Initiates A                                                                                                              | DC0 Conve     | ersion if AD0   | CM2-0 = 00     | 0b             |               |               |             |  |  |  |  |

| Bit 3:    | ADOWINT: A                                                                                                                  |               |                 |                |                |               |               |             |  |  |  |  |

|           | 0: ADC0 Wir                                                                                                                 |               |                 |                |                | d since this  | flag was las  | t cleared.  |  |  |  |  |

|           | 1: ADC0 Wir                                                                                                                 |               |                 |                |                |               | U             |             |  |  |  |  |

| Bits 2–0: | AD0CM2-0:                                                                                                                   | ADC0 Star     | rt of Convers   | ion Mode S     | elect.         |               |               |             |  |  |  |  |

|           | When AD0TI                                                                                                                  | M = 0:        |                 |                |                |               |               |             |  |  |  |  |

|           | 000: ADC0 c                                                                                                                 | onversion     | initiated on e  | very write c   | f '1' to AD0   | BUSY.         |               |             |  |  |  |  |

|           | 001: ADC0 c                                                                                                                 |               |                 |                |                |               |               |             |  |  |  |  |

|           | 010: ADC0 c                                                                                                                 |               |                 |                |                |               |               |             |  |  |  |  |

|           | 011: ADC0 c                                                                                                                 |               |                 |                |                |               |               |             |  |  |  |  |

|           | 100: ADC0 conversion initiated on rising edge of external CNVSTR.<br>101: ADC0 conversion initiated on overflow of Timer 3. |               |                 |                |                |               |               |             |  |  |  |  |

|           |                                                                                                                             |               | initiated on o  | vertiow of I   | imer 3.        |               |               |             |  |  |  |  |

|           | 11x: Reserve                                                                                                                | -             |                 |                |                |               |               |             |  |  |  |  |

|           | When AD0TI<br>000: Tracking                                                                                                 |               | on write of '1' |                | SV and last    |               | eks followo   | hy con-     |  |  |  |  |

|           | versio                                                                                                                      | -             |                 |                |                |               |               |             |  |  |  |  |

|           | 001: Tracking                                                                                                               |               | on overflow o   | f Timer 0 ar   | nd lasts 3 S   | AR clocks f   | ollowed by a  | conversio   |  |  |  |  |

|           | 010: Tracking                                                                                                               | •             |                 |                |                |               | •             |             |  |  |  |  |

|           | 011: Tracking                                                                                                               | •             |                 |                |                |               |               |             |  |  |  |  |

|           | 100: ADC0 ti<br>edge.                                                                                                       |               |                 |                |                |               |               |             |  |  |  |  |

|           | 101: Tracking                                                                                                               |               |                 | (T) 0          |                |               | مالمين مالمين |             |  |  |  |  |

|           |                                                                                                                             | n initiated ( | n overtiow o    | t limer i ar   | nd lasts X S   | AR CIOCKS T   | ollowen nv r  | CONVERSION  |  |  |  |  |

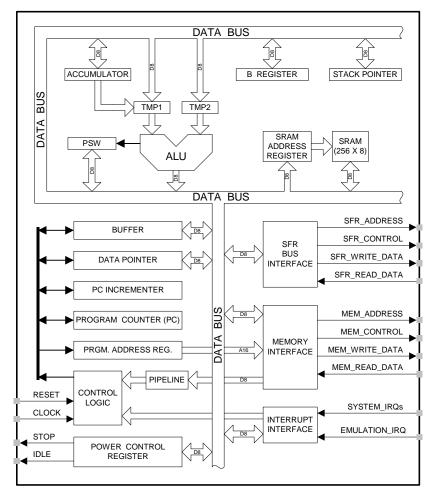

Figure 9.1. CIP-51 Block Diagram

# 9.2. Programming and Debugging Support

A C2-based serial interface is provided for in-system programming of the Flash program memory and communication with on-chip debug support logic. The re-programmable Flash can also be read and changed by the application software using the MOVC and MOVX instructions. This feature allows program memory to be used for non-volatile data storage as well as updating program code under software control.

The on-chip debug support logic facilitates full speed in-circuit debugging, allowing the setting of hardware breakpoints and watch points, starting, stopping and single stepping through program execution (including interrupt service routines), examination of the program's call stack, and reading/writing the contents of registers and memory. This method of on-chip debug is completely non-intrusive and non-invasive, requiring no RAM, Stack, timers, or other on-chip resources.

The CIP-51 is supported by development tools from Silicon Labs and third party vendors. Silicon Labs provides an integrated development environment (IDE) including editor, macro assembler, debugger and programmer. The IDE's debugger and programmer interface to the CIP-51 via its C2 interface to provide fast and efficient in-system device programming and debugging. Third party macro assemblers and C compilers are also available.

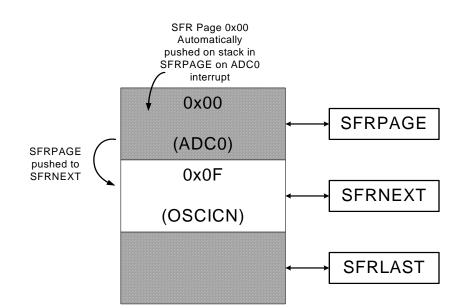

### Figure 9.5. SFR Page Stack After ADC0 Window Comparator Interrupt Occurs

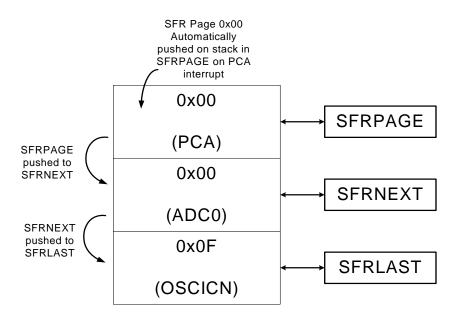

While in the ADC0 ISR, a PCA interrupt occurs. Recall the PCA interrupt is configured as a *high* priority interrupt, while the ADC0 interrupt is configured as a *low* priority interrupt. Thus, the CIP-51 will now vector to the high priority PCA ISR. Upon doing so, the CIP-51 will automatically place SFR page 0x00 into the SFRPAGE register. The value that was in the SFRPAGE register before the PCA interrupt (SFR Page 0x00 for ADC0) is pushed down the stack into SFRNEXT. Likewise, the value that was in the SFRLAST register, the "bottom" of the stack. Note that a value stored in SFRLAST (via a previous software write to the SFRLAST register) will be overwritten. See Figure 9.6 below.

# Figure 9.6. SFR Page Stack Upon PCA Interrupt Occurring During an ADC0 ISR

### SFR Definition 9.1. SFR0CN: SFR Page Control

| R/W      | R/W      | R/W        | R/W         | R/W            | R/W          | R/W      | R/W                             | Reset Valu |

|----------|----------|------------|-------------|----------------|--------------|----------|---------------------------------|------------|

| Reserved | Reserved | Reserved   | Reserved    | Reserved       | Reserved     | Reserved | SFRPGEN                         | 0000000    |

| Bit7     | Bit6     | Bit5       | Bit4        | Bit3           | Bit2         | Bit1     | Bit0                            | ·          |

|          | •        | tch to SFR | page 0. Thi | is bit is used | d to control | •        | ervice routine<br>ging functior | ı.         |

# SFR Definition 9.2. SFRPAGE: SFR Page

| R/W  | R/W                                                                                                                           | R/W                                                                               | R/W                                                        | R/W                                                          | R/W                                                     | R/W                                       | R/W         | Reset Value |

|------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------|-------------|-------------|

|      |                                                                                                                               |                                                                                   |                                                            |                                                              |                                                         |                                           |             | 0000000     |

| Bit7 | Bit6                                                                                                                          | Bit5                                                                              | Bit4                                                       | Bit3                                                         | Bit2                                                    | Bit1                                      | Bit0        |             |

|      | ifying SFR's.<br>Write: Sets th<br>Read: Byte is<br>When enable<br>switch to SFR<br>(unless SFR<br>SFRPAGE is<br>caused by in | he SFR Pa<br>s the SFR p<br>ed in the SF<br>R Page 0x0<br>Stack was<br>the top by | FR Page Cc<br>00 and retur<br>altered befo<br>te of the SF | ontrol Regis<br>in to the pre<br>ore a return<br>iR Page Sta | ter (SFR0C<br>vious SFR<br>ing from the<br>ick, and pus | page upon<br>e interrupt).<br>sh/pop ever | return fror | n interrupt |

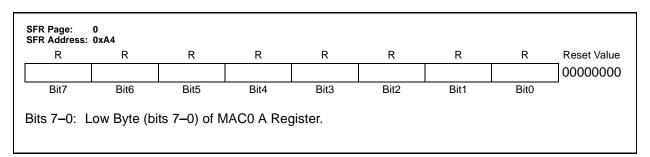

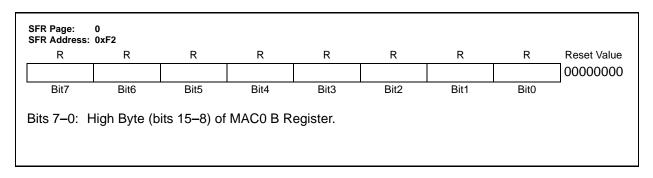

# SFR Definition 11.4. MAC0AL: MAC0 A Low Byte

# SFR Definition 11.5. MAC0BH: MAC0 B High Byte

# SFR Definition 11.6. MAC0BL: MAC0 B Low Byte

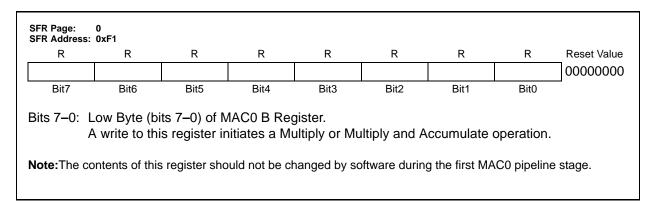

# 12. Reset Sources

Reset circuitry allows the controller to be easily placed in a predefined default condition. On entry to this reset state, the following occur:

- CIP-51 halts program execution

- Special Function Registers (SFRs) are initialized to their defined reset values

- External Port pins are forced to a known state

- Interrupts and timers are disabled.

All SFRs are reset to the predefined values noted in the SFR detailed descriptions. The contents of internal data memory are unaffected during a reset; any previously stored data is preserved. However, since the stack pointer SFR is reset, the stack is effectively lost, even though the data on the stack is not altered.

The Port I/O latches are reset to 0xFF (all logic ones) in open-drain mode. Weak pullups are enabled during and after the reset. For  $V_{DD}$  Monitor and power-on resets, the RST pin is driven low until the device exits the reset state.

On exit from the reset state, the program counter (PC) is reset, and the system clock defaults to the internal oscillator. Refer to Section "16. Oscillators" on page 168 for information on selecting and configuring the system clock source. The Watchdog Timer is enabled with the system clock divided by 12 as its clock source (Section "22.3. Watchdog Timer Mode" on page 270 details the use of the Watchdog Timer). Program execution begins at location 0x0000.

Figure 12.1. Reset Sources

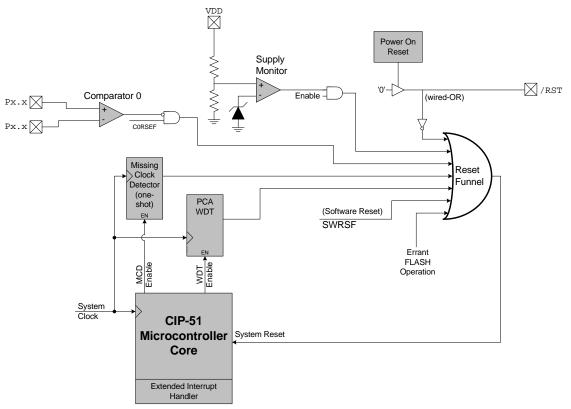

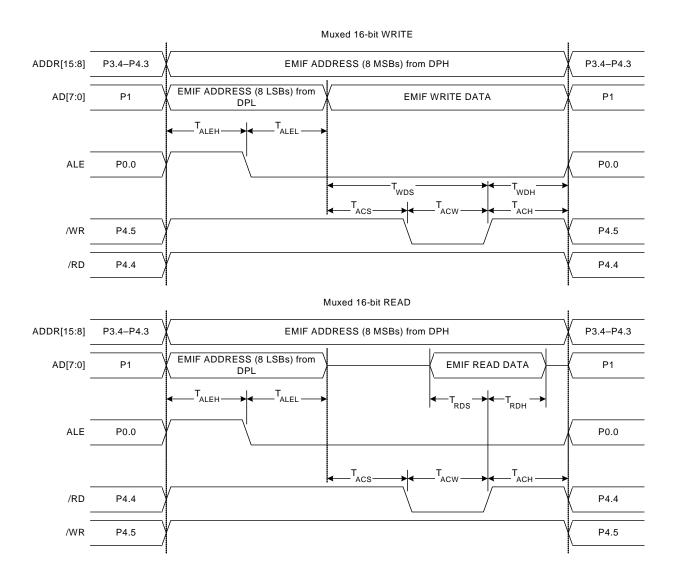

#### 15.6.2. Multiplexed Mode

#### 15.6.2.1.16-bit MOVX: EMI0CF[4:2] = '001', '010', or '011'.

Figure 15.7. Multiplexed 16-bit MOVX Timing

# 16.3. External Oscillator Drive Circuit

The external oscillator circuit may drive an external crystal, ceramic resonator, capacitor, or RC network. A CMOS clock may also provide a clock input. For a crystal or ceramic resonator configuration, the crystal/ resonator must be wired across the XTAL1 and XTAL2 pins as shown in Option 1 of Figure 16.1. A 10 M $\Omega$  resistor also must be wired across the XTAL1 and XTAL2 pins for the crystal/resonator configuration. In RC, capacitor, or CMOS clock configuration, the clock source should be wired to the XTAL2 pin as shown in Option 2, 3, or 4 of Figure 16.1. The type of external oscillator must be selected in the OSCXCN register, and the frequency control bits (XFCN) must be selected appropriately (see SFR Definition 16.5).

**Important Note on External Oscillator Usage:** Port pins must be configured when using the external oscillator circuit. When the external oscillator drive circuit is enabled in crystal/resonator mode, Port pins P0.5 and P0.6 (C8051F360/3) or P0.2 and P0.3 (C8051F361/2/4/5/6/7/8/9) are used as XTAL1 and XTAL2 respectively. When the external oscillator drive circuit is enabled in capacitor, RC, or CMOS clock mode, Port pin P0.6 (C8051F360/3) or P0.3 (C8051F361/2/4/5/6/7/8/9) is used as XTAL2. The Port I/O Crossbar should be configured to skip the Port pins used by the oscillator circuit; see Section "17.1. Priority Crossbar Decoder" on page 184 for Crossbar configuration. Additionally, when using the external oscillator circuit in crystal/resonator, capacitor, or RC mode, the associated Port pins should be configured as **analog inputs**. In CMOS clock mode, the associated pin should be configured as a **digital input**. See Section "17.2. Port I/O Initialization" on page 186 for details on Port input mode selection.

# 16.4. System Clock Selection

The internal oscillator requires little start-up time, and may be enabled and selected as the system clock in the same write to OSCICN. External crystals and ceramic resonators typically require a start-up time before they are settled and ready for use as the system clock. The Crystal Valid Flag (XTLVLD in register OSCXCN) is set to '1' by hardware when the external oscillator is settled. To avoid reading a false XTLVLD, in crystal mode software should delay at least 1 ms between enabling the external oscillator and checking XTLVLD. RC and C modes typically require no startup time. The PLL also requires time to lock onto the desired frequency, and the PLL Lock Flag (PLLLCK in register PLLOCN) is set to '1' by hardware once the PLL is locked on the correct frequency.

The CLKSL1-0 bits in register CLKSEL select which oscillator source generates the system clock. CLK-SL1-0 must be set to '01' for the system clock to run from the external oscillator; however the external oscillator may still clock certain peripherals, such as the timers and PCA, when the internal oscillator or the PLL is selected as the system clock. The system clock may be switched on-the-fly between the internal and external oscillators or the PLL, so long as the selected oscillator source is enabled and settled.

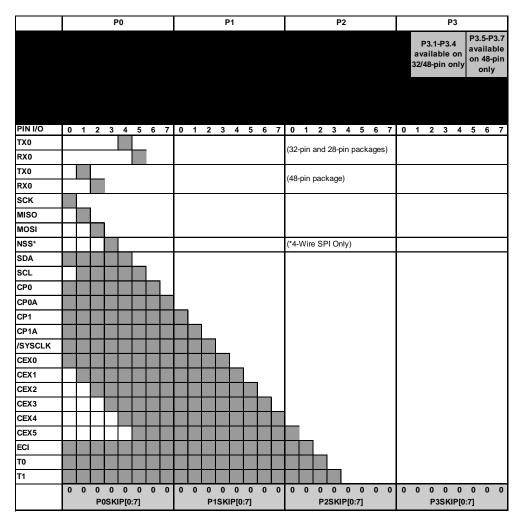

### 17.1. Priority Crossbar Decoder

The Priority Crossbar Decoder (Figure 17.3) assigns a priority to each I/O function, starting at the top with UART0. When a digital resource is selected, the least-significant unassigned Port pin is assigned to that resource (excluding UART0, which will be assigned to specific port pins (P0.1 and P0.2 in the C8051F360/3 devices, P0.4 and P0.5 in the C8051F361/2/4/5/6/7/8/9 devices). If a Port pin is assigned, the Crossbar skips that pin when assigning the next selected resource. Additionally, the Crossbar will skip Port pins whose associated bits in the PnSKIP registers are set. The PnSKIP registers allow software to skip Port pins that are to be used for analog input, dedicated functions, or GPIO.

**Important Note on Crossbar Configuration:** If a Port pin is claimed by a peripheral without use of the Crossbar, its corresponding PnSKIP bit should be set. This applies to the port pins associated with the external oscillator,  $V_{REF}$ , external CNVSTR signal, IDA0, and any selected ADC or comparator inputs. The Crossbar skips selected pins as if they were already assigned, and moves to the next unassigned pin. Figure 17.3 shows the Crossbar Decoder priority with no Port pins skipped (P0SKIP, P1SKIP, P2SKIP, P3SKIP = 0x00); Figure 17.4 shows the Crossbar Decoder priority with the P1.0 and P1.1 pins skipped (P1SKIP = 0x03).

Figure 17.3. Crossbar Priority Decoder with No Pins Skipped

Bit1

Bit0

0000000

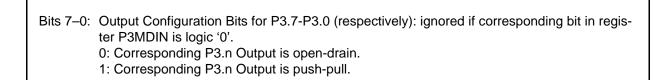

#### SFR Definition 17.23. P3MDOUT: Port3 Output Mode

Bit3

Bit2

Bit6

Bit7

Bit5

Bit4

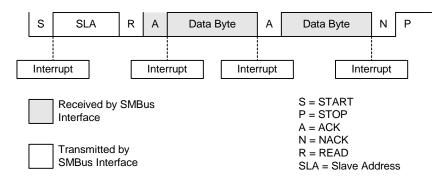

# SFR Definition 17.24. P3SKIP: Port3 Skip

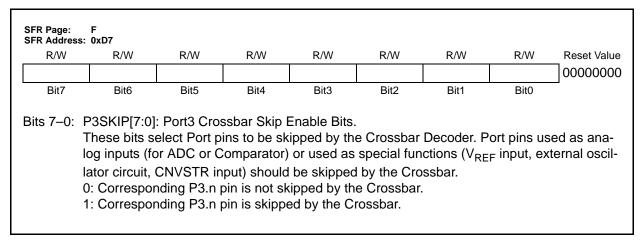

#### 18.5.2. Master Receiver Mode

Serial data is received on SDA while the serial clock is output on SCL. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic '1' (READ). Serial data is then received from the slave on SDA while the SMBus outputs the serial clock. The slave transmits one or more bytes of serial data. After each byte is received, ACKRQ is set to '1' and an interrupt is generated. Software must write the ACK bit (SMB0CN.1) to define the outgoing acknowledge value (Note: writing a '1' to the ACK bit generates an ACK; writing a '0' generates a NACK). Software should write a '0' to the ACK bit after the last byte is received, to transmit a NACK. The interface exits Master Receiver Mode after the STO bit is set and a STOP is generated. The interface will switch to Master Transmitter Mode if SMB0DAT is written while an active Master Receiver. Figure 18.6 shows a typical Master Receiver sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur **before** the ACK cycle in this mode.

Figure 18.6. Typical Master Receiver Sequence

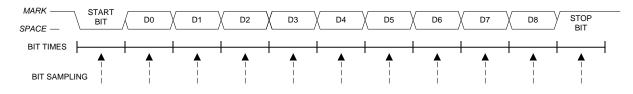

#### 19.2.2. 9-Bit UART

9-bit UART mode uses a total of eleven bits per data byte: a start bit, 8 data bits (LSB first), a programmable ninth data bit, and a stop bit. The state of the ninth transmit data bit is determined by the value in TB80 (SCON0.3), which is assigned by user software. It can be assigned the value of the parity flag (bit P in register PSW) for error detection, or used in multiprocessor communications. On receive, the ninth data bit goes into RB80 (SCON0.2) and the stop bit is ignored.

Data transmission begins when an instruction writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to '1'. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: (1) RI0 must be logic '0', and (2) if MCE0 is logic '1', the 9th bit must be logic '1' (when MCE0 is logic '0', the state of the ninth data bit is unimportant). If these conditions are met, the eight bits of data are stored in SBUF0, the ninth bit is stored in RB80, and the RI0 flag is set to '1'. If the above conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set to '1'. A UART0 interrupt will occur if enabled when either TI0 or RI0 is set to '1'.

Figure 19.5. 9-Bit UART Timing Diagram

| Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |

|------------------------------|----------------------|----------------------------------|-----------------------|----------------------------------------------|------------------|----------------------------------|

| 230400                       | 0.45%                | 218                              | SYSCLK                | XX <sup>2</sup>                              | 1                | 0x93                             |

| 115200                       | -0.01%               | 434                              | SYSCLK                | XX                                           | 1                | 0x27                             |

| 57600                        | 0.45%                | 872                              | SYSCLK/4              | 01                                           | 0                | 0x93                             |

| 28800                        | -0.01%               | 1736                             | SYSCLK/4              | 01                                           | 0                | 0x27                             |

| 14400                        | 0.22%                | 3480                             | SYSCLK/12             | 00                                           | 0                | 0x6F                             |

| 9600                         | -0.01%               | 5208                             | SYSCLK/12             | 00                                           | 0                | 0x27                             |

| 2400                         | -0.01%               | 20832                            | SYSCLK/48             | 10                                           | 0                | 0x27                             |

# Table 19.7. Timer Settings for Standard Baud Rates Using the PLL

2. X = Don't care.

| Table 19.8. | Timer  | Settings | for | Standard | Raud | Rates | Ilsina - | the PLI |

|-------------|--------|----------|-----|----------|------|-------|----------|---------|

| 1abic 13.0. | IIIICI | Settings | IUI | Stanuaru | Dauu | naico | USIIIY   |         |

|                              | Frequency: 100.0 MHz |                                  |                       |                                              |                  |                                  |  |  |  |  |

|------------------------------|----------------------|----------------------------------|-----------------------|----------------------------------------------|------------------|----------------------------------|--|--|--|--|

| Target<br>Baud Rate<br>(bps) | Baud Rate<br>% Error | Oscilla-<br>tor Divide<br>Factor | Timer Clock<br>Source | SCA1-SCA0<br>(pre-scale select) <sup>1</sup> | T1M <sup>1</sup> | Timer 1<br>Reload<br>Value (hex) |  |  |  |  |

| 230400                       | -0.01%               | 434                              | SYSCLK                | XX <sup>2</sup>                              | 1                | 0x27                             |  |  |  |  |

| 115200                       | 0.45%                | 872                              | SYSCLK/4              | 01                                           | 0                | 0x93                             |  |  |  |  |

| 57600                        | -0.01%               | 1736                             | SYSCLK/4              | 01                                           | 0                | 0x27                             |  |  |  |  |

| 28800                        | 0.22%                | 3480                             | SYSCLK/12             | 00                                           | 0                | 0x6F                             |  |  |  |  |

| 14400                        | -0.47%               | 6912                             | SYSCLK/48             | 10                                           | 0                | 0xB8                             |  |  |  |  |

| 9600                         | 0.45%                | 10464                            | SYSCLK/48             | 10                                           | 0                | 0x93                             |  |  |  |  |

| Notes:                       |                      |                                  |                       |                                              |                  |                                  |  |  |  |  |

1. SCA1–SCA0 and T1M bit definitions can be found in Section 21.1.

2. X = Don't care.

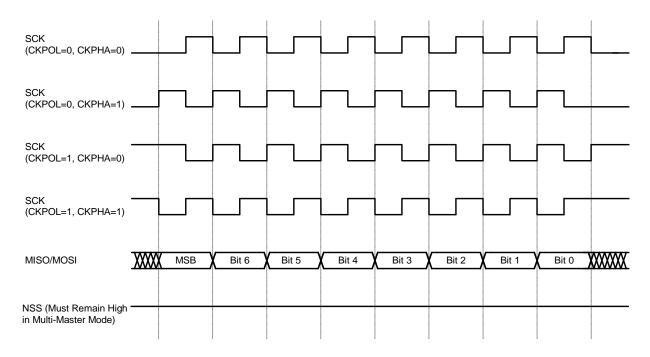

## 20.5. Serial Clock Timing

Four combinations of serial clock phase and polarity can be selected using the clock control bits in the SPI0 Configuration Register (SPI0CFG). The CKPHA bit (SPI0CFG.5) selects one of two clock phases (edge used to latch the data). The CKPOL bit (SPI0CFG.4) selects between an active-high or active-low clock. Both master and slave devices must be configured to use the same clock phase and polarity. SPI0 should be disabled (by clearing the SPIEN bit, SPI0CN.0) when changing the clock phase or polarity. The clock and data line relationships for master mode are shown in Figure 20.5. For slave mode, the clock and data relationships are shown in Figure 20.6 and Figure 20.7. Note that CKPHA must be set to '0' on both the master and slave SPI when communicating between two of the following devices: C8051F04x, C8051F06x, C8051F12x, C8051F31x, C8051F32x, C8051F33x, and C8051F36x.

The SPI0 Clock Rate Register (SPI0CKR) as shown in SFR Definition 20.3 controls the master mode serial clock frequency. This register is ignored when operating in slave mode. When the SPI is configured as a master, the maximum data transfer rate (bits/sec) is one-half the system clock frequency or 12.5 MHz, whichever is slower. When the SPI is configured as a slave, the maximum data transfer rate (bits/sec) for full-duplex operation is 1/10 the system clock frequency, provided that the master issues SCK, NSS (in 4-wire slave mode), and the serial input data synchronously with the slave's system clock. If the master issues SCK, NSS, and the serial input data asynchronously, the maximum data transfer rate (bits/sec) must be less than 1/10 the system clock frequency. In the special case where the master only wants to transmit data to the slave and does not need to receive data from the slave (i.e. half-duplex operation), the SPI slave can receive data at a maximum data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data transfer rate (bits/sec) of 1/4 the system clock frequency. This is provided that the master issues SCK, NSS, and the serial input data synchronously with the slave's system clock frequency.

Figure 20.5. Master Mode Data/Clock Timing

| SFR Definition | 20.2. | SPI0CN: | SPI0 | Control |

|----------------|-------|---------|------|---------|

|----------------|-------|---------|------|---------|

| R/W       | R/W                                                                                      | R/W                                                                                  | R/W                                                       | R/W                                                           | R/W                                   | R                             | R/W          | Reset Value |

|-----------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|---------------------------------------|-------------------------------|--------------|-------------|

| SPIF      | WCOL                                                                                     | MODF                                                                                 | RXOVRN                                                    | NSSMD1                                                        | NSSMD0                                | TXBMT                         | SPIEN        | 00000110    |

| Bit7      | Bit6                                                                                     | Bit5                                                                                 | Bit4                                                      | Bit3                                                          | Bit2                                  | Bit1                          | Bit0         |             |

| Bit 7:    | SPIF: SPI0 I<br>This bit is se<br>setting this b                                         | t to logic '1<br>it causes th                                                        | ' by hardwa<br>ne CPU to v                                | ector to the                                                  | SPI0 interr                           | upt service                   |              |             |

| Bit 6:    | automatically<br>WCOL: Write<br>This bit is se<br>the SPI0 dat<br>cleared by se          | e Collision I<br>t to logic '1<br>a register v                                       | -lag.<br>' by hardwa                                      | re (and gen                                                   | erates a SF                           | PI0 interrup                  |              |             |

| Bit 5:    | MODF: Mod<br>This bit is se<br>collision is de<br>matically cle                          | e Fault Flag<br>t to logic '1'<br>etected (NS                                        | by hardwa<br>S is low, M                                  | STEN = 1,                                                     | and NSSM                              | D[1:0] = 01)                  | ,            |             |

| Bit 4:    | RXOVRN: R<br>This bit is se<br>fer still holds<br>shifted into the<br>be cleared b       | eceive Ove<br>t to logic '1'<br>unread da<br>he SPI0 shi                             | errun Flag (\$<br>by hardwa<br>ta from a pr               | Slave Mode<br>re (and gen<br>evious trans                     | only).<br>erates a SP<br>sfer and the | 10 interrupt<br>last bit of t | he current   | transfer is |

| Bits 3–2: | NSSMD1–N<br>Selects betw<br>(See Section<br>00: 3-Wire S<br>01: 4-Wire S<br>1x: 4-Wire S | SSMD0: SI<br>veen the fol<br>20.2 and 3<br>lave or 3-w<br>lave or Mul<br>ingle-Maste | lowing NSS<br>Section 20.3<br>ire Master I<br>ti-Master M | operation r<br>3).<br>Vode. NSS<br>ode (Defau<br>SS signal is | signal is no<br>lt). NSS is a         | lways an ir                   | put to the o |             |

| Bit 1:    | TXBMT: Tran<br>This bit will b<br>data in the tr<br>indicating that                      | nsmit Buffe<br>be set to log<br>ansmit buff                                          | r Empty.<br>jic '0' when<br>er is transfe                 | new data h<br>rred to the \$                                  | SPI shift reg                         | ister, this b                 |              |             |

| Bit O:    | SPIEN: SPIC<br>This bit enable<br>0: SPI disable                                         | ) Enable.<br>bles/disable                                                            |                                                           |                                                               |                                       |                               |              |             |

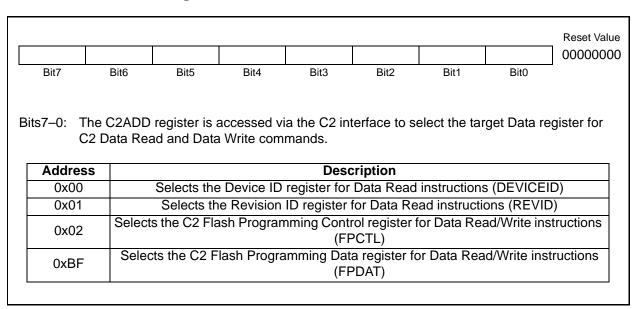

# 24. C2 Interface

C8051F36x devices include an on-chip Silicon Laboratories 2-Wire (C2) debug interface to allow Flash programming and in-system debugging with the production part installed in the end application. The C2 interface uses a clock signal (C2CK) and a bi-directional C2 data signal (C2D) to transfer information between the device and a host system. See the C2 Interface Specification for details on the C2 protocol.

### 24.1. C2 Interface Registers

The following describes the C2 registers necessary to perform Flash programming functions through the C2 interface. All C2 registers are accessed through the C2 interface as described in the C2 Interface Specification.

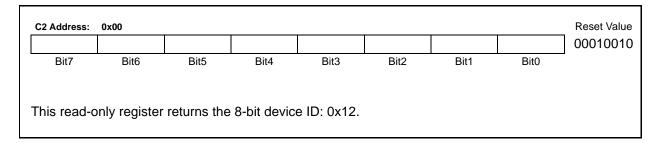

# C2 Register Definition 24.1. C2ADD: C2 Address

# C2 Register Definition 24.2. DEVICEID: C2 Device ID