#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                  |

|---------------------------------|---------------------------------------------------------------------------|

| Core Processor                  | ARM1136JF-S                                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                            |

| Speed                           | 532MHz                                                                    |

| Co-Processors/DSP               | Multimedia; GPU, IPU, MPEG-4, VFP                                         |

| RAM Controllers                 | DDR                                                                       |

| Graphics Acceleration           | Yes                                                                       |

| Display & Interface Controllers | Keyboard, Keypad, LCD                                                     |

| Ethernet                        | -                                                                         |

| SATA                            | -                                                                         |

| USB                             | USB 2.0 (3)                                                               |

| Voltage - I/O                   | 1.8V, 2.0V, 2.5V, 2.7V, 3.0V                                              |

| Operating Temperature           | 0°C ~ 70°C (TA)                                                           |

| Security Features               | Random Number Generator, RTIC, Secure Fusebox, Secure JTAG, Secure Memory |

| Package / Case                  | 457-LFBGA                                                                 |

| Supplier Device Package         | 457-LFBGA (14x14)                                                         |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx31lvkn5b     |

|                                 |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Block<br>Mnemonic | Block Name                                   | Functional<br>Grouping     | Brief Description                                                                                                                                                                              | Section/<br>Page                  |  |  |  |  |

|-------------------|----------------------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|--|

| Fusebox           | Fusebox                                      | ROM                        | The Fusebox is a ROM that is factory configured by Freescale.                                                                                                                                  | 4.3.12/55<br>See also<br>Table 11 |  |  |  |  |

| GPIO              | General<br>Purpose I/O<br>Module             | Pins                       | The GPIO provides several groups of 32-bit bidirectional, general purpose I/O. This peripheral provides dedicated general-purpose signals that can be configured as either inputs or outputs.  | _                                 |  |  |  |  |

| GPT               | General<br>Purpose Timer                     | Timer<br>Peripheral        | The GPT is a multipurpose module used to measure intervals or generate periodic output.                                                                                                        | _                                 |  |  |  |  |

| GPU               | Graphics<br>Processing Unit                  | Multimedia<br>Peripheral   | The GPU provides hardware acceleration for 2D and 3D graphics algorithms.                                                                                                                      | _                                 |  |  |  |  |

| l <sup>2</sup> C  | Inter IC<br>Communication                    | Connectivity<br>Peripheral | The I <sup>2</sup> C provides serial interface for controlling the Sensor Interface<br>and other external devices. Data rates of up to 100 Kbits/s are<br>supported.                           | 4.3.13/56                         |  |  |  |  |

| IIM               | IC Identification<br>Module                  | ID                         | The IIM provides an interface for reading device identification.                                                                                                                               | _                                 |  |  |  |  |

| IPU               | Image<br>Processing Unit                     | Multimedia<br>Peripheral   | The IPU processes video and graphics functions in the MCIMX31 and interfaces to video, still image sensors, and displays.                                                                      | 4.3.14/57,<br>4.3.15/59           |  |  |  |  |

| KPP               | Keypad Port                                  | Connectivity<br>Peripheral | The KPP is used for keypad matrix scanning or as a general purpose I/O. This peripheral simplifies the software task of scanning a keypad matrix.                                              | _                                 |  |  |  |  |

| MPEG-4            | MPEG-4 Video<br>Encoder                      | Multimedia<br>Peripherals  | The MPEG-4 encoder accelerates video compression, following the MPEG-4 standard                                                                                                                | _                                 |  |  |  |  |

| MSHC              | Memory Stick<br>Host Controller              | Connectivity<br>Peripheral | The MSHC is placed in between the AIPS and the customer memory stick to support data transfer from the MCIMX31 to the customer memory stick.                                                   | 4.3.16/84                         |  |  |  |  |

| PADIO             | Pads I/O                                     | Buffers and<br>Drivers     | The PADIO serves as the interface between the internal modules and the device's external connections.                                                                                          | 4.3.1/22                          |  |  |  |  |

| PCMCIA            | РСМ                                          | Connectivity<br>Peripheral | The PCMCIA Host Adapter provides the control logic for PCMCIA socket interfaces.                                                                                                               | 4.3.17/86                         |  |  |  |  |

| PWM               | Pulse-Width<br>Modulator                     | Timer<br>Peripheral        | The PWM has a 16-bit counter and is optimized to generate sound from stored sample audio images. It can also generate tones.                                                                   | 4.3.18/88                         |  |  |  |  |

| RNGA              | Random<br>Number<br>Generator<br>Accelerator | Security                   | The RNGA module is a digital integrated circuit capable of generating 32-bit random numbers. It is designed to comply with FIPS-140 standards for randomness and non-determinism.              | _                                 |  |  |  |  |

| RTC               | Real Time Clock                              | Timer<br>Peripheral        | The RTC module provides a current stamp of seconds, minutes, hours, and days. Alarm and timer functions are also available for programming. The RTC supports dates from the year 1980 to 2050. | —                                 |  |  |  |  |

| RTIC              | Run-Time<br>Integrity<br>Checkers            | Security                   | The RTIC ensures the integrity of the peripheral memory contents and assists with boot authentication.                                                                                         |                                   |  |  |  |  |

### Functional Description and Application Information

| Block<br>Mnemonic | Block Name                                                                    | Functional<br>Grouping          | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Section/<br>Page |

|-------------------|-------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| SCC               | Security<br>Controller<br>Module                                              | Security                        | The SCC is a hardware component composed of two blocks—the<br>Secure RAM module, and the Security Monitor. The Secure RAM<br>provides a way of securely storing sensitive information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | —                |

| SDHC              | Secured Digital<br>Host Controller                                            | Connectivity<br>Peripheral      | The SDHC controls the MMC (MultiMediaCard), SD (Secure Digital) memory, and I/O cards by sending commands to cards and performing data accesses to and from the cards.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.19/89        |

| SDMA              | Smart Direct<br>Memory Access                                                 | System<br>Control<br>Peripheral | The SDMA controller maximizes the system's performance by relieving the ARM core of the task of bulk data transfer from memory to memory or between memory and on-chip peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                |

| SIM               | Subscriber<br>Identification<br>Module                                        | Connectivity<br>Peripheral      | The SIM interfaces to an external Subscriber Identification Card. It is<br>an asynchronous serial interface adapted for Smart Card<br>communication for e-commerce applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.3.20/90        |

| SJC               | Secure JTAG<br>Controller                                                     | Debug                           | The SJC provides debug and test control with maximum security and provides a flexible architecture for future derivatives or future multi-cores architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.3.21/94        |

| SSI               | Synchronous<br>Serial Interface                                               | Multimedia<br>Peripheral        | The SSI is a full-duplex, serial port that allows the device to<br>communicate with a variety of serial devices, such as standard<br>codecs, Digital Signal Processors (DSPs), microprocessors,<br>peripherals, and popular industry audio codecs that implement the<br>inter-IC sound bus standard (I2S) and Intel AC97 standard.                                                                                                                                                                                                                                                                                                                                    | 4.3.22/96        |

| UART              | Universal<br>Asynchronous<br>Receiver/Trans<br>mitter                         | Connectivity<br>Peripheral      | The UART provides serial communication capability with external devices through an RS-232 cable or through use of external circuitry that converts infrared signals to electrical signals (for reception) or transforms electrical signals to signals that drive an infrared LED (for transmission) to provide low speed IrDA compatibility.                                                                                                                                                                                                                                                                                                                          |                  |

| USB               | Universal Serial<br>Bus—<br>2 Host<br>Controllers and<br>1 OTG<br>(On-The-Go) | Connectivity<br>Peripherals     | <ul> <li>USB Host 1 is designed to support transceiverless connection to the on-board peripherals in Low Speed and Full Speed mode, and connection to the ULPI (UTMI+ Low-Pin Count) and Legacy Full Speed transceivers.</li> <li>USB Host 2 is designed to support transceiverless connection to the Cellular Modem Baseband Processor.</li> <li>The USB-OTG controller offers HS/FS/LS capabilities in Host mode and HS/FS in device mode. In Host mode, the controller supports direct connection of a FS/LS device (without external hub). In device (bypass) mode, the OTG port functions as gateway between the Host 1 Port and the OTG transceiver.</li> </ul> | 4.3.23/104       |

| WDOG              | Watchdog Timer<br>Module                                                      | Timer<br>Peripheral             | The WDOG module protects against system failures by providing a method for the system to recover from unexpected events or programming errors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

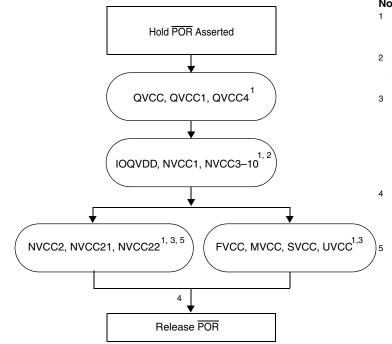

# 4.2 Supply Power-Up/Power-Down Requirements and Restrictions

Any MCIMX31 board design must comply with the power-up and power-down sequence guidelines as described in this section to guarantee reliable operation of the device. Any deviation from these sequences may result in any or all of the following situations:

- Cause excessive current during power up phase

- Prevent the device from booting

- Cause irreversible damage to the MCIMX31 (worst-case scenario)

## 4.2.1 Powering Up

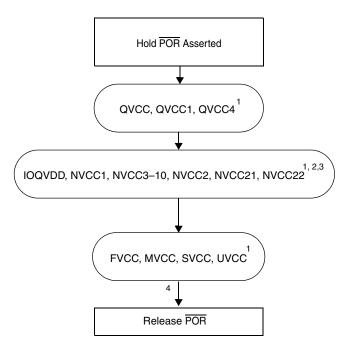

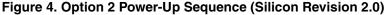

The Power On Reset ( $\overline{POR}$ ) pin must be kept asserted (low) throughout the power up sequence. Power up logic must guarantee that all power sources reach their target values prior to the release (de-assertion) of  $\overline{POR}$ . Figure 2 shows the power-up sequence for silicon Revisions 1.2 and previous. Figure 3 and Figure 4 show the power-up sequence for silicon Revision 2.0.

### NOTE

Stages need to be performed in the order shown; however, *within* each stage, supplies can be powered up in any order. For example, supplies IOQVDD, NVCC1, and NVCC3 through NVCC10 do not need to be powered up in the order shown.

## CAUTION

NVCC6 and NVCC9 must be at the same voltage potential. These supplies are connected together on-chip to optimize ESD damage immunity.

#### Notes:

- The board design must guarantee that supplies reach 90% level before transition to the next state, using Power Management IC or other means.

- <sup>2</sup> The NVCC1 supply must not precede IOQVDD by more than 0.2 V until IOQVDD has reached 1.5 V. If IOQVDD is powered up first, there are no restrictions.

- <sup>3</sup> The parallel paths in the flow indicate that supply group NVCC2, NVCC21, and NVCC22, and supply group FVCC, MVCC, SVCC, and UVCC ramp-ups are independent. Note that this power-up sequence is backward compatible to Silicon Revs. 1.15 and 1.2, because NVCC2x ramp-up proceeding PLL supplies is allowed.

- <sup>4</sup> Unlike the power-up sequence for Silicon Revision 1.2, FUSE\_VDD should not be driven on power-up for Silicon Revision 2.0. This supply is dedicated for fuse burning (programming), and should not be driven upon boot-up.

<sup>5</sup> Raising IOQVDD before NVCC21 produces a slight increase in current drain on IOQVDD of approximately 3–5 mA. The current increase will not damage the IC. Refer to Errata ID TLSbo91750 for details.

### Figure 3. Option 1 Power-Up Sequence (Silicon Revision 2.0)

#### Notes:

- <sup>1</sup> The board design must guarantee that supplies reach 90% level before transition to the next state, using Power Management IC or other means.

- <sup>2</sup> The NVCC1 supply must not precede IOQVDD by more than 0.2 V until IOQVDD has reached 1.5 V. If IOQVDD is powered up first, there are no restrictions.

- <sup>3</sup> Raising NVCC2, NVCC21, and NVCC22 at the same time as IOQVDD does not produce the slight increase in current drain on IOQVDD (as described in Figure 3, Note 5).

- <sup>4</sup> Unlike the power-up sequence for Silicon Revision 1.2, FUSE\_VDD should not be driven on power-up for Silicon Revision 2.0. This supply is dedicated for fuse burning (programming), and should not be driven upon boot-up.

## 4.2.2 Powering Down

The power-down sequence prior to silicon Revision 2.0 should be completed as follows:

- 1. Lower the FUSE\_VDD supply (when in write mode).

- 2. Lower the remaining supplies.

For silicon revisions beginning with Revision 2.0 there is no special requirements for power down sequence.

# 4.3 Module-Level Electrical Specifications

This section contains the MCIMX31 electrical information including timing specifications, arranged in alphabetical order by module name.

# 4.3.1 I/O Pad (PADIO) Electrical Specifications

This section specifies the AC/DC characterization of functional I/O of the MCIMX31. There are two main types of I/O: regular and DDR. In this document, the "Regular" type is referred to as GPIO.

## 4.3.1.1 DC Electrical Characteristics

The MCIMX31 I/O parameters appear in Table 15 for GPIO. See Table 8 for temperature and supply voltage ranges.

## NOTE

The term NVCC in this section refers to the associated supply rail of an input or output. The association is shown in the Signal Multiplexing chapter of the reference manual. NVCC for Table 15 refers to NVCC1 and NVCC3–10; QVCC refers to QVCC, QVCC1, and QVCC4.

| Parameter                                 | Symbol            | Test Conditions                                                   | Min            | Тур | Max      | Units |

|-------------------------------------------|-------------------|-------------------------------------------------------------------|----------------|-----|----------|-------|

| High-level output voltage                 | V <sub>OH</sub>   | I <sub>OH</sub> = -1 mA                                           | NVCC -0.15     | _   | —        | V     |

|                                           |                   | I <sub>OH</sub> = specified Drive                                 | 0.8*NVCC       | _   | —        | V     |

| Low-level output voltage                  | V <sub>OL</sub>   | I <sub>OL</sub> = 1 mA                                            | —              | _   | 0.15     | V     |

|                                           |                   | I <sub>OL</sub> = specified Drive                                 | _              | _   | 0.2*NVCC | V     |

| High-level output current, slow slew rate | I <sub>OH_S</sub> | V <sub>OH</sub> =0.8*NVCC<br>Std Drive<br>High Drive<br>Max Drive | -2<br>-4<br>-8 | _   | _        | mA    |

| High-level output current, fast slew rate | I <sub>OH_F</sub> | V <sub>OH</sub> =0.8*NVCC<br>Std Drive<br>High Drive<br>Max Drive | -4<br>-6<br>-8 |     | —        | mA    |

### Table 15. GPIO DC Electrical Parameters

| Parameter                                | Symbol            | Test Conditions                                                   | Min         | Тур | Max        | Units                    |

|------------------------------------------|-------------------|-------------------------------------------------------------------|-------------|-----|------------|--------------------------|

| Low-level output current, slow slew rate | I <sub>OL_S</sub> | V <sub>OL</sub> =0.2*NVCC<br>Std Drive<br>High Drive<br>Max Drive | 2<br>4<br>8 |     |            | mA                       |

| Low-level output current, fast slew rate | I <sub>OL_F</sub> | V <sub>OL</sub> =0.2*NVCC<br>Std Drive<br>High Drive<br>Max Drive | 4<br>6<br>8 |     | _          | mA                       |

| High-Level DC input voltage              | V <sub>IH</sub>   | —                                                                 | 0.7*NVCC    | _   | NVCC       | V                        |

| Low-Level DC input voltage               | V <sub>IL</sub>   | —                                                                 | 0           | _   | 0.3*QVCC   | V                        |

| Input Hysteresis                         | V <sub>HYS</sub>  | Hysteresis enabled                                                | 0.25        | _   | —          | V                        |

| Schmitt trigger VT+                      | V <sub>T</sub> +  | Hysteresis enabled                                                | 0.5*QVCC    | _   | —          | V                        |

| Schmitt trigger VT-                      | V <sub>T</sub> –  | Hysteresis enabled                                                | _           | _   | 0.5*QVCC   | V                        |

| Pull-up resistor (100 kΩ PU)             | R <sub>PU</sub>   | —                                                                 | _           | 100 | —          | kΩ                       |

| Pull-down resistor (100 k $\Omega$ PD)   | R <sub>PD</sub>   | —                                                                 | _           | 100 | —          | K52                      |

| Input current (no PU/PD)                 | I <sub>IN</sub>   | V <sub>I</sub> = NVCC or GND                                      | _           | _   | ±1         | μA                       |

| Input current (100 k $\Omega$ PU)        | I <sub>IN</sub>   | V <sub>I</sub> = 0<br>V <sub>I</sub> = NVCC                       | —           | _   | 25<br>0.1  | μ <b>Α</b><br>μ <b>Α</b> |

| Input current (100 kΩ PD)                | I <sub>IN</sub>   | V <sub>I</sub> = 0<br>V <sub>I</sub> = NVCC                       | _           |     | 0.25<br>28 | μΑ<br>μΑ                 |

| Tri-state leakage current                | I <sub>OZ</sub>   | V <sub>I</sub> = NVCC or GND<br>I/O = High Z                      | _           | _   | ±2         | μΑ                       |

| Table 15. GPIO DC Electrical Parameters ( | (continued) |

|-------------------------------------------|-------------|

|-------------------------------------------|-------------|

The MCIMX31 I/O parameters appear in Table 16 for DDR (Double Data Rate). See Table 8, "Operating Ranges," on page 13 for temperature and supply voltage ranges.

## NOTE

NVCC for Table 16 refers to NVCC2, NVCC21, and NVCC22.

## Table 16. DDR (Double Data Rate) I/O DC Electrical Parameters

| Parameter                 | Symbol          | Test Conditions                                                                             | Min                            | Тур | Max      | Units |

|---------------------------|-----------------|---------------------------------------------------------------------------------------------|--------------------------------|-----|----------|-------|

| High-level output voltage | V <sub>OH</sub> | I <sub>OH</sub> = -1 mA                                                                     | NVCC -0.12                     | _   | —        | V     |

|                           |                 | I <sub>OH</sub> = specified Drive                                                           | 0.8*NVCC                       | _   | —        | V     |

| Low-level output voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 1 mA                                                                      | —                              | _   | 0.08     | V     |

|                           |                 | I <sub>OL</sub> = specified Drive                                                           | —                              | _   | 0.2*NVCC | V     |

| High-level output current | I <sub>OH</sub> | V <sub>OH</sub> =0.8*NVCC<br>Std Drive<br>High Drive<br>Max Drive<br>DDR Drive <sup>1</sup> | -3.6<br>-7.2<br>-10.8<br>-14.4 | _   | _        | mA    |

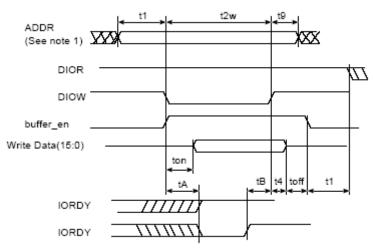

| ATA<br>Parameter | Parameter<br>from Figure 12 | Value                                                                      | Controlling<br>Variable         |

|------------------|-----------------------------|----------------------------------------------------------------------------|---------------------------------|

| t1               | t1                          | t1 (min) = time_1 * T - (tskew1 + tskew2 + tskew5)                         | time_1                          |

| t2               | t2w                         | t2 (min) = time_2w * T – (tskew1 + tskew2 + tskew5)                        | time_2w                         |

| t9               | t9                          | t9 (min) = time_9 * T - (tskew1 + tskew2 + tskew6)                         | time_9                          |

| t3               |                             | t3 (min) = (time_2w - time_on)* T - (tskew1 + tskew2 +tskew5)              | If not met, increase<br>time_2w |

| t4               | t4                          | t4 (min) = time_4 * T - tskew1                                             | time_4                          |

| tA               | tA                          | $tA = (1.5 + time_ax) * T - (tco + tsui + tcable2 + tcable2 + 2*tbuf)$     | time_ax                         |

| tO               | _                           | t0(min) = (time_1 + time_2 + time_9) * T                                   | time_1, time_2r,<br>time_9      |

| _                | _                           | Avoid bus contention when switching buffer on by making ton long enough.   | _                               |

| —                | _                           | Avoid bus contention when switching buffer off by making toff long enough. | —                               |

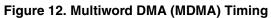

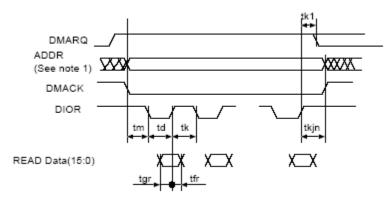

Figure 13 shows timing for MDMA read, Figure 14 shows timing for MDMA write, and Table 27 lists the timing parameters for MDMA read and write.

Figure 13. MDMA Read Timing Diagram

Figure 14. MDMA Write Timing Diagram

| ATA<br>Parameter | Parameter<br>from<br>Figure 13,<br>Figure 14 | Value                                                                                            | Controlling<br>Variable |

|------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------|

| tm, ti           | tm                                           | tm (min) = ti (min) = time_m * T - (tskew1 + tskew2 + tskew5)                                    | time_m                  |

| td               | td, td1                                      | td1.(min) = td (min) = time_d * T – (tskew1 + tskew2 + tskew6)                                   | time_d                  |

| tk               | tk                                           | tk.(min) = time_k * T - (tskew1 + tskew2 + tskew6)                                               | time_k                  |

| tO               | —                                            | t0 (min) = (time_d + time_k) * T                                                                 | time_d, time_k          |

| tg(read)         | tgr                                          | tgr (min-read) = tco + tsu + tbuf + tbuf + tcable1 + tcable2<br>tgr.(min-drive) = td - te(drive) | time_d                  |

| tf(read)         | tfr                                          | tfr (min-drive) = 0                                                                              | —                       |

| tg(write)        | —                                            | tg (min-write) = time_d * T – (tskew1 + tskew2 + tskew5)                                         | time_d                  |

| tf(write)        | —                                            | tf (min-write) = time_k * T – (tskew1 + tskew2 + tskew6)                                         | time_k                  |

| tL               | —                                            | $tL (max) = (time_d + time_k-2)^T - (tsu + tco + 2^tbuf + 2^tcable2)$                            | time_d, time_k          |

| tn, tj           | tkjn                                         | tn= tj= tkjn = (max(time_k,. time_jn) * T - (tskew1 + tskew2 + tskew6)                           | time_jn                 |

| _                | ton<br>toff                                  | ton = time_on * T – tskew1<br>toff = time_off * T – tskew1                                       | _                       |

## 4.3.6 AUDMUX Electrical Specifications

The AUDMUX provides a programmable interconnect logic for voice, audio and data routing between internal serial interfaces (SSI) and external serial interfaces (audio and voice codecs). The AC timing of AUDMUX external pins is hence governed by the SSI module. Please refer to their respective electrical specifications.

## 4.3.7 CSPI Electrical Specifications

This section describes the electrical information of the CSPI.

## 4.3.7.1 CSPI Timing

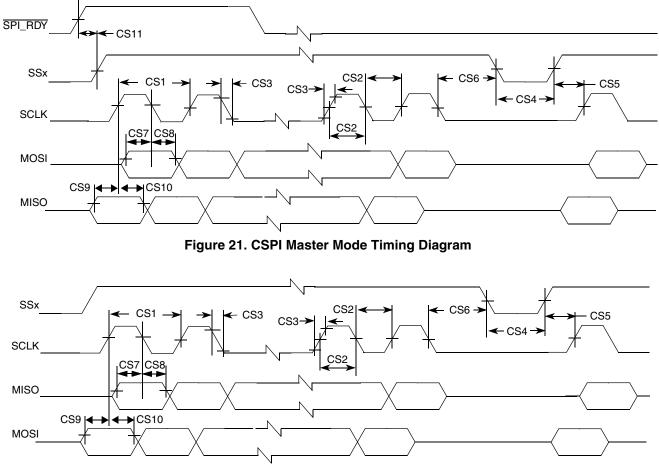

Figure 21 and Figure 22 depict the master mode and slave mode timings of CSPI, and Table 30 lists the timing parameters.

Figure 22. CSPI Slave Mode Timing Diagram

Figure 25. Write Data Latch Cycle Timing Dlagram

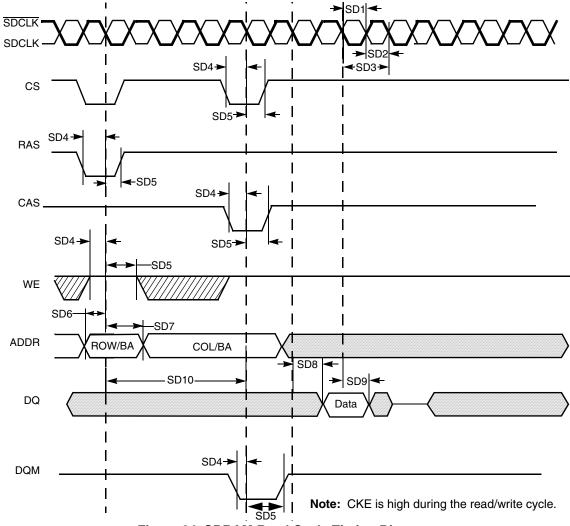

Figure 34. SDRAM Read Cycle Timing Diagram

| ID  | Parameter                             | Symbol | Min | Max  | Unit |

|-----|---------------------------------------|--------|-----|------|------|

| SD1 | SDRAM clock high-level width          | tCH    | 3.4 | 4.1  | ns   |

| SD2 | SDRAM clock low-level width           | tCL    | 3.4 | 4.1  | ns   |

| SD3 | SDRAM clock cycle time                | tCK    | 7.5 | —    | ns   |

| SD4 | CS, RAS, CAS, WE, DQM, CKE setup time | tCMS   | 2.0 | _    | ns   |

| SD5 | CS, RAS, CAS, WE, DQM, CKE hold time  | tCMH   | 1.8 | —    | ns   |

| SD6 | Address setup time                    | tAS    | 2.0 | —    | ns   |

| SD7 | Address hold time                     | tAH    | 1.8 | _    | ns   |

| SD8 | SDRAM access time                     | tAC    | _   | 6.47 | ns   |

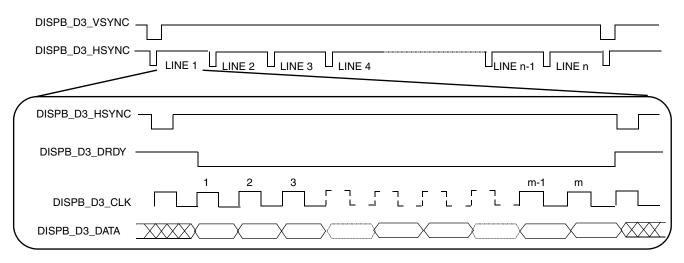

• DISPB\_D3\_DRDY acts like an output enable signal to the CRT display. This output enables the data to be shifted onto the display. When disabled, the data is invalid and the trace is off.

Figure 46. Interface Timing Diagram for TFT (Active Matrix) Panels

### 4.3.15.2.2 Interface to Active Matrix TFT LCD Panels, Electrical Characteristics

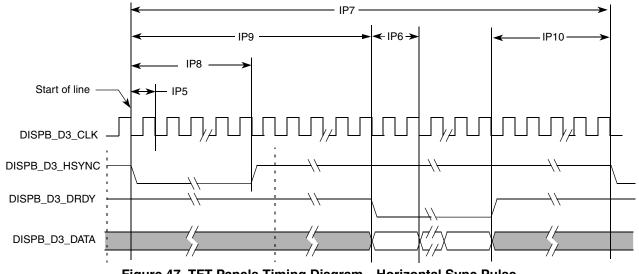

Figure 47 depicts the horizontal timing (timing of one line), including both the horizontal sync pulse and the data. All figure parameters shown are programmable. The timing images correspond to inverse polarity of the DISPB\_D3\_CLK signal and active-low polarity of the DISPB\_D3\_HSYNC, DISPB\_D3\_VSYNC and DISPB\_D3\_DRDY signals.

Figure 47. TFT Panels Timing Diagram—Horizontal Sync Pulse

Figure 48 depicts the vertical timing (timing of one frame). All figure parameters shown are programmable.

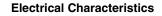

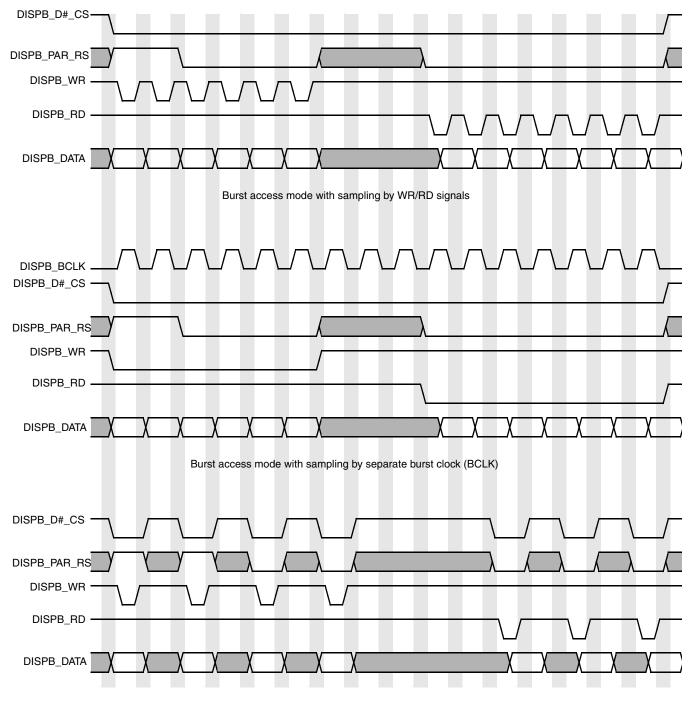

Single access mode (all control signals are not active for one display interface clock after each display access)

Single access mode (all control signals are not active for one display interface clock after each display access)

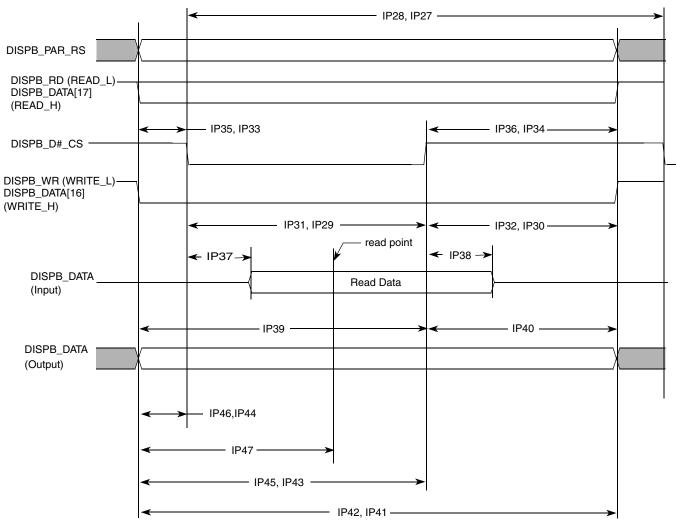

Figure 53. Asynchronous Parallel System 80 Interface (Type 2) Burst Mode Timing Diagram

Figure 57. Asynchronous Parallel System 80 Interface (Type 1) Timing Diagram

|                                                       | Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                             |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| DISPB_D#_CS -                                         | ← → 1 display IF<br>clock cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1 display IF                                |

| DISPB_SD_D_C<br>DISPB_SD_D <sup>-</sup><br>(Output) _ | CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ✓ D5 \ D4 \ D3 \ D2 \ D1 \ D0 ✓ Output data |

| DISPB_SD_D  _ (Input) _                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |

| DISPB_SER_RS -                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |

|                                                       | Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |

| DISPB_D#_CS -                                         | 1 display IF<br>clock cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1 display IF                                |

| DISPB_SD_D_C                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |

| DISPB_SD_D <sup>_</sup><br>(Output) _                 | ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ ∧ _ |                                             |

| DISPB_SD_D<br>(Input)                                 | D7 \ D6 \                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ( D5 ) D4 ) D3 ) D2 ) D1 ) D0               |

| DISPB_SER_RS                                          | <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Input data                                  |

Figure 63. 5-Wire Serial Interface (Type 1) Timing Diagram

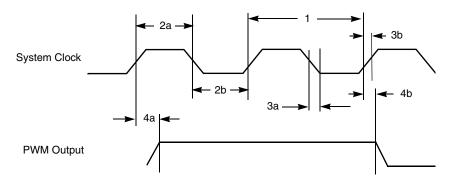

## 4.3.18.1 PWM Timing

Figure 71 depicts the timing of the PWM, and Table 55 lists the PWM timing characteristics.

### Figure 71. PWM Timing

| Table 55. F | PWM Outpu | t Timing | Parameters |

|-------------|-----------|----------|------------|

|-------------|-----------|----------|------------|

| ID | Parameter                         | Min   | Max     | Unit |

|----|-----------------------------------|-------|---------|------|

| 1  | System CLK frequency <sup>1</sup> | 0     | ipg_clk | MHz  |

| 2a | Clock high time                   | 12.29 | _       | ns   |

| 2b | Clock low time                    | 9.91  | _       | ns   |

| 3a | Clock fall time                   | —     | 0.5     | ns   |

| 3b | Clock rise time                   | —     | 0.5     | ns   |

| 4a | Output delay time                 | —     | 9.37    | ns   |

| 4b | Output setup time                 | 8.71  | _       | ns   |

<sup>1</sup> CL of PWMO = 30 pF

## 4.3.19 SDHC Electrical Specifications

This section describes the electrical information of the SDHC.

## 4.3.19.1 SDHC Timing

Figure 72 depicts the timings of the SDHC, and Table 56 lists the timing parameters.

| ID   | Parameter                     | All Freq | uencies | Unit |

|------|-------------------------------|----------|---------|------|

|      | Falancici                     | Min      | Max     | onit |

| SJ11 | TCK low to TDO high impedance | _        | 44      | ns   |

| SJ12 | TRST assert time              | 100      | _       | ns   |

| SJ13 | TRST set-up time to TCK low   | 40       | _       | ns   |

### Table 59. SJC Timing Parameters (continued)

<sup>1</sup> On cases where SDMA TAP is put in the chain, the max TCK frequency is limited by max ratio of 1:8 of SDMA core frequency to TCK limitation. This implies max frequency of 8.25 MHz (or 121.2 ns) for 66 MHz IPG clock.

$^{2}$  V<sub>M</sub> mid point voltage

## 4.3.22 SSI Electrical Specifications

This section describes the electrical information of SSI. Note the following pertaining to timing information:

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on AUDMUX signals when SSI is being used for data transfer.

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- For internal Frame Sync operation using external clock, the FS timing will be same as that of Tx Data (for example, during AC97 mode of operation).

## 4.3.22.1 SSI Transmitter Timing with Internal Clock

Figure 81 depicts the SSI transmitter timing with internal clock, and Table 60 lists the timing parameters.

| Signal | Ball Location |

|--------|---------------|

| NC     | N7            |

| NC     | P7            |

| NC     | U21           |

| Table 68. 19 x 19 BGA No Con | inects <sup>1</sup> |

|------------------------------|---------------------|

|------------------------------|---------------------|

<sup>1</sup> These contacts are not used and must be floated by the user.

## 5.2.3.2 BGA Signal ID by Ball Grid Location—19 x 19 0.8 mm

Table 69. 19 x 19 BGA Signal ID by Ball Grid Location

| Signal ID  | Ball Location |

|------------|---------------|

| A0         | Y6            |

| A1         | AC5           |

| A10        | V15           |

| A11        | AB3           |

| A12        | AA3           |

| A13        | Y3            |

| A14        | Y15           |

| A15        | Y14           |

| A16        | V14           |

| A17        | Y13           |

| A18        | V13           |

| A19        | Y12           |

| A2         | AB5           |

| A20        | V12           |

| A21        | Y11           |

| A22        | V11           |

| A23        | Y10           |

| A24        | Y9            |

| A25        | Y8            |

| A3         | AA5           |

| A4         | Y5            |

| A5         | AC4           |

| A6         | AB4           |

| A7         | AA4           |

| A8         | Y4            |

| A9         | AC3           |

| ATA_CS0    | E1            |

| ATA_CS1    | G4            |

| ATA_DIOR   | E3            |

| ATA_DIOW   | H6            |

| ATA_DMACK  | E2            |

| ATA_RESET  | F3            |

| BATT_LINE  | F6            |

| BCLK       | W20           |

| BOOT_MODE0 | F17           |

| BOOT_MODE1 | C21           |

| Signal ID     | Ball Location |

|---------------|---------------|

| CKIL          | E21           |

| CLKO          | C20           |

| CLKSS         | H17           |

| COMPARE       | A20           |

| CONTRAST      | N21           |

| CS0           | U17           |

| CS1           | Y22           |

| CS2           | Y18           |

| CS3           | Y19           |

| CS4           | Y20           |

| CS5           | AA21          |

| CSI_D10       | K21           |

| CSI_D11       | K22           |

| CSI_D12       | K23           |

| CSI_D13       | L20           |

| CSI_D14       | L18           |

| CSI_D15       | L21           |

| CSI_D4        | J20           |

| CSI_D5        | J21           |

| CSI_D6        | L17           |

| CSI_D7        | J22           |

| CSI_D8        | J23           |

| CSI_D9        | K20           |

| CSI_HSYNC     | H22           |

| CSI_MCLK      | H20           |

| CSI_PIXCLK    | H23           |

| CSI_VSYNC     | H21           |

| CSPI1_MISO    | N2            |

| CSPI1_MOSI    | N1            |

| CSPI1_SCLK    | M4            |

| CSPI1_SPI_RDY | M1            |

| CSPI1_SS0     | M2            |

| CSPI1_SS1     | N6            |

| CSPI1_SS2     | M3            |

| CSPI2_MISO    | B4            |

| CSPI2_MOSI    | D5            |

# 5.3 Ball Maps

## Table 70. Ball Map—14 x 14 0.5 mm Pitch

| ۸. | GND             | GND            | SFS5                  |           |               | USBOT                 |                |                      |                      | RXD1        | DSR_D        |              | RXD2         | CE_CO        |              |              | KEY_C        |              |             | SJC_M              | SVEN0          | CAPTU          | GPIO1_      |                | GND                  | GND                     |

|----|-----------------|----------------|-----------------------|-----------|---------------|-----------------------|----------------|----------------------|----------------------|-------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|-------------|--------------------|----------------|----------------|-------------|----------------|----------------------|-------------------------|

|    |                 |                |                       | _MISO     |               | A7                    | G_DAT<br>A3    |                      |                      |             | CE1          | TE1          |              | NTROL        |              | OW7          | OL3          | OL7          |             | OD                 |                | RE             | 6           | DOG_R<br>ST    |                      |                         |

| ;  | GND             | GND            | STXD4                 | SRXD<br>5 | CSPI2_<br>SS0 |                       |                | USBOT<br>G_DAT<br>A1 |                      | USB_P<br>WR | CTS1         | DCD_D<br>CE1 | DCD_D<br>TE1 | RTS2         | KEY_R<br>OW1 | KEY_R<br>OW5 | KEY_C<br>OL1 | KEY_C<br>OL5 | тск         | TRSTB              | SRX0           | SCLK0          | GPIO1_<br>1 | GPIO1_<br>5    | GND                  | GND                     |

|    | GND             | GND            | SRXD4                 | SCK4      | STXD5         | CSPI2_<br>SS1         | CSPI2_<br>SCLK | USBOT<br>G_DAT<br>A4 |                      |             | DTR_D<br>CE1 | DTR_D<br>TE1 | TXD2         |              | KEY_C<br>OL0 | KEY_C<br>OL4 | RTCK         | DE           | SRST0       |                    | BOOT_<br>MODE1 | BOOT_<br>MODE3 | CLKO        | GND            | GND                  | GND                     |

| ľ  | GND             | CSPI3_<br>MOSI | SCK5                  |           |               |                       |                |                      |                      |             |              |              |              |              |              |              |              |              |             |                    |                |                |             | BOOT_<br>MODE2 | GND                  | BOOT_<br>MODE           |

|    | CSPI3_<br>SCLK  | ATA_DI<br>OR   | CSPI2_<br>MOSI        |           | NVCC5         |                       |                |                      |                      |             |              |              |              |              |              |              |              |              |             |                    |                | GND            |             | GND            | DVFS0                | POWEI<br>_FAIL          |

|    | ATA_D<br>MACK   | ATA_C<br>S1    | SFS4                  |           |               | NVCC5                 |                | USBOT<br>G_DAT<br>A6 |                      | TXD1        | RI_DC<br>E1  | DTR_D<br>CE2 | KEY_R<br>OW0 |              | KEY_C<br>OL6 | TDI          | STX0         | GPIO1<br>_0  |             | BOOT_<br>MODE<br>0 | GND            |                |             | СКІН           | GPIO1_<br>3          | VSTBY                   |

| i  | PWMO            | PC_RW          | CSPI3_<br>MISO        |           |               | CSPI3_<br>SPI_R<br>DY | NVCC5          |                      | USBOT<br>G_DAT<br>A2 |             | RTS1         | RI_DT<br>E1  | CTS2         | KEY_R<br>OW4 | KEY_C<br>OL2 | TMS          | SIMPD<br>0   | COMP<br>ARE  | NVCC1       | -                  | NVCC1          |                |             | DVFS1          | VPG0                 | CLKSS                   |

| 1  | PC_RS<br>T      | PC_BV<br>D1    | ATA_R<br>ESET         |           |               | ATA_DI<br>OW          |                |                      |                      |             |              |              |              |              |              |              |              |              |             |                    | CKIL           |                |             | POR            | I2C_DA<br>T          | GPIO3 <u>.</u><br>1     |

| Ì  | PC_VS<br>1      |                | IOIS16                |           |               | -                     | PC_PO<br>E     |                      |                      | QVCC1       | QVCC1        | NVCC8        | NVCC8        | QVCC         | NVCC6        | NVCC6        | NVCC9        |              |             | VPG1               | RESET_         |                |             | I2C_CL<br>K    | CSI_VS<br>YNC        | CSI_PI<br>CLK           |

| ,  | PC_CD           |                | PC_PW<br>RON          |           |               | PC_BV<br>D2           | PC_VS<br>2     |                      | QVCC1                |             |              |              |              |              | NVCC6        |              |              | NVCC1        |             | CSI_H<br>SYNC      | GPIO3_<br>0    |                |             | CSI_MC<br>LK   |                      | CSI_D                   |

|    | SD1_D<br>ATA1   | SD1_C<br>MD    | SD1_D<br>ATA2         |           |               | PC_WA                 | PC_CD          |                      | NVCC3                |             | QVCC1        | GND          | QVCC         | QVCC         | QVCC         | QVCC         |              | NVCC4        | NVCC4       | CSI_D8             | CSI_D4         |                |             | CSI_D6         | CSI_D9               | CSI_D <sup>.</sup><br>1 |

| 1  | USBH2<br>_DATA0 | USBH2<br>_STP  | USBH2<br>_DATA1       |           |               | SD1_D<br>ATA0         | SD1_C<br>LK    |                      | NVCC3                |             | GND          | GND          | GND          | GND          | GND          | GND          |              | QVCC         |             | CSI_D1<br>4        | CSI_D1<br>2    |                |             | CSI_D1<br>0    | CSI_D1<br>3          | CSI_D <sup>·</sup><br>5 |

|    | USBH2<br>_CLK   | CSPI1_<br>SCLK | CSPI1_<br>SPI_RD<br>Y |           |               | USBH2<br>_NXT         | USBH2<br>_DIR  |                      | QVCC4                |             | NVCC3        | GND          | GND          | GND          | GND          | GND          |              | NVCC7        |             | SD_D_I             | FPSHIF<br>T    |                |             | VSYNC<br>0     | HSYNC                | DRDY0                   |

|    | CSPI1_<br>SS1   | CSPI1_<br>MOSI | CSPI1_<br>SS0         |           |               | CSPI1_<br>SS2         | CSPI1_<br>MISO |                      | NVCC1<br>0           |             | NVCC1<br>0   | GND          | GND          | GND          | GND          | GND          |              | NVCC7        |             | READ               | LCS1           |                |             |                | SD_D_I<br>O          | LCS0                    |

| 1  | STXD3           | SCK3           | SRXD3                 |           |               | SFS3                  | SRXD6          |                      | QVCC4                |             | NVCC1<br>0   | GND          | GND          | GND          | GND          | GND          |              | NVCC7        |             | D3_CL<br>S         | PAR_RS         |                |             | CONTR<br>AST   | WRITE                | VSYNC<br>3              |

| ·  | STXD6           | SCK6           | SFS6                  |           |               | NFCE                  | NFWE           |                      | QVCC4                |             | NVCC1<br>0   | GND          | GND          | SGND         | MGND         | UGND         |              | NVCC7        |             | LD4                | LD2            |                |             | LD0            | SER_R<br>S           | D3_RE                   |

|    | NFRB            | NFWP           | NFCLE                 |           |               | D15                   | D11            |                      | QVCC4                |             |              |              |              |              |              |              |              | QVCC         |             | TTM_P<br>AD        | LD8            |                |             | LD6            | D3_SPL               | LD1                     |

| -  | NFALE           |                | D13                   |           |               | -                     | D5             |                      |                      | QVCC        | QVCC         | QVCC         | QVCC         | SVCC         | MVCC         | UVCC         | GND          |              |             | LD17               | LD13           |                |             | LD10           | LD3                  | LD5                     |

|    | D14             |                | D7                    |           |               |                       | NVCC2<br>2     |                      |                      |             |              |              |              |              |              |              |              |              |             |                    | EB0            |                |             | LD15           | LD7                  | LD9                     |

|    | D10             |                | D1                    |           |               | D                     | NVCC2<br>2     | 2                    | 2                    | 2           | NVCC2<br>2   | 2            | 2            | 1            | 1            | 1            |              | NVCC2        |             |                    | NT             |                |             | EB1            | LD11                 | LD12                    |

|    | D6              | D4             | A4                    |           |               | NVCC2<br>2            | SD31           | SD28                 | SD27                 | SD23        | SD21         | SD18         | SD16         | SD13         | SD9          | SD7          | SD5          | SD3          | SD2         | DQM2               | SDCLK          |                |             | FVCC           | LD14                 | LD16                    |

|    | D2              | D0<br>GND      | A6<br>A11             |           | A2            |                       |                |                      |                      |             |              |              |              |              |              |              |              |              |             |                    |                | RW             |             | FGND<br>FUSE V | OE                   | BCLK<br>GND             |

|    | MA10<br>GND     |                |                       | A13       | A8            | A0                    | CDB AC         | SDQS3                | 8000                 | SD25        | SDQS2        | SD17         | SD15         | CD10         | 000          | SDQS0        | SD4          | SD0          | DQM1        | CAS                | SDCKE          | CS3            | ECB         | DD<br>GND      | M_REQ<br>UEST<br>GND | GND                     |

|    |                 | GND            | A12                   |           | _             | -                     |                |                      |                      |             |              |              |              |              | SD8          |              |              |              |             |                    | 0              |                |             |                |                      |                         |

|    | GND<br>GND      | GND<br>GND     | A7<br>A9              | A3<br>A5  | SDBA1<br>A1   | SD30<br>A25           | SD26<br>A24    |                      | SD22<br>A22          | SD20<br>A21 | SD19<br>A20  | SDQS1<br>A19 |              | SD11<br>A17  | SD10<br>A16  | SD6<br>A15   | SD1<br>A14   | DQM3<br>A10  | DQM0<br>RAS |                    | CS2<br>SDCKE   | LBA<br>CS5     | CS0<br>CS1  | GND<br>CS4     | GND<br>GND           | GND<br>GND              |

|    | 1               | 2              | 3                     | 4         | 5             | 6                     | 7              | 8                    | 9                    | 10          | 11           | 12           | 13           | 14           | 15           | 16           | 17           | 18           | 19          | 20                 | 1<br>21        | 22             | 23          | 24             | 25                   | 26                      |

Package Information and Pinout

N