#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

-XF

| Product Status                  | Obsolete                                                                  |

|---------------------------------|---------------------------------------------------------------------------|

| Core Processor                  | ARM1136JF-S                                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                            |

| Speed                           | 532MHz                                                                    |

| Co-Processors/DSP               | Multimedia; GPU, IPU, MPEG-4, VFP                                         |

| RAM Controllers                 | DDR                                                                       |

| Graphics Acceleration           | Yes                                                                       |

| Display & Interface Controllers | Keyboard, Keypad, LCD                                                     |

| Ethernet                        | -                                                                         |

| SATA                            | -                                                                         |

| USB                             | USB 2.0 (3)                                                               |

| Voltage - I/O                   | 1.8V, 2.0V, 2.5V, 2.7V, 3.0V                                              |

| Operating Temperature           | 0°C ~ 70°C (TA)                                                           |

| Security Features               | Random Number Generator, RTIC, Secure Fusebox, Secure JTAG, Secure Memory |

| Package / Case                  | 473-LFBGA                                                                 |

| Supplier Device Package         | 473-LFBGA (19x19)                                                         |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcimx31lvmn5c                |

|                                 |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Functional Description and Application Information

# 2.2 Module Inventory

Table 3 shows an alphabetical listing of the modules in the multimedia applications processor. For extended descriptions of the modules, see the reference manual. A cross-reference is provided to the electrical specifications and timing information for each module with external signal connections.

| Block<br>Mnemonic | Block Name                                           | Functional<br>Grouping       | Brief Description                                                                                                                                                                                                                                                                                | Section/<br>Page                         |

|-------------------|------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 1-Wire®           | 1-Wire Interface                                     | Connectivity<br>Peripheral   | The 1-Wire module provides bi-directional communication between the ARM11 core and external 1-Wire devices.                                                                                                                                                                                      | 4.3.4/26                                 |

| ATA               | Advanced<br>Technology (AT)<br>Attachment            | Connectivity<br>Peripheral   | The ATA block is an AT attachment host interface. It is designed to interface with IDE hard disc drives and ATAPI optical disc drives.                                                                                                                                                           | 4.3.5/27                                 |

| AUDMUX            | Digital Audio<br>Multiplexer                         | Multimedia<br>Peripheral     | The AUDMUX interconnections allow multiple, simultaneous audio/voice/data flows between the ports in point-to-point or point-to-multipoint configurations.                                                                                                                                       | 4.3.6/36                                 |

| CAMP              | Clock Amplifier<br>Module                            | Clock                        | The CAMP converts a square wave/sinusoidal input into a rail-to-rail square wave. The output of CAMP feeds the predivider.                                                                                                                                                                       | 4.3.3/25                                 |

| ССМ               | Clock Control<br>Module                              | Clock                        | The CCM provides clock, reset, and power management control for the MCIMX31.                                                                                                                                                                                                                     | —                                        |

| CSPI              | Configurable<br>Serial Peripheral<br>Interface (x 3) | Connectivity<br>Peripheral   | The CSPI is equipped with data FIFOs and is a master/slave configurable serial peripheral interface module, capable of interfacing to both SPI master and slave devices.                                                                                                                         | 4.3.7/36                                 |

| DPLL              | Digital Phase<br>Lock Loop                           | Clock                        | The DPLLs produce high-frequency on-chip clocks with low frequency and phase jitters.<br>Note: External clock sources provide the reference frequencies.                                                                                                                                         | 4.3.8/37                                 |

| ECT               | Embedded<br>Cross Trigger                            | Debug                        | The ECT is composed of three CTIs (Cross Trigger Interface) and one CTM (Cross Trigger Matrix—key in the multi-core and multi-peripheral debug strategy.                                                                                                                                         | _                                        |

| EMI               | External<br>Memory<br>Interface                      | Memory<br>Interface<br>(EMI) | The EMI includes<br>• Multi-Master Memory Interface (M3IF)<br>• Enhanced SDRAM Controller (ESDCTL)<br>• NAND Flash Controller (NFC)<br>• Wireless External Interface Module (WEIM)                                                                                                               | 4.3.9.3/46,<br>4.3.9.1/38,<br>4.3.9.2/41 |

| EPIT              | Enhanced<br>Periodic<br>Interrupt Timer              | Timer<br>Peripheral          | The EPIT is a 32-bit "set and forget" timer which starts counting after<br>the EPIT is enabled by software. It is capable of providing precise<br>interrupts at regular intervals with minimal processor intervention.                                                                           | _                                        |

| ETM               | Embedded<br>Trace Macrocell                          | Debug/Trace                  | The ETM (from ARM, Ltd.) supports real-time instruction and data tracing by way of ETM auxiliary I/O port.                                                                                                                                                                                       | 4.3.10/54                                |

| FIR               | Fast InfraRed<br>Interface                           | Connectivity<br>Peripheral   | This FIR is capable of establishing a 0.576 Mbit/s, 1.152 Mbit/s or 4 Mbit/s half duplex link via a LED and IR detector. It supports 0.576 Mbit/s, 1.152 Mbit/s medium infrared (MIR) physical layer protocol and 4Mbit/s fast infrared (FIR) physical layer protocol defined by IrDA, Rev. 1.4. | 4.3.11/55                                |

| Table 3. | Digital | and | Analog | Modules |

|----------|---------|-----|--------|---------|

| 14010 01 |         | ~   | /a.eg  |         |

### Functional Description and Application Information

| Block<br>Mnemonic | Block Name                                                                    | Functional<br>Grouping          | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Section/<br>Page |

|-------------------|-------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| SCC               | Security<br>Controller<br>Module                                              | Security                        | The SCC is a hardware component composed of two blocks—the Secure RAM module, and the Security Monitor. The Secure RAM provides a way of securely storing sensitive information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                |

| SDHC              | Secured Digital<br>Host Controller                                            | Connectivity<br>Peripheral      | The SDHC controls the MMC (MultiMediaCard), SD (Secure Digital) memory, and I/O cards by sending commands to cards and performing data accesses to and from the cards.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.3.19/89        |

| SDMA              | Smart Direct<br>Memory Access                                                 | System<br>Control<br>Peripheral | The SDMA controller maximizes the system's performance by relieving the ARM core of the task of bulk data transfer from memory to memory or between memory and on-chip peripherals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                |

| SIM               | Subscriber<br>Identification<br>Module                                        | Connectivity<br>Peripheral      | The SIM interfaces to an external Subscriber Identification Card. It is<br>an asynchronous serial interface adapted for Smart Card<br>communication for e-commerce applications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4.3.20/90        |

| SJC               | Secure JTAG<br>Controller                                                     | Debug                           | The SJC provides debug and test control with maximum security and provides a flexible architecture for future derivatives or future multi-cores architecture.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.3.21/94        |

| SSI               | Synchronous<br>Serial Interface                                               | Multimedia<br>Peripheral        | The SSI is a full-duplex, serial port that allows the device to<br>communicate with a variety of serial devices, such as standard<br>codecs, Digital Signal Processors (DSPs), microprocessors,<br>peripherals, and popular industry audio codecs that implement the<br>inter-IC sound bus standard (I2S) and Intel AC97 standard.                                                                                                                                                                                                                                                                                                                                    | 4.3.22/96        |

| UART              | Universal<br>Asynchronous<br>Receiver/Trans<br>mitter                         | Connectivity<br>Peripheral      | The UART provides serial communication capability with external devices through an RS-232 cable or through use of external circuitry that converts infrared signals to electrical signals (for reception) or transforms electrical signals to signals that drive an infrared LED (for transmission) to provide low speed IrDA compatibility.                                                                                                                                                                                                                                                                                                                          |                  |

| USB               | Universal Serial<br>Bus—<br>2 Host<br>Controllers and<br>1 OTG<br>(On-The-Go) | Connectivity<br>Peripherals     | <ul> <li>USB Host 1 is designed to support transceiverless connection to the on-board peripherals in Low Speed and Full Speed mode, and connection to the ULPI (UTMI+ Low-Pin Count) and Legacy Full Speed transceivers.</li> <li>USB Host 2 is designed to support transceiverless connection to the Cellular Modem Baseband Processor.</li> <li>The USB-OTG controller offers HS/FS/LS capabilities in Host mode and HS/FS in device mode. In Host mode, the controller supports direct connection of a FS/LS device (without external hub). In device (bypass) mode, the OTG port functions as gateway between the Host 1 Port and the OTG transceiver.</li> </ul> | 4.3.23/104       |

| WDOG              | Watchdog Timer<br>Module                                                      | Timer<br>Peripheral             | The WDOG module protects against system failures by providing a method for the system to recover from unexpected events or programming errors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |

| Ref. Num | Description                                                                                     | Symbol               | Minimum | Typical | Maximum | Units |

|----------|-------------------------------------------------------------------------------------------------|----------------------|---------|---------|---------|-------|

| 1        | eFuse Program Current. <sup>1</sup><br>Current to program one eFuse bit: efuse_pgm = 3.0 V      | I <sub>program</sub> | _       | 35      | 60      | mA    |

| 2        | eFuse Read Current <sup>2</sup><br>Current to read an 8-bit eFuse word<br>vdd_fusebox = 1.875 V | I <sub>read</sub>    | _       | 5       | 8       | mA    |

Table 11. Fusebox Supply Current Parameters

<sup>1</sup> The current I<sub>program</sub> is during program time (t<sub>program</sub>).

<sup>2</sup> The current I<sub>read</sub> is present for approximately 50 ns of the read access to the 8-bit word, and only applies to Silicon Rev. 1.2 and previous.

# 4.1.1 Supply Current Specifications

Table 12 shows the core current consumption for 0°C to 70°C for Silicon Revision 1.2 and previous for the MCIMX31.

| Mode               | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | /CC<br>oheral) |      | CC1<br>RM) | QVCC4<br>(L2) |     |      |     | + UVCC | Unit |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------|------|------------|---------------|-----|------|-----|--------|------|

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Тур  | Max            | Тур  | Max        | Тур           | Max | Тур  | Max |        |      |

| State<br>Retention | <ul> <li>QVCC and QVCC1 = 0.95 V</li> <li>L2 caches are power gated (QVCC4 = 0 V)</li> <li>All PLLs are off, VCC = 1.4 V</li> <li>ARM is in well bias</li> <li>FPM is off</li> <li>32 kHz input is on</li> <li>CKIH input is off</li> <li>CAMP is off</li> <li>TCK input is off</li> <li>All modules are off</li> <li>No external resistive loads</li> <li>RNGA oscillator is off</li> </ul>                                                                                                                                         | 0.80 |                | 0.50 | _          |               |     | 0.04 |     | mA     |      |

| Wait               | <ul> <li>QVCC, QVCC1, and QVCC4 = 1.22 V</li> <li>ARM is in wait for interrupt mode</li> <li>MAX is active</li> <li>L2 cache is stopped but powered</li> <li>MCU PLL is on (532 MHz), VCC = 1.4 V</li> <li>USB PLL and SPLL are off, VCC = 1.4 V</li> <li>FPM is on</li> <li>CKIH input is on</li> <li>CAMP is on</li> <li>32 kHz input is on</li> <li>All clocks are gated off</li> <li>All modules are off<br/>(by programming CGR[2:0] registers)</li> <li>RNGA oscillator is off</li> <li>No external resistive loads</li> </ul> | 6.00 | _              | 3.00 | _          | 0.04          | _   | 3.50 |     | mA     |      |

| Table 12. Current Consumption for 0°C to 70°C <sup>1, 2</sup> for Silicon Revision 1.2 ar | nd Previous |

|-------------------------------------------------------------------------------------------|-------------|

|-------------------------------------------------------------------------------------------|-------------|

<sup>1</sup> Typical column: TA =  $25^{\circ}$ C

<sup>2</sup> Maximum column:  $TA = 70^{\circ}C$

### Table 14 shows the core current consumption for 0°C to 70°C for Silicon Revision 2.0 for the MCIMX31.

| Mode               | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | QVCC<br>(Peripheral) |       | QVCC1<br>(ARM) |       | QVCC4<br>(L2) |      | FVCC, +MVCC,<br>+SVCC, +UVCC<br>(PLL) |      | Unit |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------|----------------|-------|---------------|------|---------------------------------------|------|------|

|                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Тур                  | Мах   | Тур            | Мах   | Тур           | Max  | Тур                                   | Max  |      |

| Deep<br>Sleep      | <ul> <li>QVCC = 0.95 V</li> <li>ARM and L2 caches are power gated<br/>(QVCC1 2= QVCC4 = 0 V)</li> <li>All PLLs are off, VCC = 1.4 V</li> <li>ARM is in well bias</li> <li>FPM is off</li> <li>32 kHz input is on</li> <li>CKIH input is off</li> <li>CAMP is off</li> <li>TCK input is off</li> <li>All modules are off</li> <li>No external resistive loads</li> <li>RNGA oscillator is off</li> </ul>                                                                                                                              | 0.16                 | 2.50  |                |       |               |      | 0.02                                  | 0.10 | mA   |

| State<br>Retention | <ul> <li>QVCC and QVCC1 = 0.95 V</li> <li>L2 caches are power gated (QVCC4 = 0 V)</li> <li>All PLLs are off, VCC = 1.4 V</li> <li>ARM is in well bias</li> <li>FPM is off</li> <li>32 kHz input is on</li> <li>CKIH input is off</li> <li>CAMP is off</li> <li>TCK input is off</li> <li>All modules are off</li> <li>No external resistive loads</li> <li>RNGA oscillator is off</li> </ul>                                                                                                                                         | 0.16                 | 2.50  | 0.07           | 1.60  |               |      | 0.02                                  | 0.10 | mA   |

| Wait               | <ul> <li>QVCC, QVCC1, and QVCC4 = 1.22 V</li> <li>ARM is in wait for interrupt mode</li> <li>MAX is active</li> <li>L2 cache is stopped but powered</li> <li>MCU PLL is on (532 MHz), VCC = 1.4 V</li> <li>USB PLL and SPLL are off, VCC = 1.4 V</li> <li>FPM is on</li> <li>CKIH input is on</li> <li>CAMP is on</li> <li>32 kHz input is on</li> <li>All clocks are gated off</li> <li>All modules are off<br/>(by programming CGR[2:0] registers)</li> <li>RNGA oscillator is off</li> <li>No external resistive loads</li> </ul> | 6.00                 | 13.00 | 2.20           | 16.00 | 0.03          | 0.17 | 3.60                                  | 4.40 | mA   |

## Table 14. Current Consumption for 0°C to 70°C<sup>1, 2</sup> for Silicon Revision 2.0

<sup>1</sup> Typical column: TA =  $25^{\circ}$ C

<sup>2</sup> Maximum column:  $TA = 70^{\circ}C$

# 4.2 Supply Power-Up/Power-Down Requirements and Restrictions

Any MCIMX31 board design must comply with the power-up and power-down sequence guidelines as described in this section to guarantee reliable operation of the device. Any deviation from these sequences may result in any or all of the following situations:

- Cause excessive current during power up phase

- Prevent the device from booting

- Cause irreversible damage to the MCIMX31 (worst-case scenario)

# 4.2.1 Powering Up

The Power On Reset ( $\overline{POR}$ ) pin must be kept asserted (low) throughout the power up sequence. Power up logic must guarantee that all power sources reach their target values prior to the release (de-assertion) of  $\overline{POR}$ . Figure 2 shows the power-up sequence for silicon Revisions 1.2 and previous. Figure 3 and Figure 4 show the power-up sequence for silicon Revision 2.0.

### NOTE

Stages need to be performed in the order shown; however, *within* each stage, supplies can be powered up in any order. For example, supplies IOQVDD, NVCC1, and NVCC3 through NVCC10 do not need to be powered up in the order shown.

### CAUTION

NVCC6 and NVCC9 must be at the same voltage potential. These supplies are connected together on-chip to optimize ESD damage immunity.

# 4.3.4 1-Wire Electrical Specifications

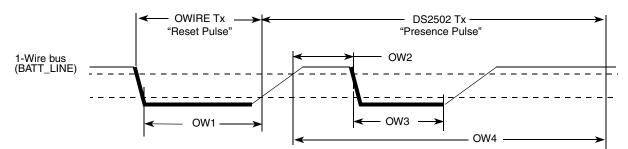

Figure 7 depicts the RPP timing, and Table 21 lists the RPP timing parameters.

Figure 7. Reset and Presence Pulses (RPP) Timing Diagram

| ID  | Parameters           | Symbol            | Min | Тур | Max | Units |

|-----|----------------------|-------------------|-----|-----|-----|-------|

| OW1 | Reset Time Low       | t <sub>RSTL</sub> | 480 | 511 | _   | μs    |

| OW2 | Presence Detect High | t <sub>PDH</sub>  | 15  |     | 60  | μs    |

| OW3 | Presence Detect Low  | t <sub>PDL</sub>  | 60  | _   | 240 | μs    |

| OW4 | Reset Time High      | t <sub>RSTH</sub> | 480 | 512 | _   | μs    |

Table 21. RPP Sequence Delay Comparisons Timing Parameters

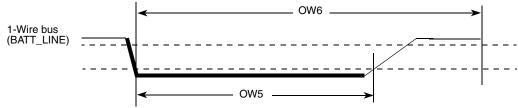

Figure 8 depicts Write 0 Sequence timing, and Table 22 lists the timing parameters.

Figure 8. Write 0 Sequence Timing Diagram

Table 22. WR0 Sequence Timing Parameters

| ID  | Parameter                 | Symbol               | Min | Тур | Max | Units |

|-----|---------------------------|----------------------|-----|-----|-----|-------|

| OW5 | Write 0 Low Time          | t <sub>WR0_low</sub> | 60  | 100 | 120 | μs    |

| OW6 | N6 Transmission Time Slot |                      | OW5 | 117 | 120 | μs    |

Figure 9 depicts Write 1 Sequence timing, Figure 10 depicts the Read Sequence timing, and Table 23 lists the timing parameters.

# 4.3.5.2 PIO Mode Timing

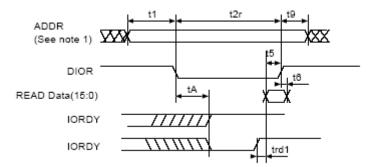

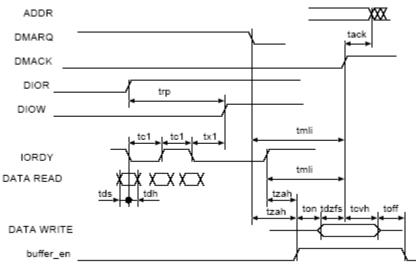

Figure 11 shows timing for PIO read, and Table 25 lists the timing parameters for PIO read.

Figure 11. PIO Read Timing Diagram

| Table 25. PIO Read Timing Parameters |       |                                                                                                                                                                                                               |                                |  |  |  |

|--------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|--|

| ATA<br>Parameter                     | Value |                                                                                                                                                                                                               |                                |  |  |  |

| t1                                   | t1    | t1 (min) = time_1 * T - (tskew1 + tskew2 + tskew5)                                                                                                                                                            | time_1                         |  |  |  |

| t2                                   | t2r   | t2 min) = time_2r * T - (tskew1 + tskew2 + tskew5)                                                                                                                                                            | time_2r                        |  |  |  |

| t9                                   | t9    | t9 (min) = time_9 * T - (tskew1 + tskew2 + tskew6)                                                                                                                                                            | time_3                         |  |  |  |

| t5                                   | t5    | t5 (min) = tco + tsu + tbuf + tbuf + tcable1 + tcable2                                                                                                                                                        | If not met, increase<br>time_2 |  |  |  |

| t6                                   | t6    | 0                                                                                                                                                                                                             | —                              |  |  |  |

| tA                                   | tA    | $tA (min) = (1.5 + time_ax) * T - (tco + tsui + tcable2 + tcable2 + 2*tbuf)$                                                                                                                                  | time_ax                        |  |  |  |

| trd                                  | trd1  | $\label{eq:trd1} \begin{array}{l} (max) = (-trd) + (tskew3 + tskew4) \\ trd1 \ (min) = (time\_pio\_rdx - 0.5)^{*}T - (tsu + thi) \\ (time\_pio\_rdx - 0.5) \ ^{*}T > tsu + thi + tskew3 + tskew4 \end{array}$ | time_pio_rdx                   |  |  |  |

| tO                                   | —     | t0 (min) = (time_1 + time_2 + time_9) * T                                                                                                                                                                     | time_1, time_2r, time_9        |  |  |  |

Figure 12 shows timing for PIO write, and Table 26 lists the timing parameters for PIO write.

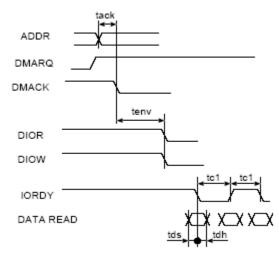

# 4.3.5.3 UDMA In Timing

Figure 15 shows timing when the UDMA in transfer starts, Figure 16 shows timing when the UDMA in host terminates transfer, Figure 17 shows timing when the UDMA in device terminates transfer, and Table 28 lists the timing parameters for UDMA in burst.

Figure 15. UDMA In Transfer Starts Timing Diagram

Figure 16. UDMA In Host Terminates Transfer Timing Diagram

# 4.3.6 AUDMUX Electrical Specifications

The AUDMUX provides a programmable interconnect logic for voice, audio and data routing between internal serial interfaces (SSI) and external serial interfaces (audio and voice codecs). The AC timing of AUDMUX external pins is hence governed by the SSI module. Please refer to their respective electrical specifications.

# 4.3.7 CSPI Electrical Specifications

This section describes the electrical information of the CSPI.

# 4.3.7.1 CSPI Timing

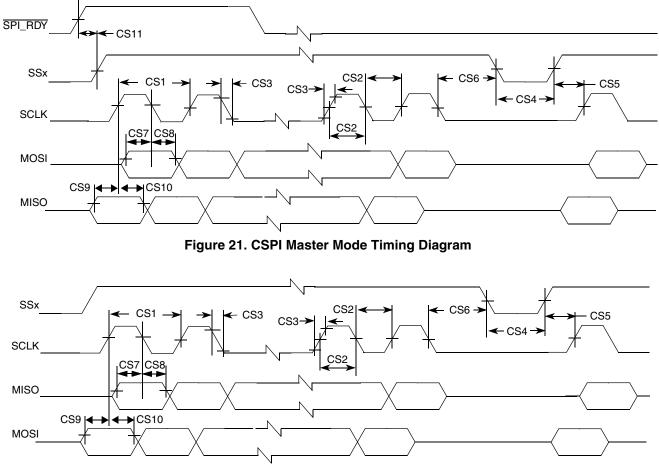

Figure 21 and Figure 22 depict the master mode and slave mode timings of CSPI, and Table 30 lists the timing parameters.

Figure 22. CSPI Slave Mode Timing Diagram

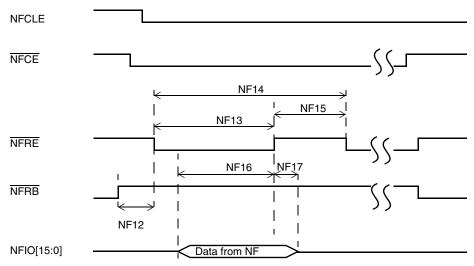

Figure 26. Read Data Latch Cycle Timing Dlagram

| ID   | Parameter           | Symbol | Timing<br>T = NFC Clock Cycle <sup>2</sup> |        | Example Tir<br>NFC Clock ≈<br>T = 30 | 33 MHz | Unit |

|------|---------------------|--------|--------------------------------------------|--------|--------------------------------------|--------|------|

|      |                     |        | Min                                        | Max    | Min                                  | Мах    |      |

| NF1  | NFCLE Setup Time    | tCLS   | T–1.0 ns                                   | _      | 29                                   | _      | ns   |

| NF2  | NFCLE Hold Time     | tCLH   | T–2.0 ns                                   | _      | 28                                   | _      | ns   |

| NF3  | NFCE Setup Time     | tCS    | T–1.0 ns                                   |        | 29                                   | _      | ns   |

| NF4  | NFCE Hold Time      | tCH    | T–2.0 ns                                   | _      | 28                                   | _      | ns   |

| NF5  | NF_WP Pulse Width   | tWP    | T–1.5 ns                                   |        | 28.5                                 |        | ns   |

| NF6  | NFALE Setup Time    | tALS   | Т                                          | _      | 30                                   | _      | ns   |

| NF7  | NFALE Hold Time     | tALH   | T–3.0 ns                                   | _      | 27                                   | _      | ns   |

| NF8  | Data Setup Time     | tDS    | Т                                          | _      | 30                                   | _      | ns   |

| NF9  | Data Hold Time      | tDH    | T–5.0 ns                                   | _      | 25                                   | _      | ns   |

| NF10 | Write Cycle Time    | tWC    |                                            | 2T     | 60                                   |        | ns   |

| NF11 | NFWE Hold Time      | tWH    | T–2                                        | 2.5 ns | 27.5                                 |        | ns   |

| NF12 | Ready to NFRE Low   | tRR    | 6T                                         | _      | 180                                  | _      | ns   |

| NF13 | NFRE Pulse Width    | tRP    | 1.5T                                       | _      | 45                                   | _      | ns   |

| NF14 | READ Cycle Time     | tRC    | 2T                                         |        | 60                                   | _      | ns   |

| NF15 | NFRE High Hold Time | tREH   | 0.5T–2.5 ns                                |        | 12.5                                 | _      | ns   |

| NF16 | Data Setup on READ  | tDSR   | N/A                                        |        | 10                                   | —      | ns   |

| NF17 | Data Hold on READ   | tDHR   | 1                                          | N/A    | 0                                    | _      | ns   |

| Table 32. NFC | Timing | Parameters <sup>1</sup> |

|---------------|--------|-------------------------|

|---------------|--------|-------------------------|

<sup>1</sup> The flash clock maximum frequency is 50 MHz.

<sup>2</sup> Subject to DPLL jitter specification on Table 31, "DPLL Specifications," on page 37.

MCIMX31/MCIMX31L Technical Data, Rev. 4.1

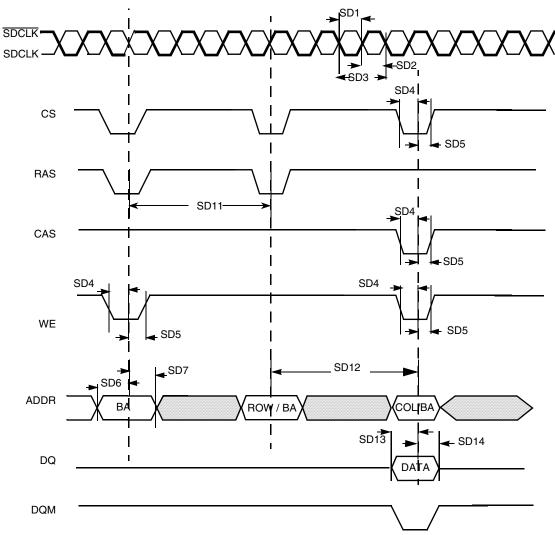

Figure 35. SDR SDRAM Write Cycle Timing Diagram

| ID   | Parameter                                       | Symbol | Min | Max | Unit  |

|------|-------------------------------------------------|--------|-----|-----|-------|

| SD1  | SDRAM clock high-level width                    | tCH    | 3.4 | 4.1 | ns    |

| SD2  | SDRAM clock low-level width                     | tCL    | 3.4 | 4.1 | ns    |

| SD3  | SDRAM clock cycle time                          | tCK    | 7.5 | —   | ns    |

| SD4  | CS, RAS, CAS, WE, DQM, CKE setup time           | tCMS   | 2.0 | —   | ns    |

| SD5  | CS, RAS, CAS, WE, DQM, CKE hold time            | tCMH   | 1.8 | —   | ns    |

| SD6  | Address setup time                              | tAS    | 2.0 | —   | ns    |

| SD7  | Address hold time                               | tAH    | 1.8 | —   | ns    |

| SD11 | Precharge cycle period <sup>1</sup>             | tRP    | 1   | 4   | clock |

| SD12 | Active to read/write command delay <sup>1</sup> | tRCD   | 1   | 8   | clock |

# 4.3.14 IPU—Sensor Interfaces

## 4.3.14.1 Supported Camera Sensors

Table 44 lists the known supported camera sensors at the time of publication.

| Vendor                 | Model                                                                                                                         |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Conexant               | CX11646, CX20490 <sup>2</sup> , CX20450 <sup>2</sup>                                                                          |  |

| Agilant                | HDCP-2010, ADCS-1021 <sup>2</sup> , ADCS-1021 <sup>2</sup>                                                                    |  |

| Toshiba                | TC90A70                                                                                                                       |  |

| ICMedia                | ICM202A, ICM102 <sup>2</sup>                                                                                                  |  |

| iMagic                 | IM8801                                                                                                                        |  |

| Transchip              | TC5600, TC5600J, TC5640, TC5700, TC6000                                                                                       |  |

| Fujitsu                | MB86S02A                                                                                                                      |  |

| Micron                 | MI-SOC-0133                                                                                                                   |  |

| Matsushita             | MN39980                                                                                                                       |  |

| STMicro                | W6411, W6500, W6501 <sup>2</sup> , W6600 <sup>2</sup> , W6552 <sup>2</sup> , STV0974 <sup>2</sup>                             |  |

| OmniVision             | OV7620, OV6630                                                                                                                |  |

| Sharp                  | LZ0P3714 (CCD)                                                                                                                |  |

| Motorola               | MC30300 (Python) <sup>2</sup> , SCM20014 <sup>2</sup> , SCM20114 <sup>2</sup> , SCM22114 <sup>2</sup> , SCM20027 <sup>2</sup> |  |

| National Semiconductor | LM9618 <sup>2</sup>                                                                                                           |  |

### Table 44. Supported Camera Sensors<sup>1</sup>

<sup>1</sup> Freescale Semiconductor does not recommend one supplier over another and in no way suggests that these are the only camera suppliers.

<sup>2</sup> These sensors not validated at time of publication.

# 4.3.14.2 Functional Description

There are three timing modes supported by the IPU.

### 4.3.14.2.1 Pseudo BT.656 Video Mode

Smart camera sensors, which include imaging processing, usually support video mode transfer. They use an embedded timing syntax to replace the SENSB\_VSYNC and SENSB\_HSYNC signals. The timing syntax is defined by the BT.656 standard.

This operation mode follows the recommendations of ITU BT.656 specifications. The only control signal used is SENSB\_PIX\_CLK. Start-of-frame and active-line signals are embedded in the data stream. An active line starts with a SAV code and ends with a EAV code. In some cases, digital blanking is inserted in between EAV and SAV code. The CSI decodes and filters out the timing-coding from the data stream, thus recovering SENSB\_VSYNC and SENSB\_HSYNC signals for internal use.

| ID   | Parameter                 | Symbol | Value                    | Units |

|------|---------------------------|--------|--------------------------|-------|

| IP21 | SPL rise time             | Tsplr  | (BGXP – 1) * Tdpcp       | ns    |

| IP22 | CLS rise time             | Tclsr  | CLS_RISE_DELAY * Tdpcp   | ns    |

| IP23 | CLS fall time             | Tclsf  | CLS_FALL_DELAY * Tdpcp   | ns    |

| IP24 | CLS rise and PS fall time | Tpsf   | PS_FALL_DELAY * Tdpcp    | ns    |

| IP25 | PS rise time              | Tpsr   | PS_RISE_DELAY * Tdpcp    | ns    |

| IP26 | REV toggle time           | Trev   | REV_TOGGLE_DELAY * Tdpcp | ns    |

### Table 49. Sharp Synchronous Display Interface Timing Parameters—Pixel Level

## 4.3.15.4 Synchronous Interface to Dual-Port Smart Displays

Functionality and electrical characteristics of the synchronous interface to dual-port smart displays are identical to parameters of the synchronous interface. See Section 4.3.15.2.2, "Interface to Active Matrix TFT LCD Panels, Electrical Characteristics."

### 4.3.15.4.1 Interface to a TV Encoder, Functional Description

The interface has an 8-bit data bus, transferring a single 8-bit value (Y/U/V) in each cycle. The bits D7–D0 of the value are mapped to bits LD17–LD10 of the data bus, respectively. Figure 51 depicts the interface timing,

- The frequency of the clock DISPB\_D3\_CLK is 27 MHz (within 10%).

- The DISPB\_D3\_HSYNC, DISPB\_D3\_VSYNC and DISPB\_D3\_DRDY signals are active low.

- The transition to the next row is marked by the negative edge of the DISPB\_D3\_HSYNC signal. It remains low for a single clock cycle.

- The transition to the next field/frame is marked by the negative edge of the DISPB\_D3\_VSYNC signal. It remains low for at least one clock cycle.

- At a transition to an odd field (of the next frame), the negative edges of DISPB\_D3\_VSYNC and DISPB\_D3\_HSYNC coincide.

- At a transition to an even field (of the same frame), they do not coincide.

- The active intervals—during which data is transferred—are marked by the DISPB\_D3\_HSYNC signal being high.

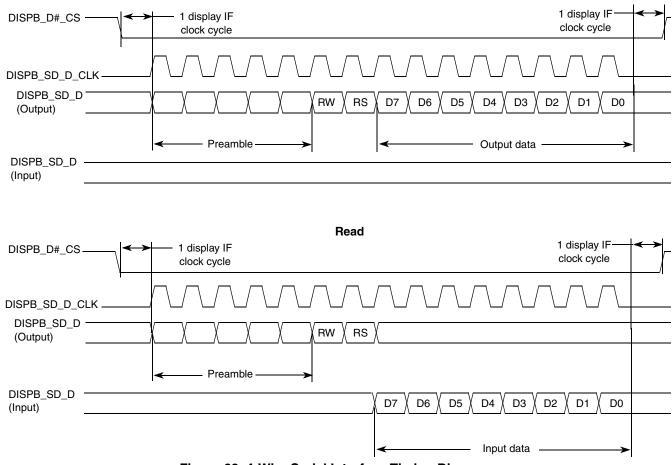

Figure 62. 4-Wire Serial Interface Timing Diagram

Figure 63 depicts timing of the 5-wire serial interface (Type 1). For this interface, a separate RS line is added. When a burst is transmitted within single active chip select interval, the RS can be changed at boundaries of words.

| ID   | Parameter                                | Symbol | Min.                 | Typ. <sup>1</sup> | Max.                                              | Units |

|------|------------------------------------------|--------|----------------------|-------------------|---------------------------------------------------|-------|

| IP56 | Controls setup time for write            | Tdcsw  | Tdicuw–1.5           | Tdicuw            | —                                                 | ns    |

| IP57 | Controls hold time for write             | Tdchw  | Tdicpw-Tdicdw-1.5    | Tdicpw-Tdicdw     | —                                                 | ns    |

| IP58 | Slave device data delay <sup>8</sup>     | Tracc  | 0                    | —                 | Tdrp <sup>9</sup> –Tlbd <sup>10</sup> –Tdicur–1.5 | ns    |

| IP59 | Slave device data hold time <sup>8</sup> | Troh   | Tdrp-Tlbd-Tdicdr+1.5 | —                 | Tdicpr-Tdicdr-1.5                                 | ns    |

| IP60 | Write data setup time                    | Tds    | Tdicdw-1.5           | Tdicdw            | —                                                 | ns    |

| IP61 | Write data hold time                     | Tdh    | Tdicpw-Tdicdw-1.5    | Tdicpw-Tdicdw     | —                                                 | ns    |

| IP62 | Read period <sup>2</sup>                 | Tdicpr | Tdicpr–1.5           | Tdicpr            | Tdicpr+1.5                                        | ns    |

| IP63 | Write period <sup>3</sup>                | Tdicpw | Tdicpw-1.5           | Tdicpw            | Tdicpw+1.5                                        | ns    |

| IP64 | Read down time <sup>4</sup>              | Tdicdr | Tdicdr-1.5           | Tdicdr            | Tdicdr+1.5                                        | ns    |

| IP65 | Read up time <sup>5</sup>                | Tdicur | Tdicur–1.5           | Tdicur            | Tdicur+1.5                                        | ns    |

| IP66 | Write down time <sup>6</sup>             | Tdicdw | Tdicdw-1.5           | Tdicdw            | Tdicdw+1.5                                        | ns    |

| IP67 | Write up time <sup>7</sup>               | Tdicuw | Tdicuw-1.5           | Tdicuw            | Tdicuw+1.5                                        | ns    |

| IP68 | Read time point <sup>9</sup>             | Tdrp   | Tdrp-1.5             | Tdrp              | Tdrp+1.5                                          | ns    |

Table 51. Asynchronous Serial Interface Timing Parameters—Access Level (continued)

<sup>1</sup> The exact conditions have not been finalized, but will likely match the current customer requirement for their specific display. These conditions may be device specific.

<sup>2</sup> Display interface clock period value for read:

$Tdicpr = T_{HSP\_CLK} \cdot ceil \left[ \frac{DISP\#\_IF\_CLK\_PER\_RD}{HSP\_CLK\_PERIOD} \right]$

<sup>3</sup> Display interface clock period value for write:

$Tdicpw = T_{HSP\_CLK} \cdot ceil \left[ \frac{DISP\#\_IF\_CLK\_PER\_WR}{HSP\_CLK\_PERIOD} \right]$

<sup>4</sup> Display interface clock down time for read:

$Tdicdr = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_DOWN\_RD}{HSP\_CLK\_PERIOD}\right]$

<sup>5</sup> Display interface clock up time for read:

$Tdicur = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_UP\_RD}{HSP\_CLK\_PERIOD}\right]$

<sup>6</sup> Display interface clock down time for write:

$$\begin{bmatrix} \text{dicdw} &= \frac{1}{2} \text{T}_{\text{HSP}\_\text{CLK}} \cdot \text{ceil} \begin{bmatrix} \frac{2 \cdot \text{DISP}\#\_\text{IF}\_\text{CLK}\_\text{DOWN}\_\text{WR}}{\text{HSP}\_\text{CLK}\_\text{PERIOD}} \end{bmatrix}$$

<sup>7</sup> Display interface clock up time for write:

- <sup>8</sup> This parameter is a requirement to the display connected to the IPU.

- <sup>9</sup> Data read point:

$drp = T_{HSP_CLK} \cdot ceil \left[ \frac{DISP\#_READ_EN}{HSP_CLK_PERIOD} \right]$

<sup>10</sup> Loopback delay Tlbd is the cumulative propagation delay of read controls and read data. It includes an IPU output delay, a device-level output delay, board delays, a device-level input delay, an IPU input delay. This value is device specific.

Figure 68. Transfer Operation Timing Diagram (Parallel)

NOTE

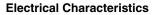

The Memory Stick Host Controller is designed to meet the timing requirements per Sony's *Memory Stick Pro Format Specifications* document. Tables in this section details the specifications requirements for parallel and serial modes, and not the MCIMX31 timing.

| Cinnal    | Parameter         | Cumhal  | Stand | Standards |      |  |

|-----------|-------------------|---------|-------|-----------|------|--|

| Signal    | Parameter         | Symbol  | Min.  | Max.      | Unit |  |

|           | Cycle             | tSCLKc  | 50    | _         | ns   |  |

|           | H pulse length    | tSCLKwh | 15    | _         | ns   |  |

| MSHC_SCLK | L pulse length    | tSCLKwl | 15    | _         | ns   |  |

|           | Rise time         | tSCLKr  | —     | 10        | ns   |  |

|           | Fall time         | tSCLKf  | _     | 10        | ns   |  |

|           | Setup time        | tBSsu   | 5     |           | ns   |  |

| MSHC_BS   | Hold time         | tBSh    | 5     | _         | ns   |  |

|           | Setup time        | tDsu    | 5     | _         | ns   |  |

| MSHC_DATA | Hold time         | tDh     | 5     | _         | ns   |  |

|           | Output delay time | tDd     | —     | 15        | ns   |  |

| Table 52. S | Serial Interface | Timing | Parameters <sup>1</sup> |

|-------------|------------------|--------|-------------------------|

|-------------|------------------|--------|-------------------------|

<sup>1</sup> Timing is guaranteed for NVCC from 2.7 through 3.1 V and up to a maximum overdrive NVCC of 3.3 V. See NVCC restrictions described in Table 8, "Operating Ranges," on page 13.

#### MCIMX31/MCIMX31L Technical Data, Rev. 4.1

| Circal    | Parameter         | Cumbal  | Stand | Standards |      |  |

|-----------|-------------------|---------|-------|-----------|------|--|

| Signal    | Parameter Symbol  |         | Min   | Мах       | Unit |  |

|           | Cycle             | tSCLKc  | 25    | _         | ns   |  |

|           | H pulse length    | tSCLKwh | 5     | _         | ns   |  |

| MSHC_SCLK | L pulse length    | tSCLKwl | 5     |           | ns   |  |

|           | Rise time         | tSCLKr  | —     | 10        | ns   |  |

|           | Fall time         | tSCLKf  | _     | 10        | ns   |  |

|           | Setup time        | tBSsu   | 8     | _         | ns   |  |

| MSHC_BS   | Hold time         | tBSh    | 1     | _         | ns   |  |

|           | Setup time        | tDsu    | 8     |           | ns   |  |

| MSHC_DATA | Hold time         | tDh     | 1     |           | ns   |  |

|           | Output delay time | tDd     | _     | 15        | ns   |  |

Table 53. Parallel Interface Timing Parameters<sup>1</sup>

<sup>1</sup> Timing is guaranteed for NVCC from 2.7 through 3.1 V and up to a maximum overdrive NVCC of 3.3 V. See NVCC restrictions described in Table 8, "Operating Ranges," on page 13.

# 4.3.17 Personal Computer Memory Card International Association (PCMCIA)

Figure 69 and Figure 70 depict the timings pertaining to the PCMCIA module, each of which is an example of one clock of strobe set-up time and one clock of strobe hold time. Table 54 lists the timing parameters.

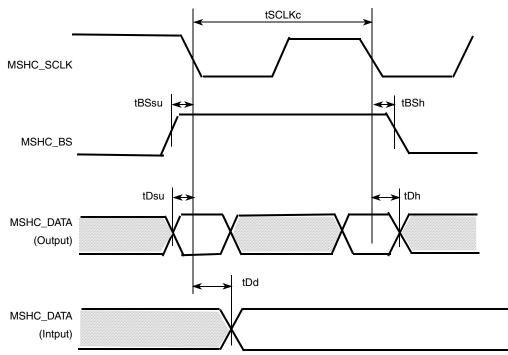

#### 4.3.20.3 **Power Down Sequence**

Power down sequence for SIM interface is as follows:

- 1. SIMPD port detects the removal of the SIM Card

- 2. RST goes Low

- 3. CLK goes Low

- 4. TX goes Low

- 5. VEN goes Low

Each of this steps is done in one CKIL period (usually 32 kHz). Power down can be started because of a SIM Card removal detection or launched by the processor. Figure 76 and Table 58 show the usual timing requirements for this sequence, with Fckil = CKIL frequency value.

| Table 58. Timing Red | quirements for Power | Down Sequence |

|----------------------|----------------------|---------------|

|----------------------|----------------------|---------------|

| Num | Description                          | Symbol               | Min         | Мах | Unit |

|-----|--------------------------------------|----------------------|-------------|-----|------|

| 1   | SIM reset to SIM clock stop          | S <sub>rst2clk</sub> | 0.9*1/FCKIL | 0.8 | μs   |

| 2   | SIM reset to SIM TX data low         | S <sub>rst2dat</sub> | 1.8*1/FCKIL | 1.2 | μs   |

| 3   | SIM reset to SIM Voltage Enable Low  | S <sub>rst2ven</sub> | 2.7*1/FCKIL | 1.8 | μs   |

| 4   | SIM Presence Detect to SIM reset Low | S <sub>pd2rst</sub>  | 0.9*1/FCKIL | 25  | ns   |

| Signal | Ball Location |

|--------|---------------|

| NC     | N7            |

| NC     | P7            |

| NC     | U21           |

| Table 68. 19 x 19 BGA No Cor | nnects <sup>1</sup> |

|------------------------------|---------------------|

|------------------------------|---------------------|

<sup>1</sup> These contacts are not used and must be floated by the user.

# 5.2.3.2 BGA Signal ID by Ball Grid Location—19 x 19 0.8 mm

Table 69. 19 x 19 BGA Signal ID by Ball Grid Location

| Signal ID  | Ball Location |

|------------|---------------|

| A0         | Y6            |

| A1         | AC5           |

| A10        | V15           |

| A11        | AB3           |

| A12        | AA3           |

| A13        | Y3            |

| A14        | Y15           |

| A15        | Y14           |

| A16        | V14           |

| A17        | Y13           |

| A18        | V13           |

| A19        | Y12           |

| A2         | AB5           |

| A20        | V12           |

| A21        | Y11           |

| A22        | V11           |

| A23        | Y10           |

| A24        | Y9            |

| A25        | Y8            |

| A3         | AA5           |

| A4         | Y5            |

| A5         | AC4           |

| A6         | AB4           |

| A7         | AA4           |

| A8         | Y4            |

| A9         | AC3           |

| ATA_CS0    | E1            |

| ATA_CS1    | G4            |

| ATA_DIOR   | E3            |

| ATA_DIOW   | H6            |

| ATA_DMACK  | E2            |

| ATA_RESET  | F3            |

| BATT_LINE  | F6            |

| BCLK       | W20           |

| BOOT_MODE0 | F17           |

| BOOT_MODE1 | C21           |

| Signal ID     | Ball Location |

|---------------|---------------|

| CKIL          | E21           |

| CLKO          | C20           |

| CLKSS         | H17           |

| COMPARE       | A20           |

| CONTRAST      | N21           |

| CS0           | U17           |

| CS1           | Y22           |

| CS2           | Y18           |

| CS3           | Y19           |

| CS4           | Y20           |

| CS5           | AA21          |

| CSI_D10       | K21           |

| CSI_D11       | K22           |

| CSI_D12       | K23           |

| CSI_D13       | L20           |

| CSI_D14       | L18           |

| CSI_D15       | L21           |

| CSI_D4        | J20           |

| CSI_D5        | J21           |

| CSI_D6        | L17           |

| CSI_D7        | J22           |

| CSI_D8        | J23           |

| CSI_D9        | K20           |

| CSI_HSYNC     | H22           |

| CSI_MCLK      | H20           |

| CSI_PIXCLK    | H23           |

| CSI_VSYNC     | H21           |

| CSPI1_MISO    | N2            |

| CSPI1_MOSI    | N1            |

| CSPI1_SCLK    | M4            |

| CSPI1_SPI_RDY | M1            |

| CSPI1_SS0     | M2            |

| CSPI1_SS1     | N6            |

| CSPI1_SS2     | M3            |

| CSPI2_MISO    | B4            |

| CSPI2_MOSI    | D5            |

MCIMX31/MCIMX31L Technical Data, Rev. 4.1